FIR filtering realization method and filtering device

A filter and filter coefficient technology, applied in the field of FIR filtering, can solve problems such as waste of FPGA resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the technical problems, technical solutions and advantages to be solved by the present invention clearer, the following will describe in detail with reference to the drawings and specific embodiments.

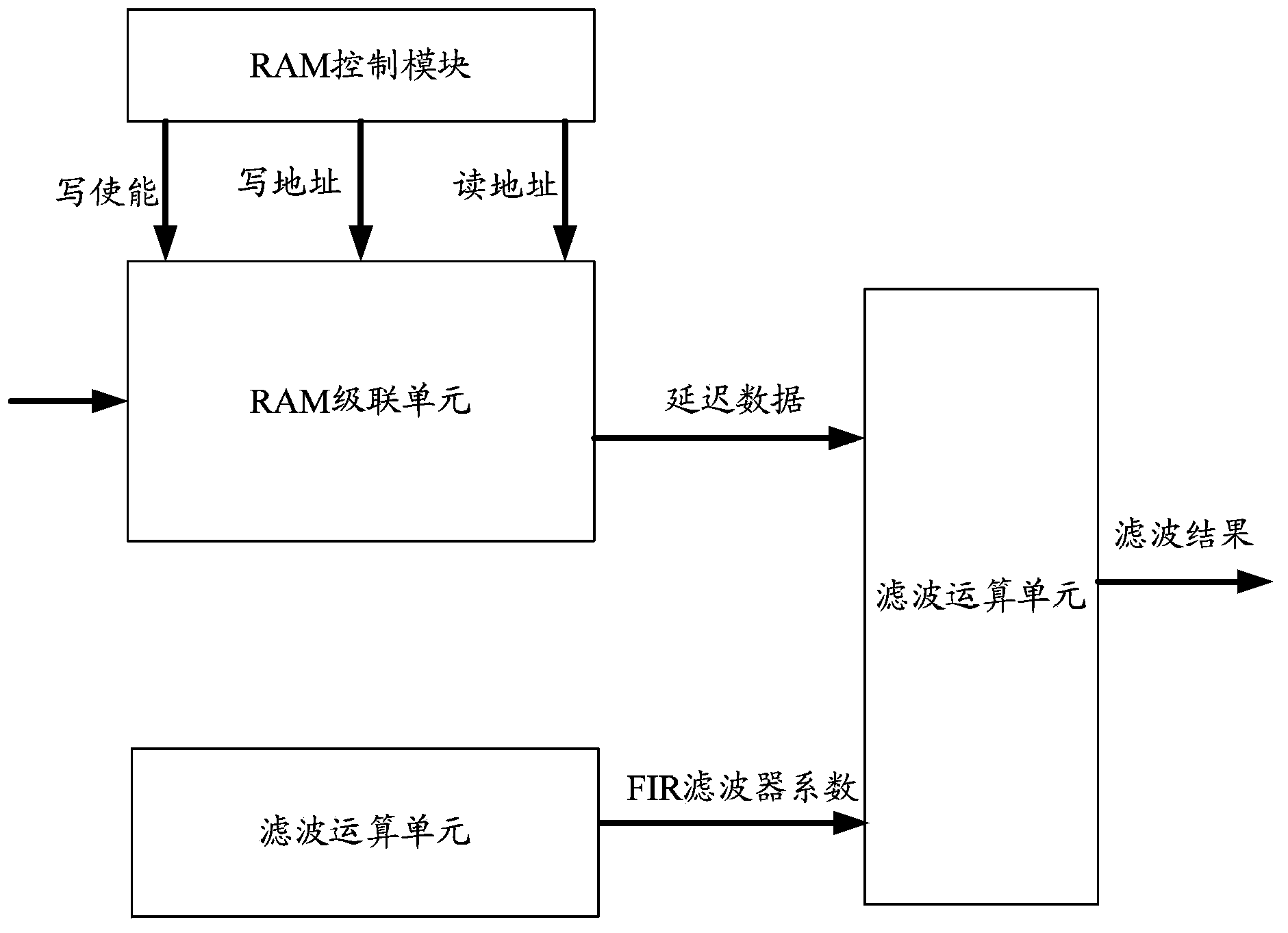

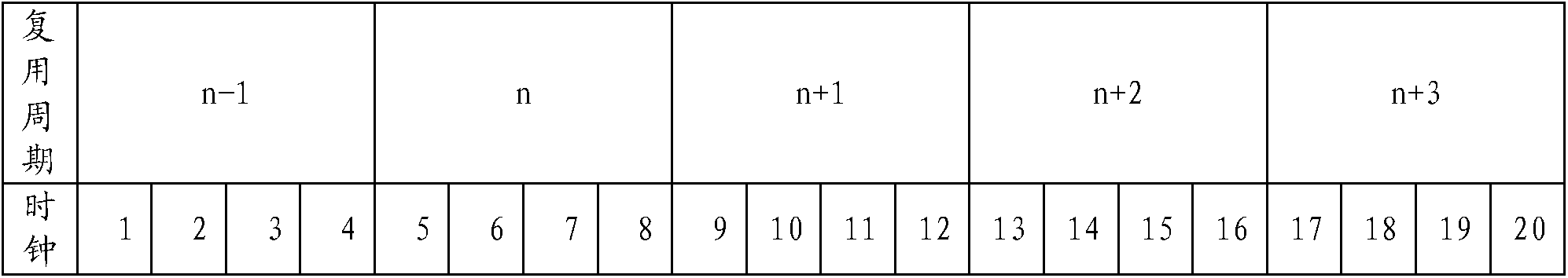

[0021] In the present invention, utilize the clock frequency of the FIR filter in the FPGA to be higher than the characteristics of the data input rate of the FIR filter, the RAMs in the FPGA are cascaded, and the changes of the read and write addresses of each RAM and the write enable are used to realize the internal data of each RAM. Selective write and read, realize the output of FIR filter delay data. Wherein, the clock period of the FIR filter can be calculated according to the clock frequency of the FIR filter.

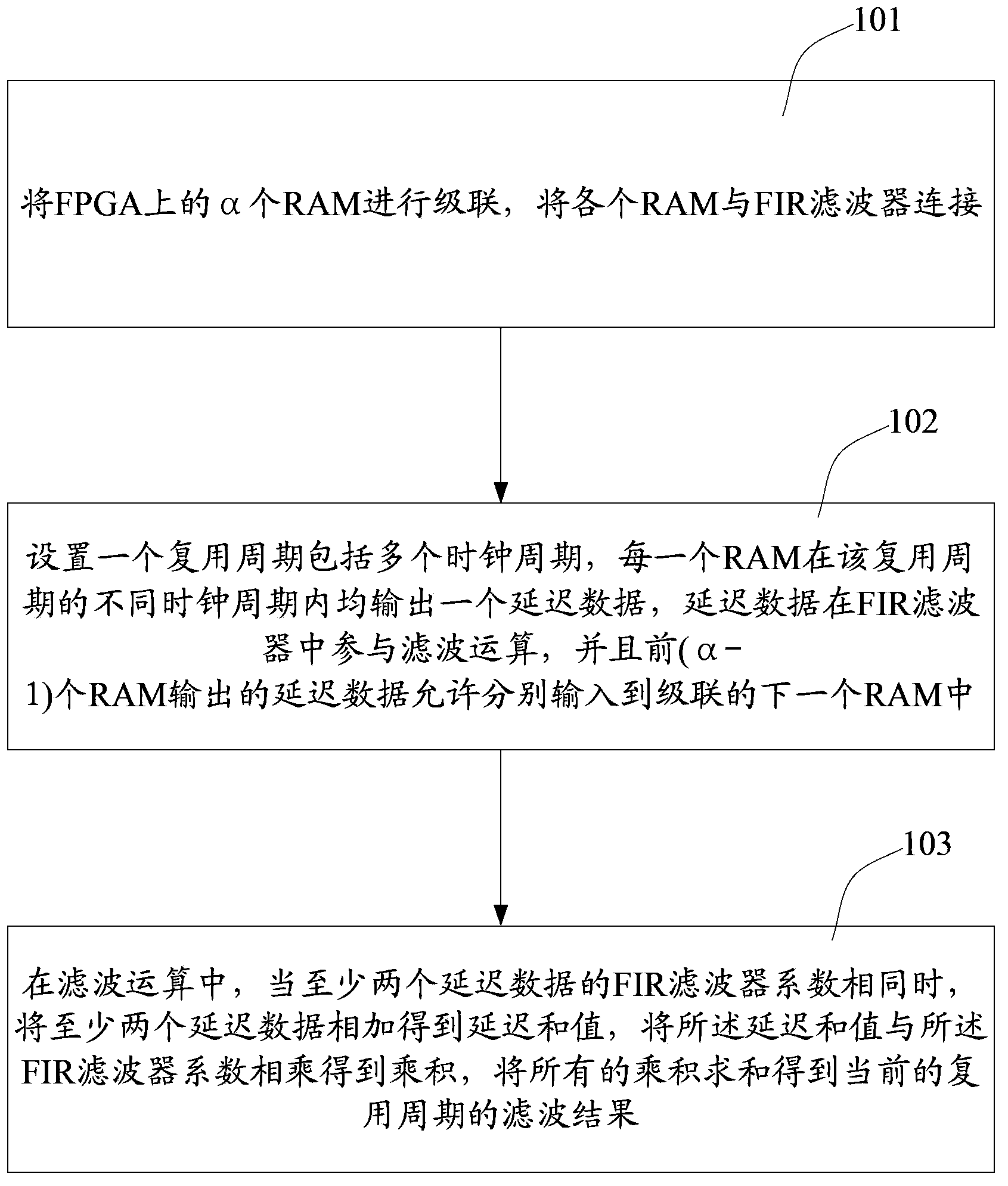

[0022] An embodiment of the present invention provides a method for implementing FIR filtering, such as figure 1 As shown, applied to FPGA, the methods include:

[0023] Step 101, cascading α RAMs on the FPGA, and connecting each RAM wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More