System level model building method of multiple core sharing SIMD coprocessor

A technology of coprocessor and construction method, applied in the field of system-level model construction of multi-core shared SIMD coprocessor, can solve the problems of waste of resources and power consumption, and achieve the goal of reducing system power consumption, high efficiency and improving resource utilization. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] A method for constructing a system-level model of a multi-core shared SIMD coprocessor of the present invention will be described in detail below in conjunction with the embodiments and the accompanying drawings.

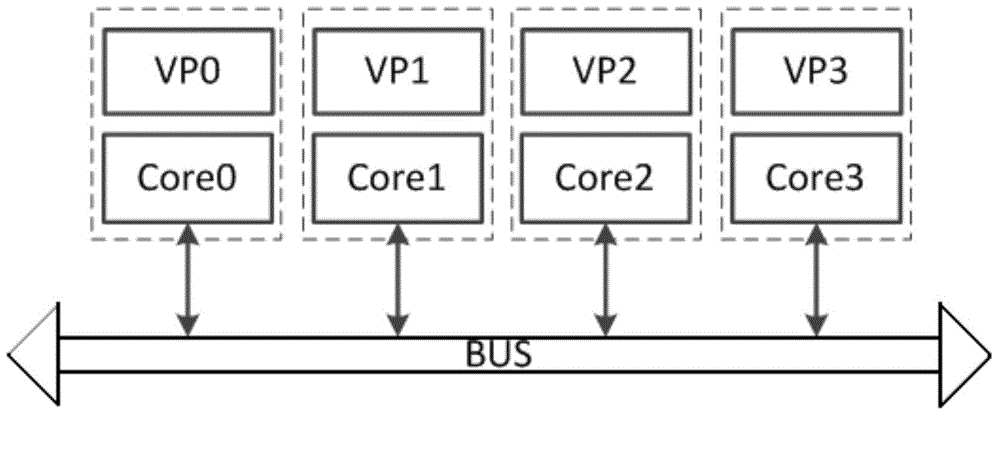

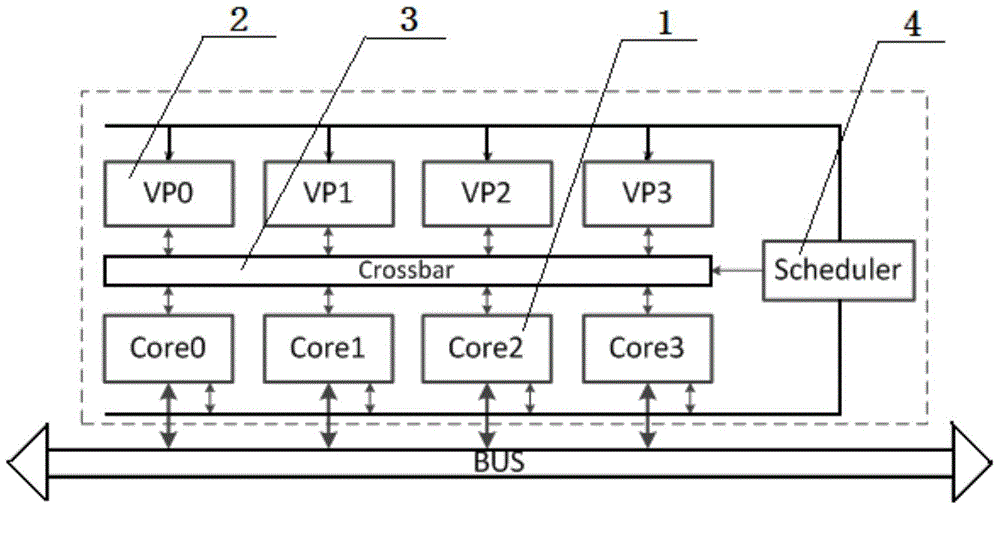

[0021] A system-level model building method for a multi-core shared SIMD coprocessor of the present invention includes a system-on-chip, and the system-on-chip is provided with n cores and n vector coprocessors, wherein n is a positive even number, and the The n vector coprocessors are connected to the n cores through a crossbar switch, and are respectively connected to the n cores, n vector coprocessors and crossbar switches for passing through the crossbar A scheduler that switches and schedules the vector coprocessor in communication with the core, wherein the scheduler schedules the vector coprocessor according to the current state of each vector coprocessor.

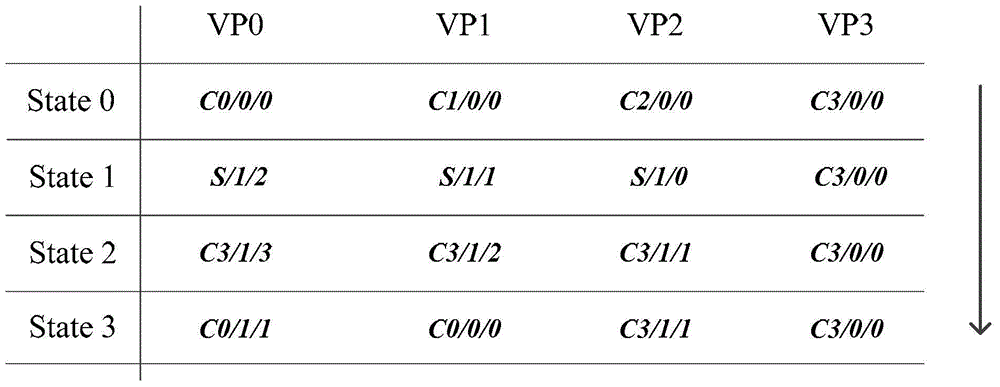

[0022] Each of the vector coprocessors describes the current state through 3 state registers, w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More