Patents

Literature

35 results about "N-vector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The n-vector representation (also called geodetic normal or ellipsoid normal vector) is a three-parameter non-singular representation well-suited for replacing latitude and longitude as horizontal position representation in mathematical calculations and computer algorithms.

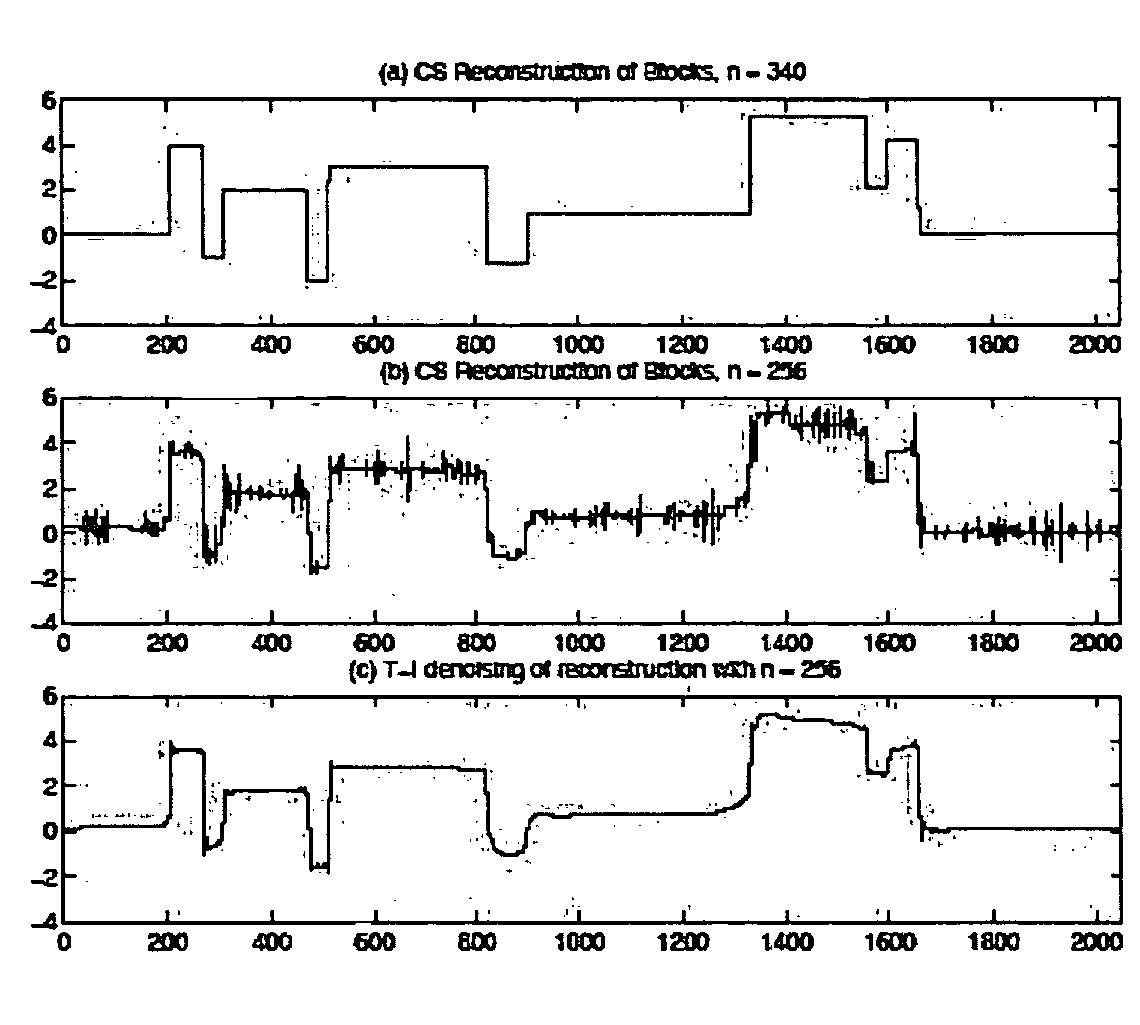

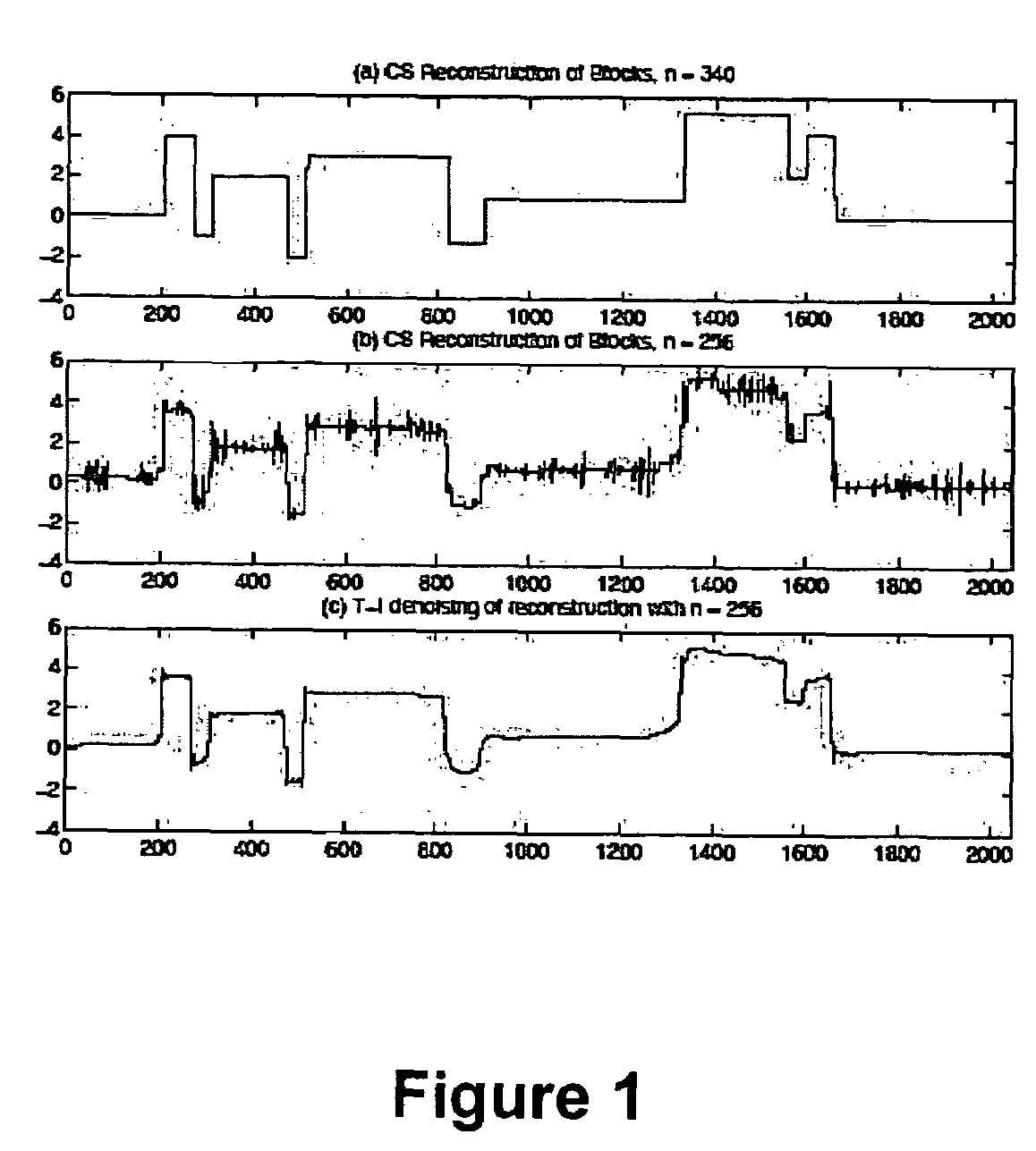

Method and apparatus for compressed sensing

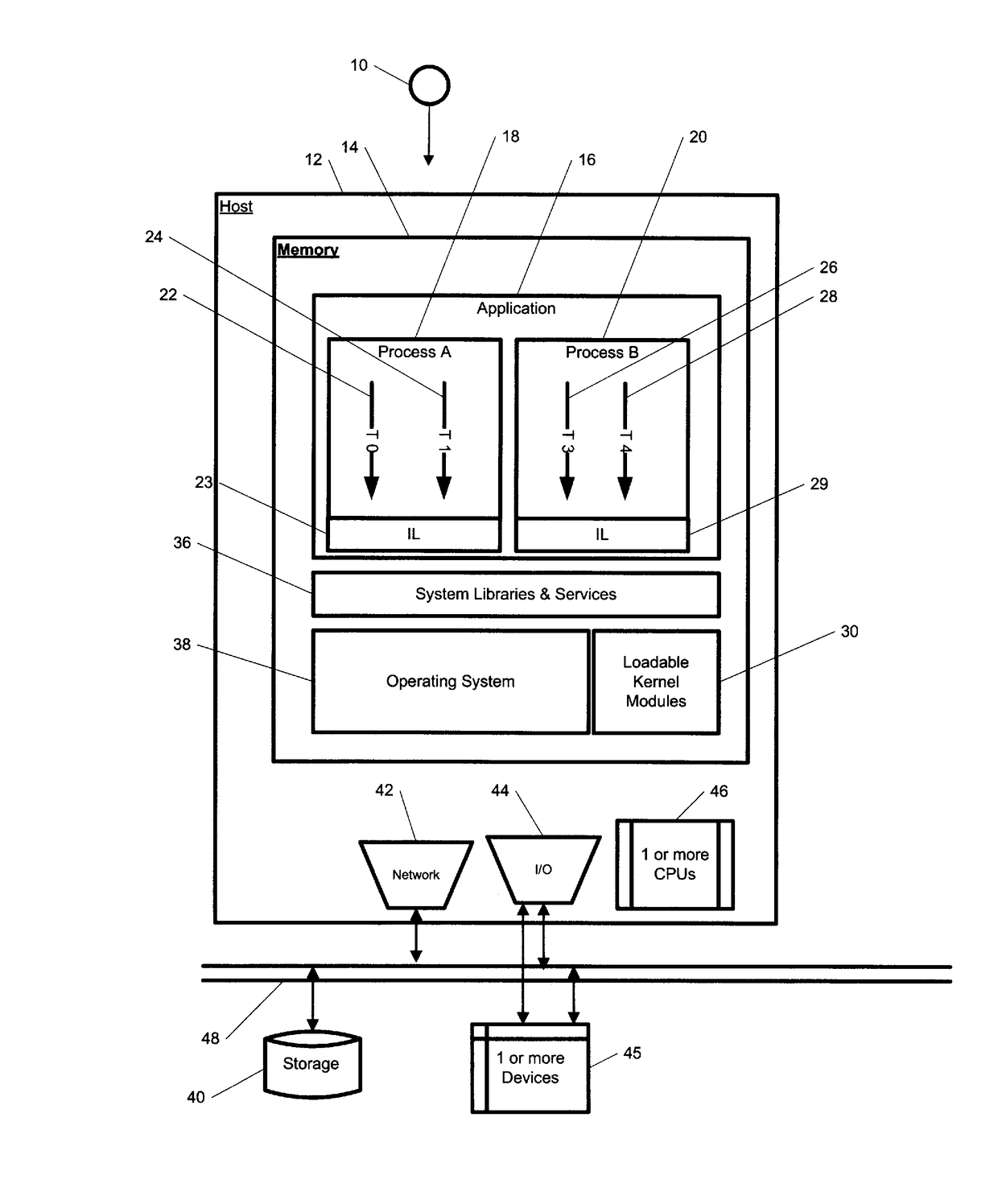

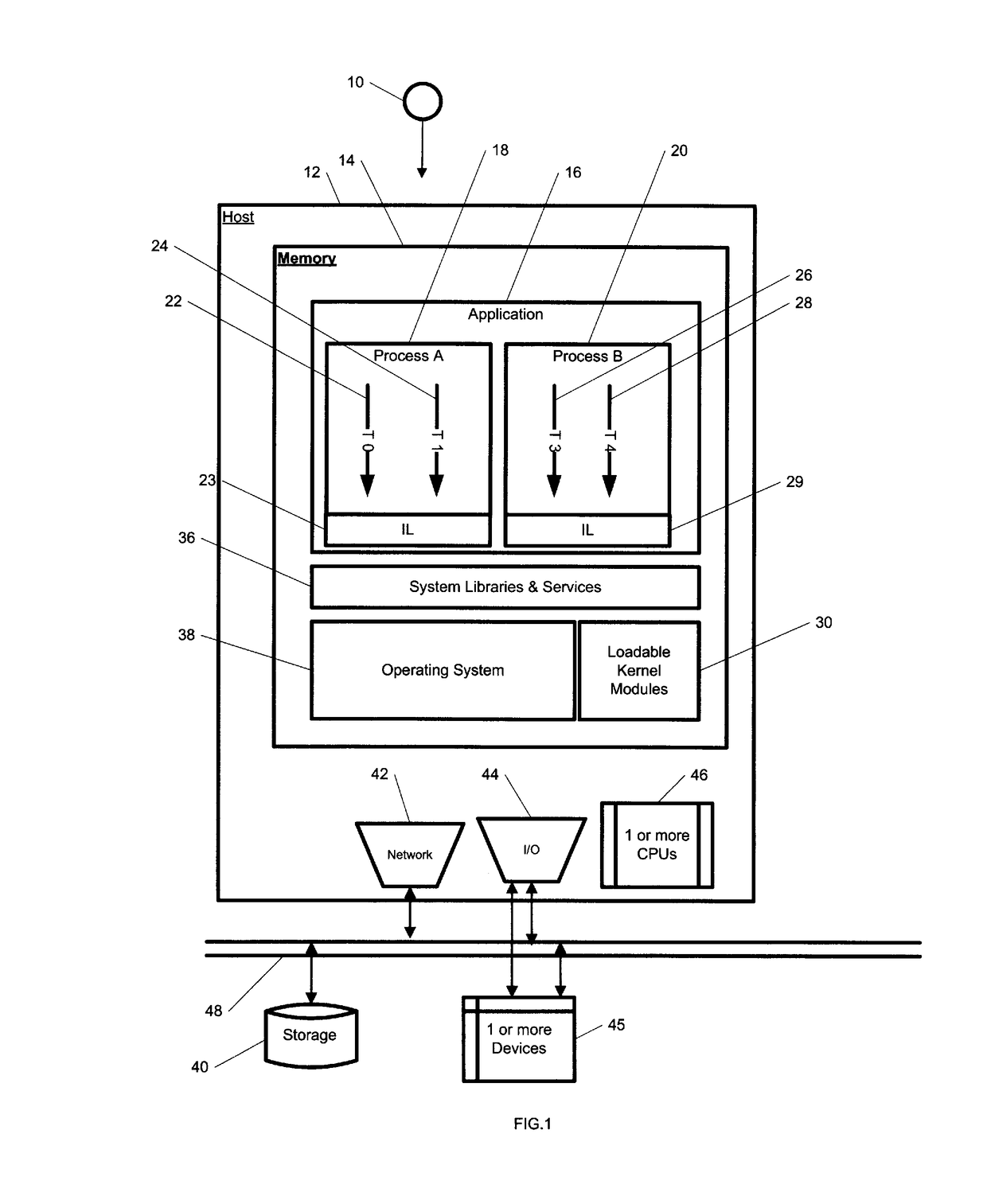

ActiveUS7646924B2Image enhancementReconstruction from projectionArray data structureComputer science

Method and apparatus for compressed sensing yields acceptable quality reconstructions of an object from reduced numbers of measurements. A component x of a signal or image is represented as a vector having m entries. Measurements y, comprising a vector with n entries, where n is less than m, are made. An approximate reconstruction of the m-vector x is made from y. Special measurement matrices allow measurements y=Ax+z, where y is the measured m-vector, x the desired n-vector and z an m-vector representing noise. “A” is an n by m matrix, i.e. an array with fewer rows than columns. “A” enables delivery of an approximate reconstruction, x#, of x. An embodiment discloses approximate reconstruction of x from the reduced-dimensionality measurement y. Given y, and the matrix A, x# of x is possible. This embodiment is driven by the goal of promoting the approximate sparsity of x#.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

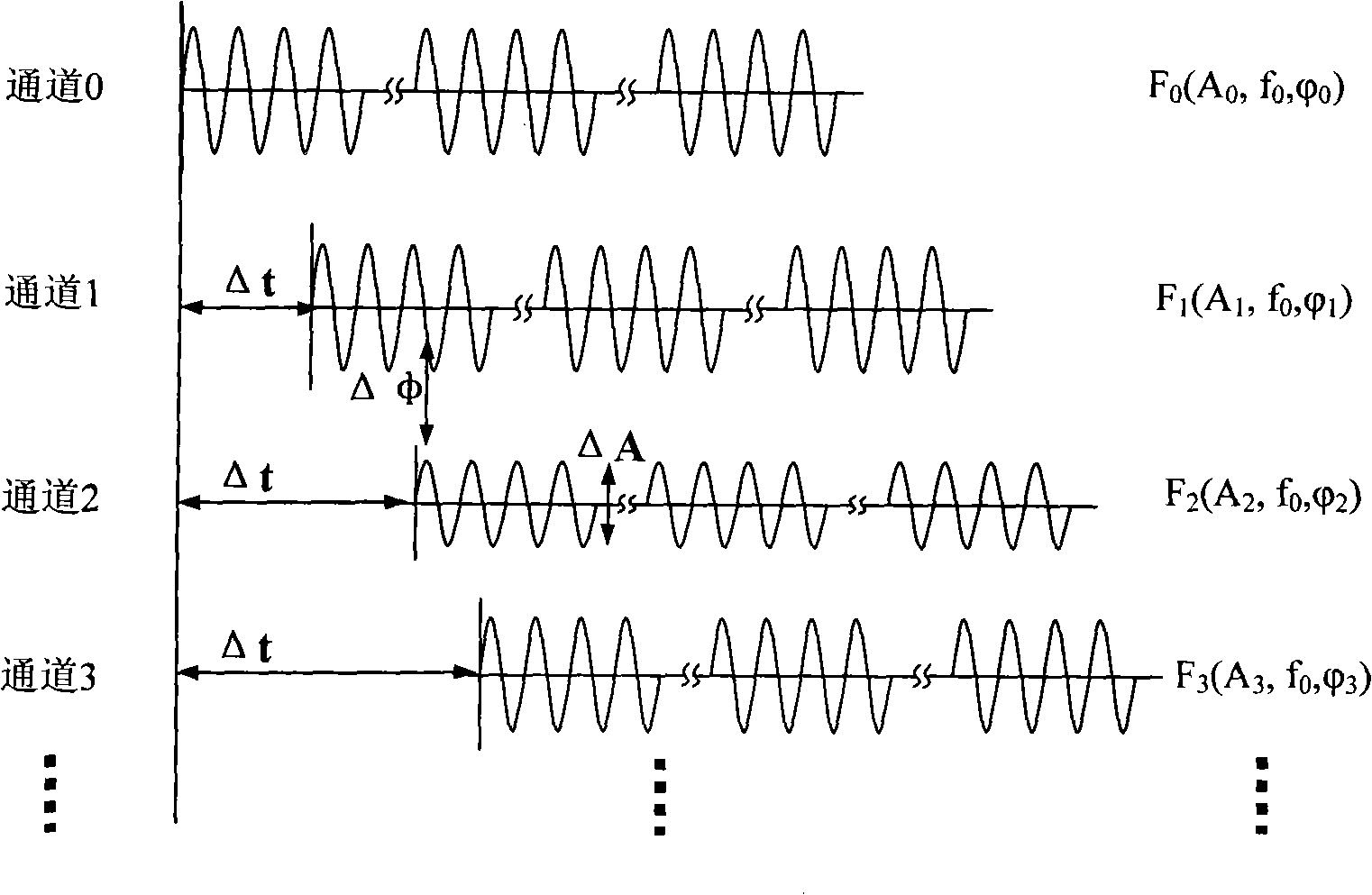

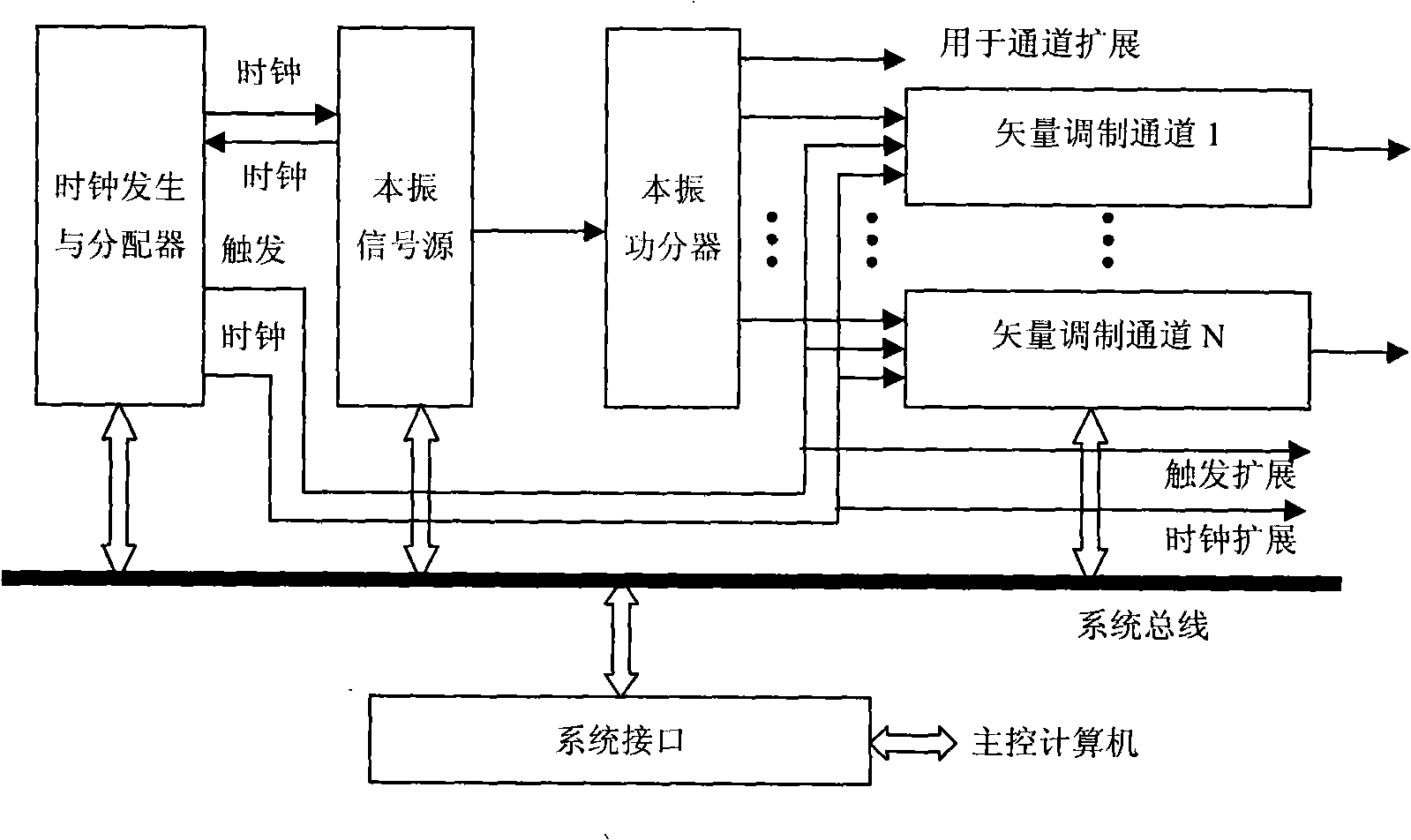

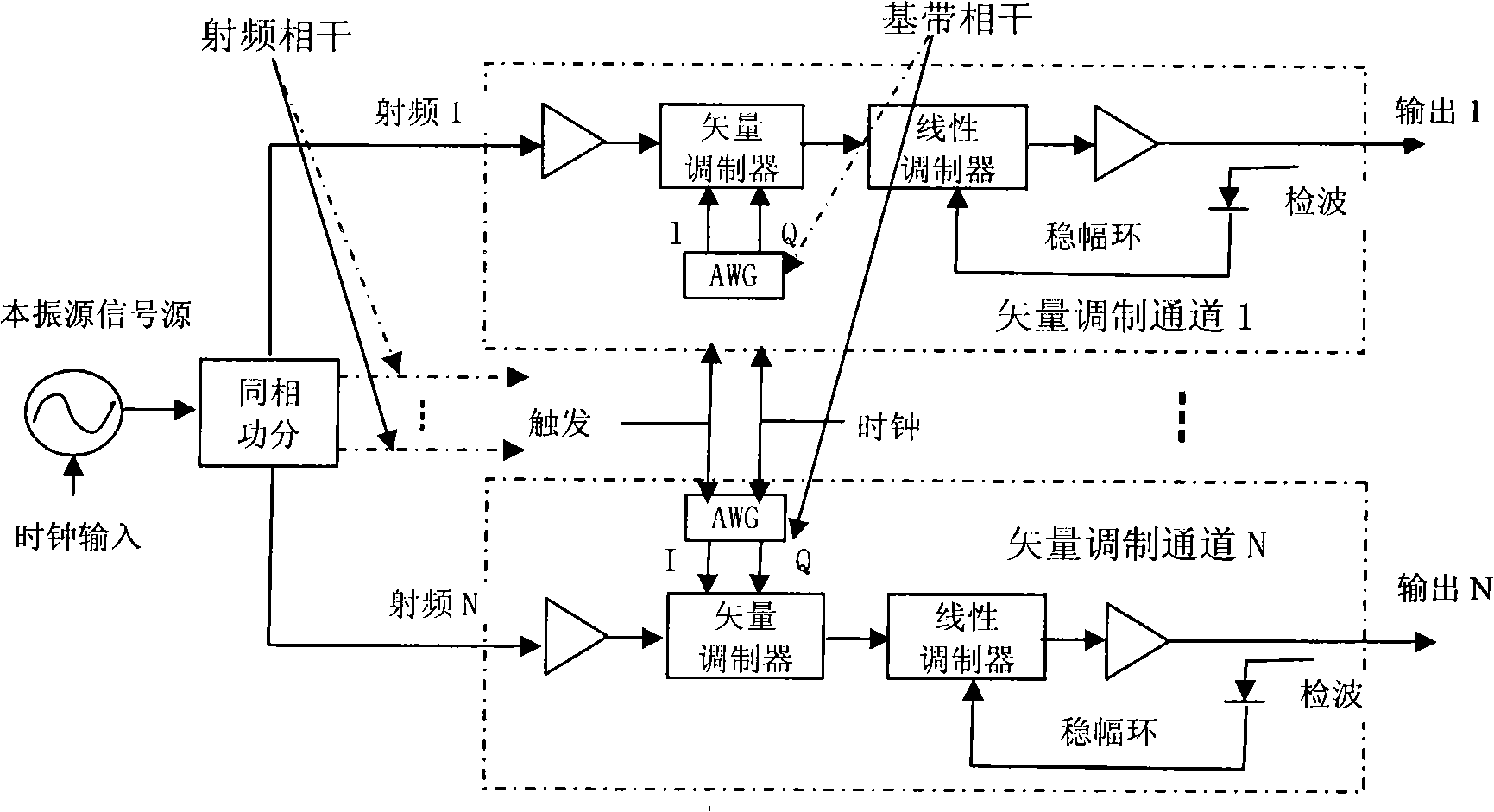

Modularization phase coherent multichannel signal generating device based on PXI bus

InactiveCN101281246AWide Phase Adjustment RangeReduce volumeRadio wave finder detailsRadio wave direction/deviation determination systemsEngineeringSignal generator

A modularization phase coherent multichannel signal generating device based on PXI bus, relates to the measuring and testing technique field. A main control computer is connected with the system bus through system interfaces; the system bus is respectively connected with a clock generating and distribution device, a local oscillation signal source and N vector modulation channels through signal wires; the clock generating and distribution device and the local oscillation signal source respectively provide clock signals to each other through two signal wires; the clock generating and distribution device respectively provides clock signals and trigger signals to N vector modulation channels, and provides externally a clock extension interface and a triggering extension interface, through 2N+2 signal wires; the local oscillation signal source is connected with a local oscillation power divider; the local oscillation power divider is connected with N vector modulation channels, and externally provides a channel extension interface, through N+1 signal wires; each vector modulation channel externally provides a coherent signal output interface. The invention has advantages of wide phase adjustment scope, small volume, light weight, high system flexibility and low cost.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

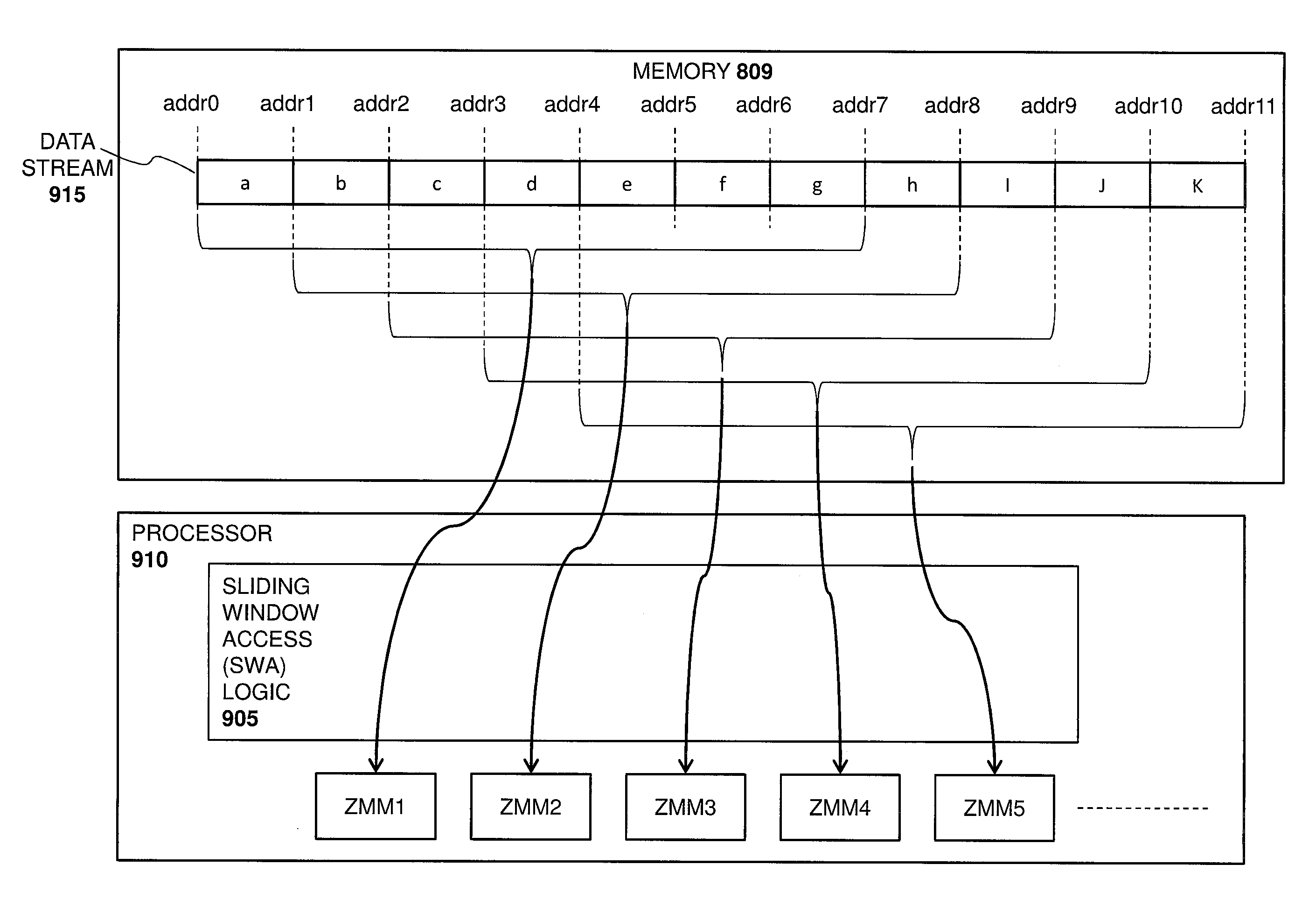

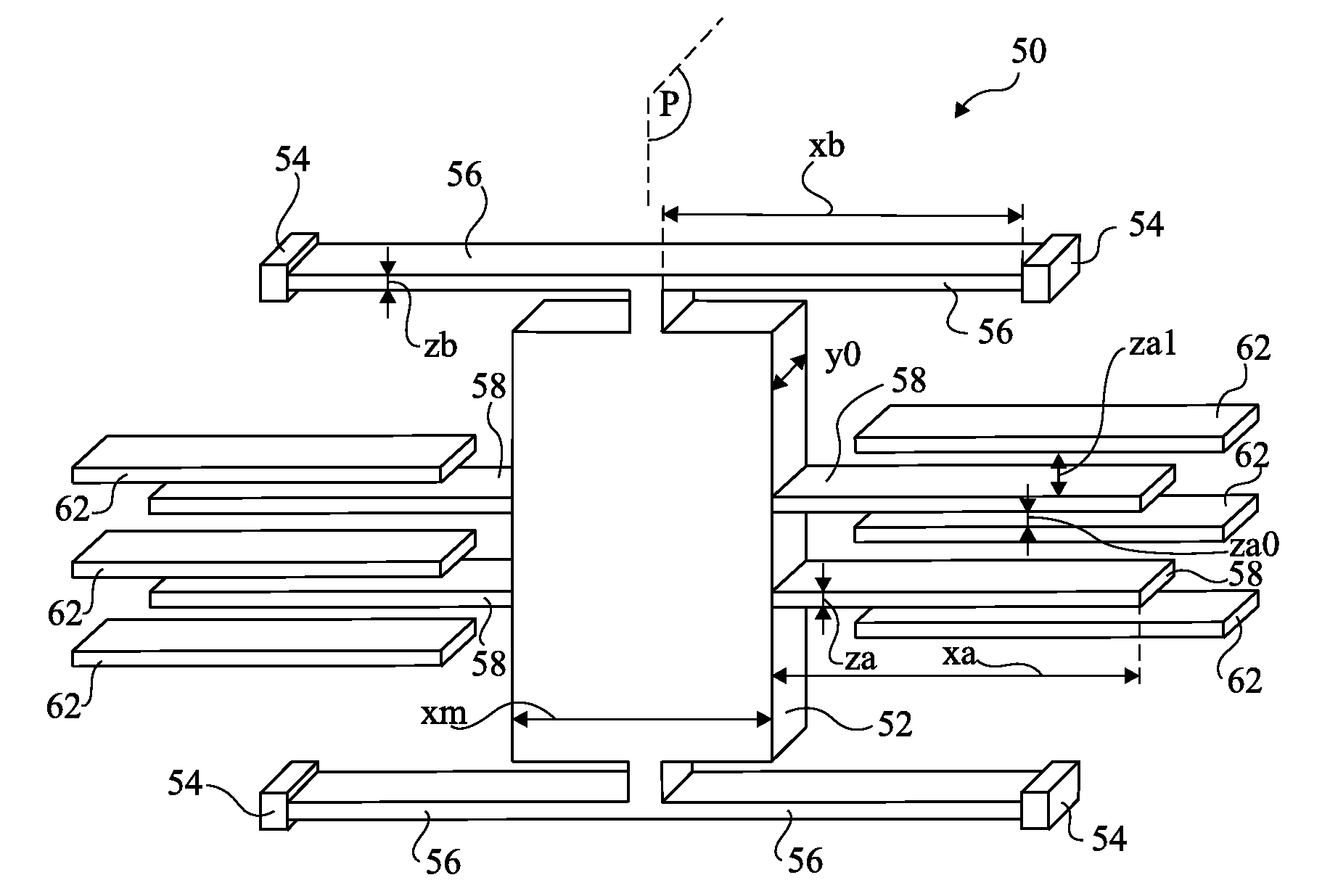

Apparatus and method for sliding window data access

An apparatus and method are described for fetching and storing a plurality of portions of a data stream into a plurality of registers. For example, a method according to one embodiment includes the following operations: determining a set of N vector registers into which to read N designated portions of a data stream stored in system memory; determining the system memory addresses for each of the N designated portions of the data stream; fetching the N designated portions of the data stream from the system memory at the system memory addresses; and storing the N designated portions of the data stream into the N vector registers.

Owner:TAHOE RES LTD

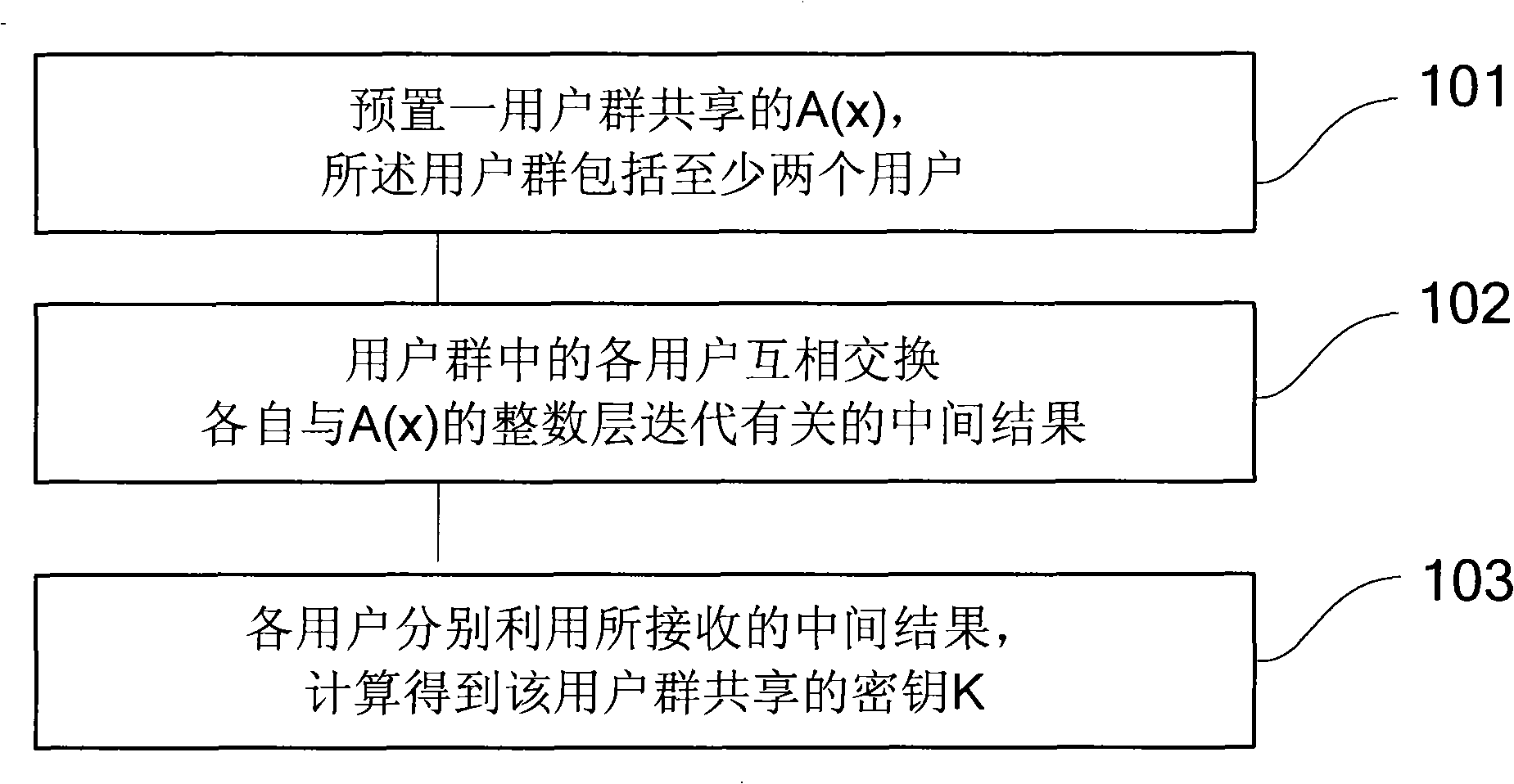

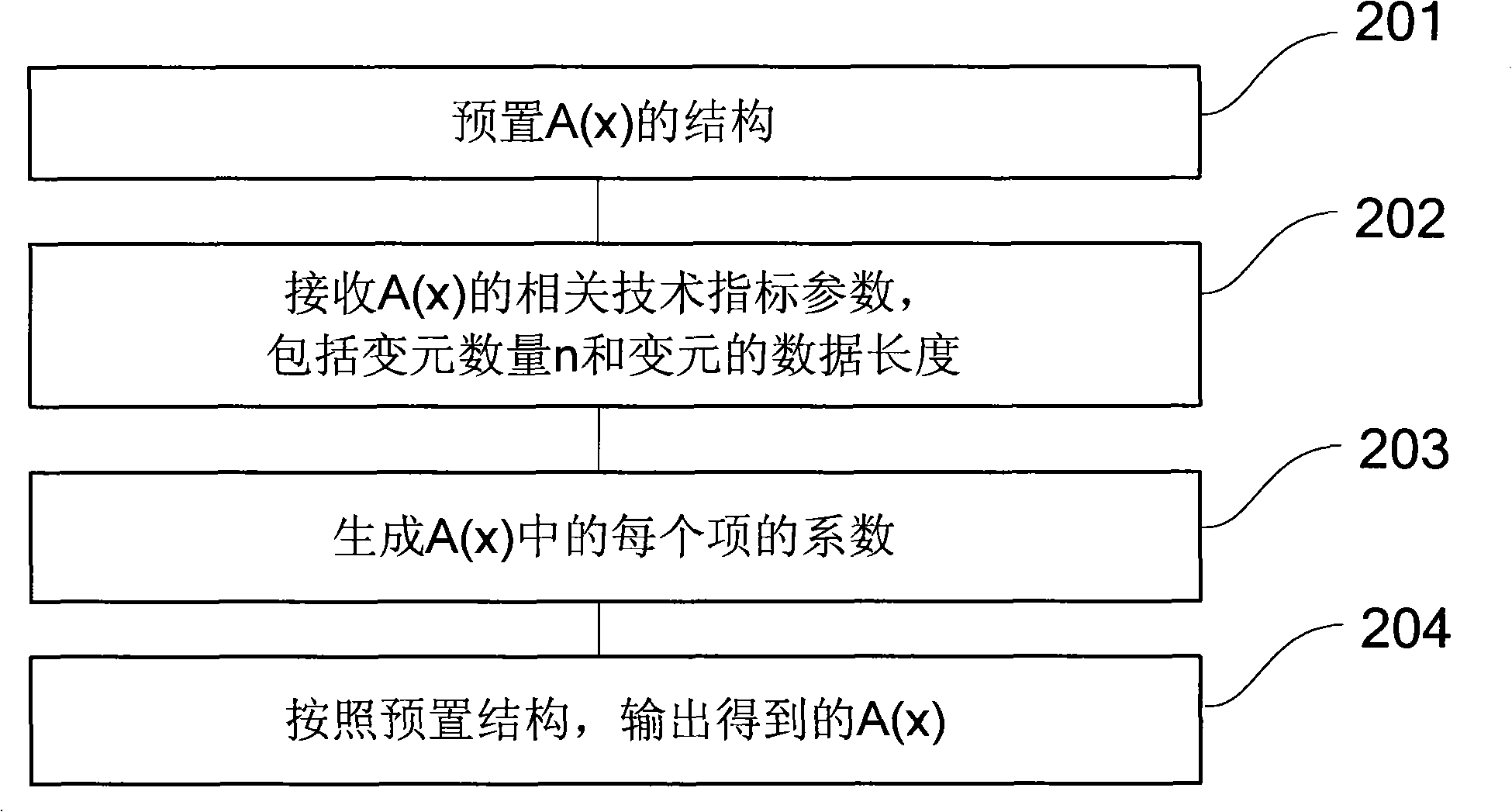

Cipher key negotiating method, enciphering/deciphering method and signature/verification method

InactiveCN101374043AScale upIncreased complexityKey distribution for secure communicationPublic key for secure communicationAlgorithmFunction group

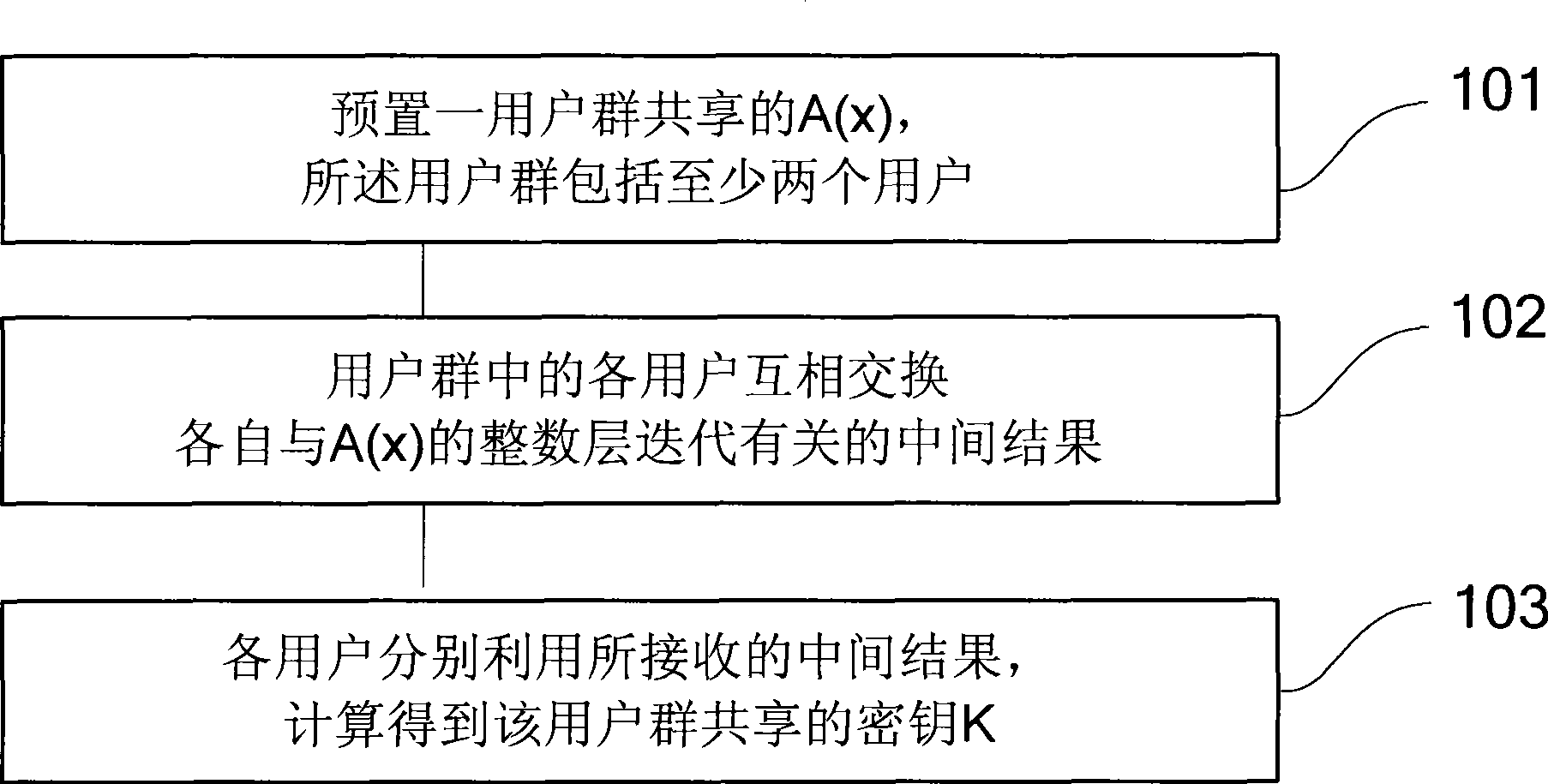

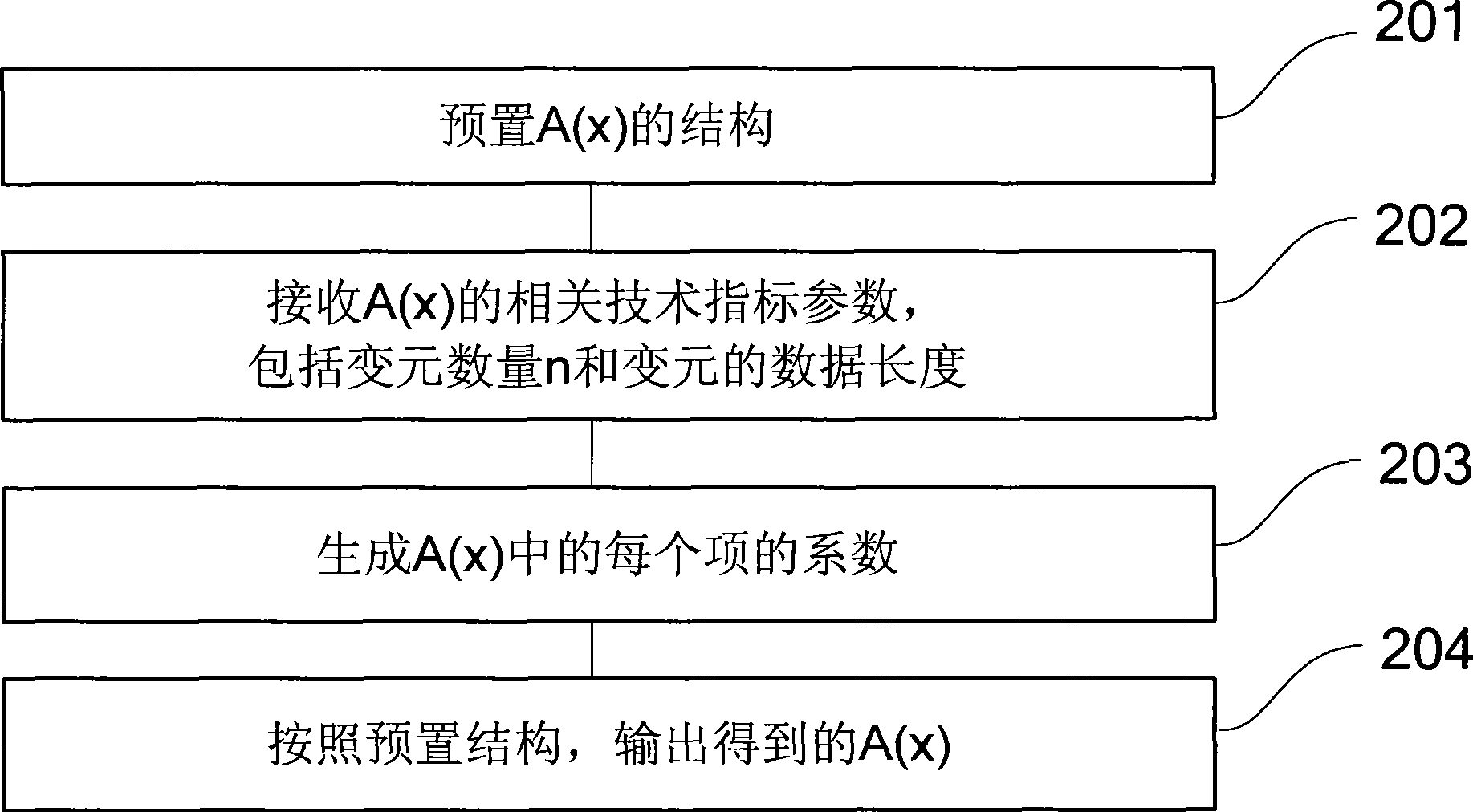

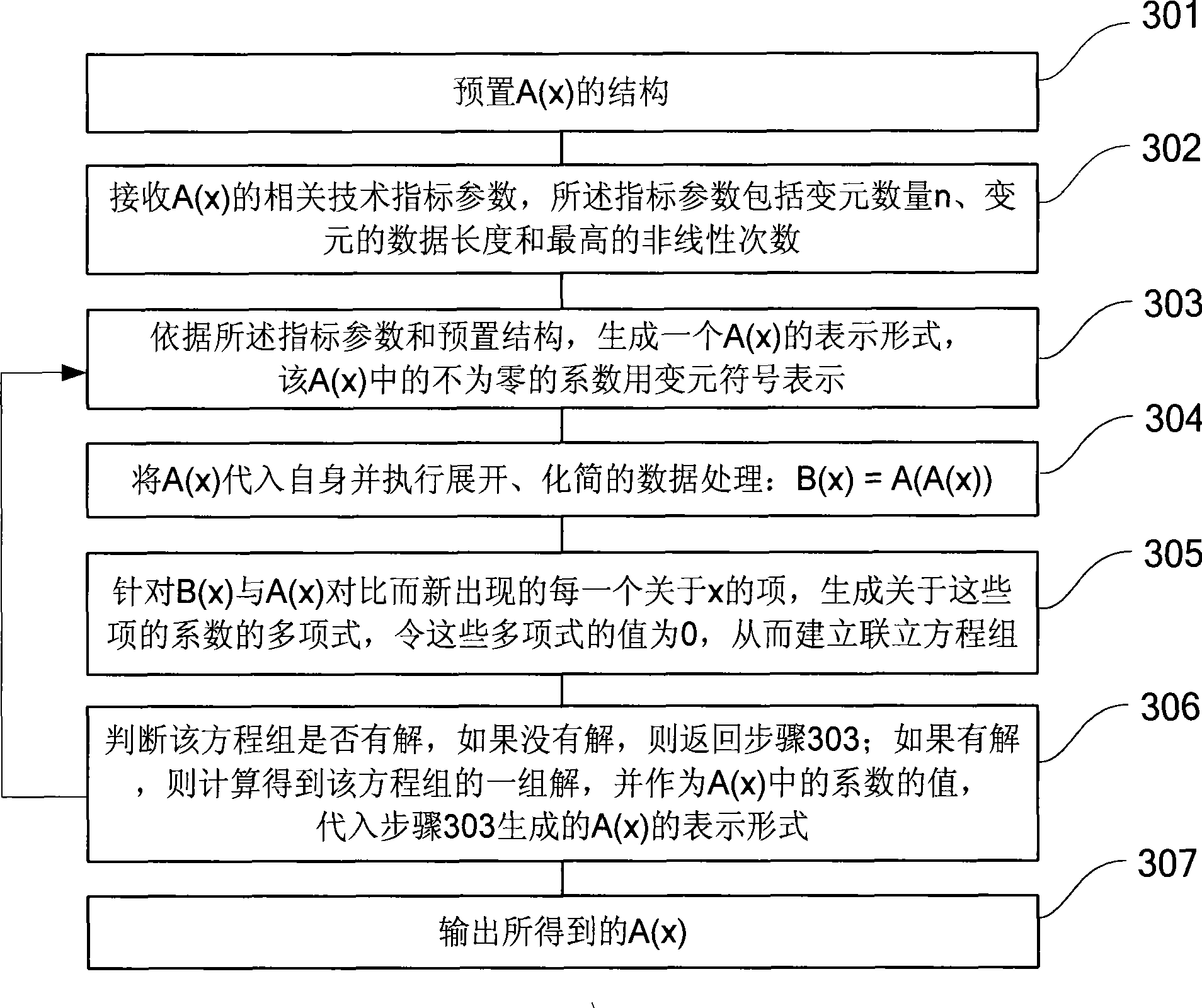

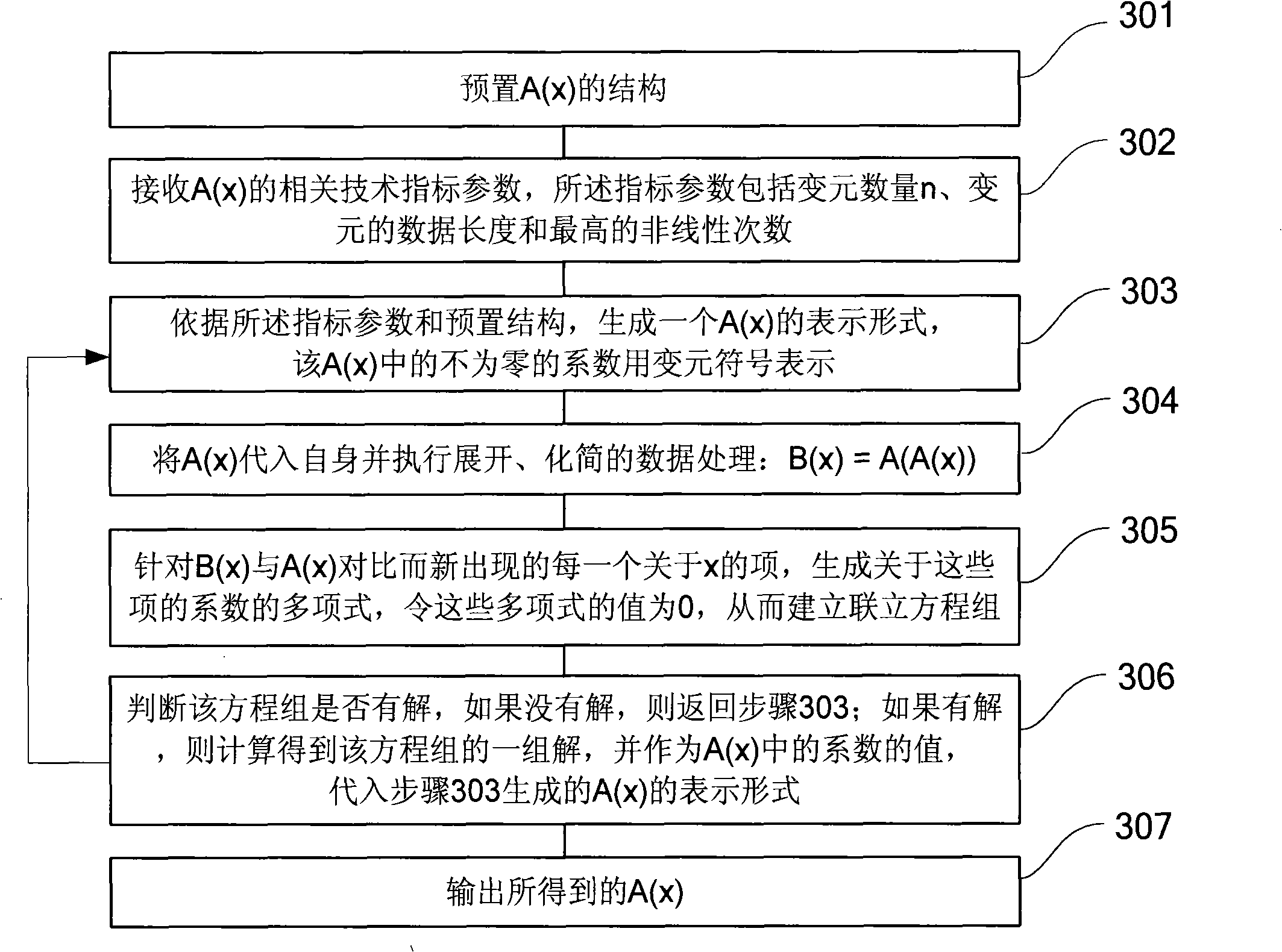

The invention provides a key agreement method and an encryption / decryption method and a signature / verification method. The key agreement method comprises the following steps: step 1. an A(x) shared by a user group is prearranged, wherein the user group comprises at least two users; the A(x) is a nonlinear function group from n vector x to n vector y=(y1,ellipsis, yn)=A(x)=(A1(x1,ellipsis,xn),ellipsis, An(x1,ellipsis,xn), wherein n is more than 1; and the A(x) meets the conditions that when the s layer iterative A<(s)>(x) of the A(x) is compared with the A(x), the number and type of the subsections with non-zero x coefficient are kept unchanged, and s is an integer; if B(x) is equal to A(A(x)), A(B(x)) is equal to B(A(x)); step 2: the users in the user group exchange the intermediate results related to the integer layer iteratives of the A(x); and the step 3: the users respectively adopt the received intermediate results to calculate the key K which is shared by the user group. The method has the advantages of unique coding style, strong attack resistance, enhanced scale and complexity of the cryptographic algorithm, and improved space and safety of the algorithm.

Owner:管海明 +1

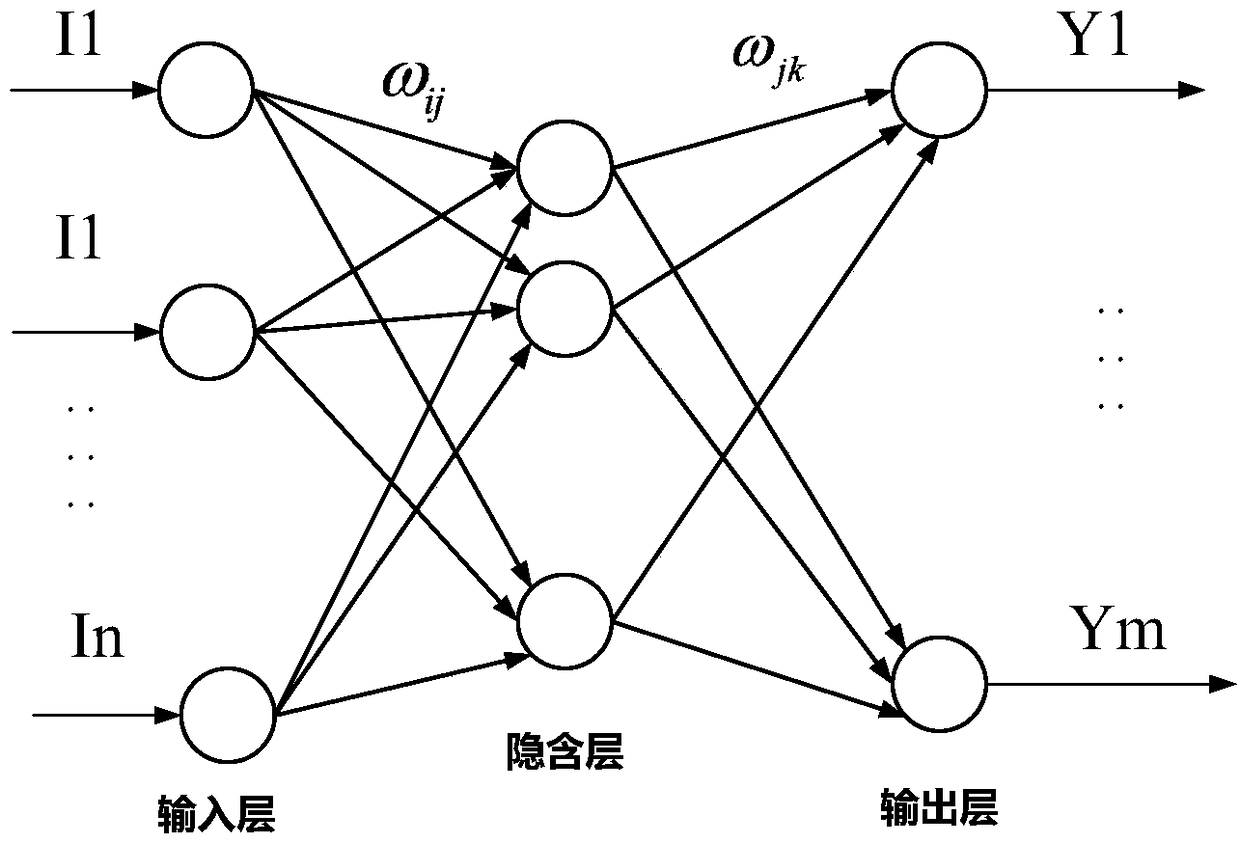

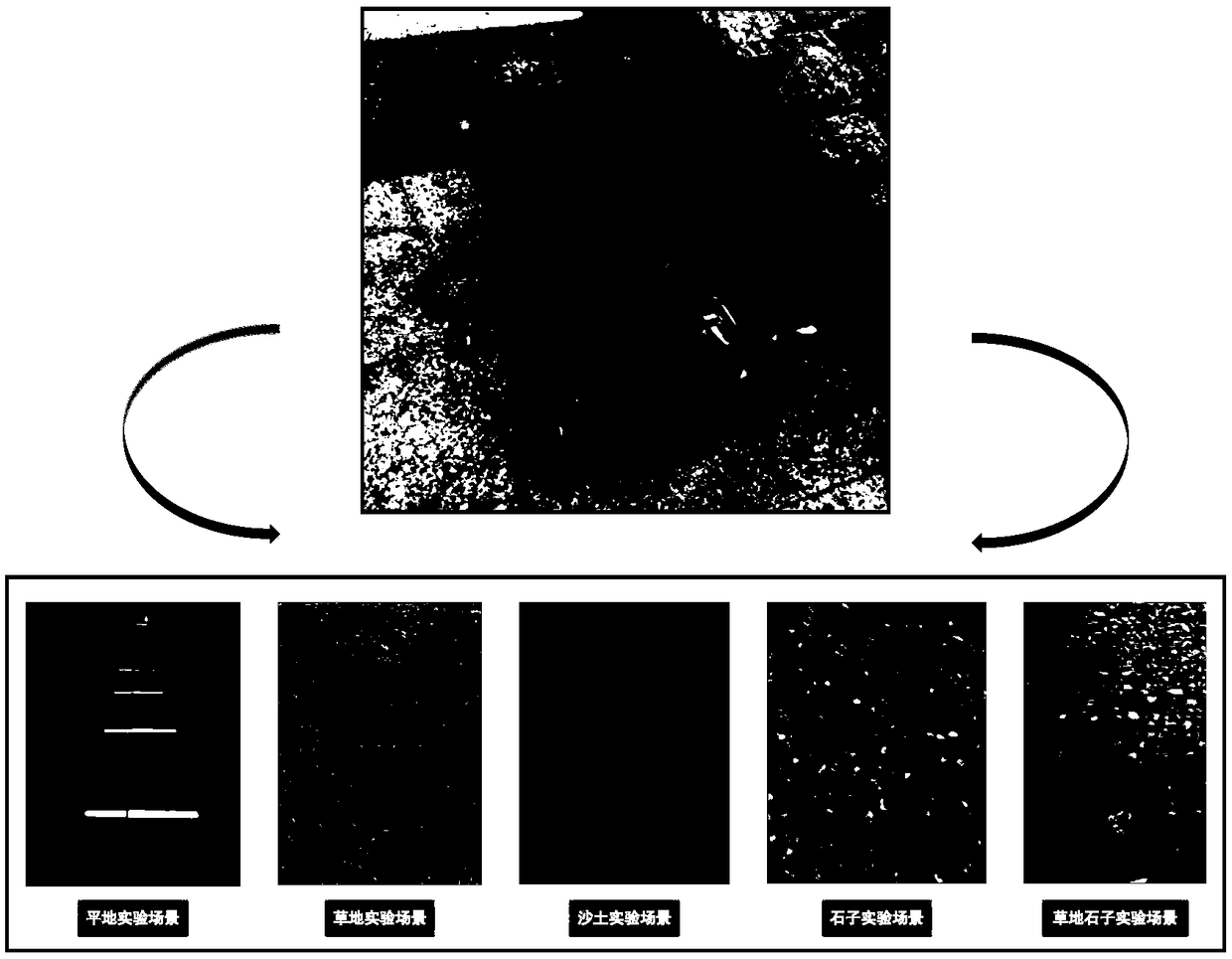

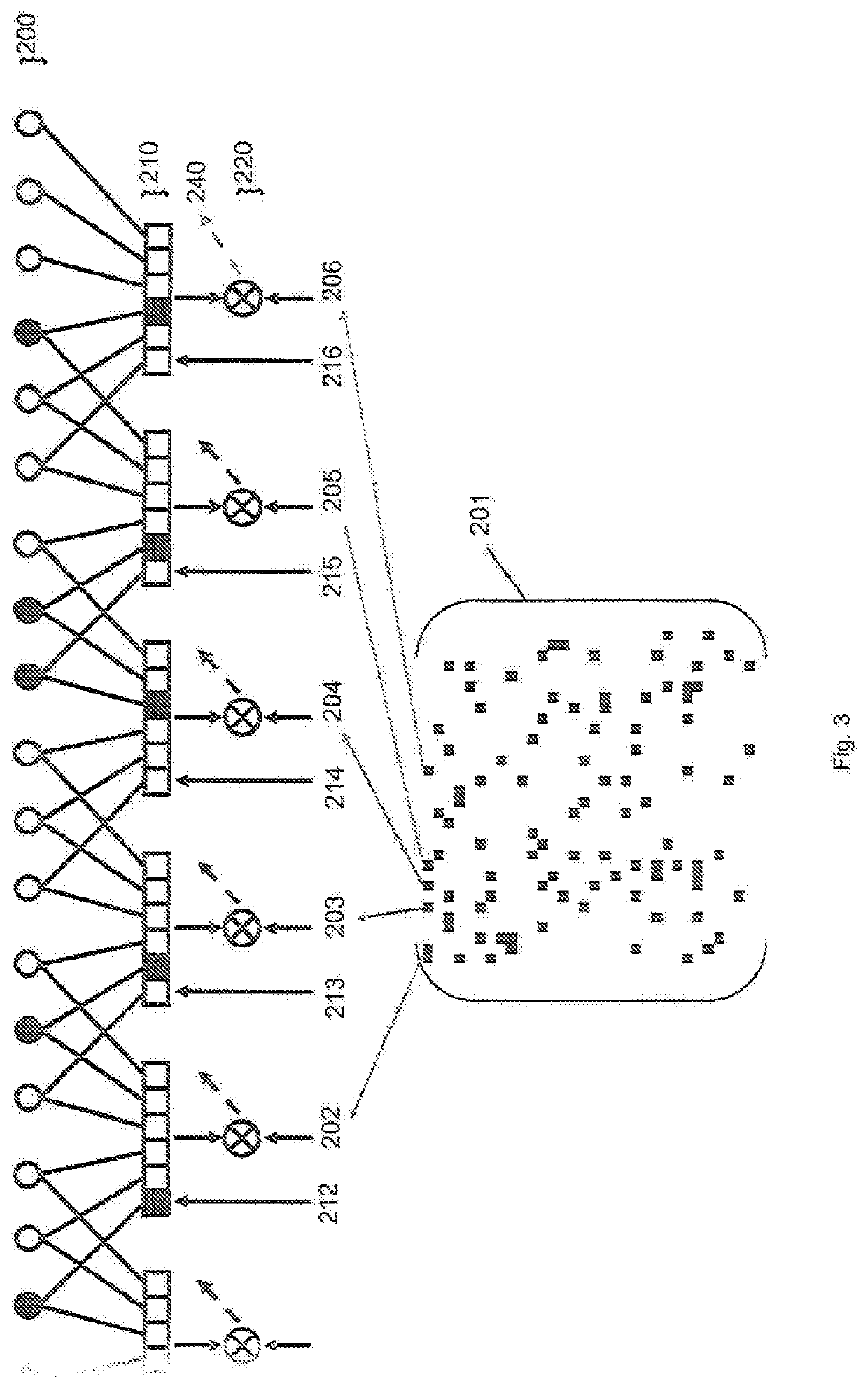

Terrain classification and recognition method based on learned vibration information

InactiveCN108830325AHigh feasibilityImprove accuracyScene recognitionLearning basedPattern recognition

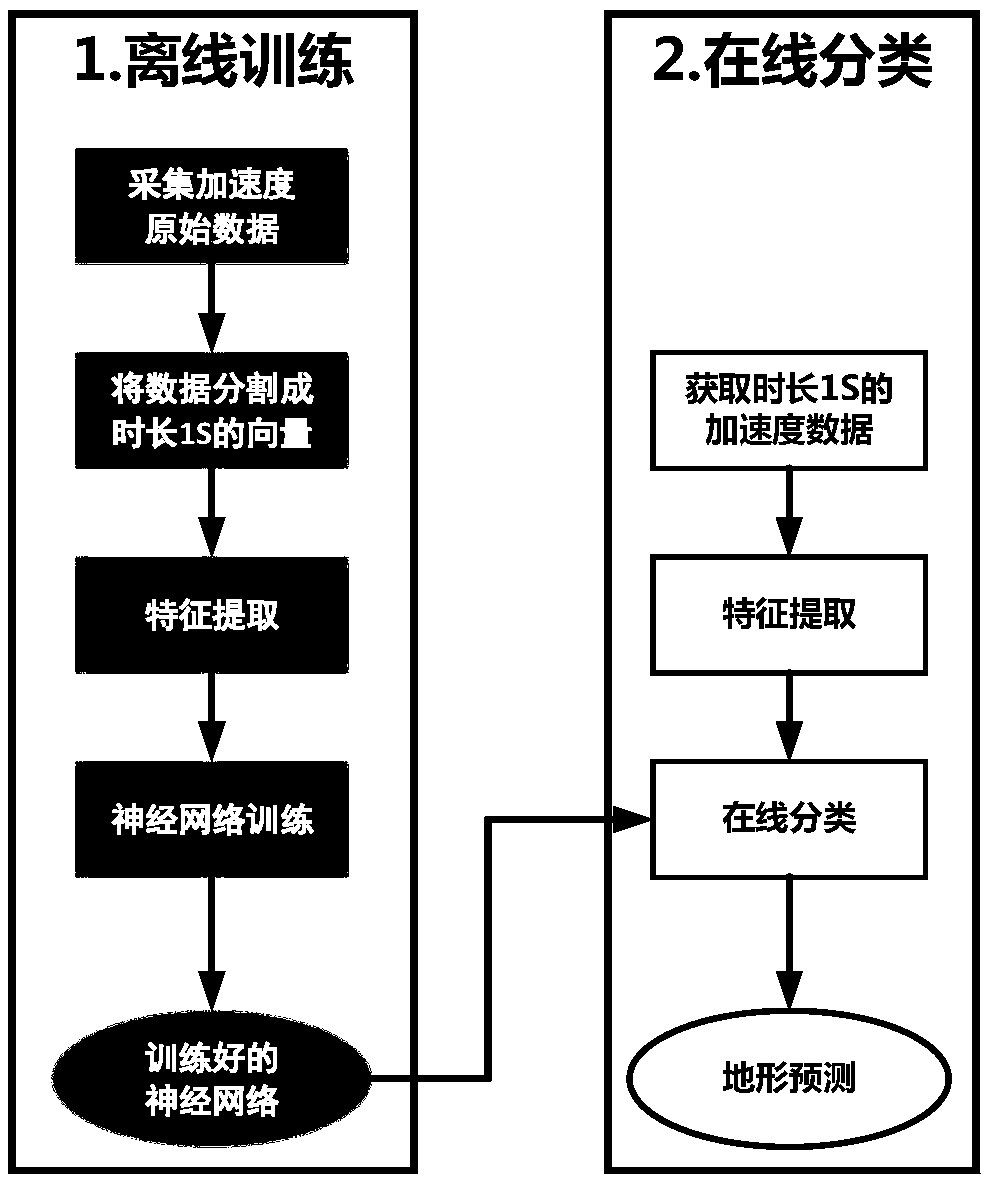

The invention relates to a terrain classification and recognition method based on learned vibration information, which aims to solve a problem of low accuracy of the existing classification and recognition method. The terrain classification and recognition method comprises the steps of first, collecting original data of vibration information of a sensor in the x-axis, y-axis and z-axis directionsin a coordinate system; second, performing segmentation processing on the original data to form n vectors with the time length being 1s; third, performing terrain type marking on the n vectors; fourth, converting the segmented n vectors into a frequency domain; fifth, performing off-line learning training on the n vectors converted into the frequency domain by using a multilayer feedforward neuralnetwork to obtain a trained multilayer feedforward neural network; and sixth, obtaining vibration data online in real time, executing the step two to the step four, and performing online classification and recognition by using the trained multilayer feedforward neural network in the step five to obtain the terrain type. The terrain classification and recognition method is applied to the technicalfield of recognition and classification.

Owner:HARBIN INST OF TECH

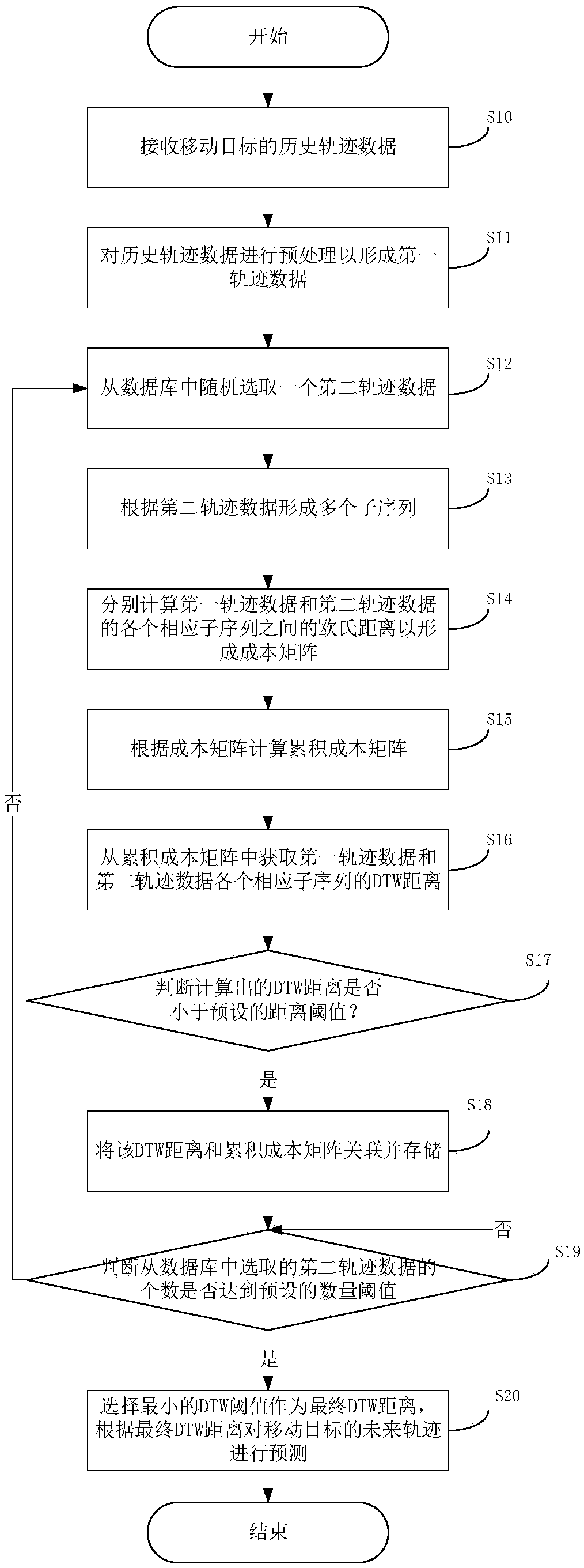

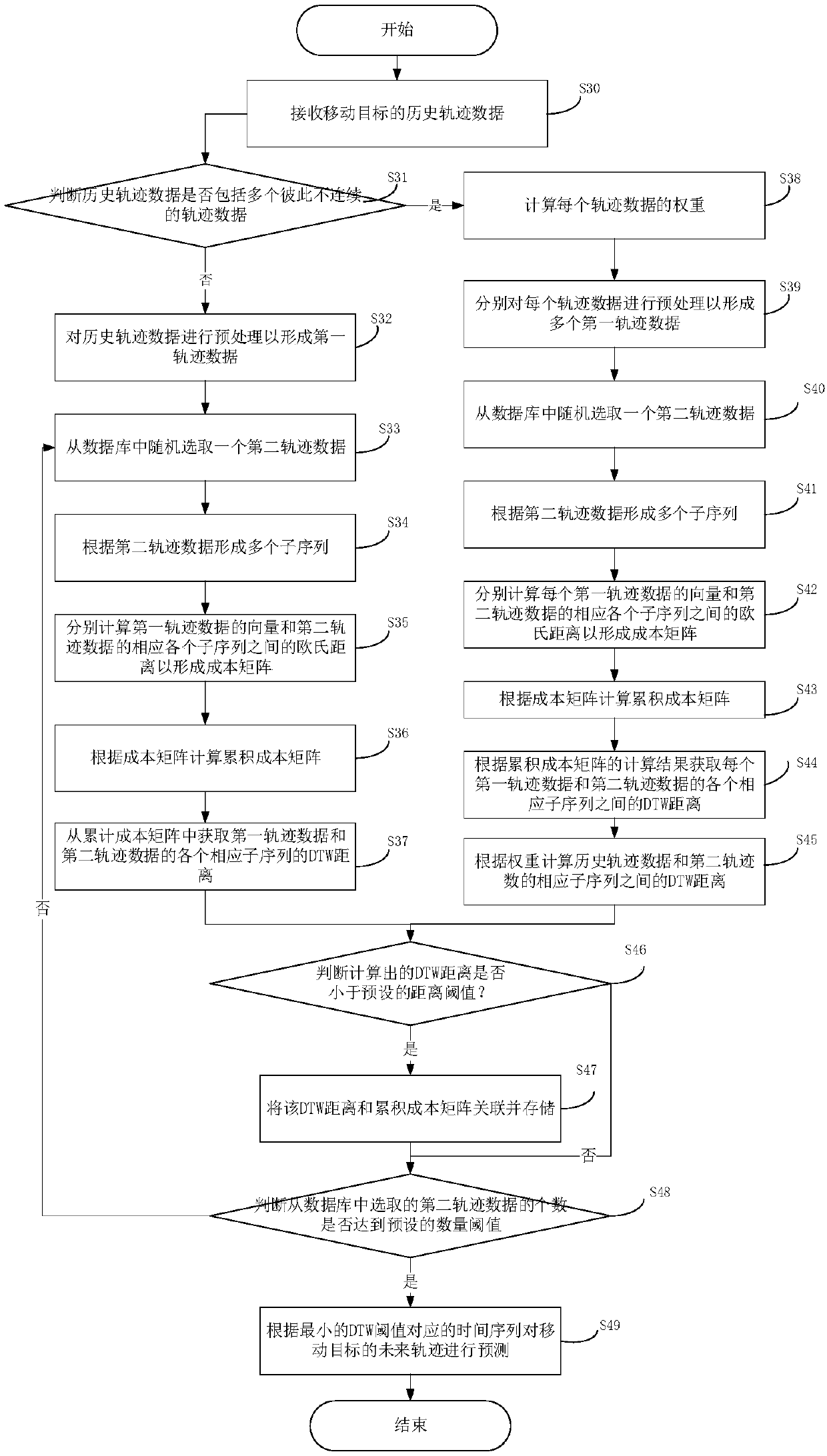

Method and system for measuring marine moving target trajectory similarity

ActiveCN109635867AImprove accuracyHigh precisionCharacter and pattern recognitionCumulative costComputer science

The invention provides a method and a system for measuring ocean moving target track similarity, and belongs to the technical field of ocean moving target track detection. The method comprises: receiving historical track data; preprocessing the historical track data to form first track data; randomly selecting one piece of unselected second track data from a preset database, the second track datacomprising n vectors; forming a plurality of sub-sequences according to the selected second track data; for each sub-sequence, calculating the Euclidean distance between the vector of the sub-sequenceand the vector of the first track data to form a cost matrix; calculating a cumulative cost matrix according to the cost matrix; obtaining DTW distances between corresponding sub-sequences of the first track data and the second track data according to a calculation result of the cumulative cost matrix; whether the DTW distance is smaller than a preset distance threshold value or not is judged; and under the condition that it is judged that the DTW distance is smaller than a distance threshold value, the calculated DTW distance and the corresponding cumulative cost matrix are associated and stored.

Owner:HEFEI UNIV OF TECH

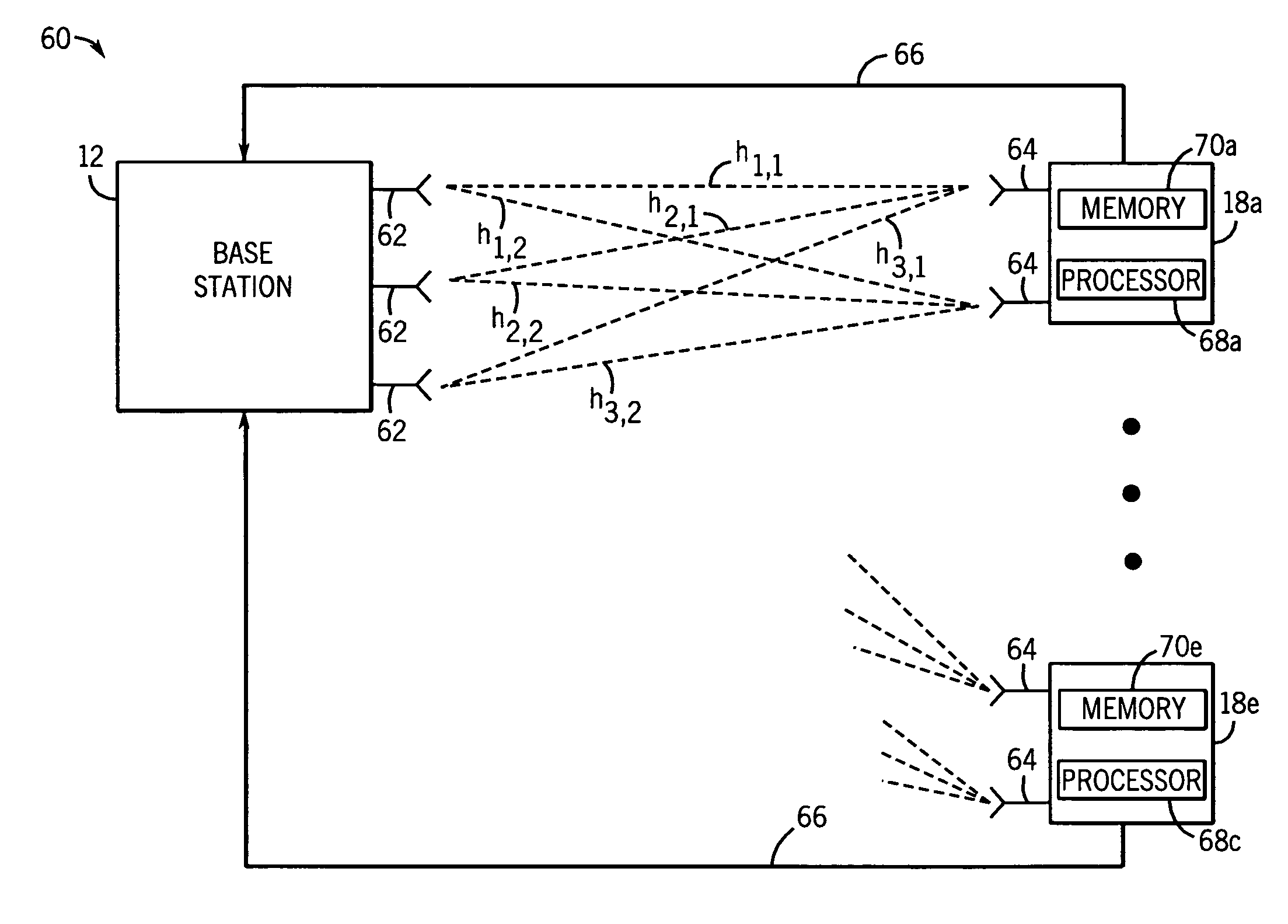

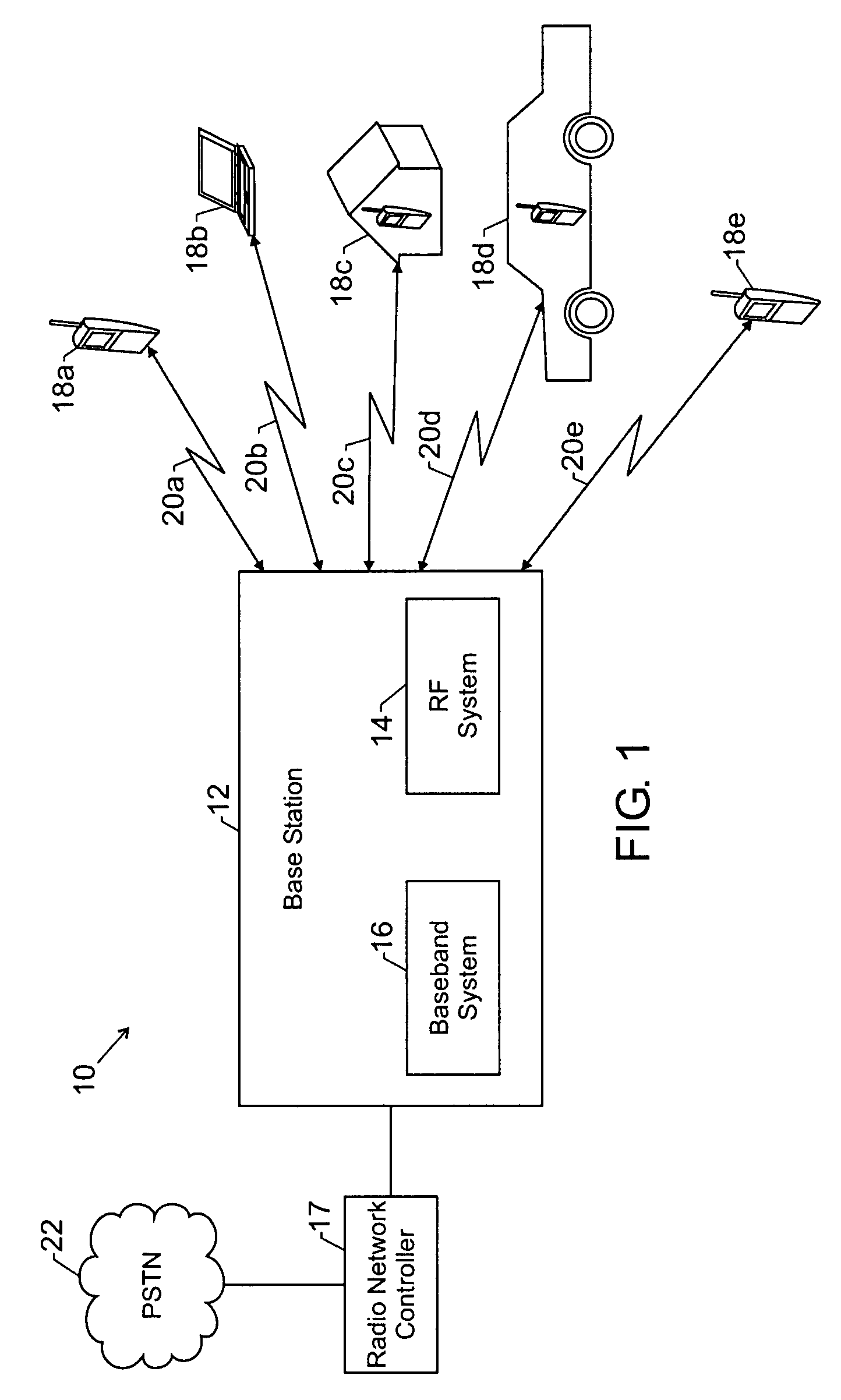

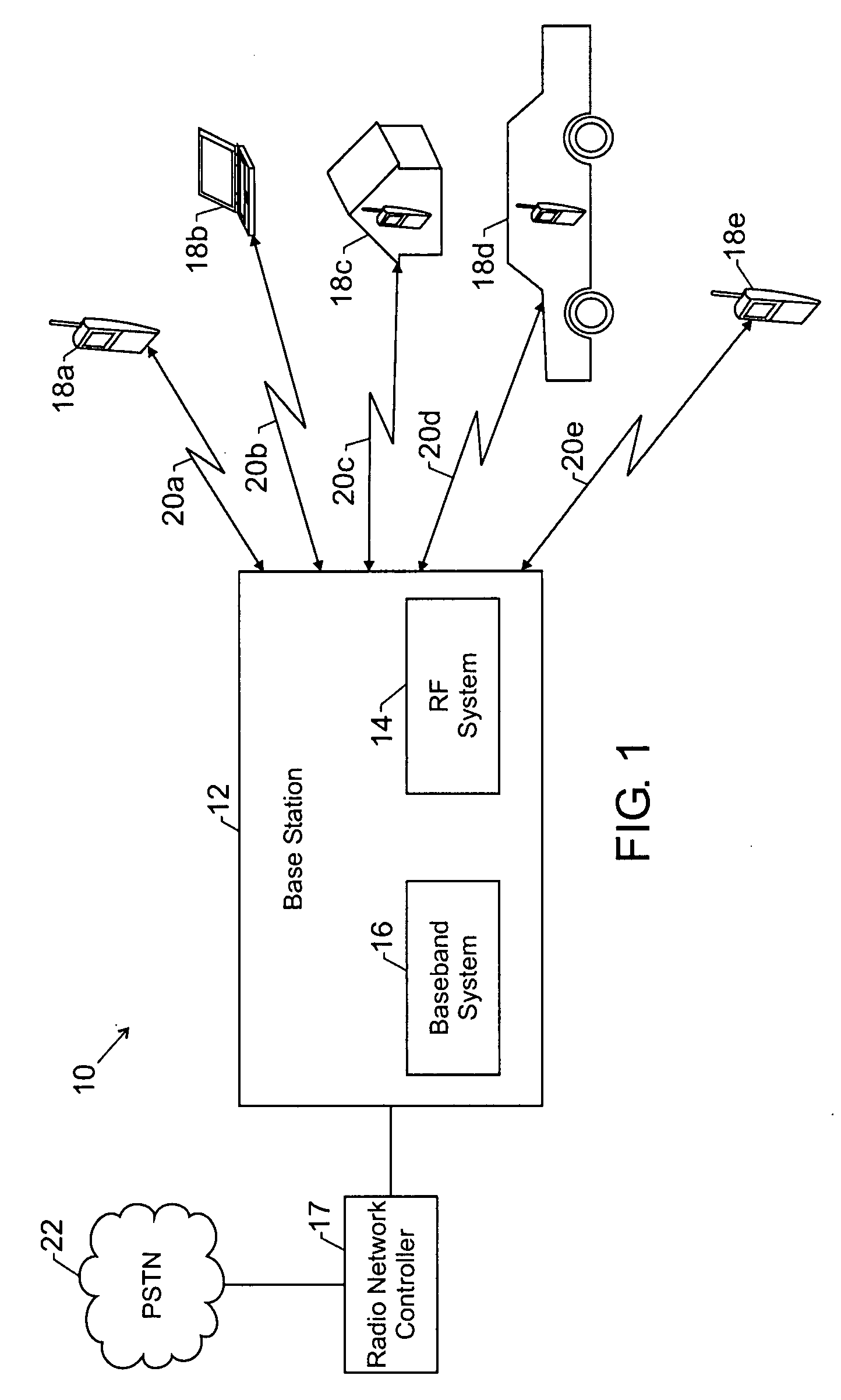

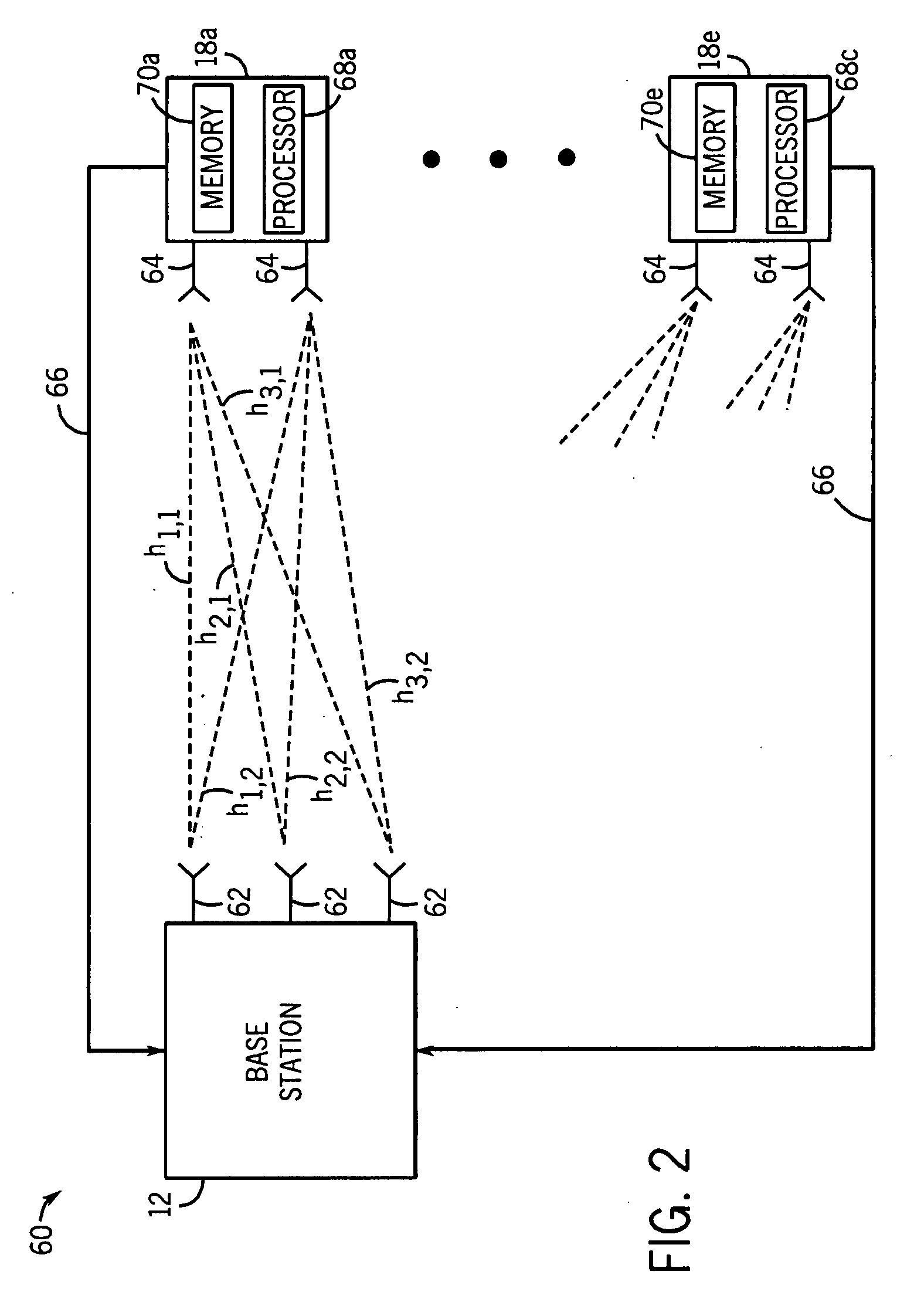

Providing feedback in a MIMO system

ActiveUS8270515B2Diversity/multi-antenna systemsSecret communicationCommunications systemEngineering

There is provided a system and method of operating a multiple-input multiple-output (MIMO) receiver with N antennas in a wireless communication system. The method includes measuring N vectors, each vector defining channel transfer coefficients between M antennas of a transmitter and a corresponding antenna of the receiver. Additionally, a vector in a linear space generated by the N measured vectors is selected and quantized values of less than M components of the selected vector are fed back to the transmitter.

Owner:ALCATEL LUCENT SAS

Providing feedback in a MIMO system

ActiveUS20090067530A1Diversity/multi-antenna systemsSecret communicationCommunications systemMultiple input

There is provided a system and method of operating a multiple-input multiple-output (MIMO) receiver with N antennas in a wireless communication system. The method includes measuring N vectors, each vector defining channel transfer coefficients between M antennas of a transmitter and a corresponding antenna of the receiver. Additionally, a vector in a linear space generated by the N measured vectors is selected and quantized values of less than M components of the selected vector are fed back to the transmitter.

Owner:ALCATEL LUCENT SAS

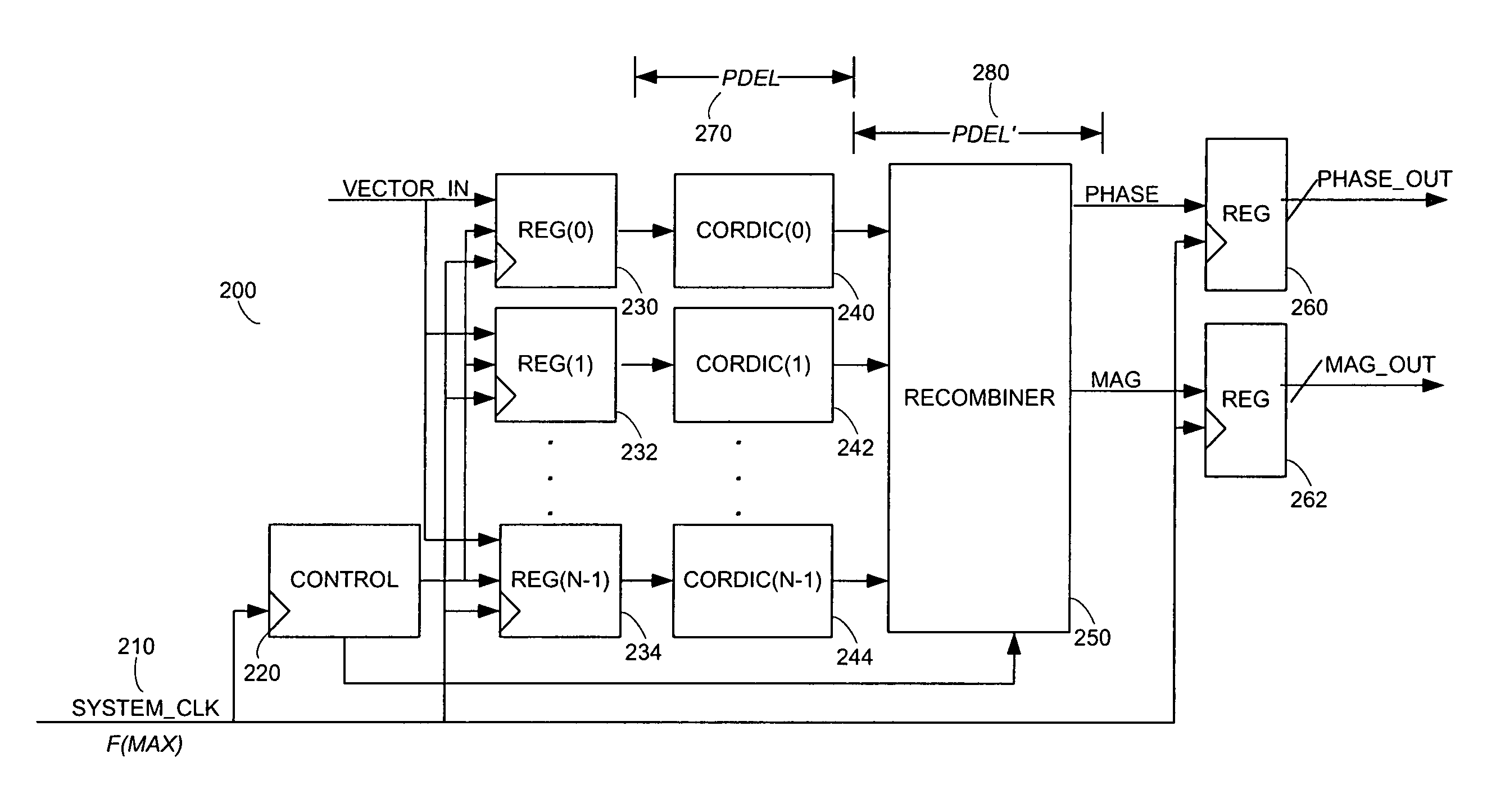

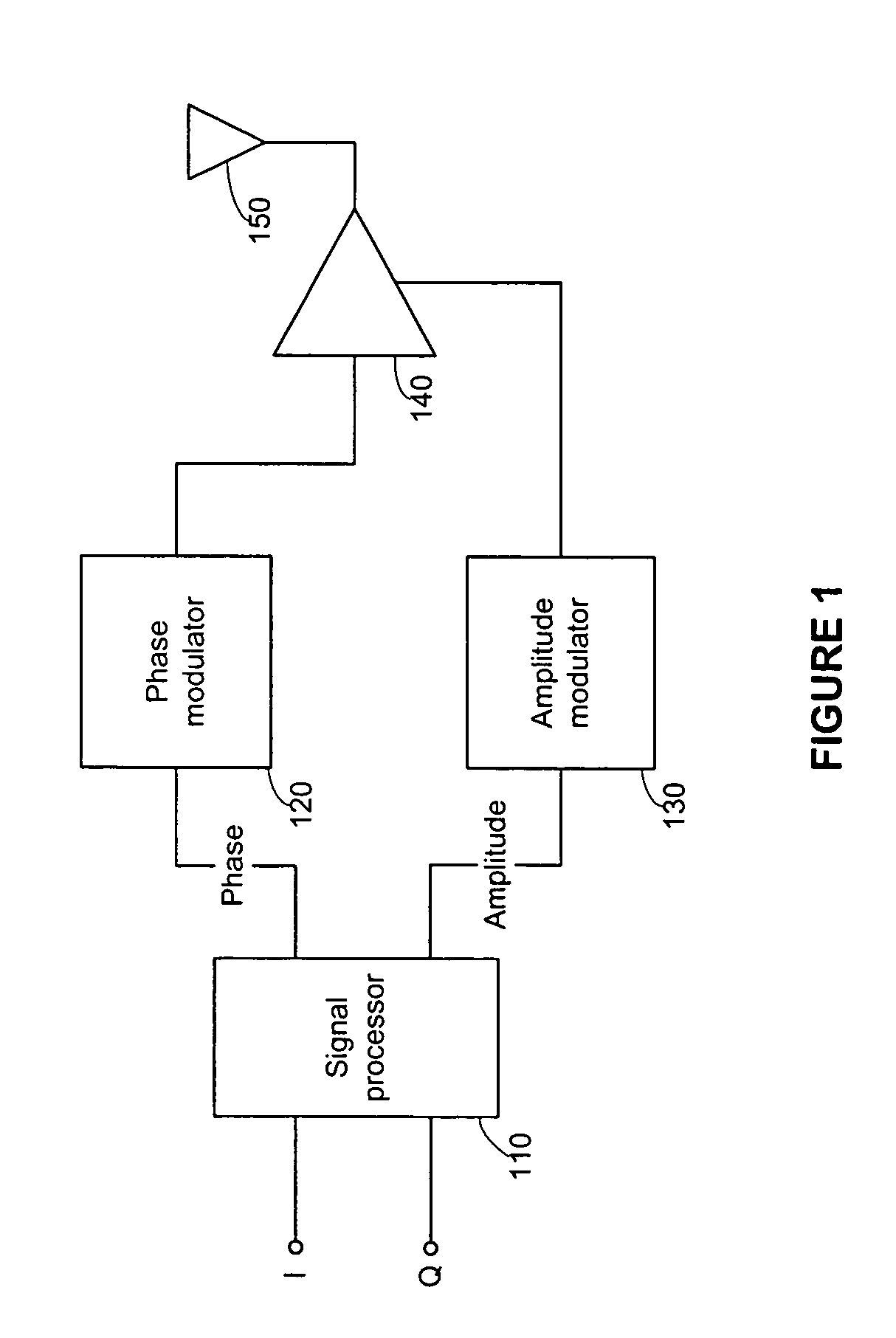

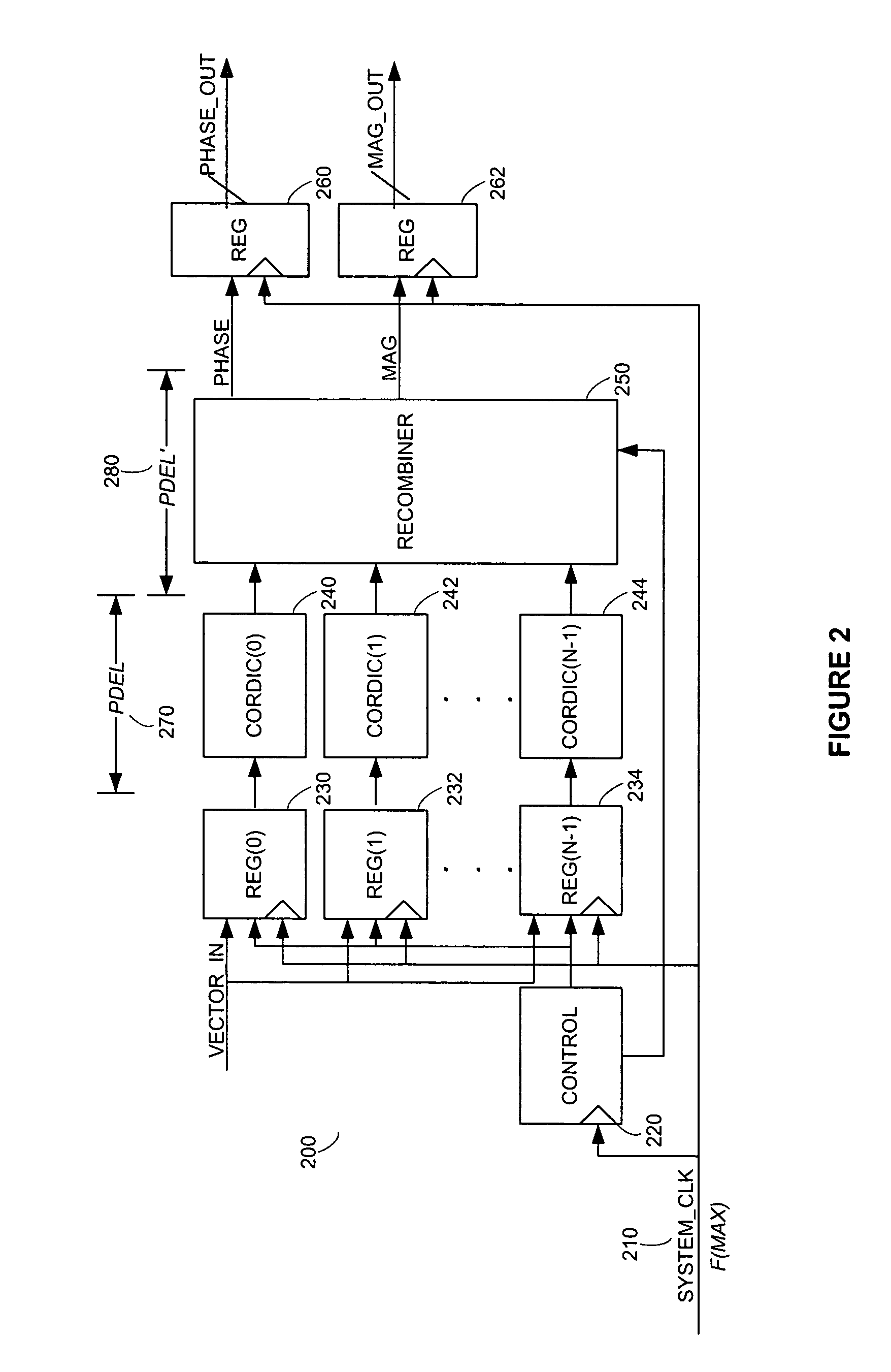

System and method for efficient rectangular to polar signal conversion using cordic algorithm

InactiveUS20070237255A1Modulated-carrier systemsDigital data processing detailsProcessor registerAlgorithm

A system and method is provided for converting an input signal from a sequence of rectangular coordinate pairs to a sequence of polar coordinate pairs. The input signal includes a sequence of input vectors each including a pair of rectangular coordinates. A plurality of N input registers is configured to store an input vector of the input signal. The system includes a plurality of N CORDIC algorithm instances, each in communication with a corresponding one of the N input registers. Each CORDIC algorithm instance is configured to receive the input vector stored in the corresponding input register and to convert the received input vector to a corresponding output vector including a pair of polar coordinates. A recombiner is configured to receive the N output vectors and to recombine at least the N output vectors in sequence to form an output signal.

Owner:PINE VALLEY INVESTMENTS INC

Processing Matrix Vector Multiplication

ActiveUS20190361954A1Improve processing speedSmall sizeInput/output to record carriersOther databases indexingVector elementParallel computing

A size M×N sparse matrix, including zero values, is multiplied with a size N vector, using a processor arrangement. A data storage linked to the processor arrangement stores the matrix in a compressed formal. Zero values are not stored. The data storage stores the vector as vector parts, each of a respective size Ki, 1<Ki<N and i=1 . . . P. A vector part comprises a vector element in common with another vector part. Each vector part is stored in a distinct memory block. Each of a plurality of the non-zero values of a matrix row is associated with a memory block storing an element of the vector having an index corresponding with a respective index of the non-zero value. The processor arrangement multiplies, in parallel, each of the plurality of the non-zero values of the matrix row by the respective vector element having a corresponding index stored in the associated memory block.

Owner:MYRTLE SOFTWARE LTD

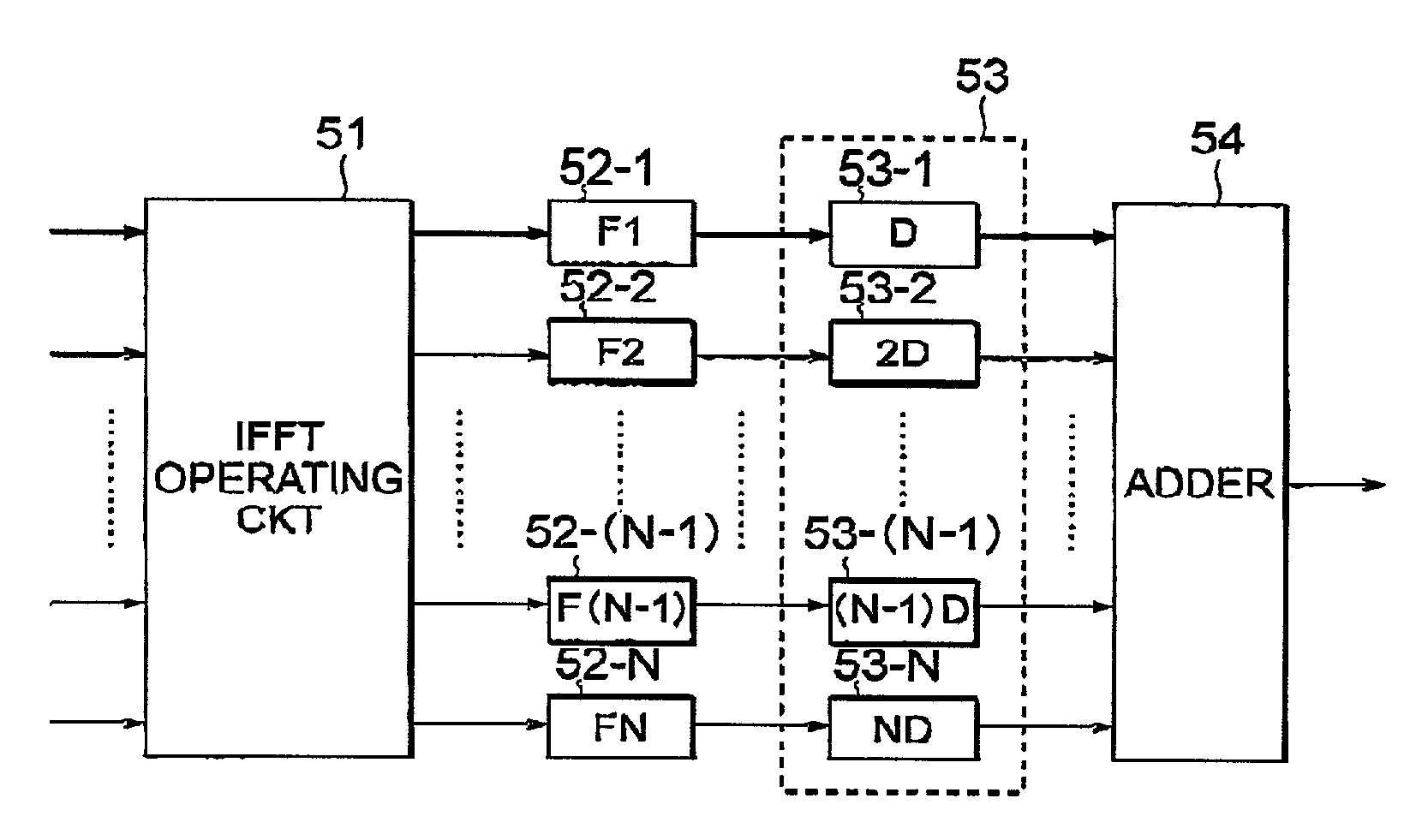

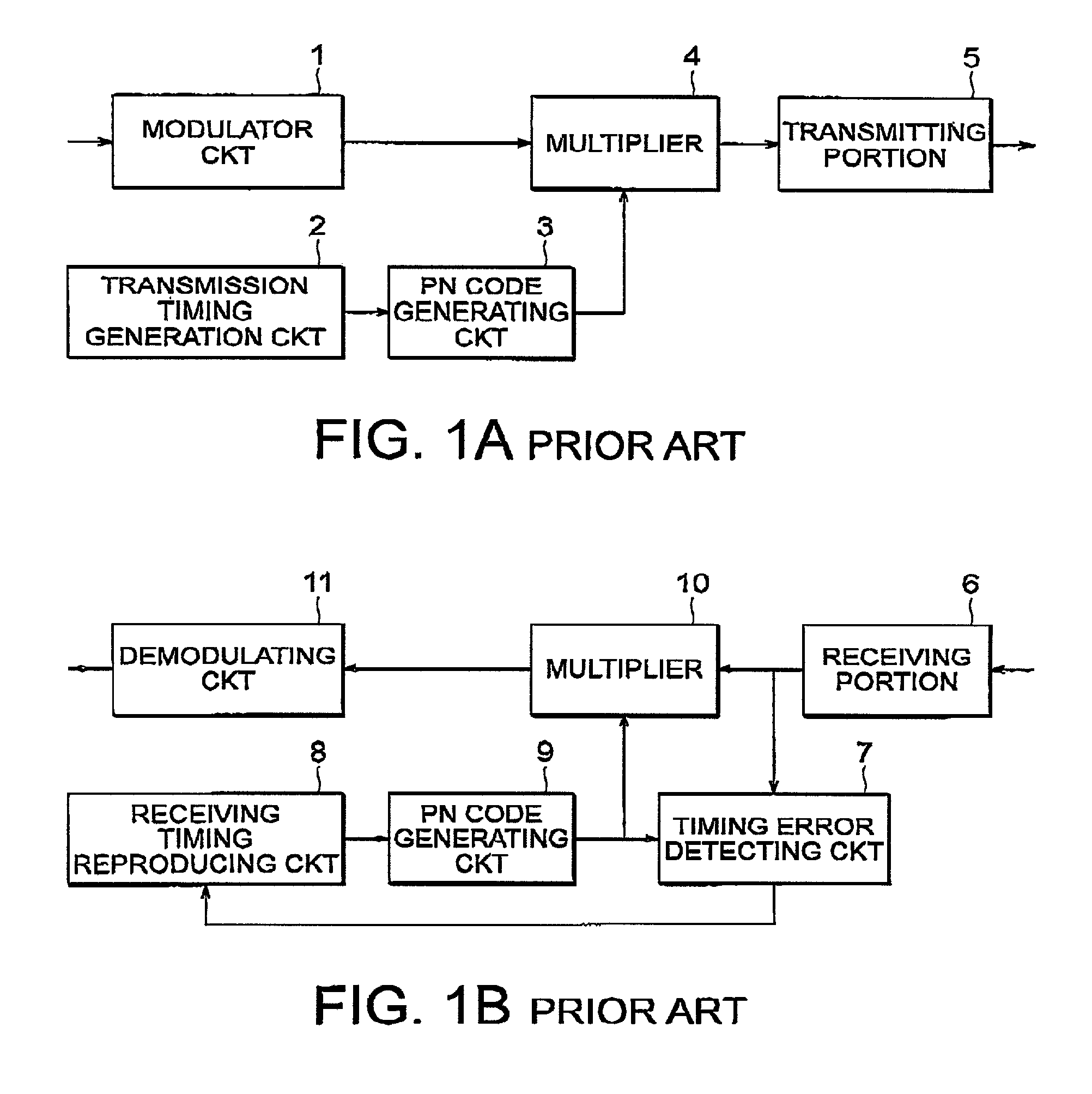

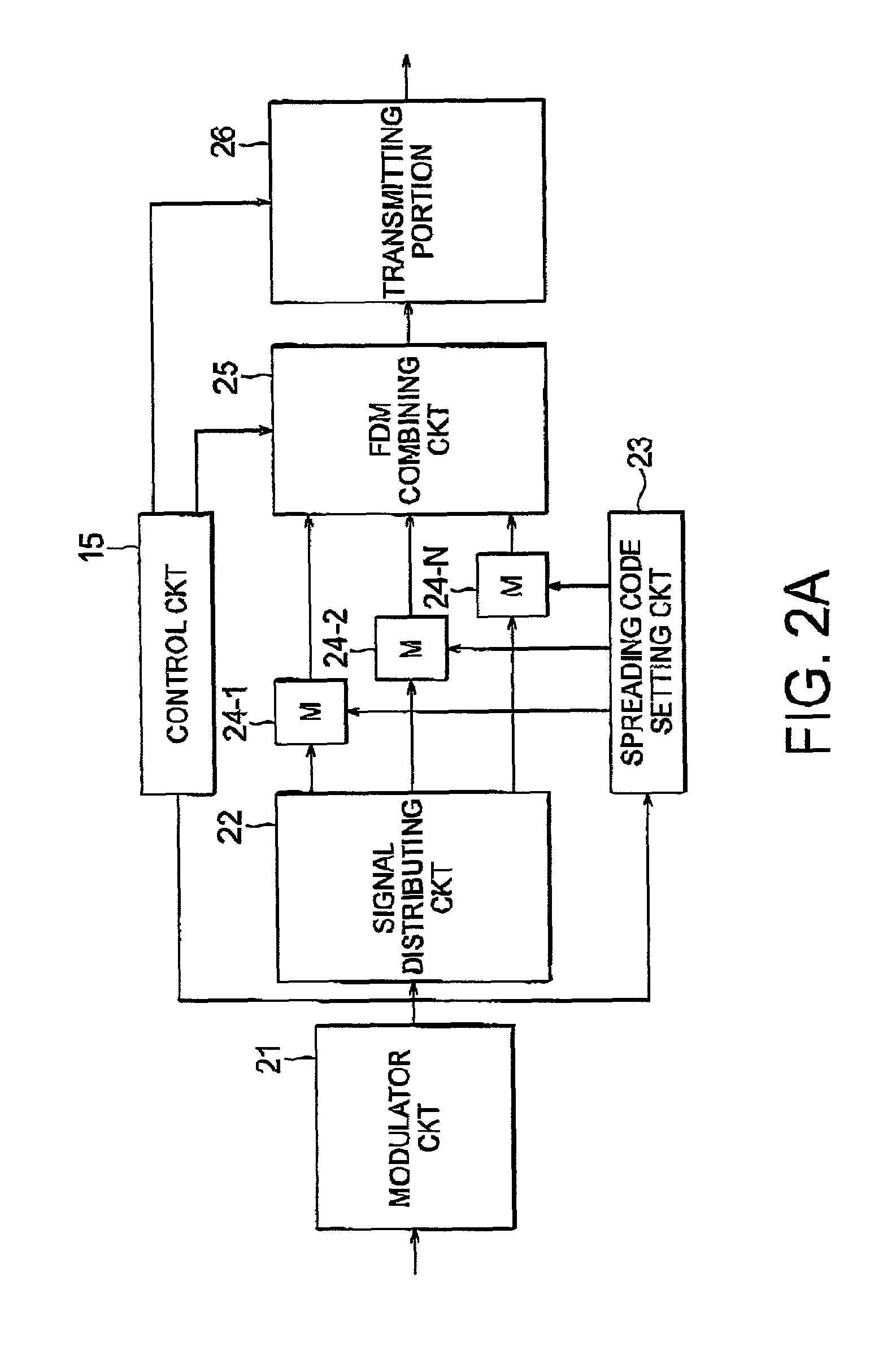

FDM-CDMA transmitting method, FDM-CDMA receiving method, FDM-CDMA transmitting device and FDM-CDMA receiving device

InactiveUS7002945B2Easy to implementPerform inverse spread modulation easily and instantly at the time of receptionTime-division multiplexFrequency-division multiplexComputer scienceN-vector

Owner:NEC CORP

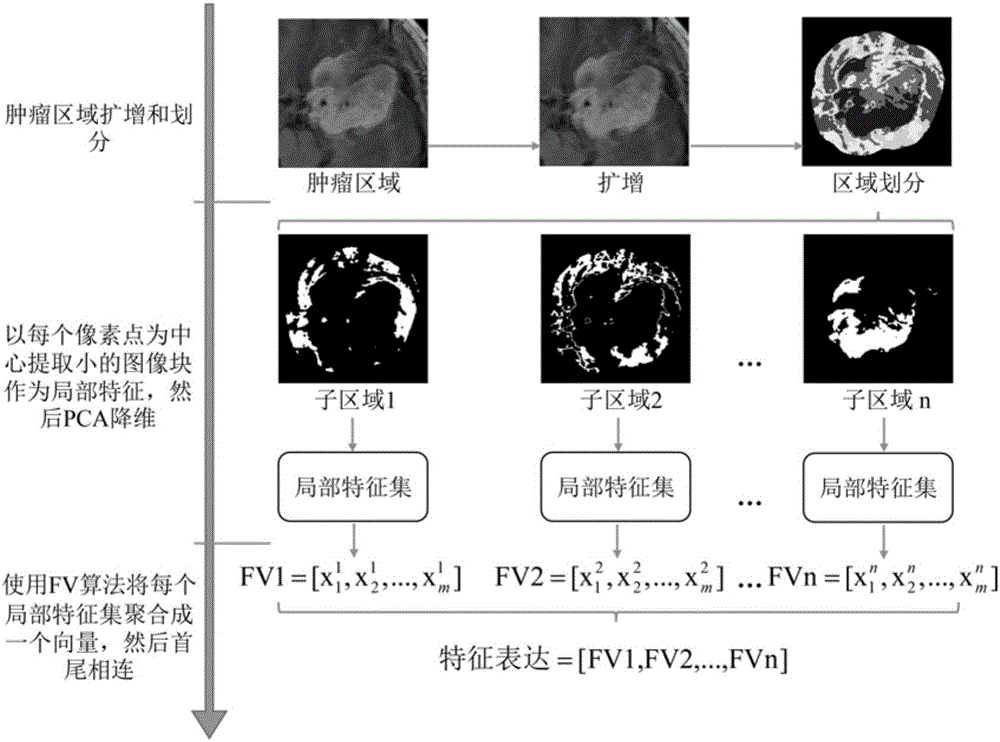

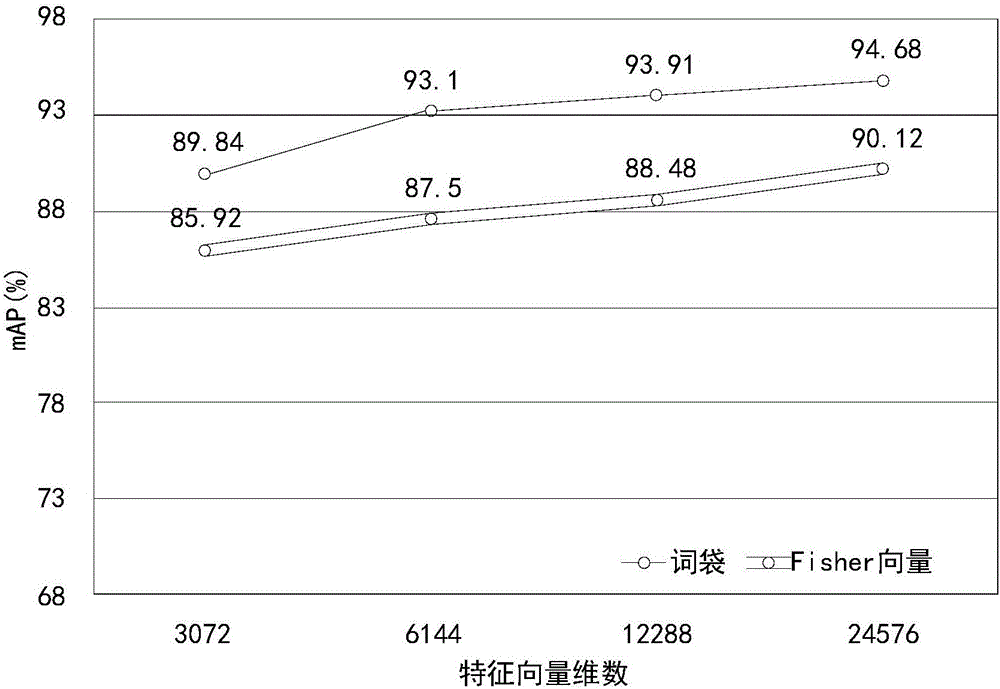

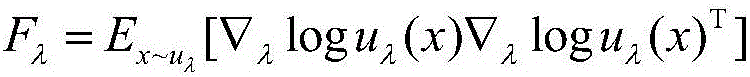

Medical lesion image feature expression method based on region division and Fisher vector

InactiveCN106204545AImprove accuracyStrong discriminationImage enhancementImage analysisAdjuvantFeature set

The invention relates to the technical field of medical lesion image recognition, in particular to a medical lesion image feature expression method based on region division and a Fisher vector. The method uses an expanded lesion region as a region of interest (ROI), divides the ROI into N sub regions according to the gray values of all pixels in the ROI; in each sub region, extracts small image blocks as local feature descriptors; aggregates the local feature set of each sub region into a vector by using a Fisher vector (FV) algorithm, and then connects the obtained N vectors end to end to obtain the feature expression of a medical lesion image. The feature expression method of the present invention utilizes the region information and space position information around the lesion, and uses the FV algorithm which is more effective than a conventional bag-of-word model to make the constructed feature expression more discriminative, thereby contributing to improving the accuracy of clinical adjuvant diagnosis.

Owner:SOUTHERN MEDICAL UNIVERSITY

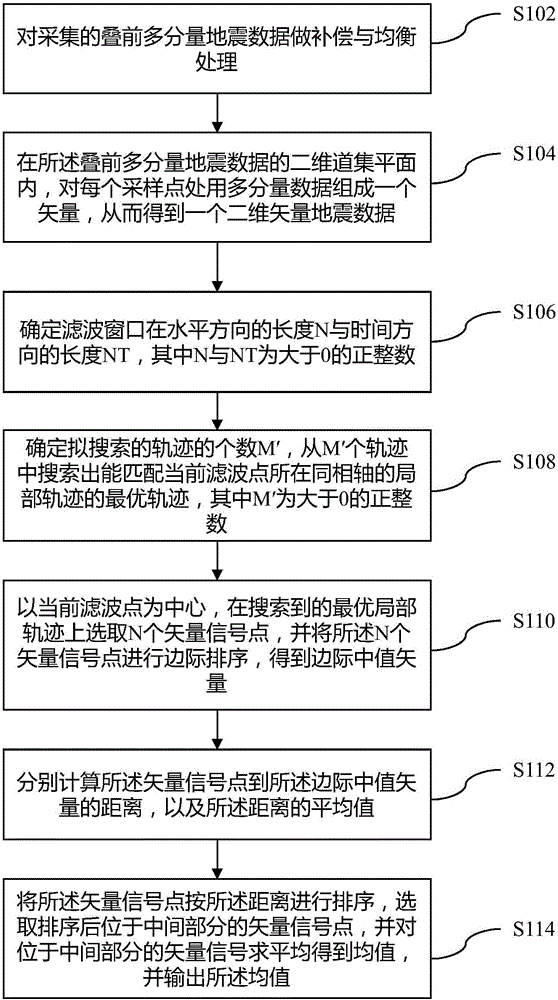

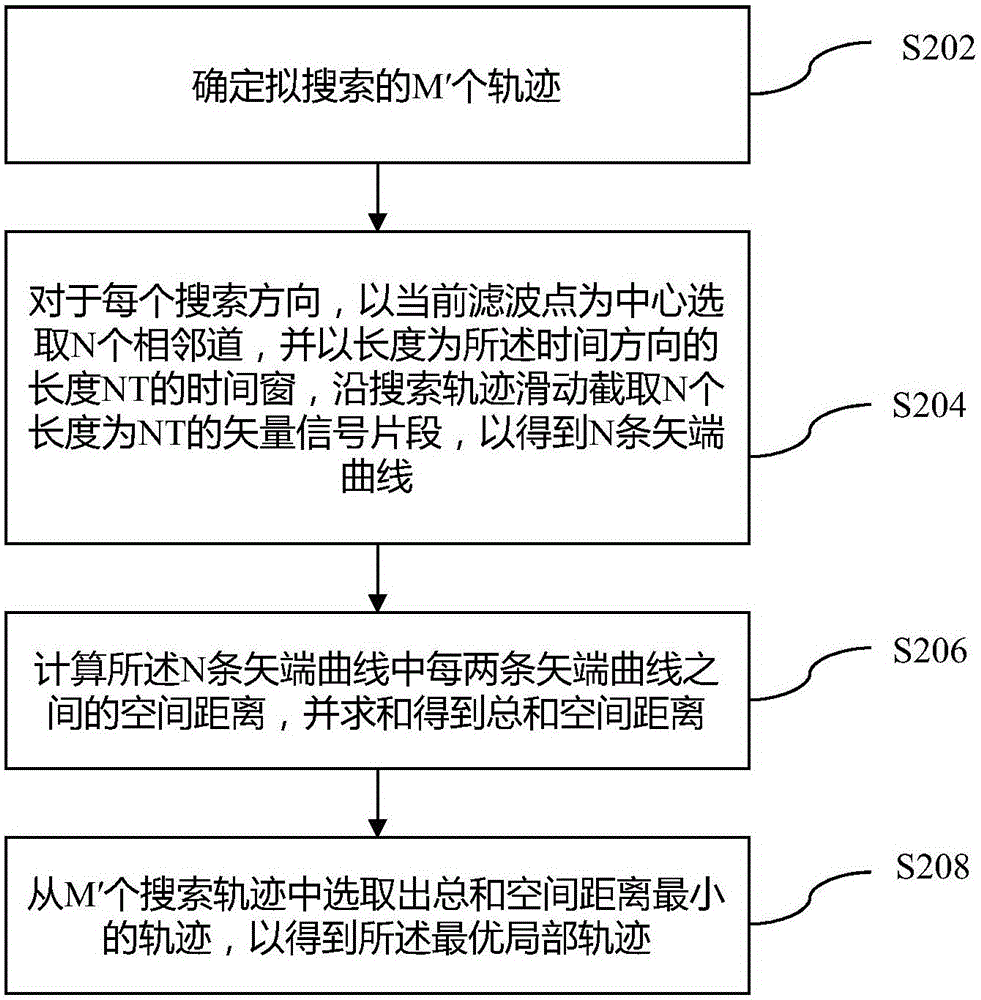

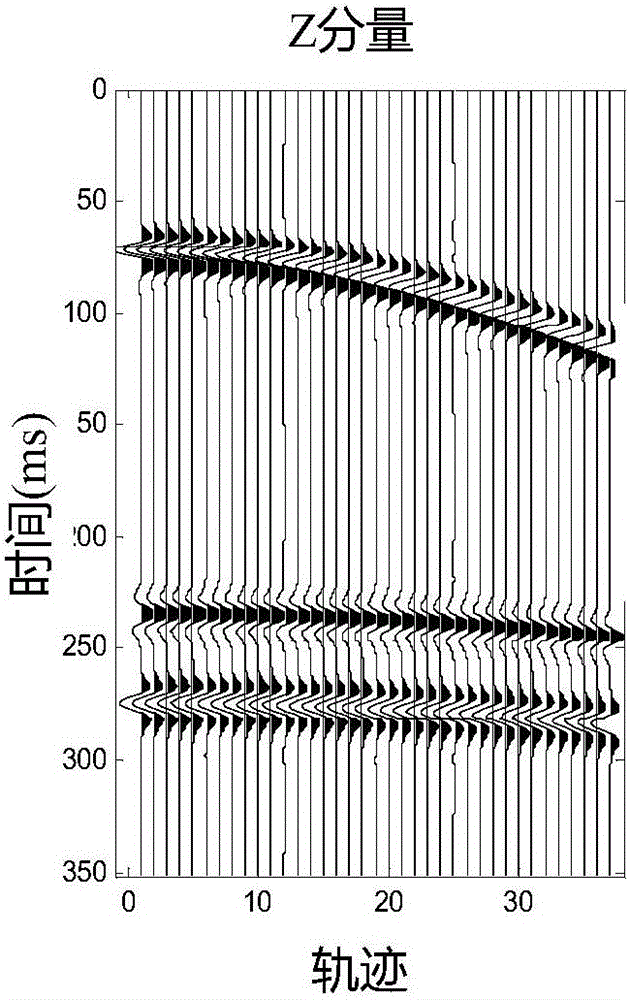

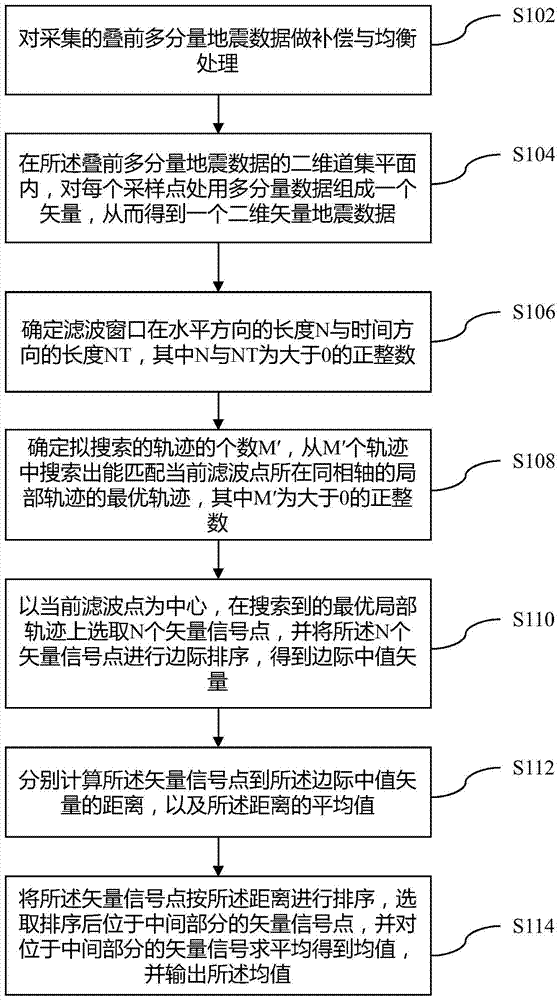

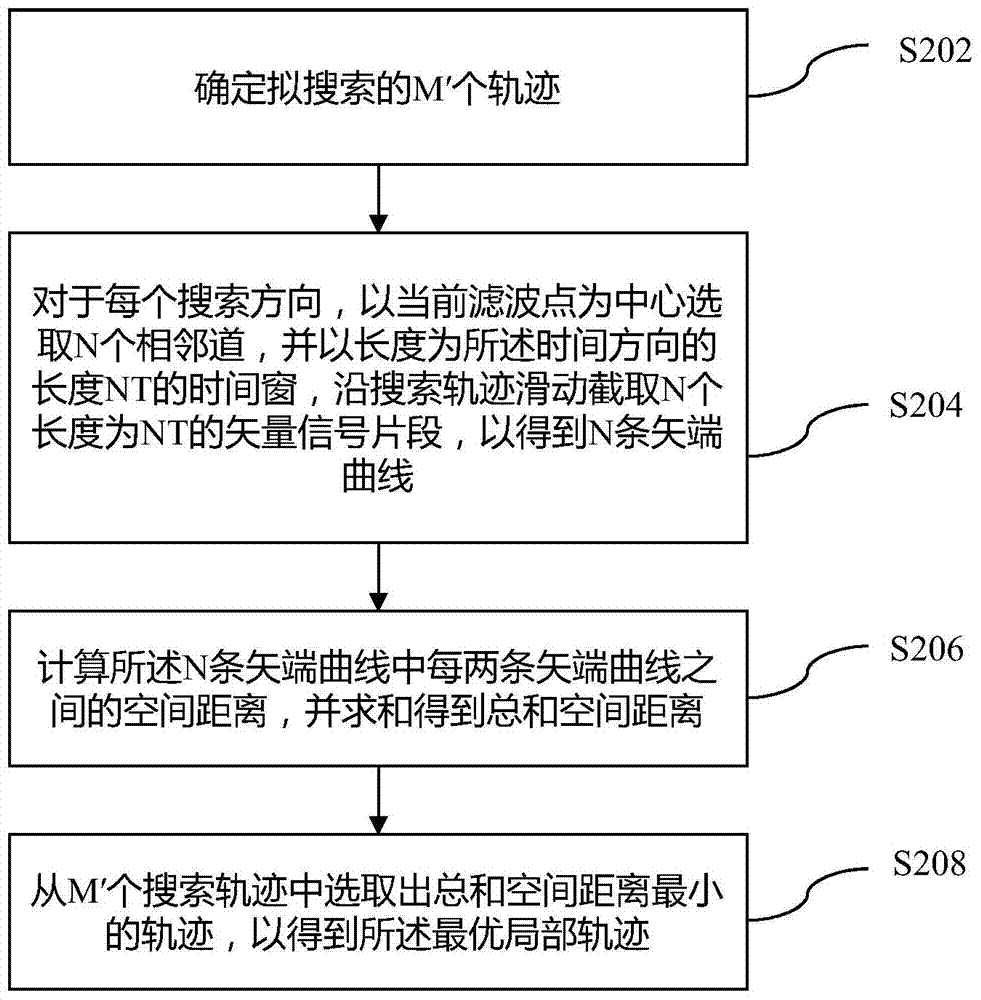

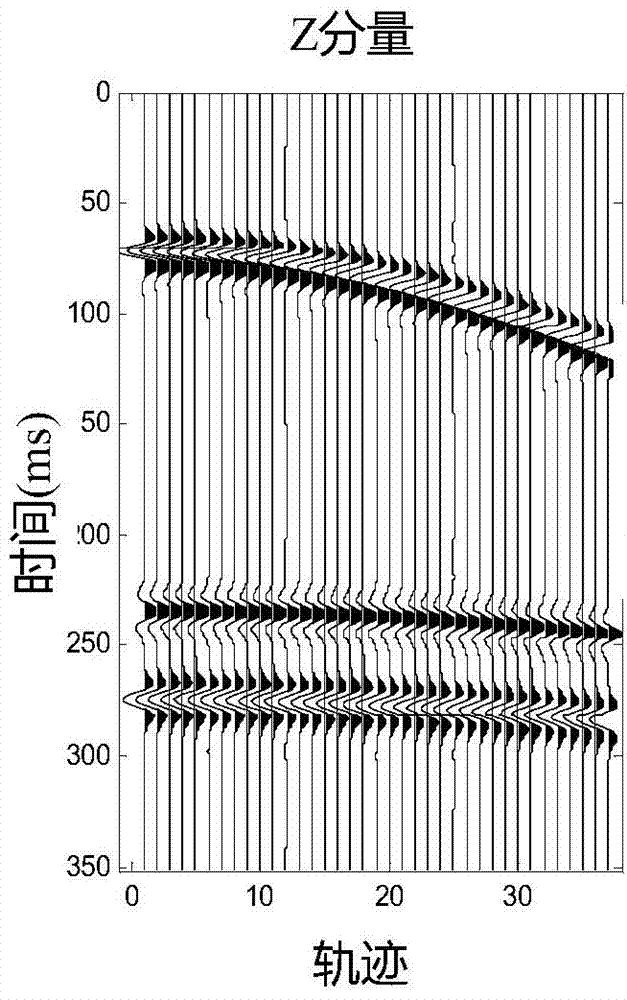

Multi-component earthquake data vector mean value filtering method

ActiveCN105093327AKeep special vector features undistortedFix damageSeismic signal processingLocal optimumRandom noise

The invention discloses a multi-component earthquake data vector mean value filtering method, comprising steps of processing the multi-component earthquake data before superstition, using multi-component data on each sampling point to constitute a vector, determining the length N of a filtering window on a horizontal direction and the length on the time direction, searching the local optimal track of the current filtering point on a same-phase axis through the distance between the vectorend curves of the adjacent channel vector data, taking the current filtering point as a center, choosing N vector signal points on the optimal local tracks, performing boundary sequencing on the N vector signals to obtain a boundary mid-value vector, calculating the distance between the vector signal point and the boundary mid-value and the mean value, choosing the vector signal point which is positioned the in the middle portion after sequencing, and performing averaging on the vector signals positioned in the middle to obtain the average value. The invention solves the problem that the prior art is likely to damage the vector relation between the multi-component earthquake components when suppressing the random noise.

Owner:INST OF GEOCHEM CHINESE ACADEMY OF SCI

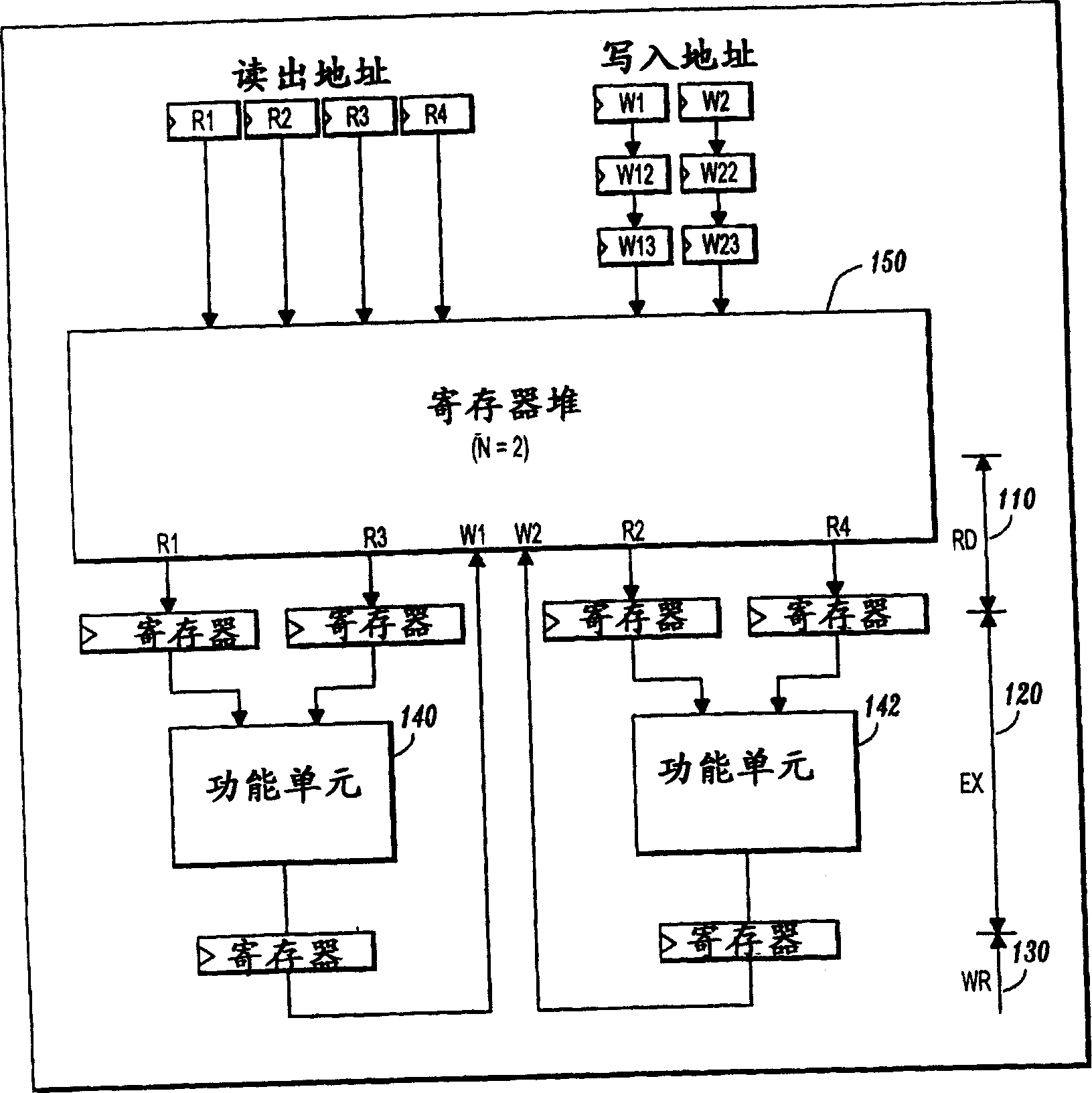

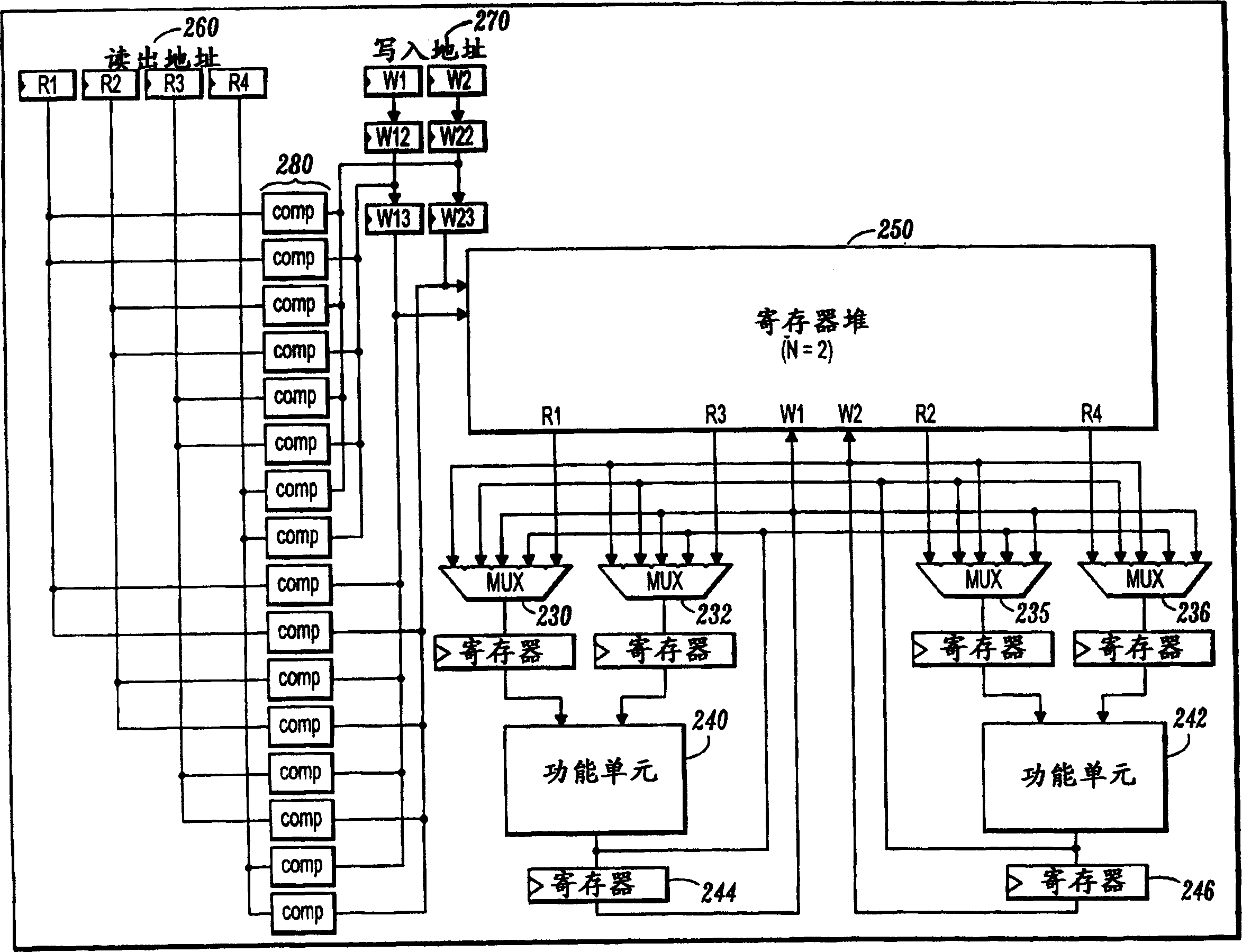

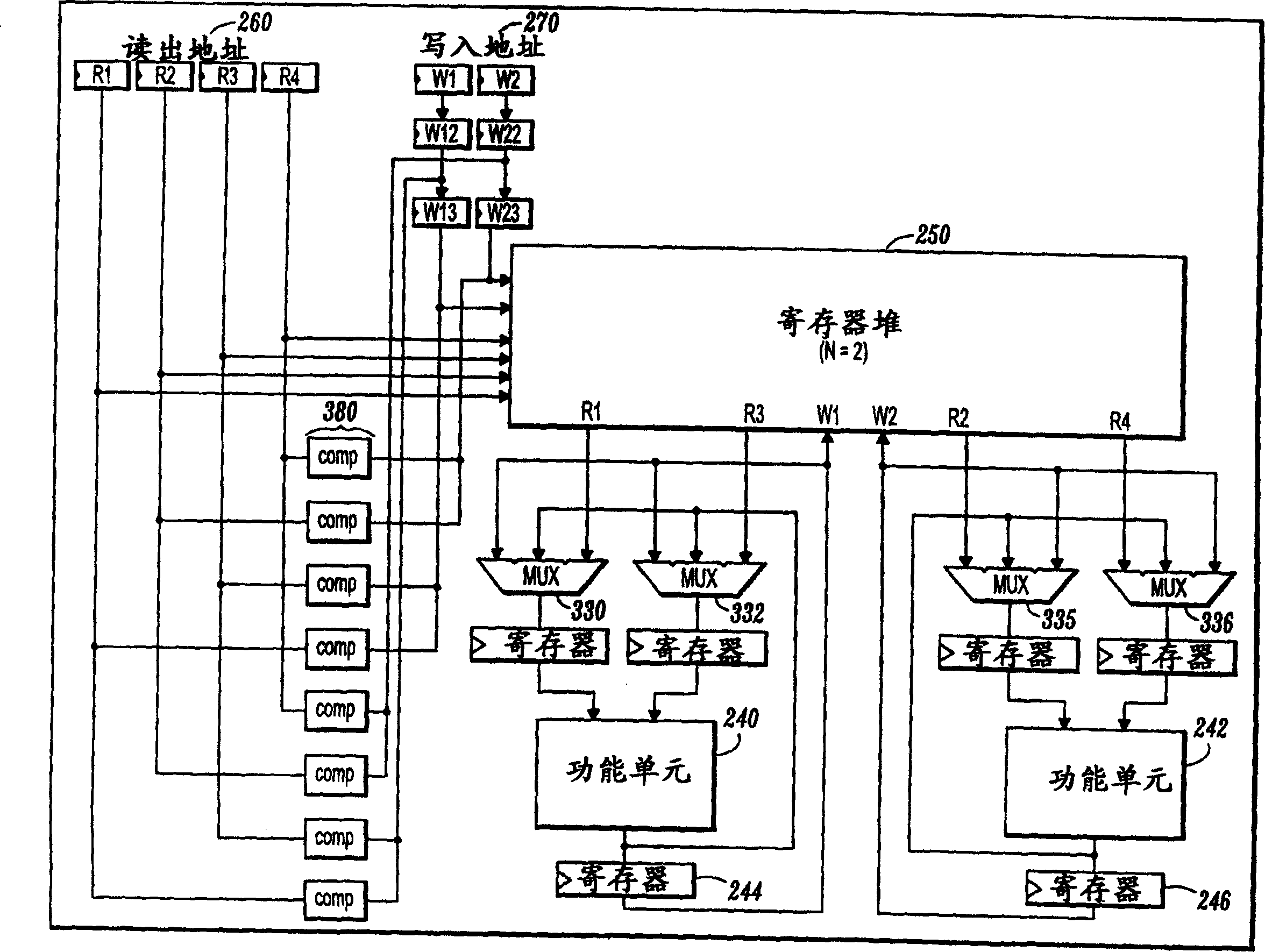

Method of selecting by pass of multiport register pile and equipment

InactiveCN1493976AConcurrent instruction executionArchitecture with multiple processing unitsProcessor registerMulti port

A multi-port register file may be selectively bypassed such that any element in a result vector is bypassed to the same index of an input vector of a succeeding operation when the element is requested in the succeeding operation in the same index as it was generated. Alternatively, the results to be placed in a register file may be bypassed to a succeeding operation when the N elements that dynamically compose a vector are requested as inputs to the next operation exactly in the same order as they were generated. That is, for the purposes of bypassing, the N vector elements are treated as a single entity. Similar rules apply for the write-through path.

Owner:IBM CORP

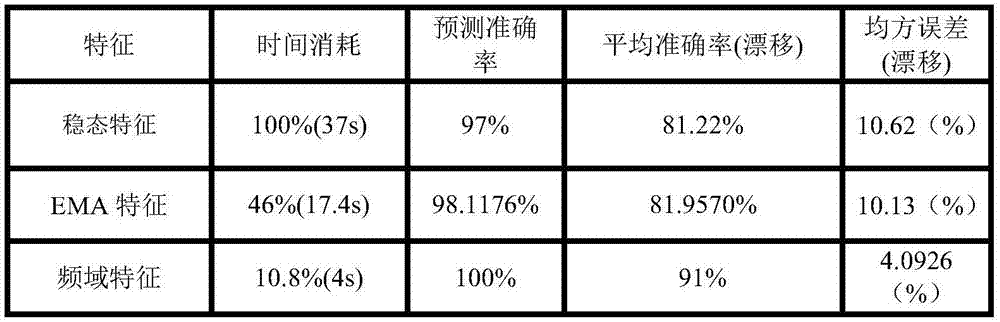

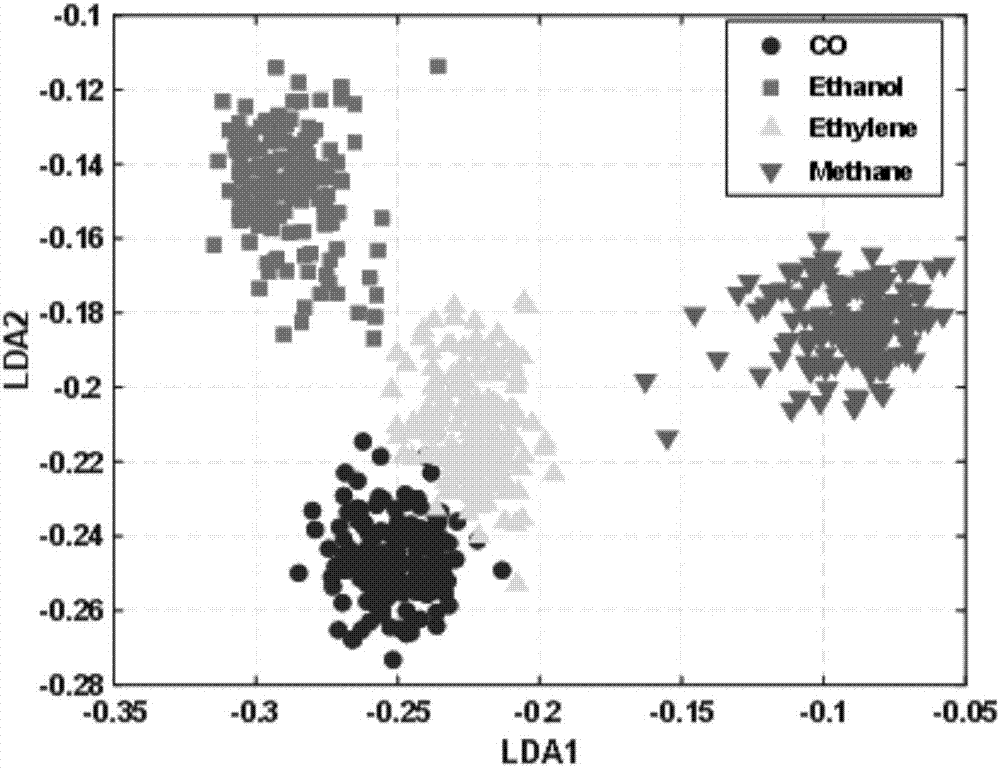

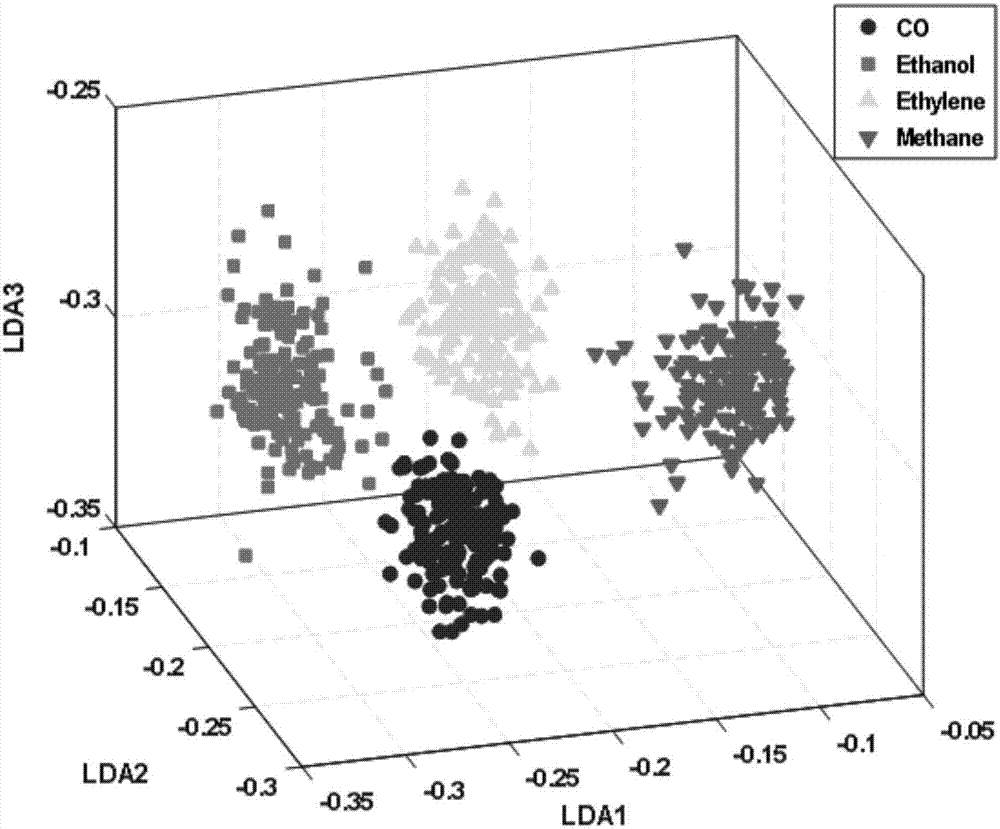

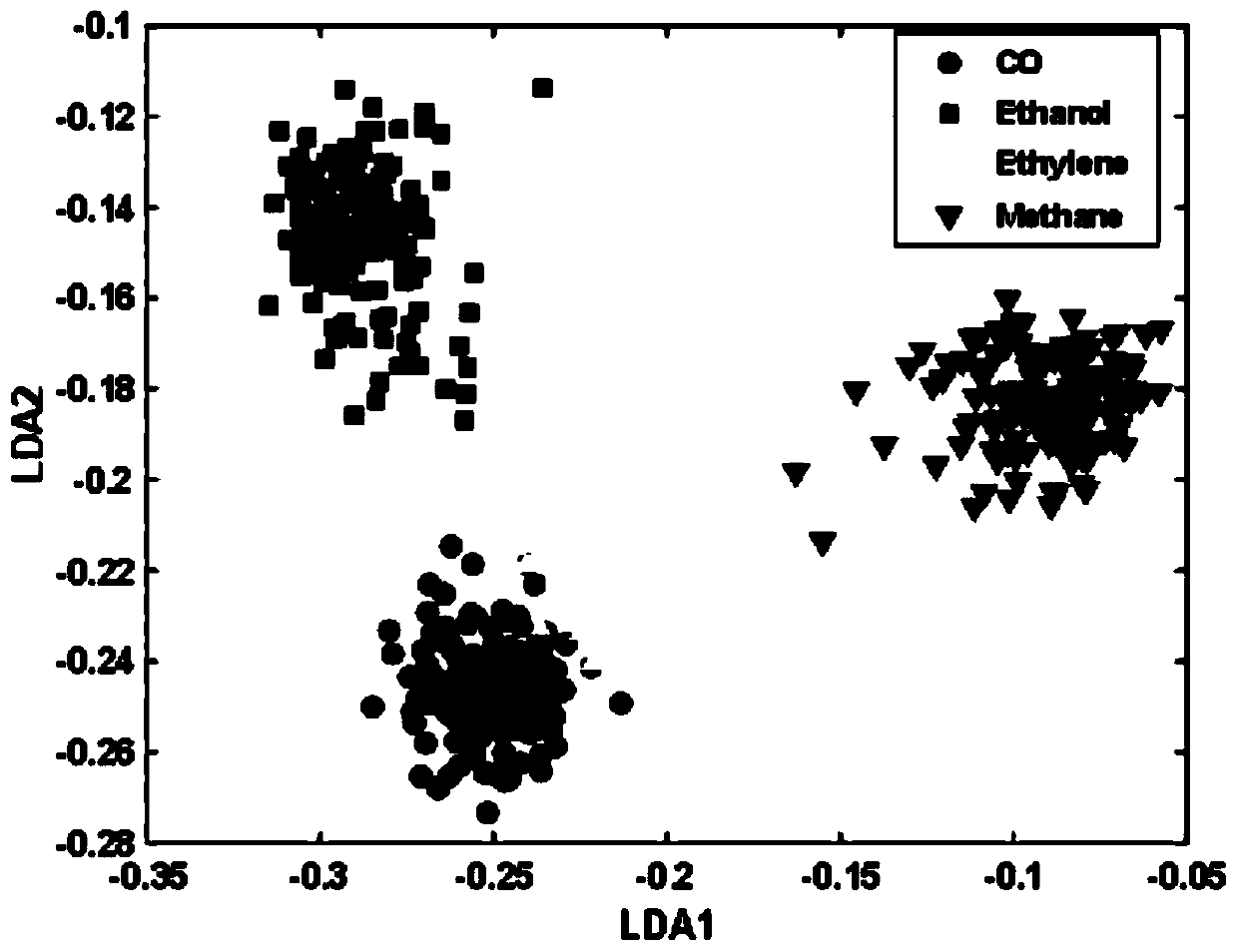

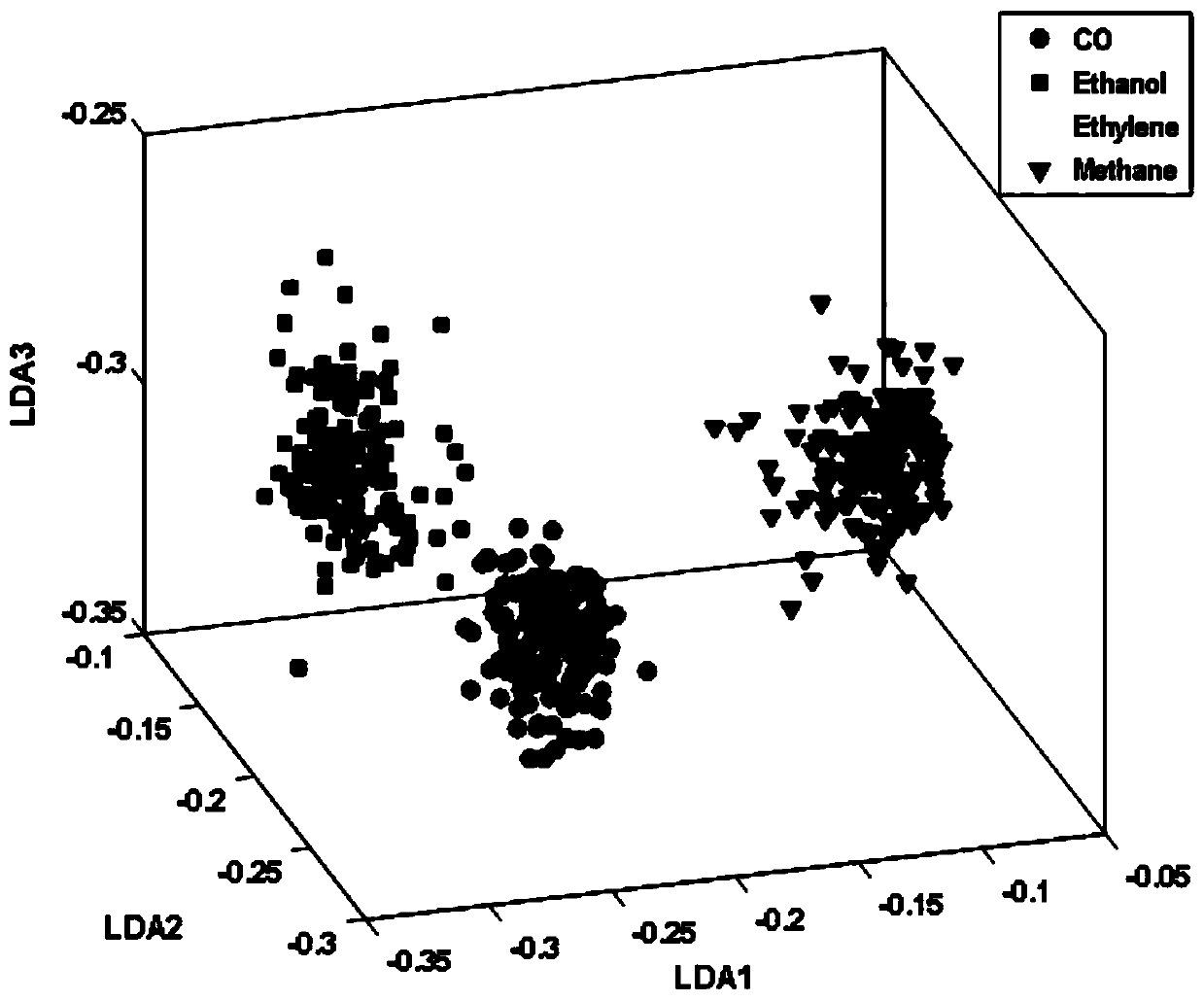

Frequency domain feature extraction based rapid gas identification algorithm

The invention provides a frequency domain feature extraction based rapid gas identification algorithm which is a novel gas identification algorithm. The rapid gas identification algorithm includes that passing gas is subjected to data acquisition and interception through sensors, intercepted data are subjected to Fourier transform to acquire distribution of intercept sequences in a frequency domain, first 20 data values from the 0Hz position are removed to serve as features of the data acquired through single sensors, features of n sensor data are spliced into a 20*n vector according to a certain order, a large number of the vectors are acquired by repeating the previous steps and are given labels of corresponding gas types, the vectors and the labels are mapped to a three-dimensional space by means of an LDA (linear discriminant analysis) algorithm to acquire a mapping matrix, the vectors and labor data acquired through dimensionality reduction are input in an SVM (support vector machine) classifier to perform modeling of the classifier, vectors of the data under the three-dimensional space of the LDA are acquired by multiplying unknown feature vectors with the mapping matrix, and the vectors are input into the established classifier model to perform prediction of the gas types measured currently.

Owner:SHENZHEN UNIV

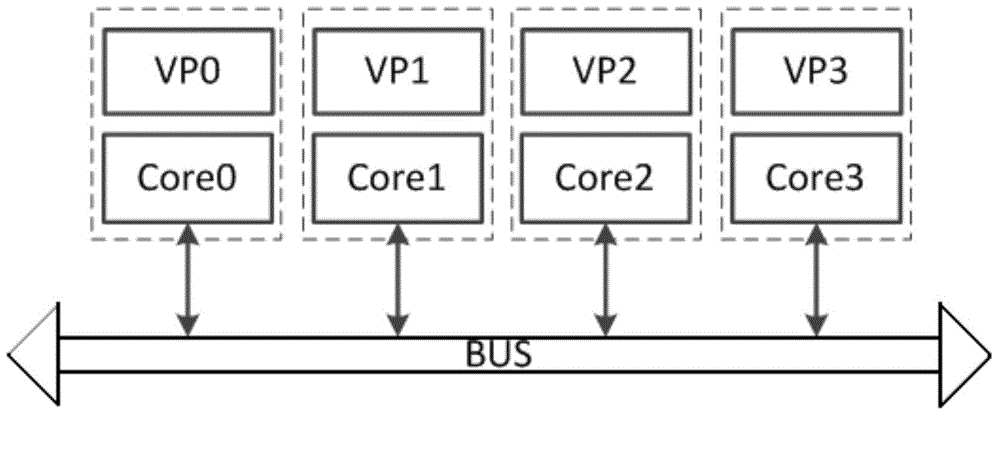

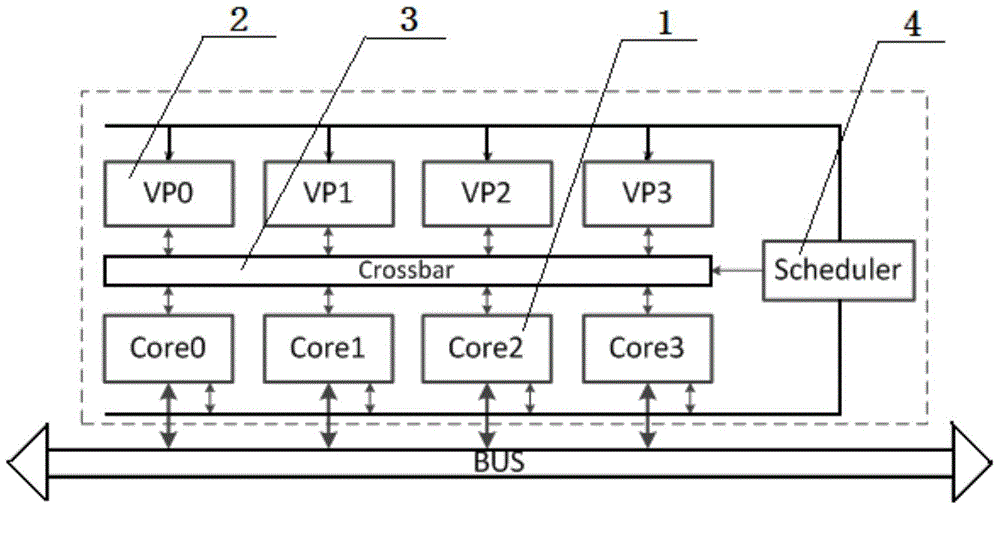

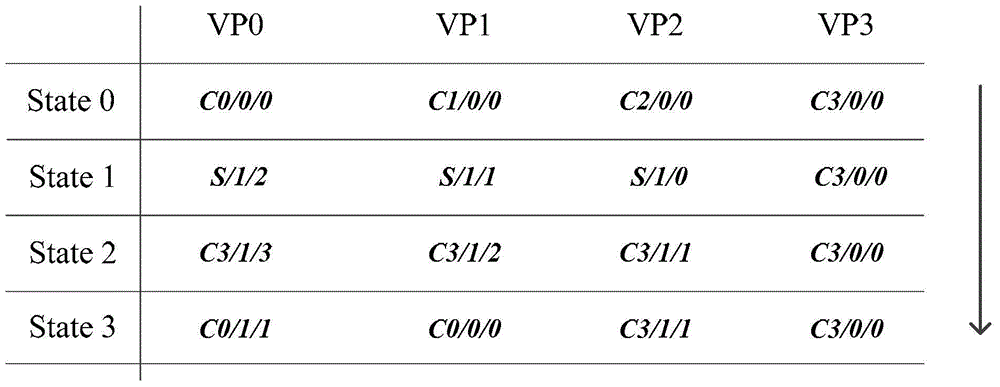

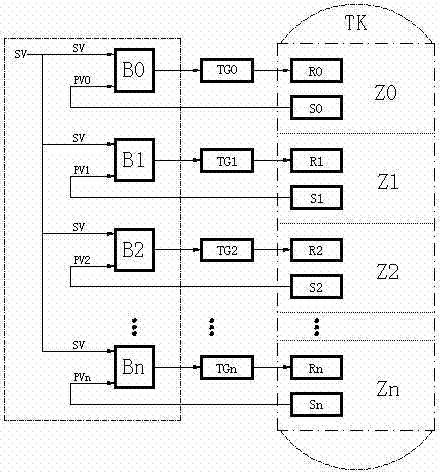

System level model building method of multiple core sharing SIMD coprocessor

InactiveCN104391821AImprove resource utilizationImprove efficiencyArchitecture with multiple processing unitsTask completionCrossbar switch

Disclosed is a system level model building method of a multiple core sharing SIMD coprocessor. The system level model building method of the multiple core sharing SIMD coprocessor comprises an SOC (system on chip), wherein n cores and n vector coprocessors are arranged on the SOC, n is a positive even number, and the n vector coprocessors are connected with the n cores through a crossbar switch. The system level model building method of the multiple core sharing SIMD coprocessor further comprises a dispatcher connected with the n cores, the n vector coprocessors and the crossbar switch, and used to dispatch the vector coprocessors to communicate with the n cores through the crossbar switch, wherein the dispatcher dispatches the vector coprocessor according to current states of the vector coprocessors. The system level model building method of the multiple core sharing SIMD coprocessor significantly improves resource utilization rate of the multiple core sharing SIMD coprocessor through a sharing mechanism, and reduces system power consumption, and furthermore, compared with the prior art, the system level model building method of the multiple core sharing SIMD coprocessor efficiently completes a task under the circumstance that the quantity of resources is fixed.

Owner:TIANJIN UNIV

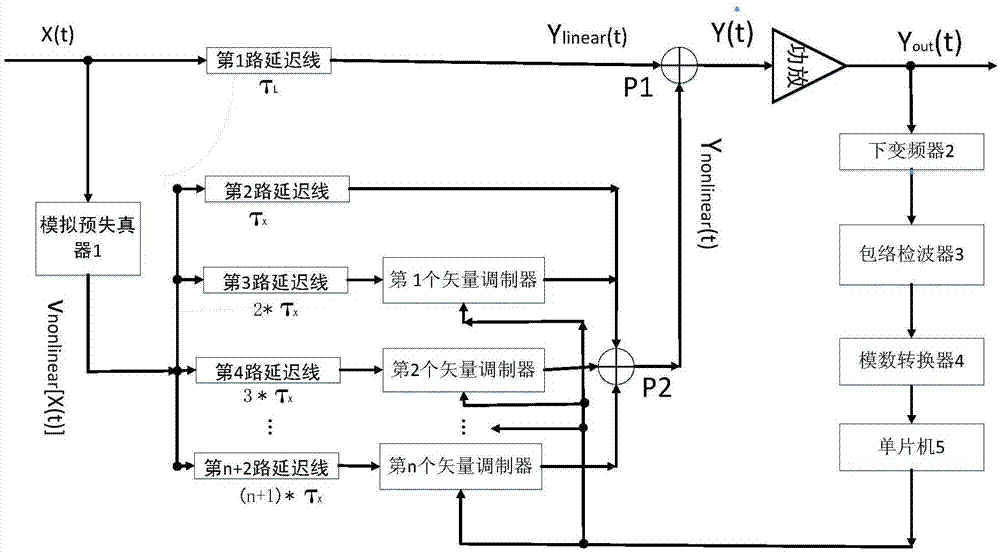

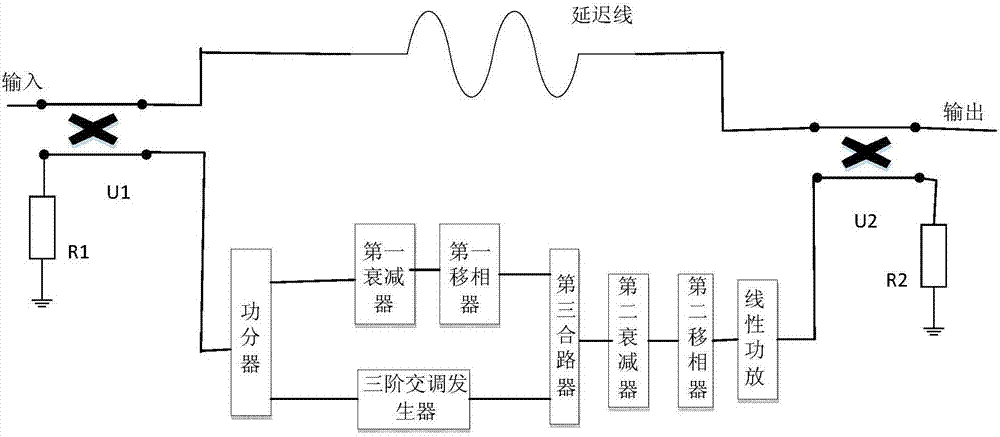

Memory effect compensation-based analog pre-distortion system

ActiveCN107885942ASimple structureLow costCAD circuit designSpecial data processing applicationsMicrocontrollerOptimal control

The invention discloses a memory effect compensation-based analog pre-distortion system. The system comprises an analog pre-distorter, n+2 delay lines, n vector modulators, a first combiner, a secondcombiner, a down converter, an envelope detector, an analog-digital converter and a single-chip microcomputer, wherein the single-chip microcomputer stores reference ranges of nonlinear outputs of multiple power amplifiers and optimal control voltage values of the n vector modulators corresponding to the reference ranges of the nonlinear outputs of the power amplifiers; and after the single-chip microcomputer receives a signal sent by the analog-digital converter, the reference range of the nonlinear output of the power amplifier corresponding to the signal is judged, then the corresponding optimal control voltage values of the n vector modulators are selected according to a judgment result, the control voltages of the n vector modulators are regulated, and the nonlinearity of the power amplifiers is subjected to adaptive pre-distortion regulation. The system has the advantages of simple structure, relatively low cost and high adaptability, can be used for memory effect compensation ofmillimeter wave band power amplifiers, and is relatively high in pre-distortion precision.

Owner:NINGBO UNIV

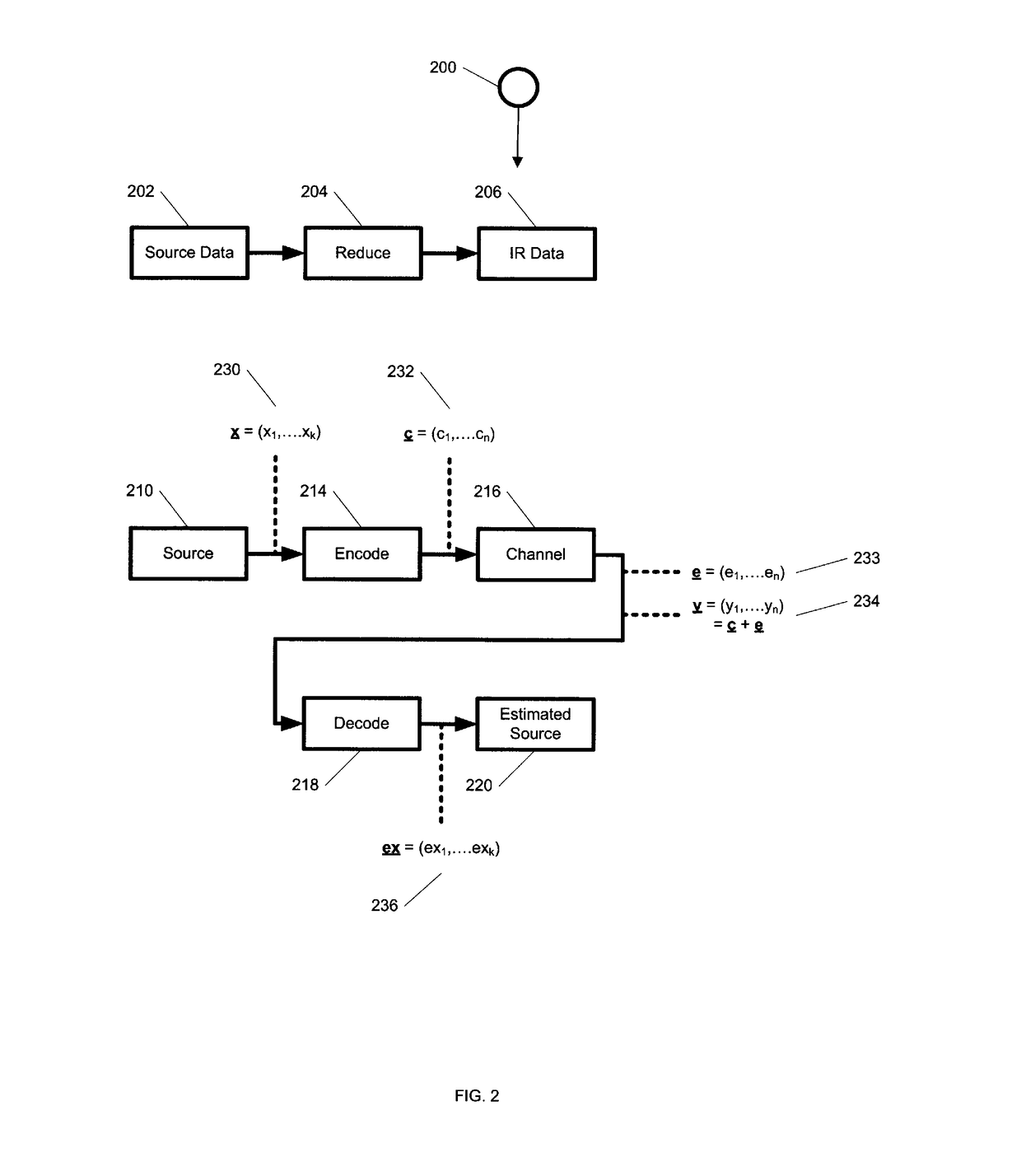

System and method for informational reduction

ActiveUS9948324B1Reduce the amount requiredError correction/detection using multiple parity bitsCode conversionComputer scienceError correcting

Information reduction in data processing environments includes at least one of: one or more Error Correcting Codes that decode n-vectors into k-vectors and utilize said decoding to information-reduce data from a higher dimensional space into a lower dimensional space. The information reduction further provides for a hierarchy of information reduction allowing a variety of information reductions. Transformations are provided to utilize available data space, and data may be transformed using several techniques including windowing functions, filters in the time and frequency domains, or any numeric processing on the data.

Owner:PHILIPS NORTH AMERICA LLC

A Vector Mean Filtering Method for Multicomponent Seismic Data

ActiveCN105093327BKeep vector features undistortedFix damageSeismic signal processingLocal optimumRandom noise

The invention discloses a multi-component earthquake data vector mean value filtering method, comprising steps of processing the multi-component earthquake data before superstition, using multi-component data on each sampling point to constitute a vector, determining the length N of a filtering window on a horizontal direction and the length on the time direction, searching the local optimal track of the current filtering point on a same-phase axis through the distance between the vectorend curves of the adjacent channel vector data, taking the current filtering point as a center, choosing N vector signal points on the optimal local tracks, performing boundary sequencing on the N vector signals to obtain a boundary mid-value vector, calculating the distance between the vector signal point and the boundary mid-value and the mean value, choosing the vector signal point which is positioned the in the middle portion after sequencing, and performing averaging on the vector signals positioned in the middle to obtain the average value. The invention solves the problem that the prior art is likely to damage the vector relation between the multi-component earthquake components when suppressing the random noise.

Owner:INST OF GEOCHEM CHINESE ACADEMY OF SCI

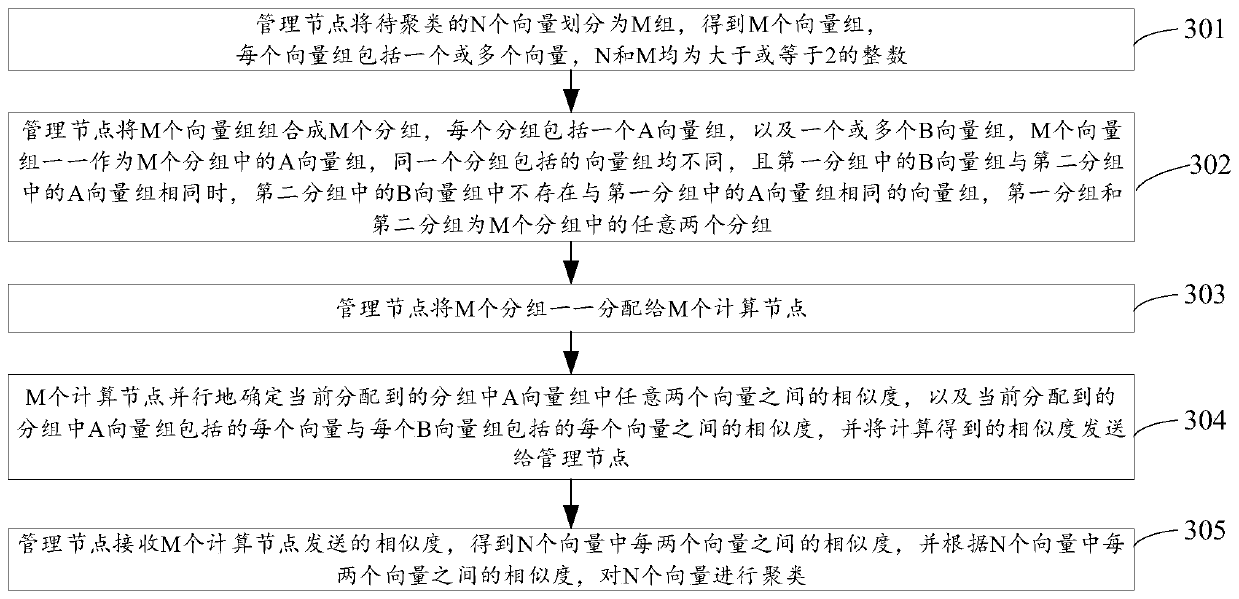

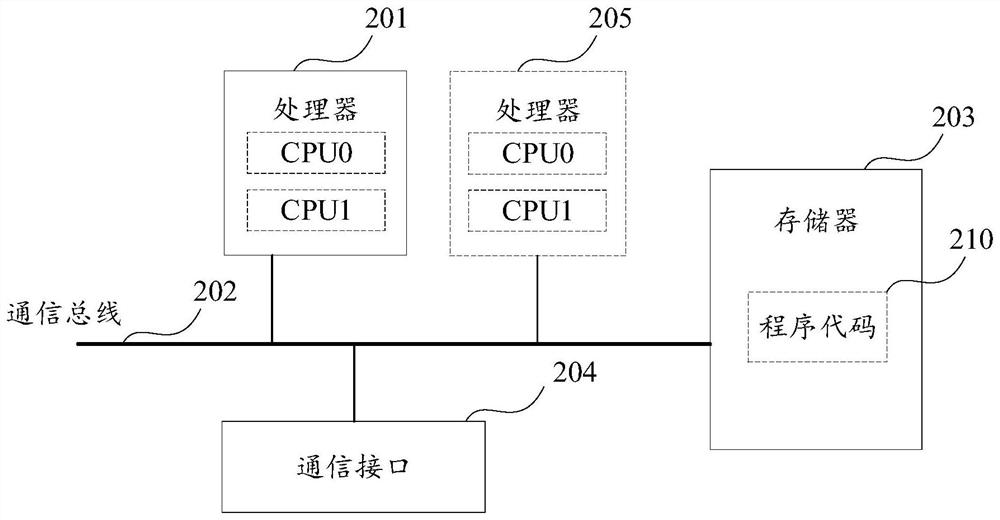

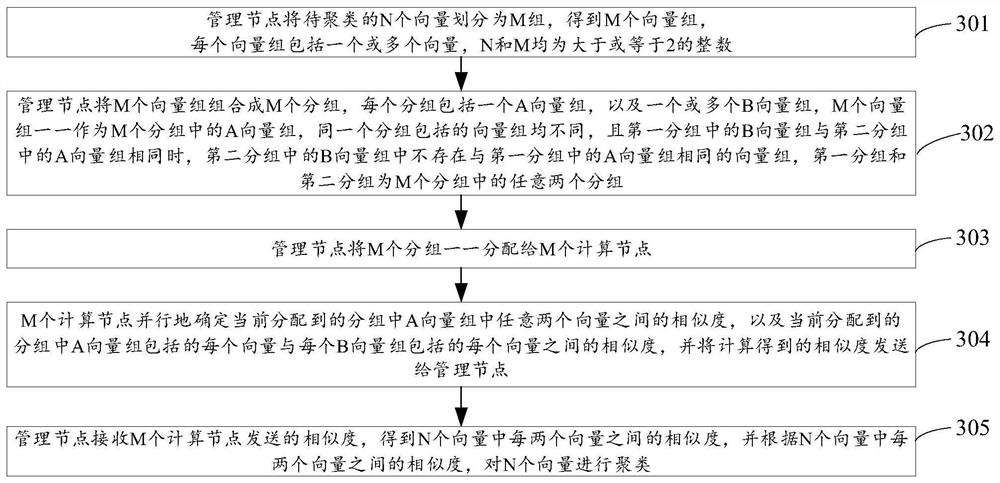

Vector clustering method and device and storage medium

ActiveCN110781247AThere will be no double counting problemsReduce computational overheadRelational databasesSpecial data processing applicationsTwo-vectorAlgorithm

The invention discloses a vector clustering method and device and a storage medium, and belongs to the field of data processing. The method comprises the following steps: dividing N vectors to be clustered into M groups, obtaining M vector groups, combining the M vector groups into M subgroups, wherein each subgroup comprises an A vector group and one or more B vector groups, determining the similarity between any two vectors in each A vector group; and obtaining the similarity between every two vectors in the N vectors according to the similarity between every two vectors in the N vectors andthe similarity between each vector included in the A vector group and each vector included in each B vector group in the same group, and clustering the N vectors according to the similarity between every two vectors in the N vectors. According to the method and the device, the problem of repeated calculation can be avoided, so that the calculation overhead is reduced, and too much storage space is not occupied.

Owner:HUAWEI TECH CO LTD

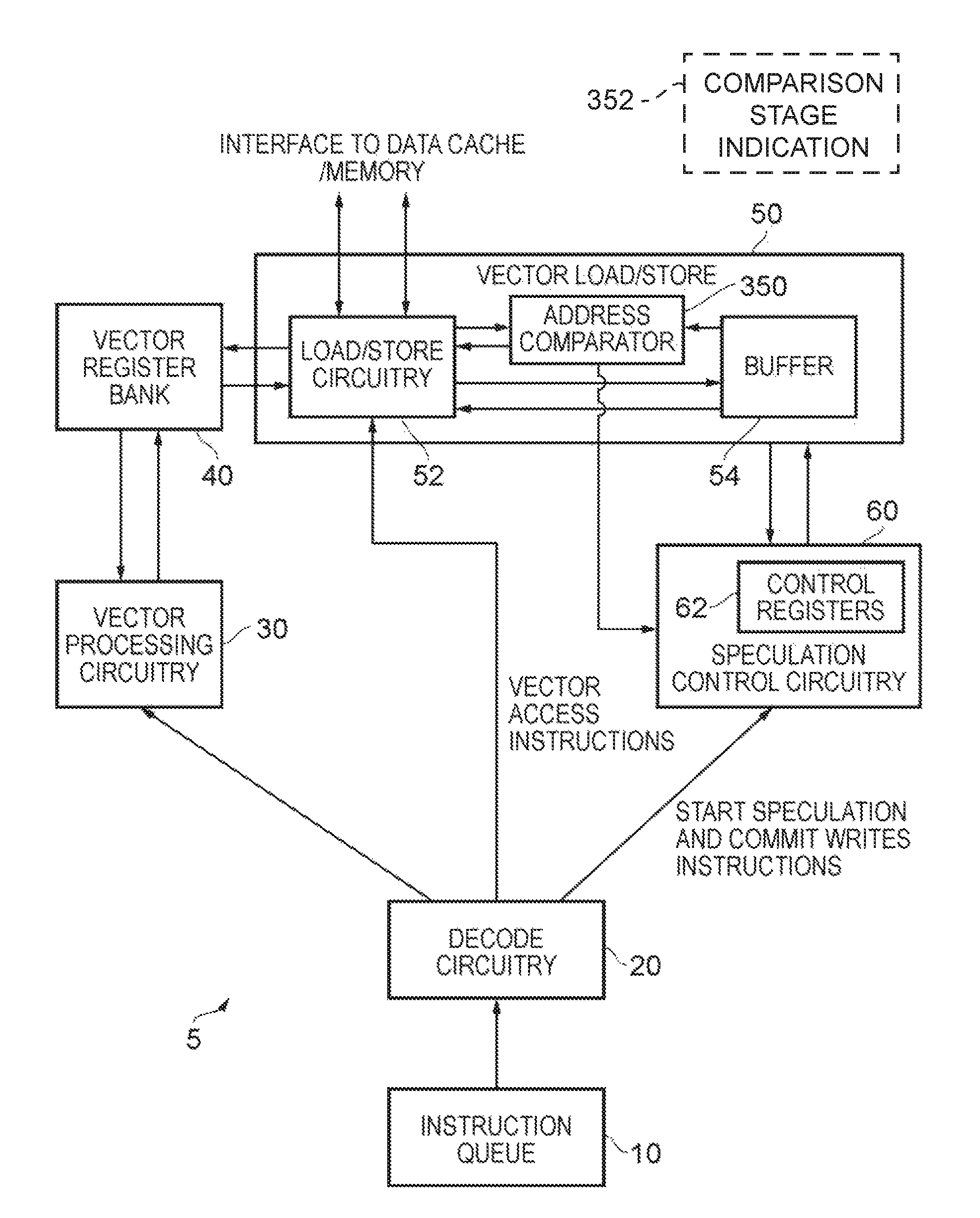

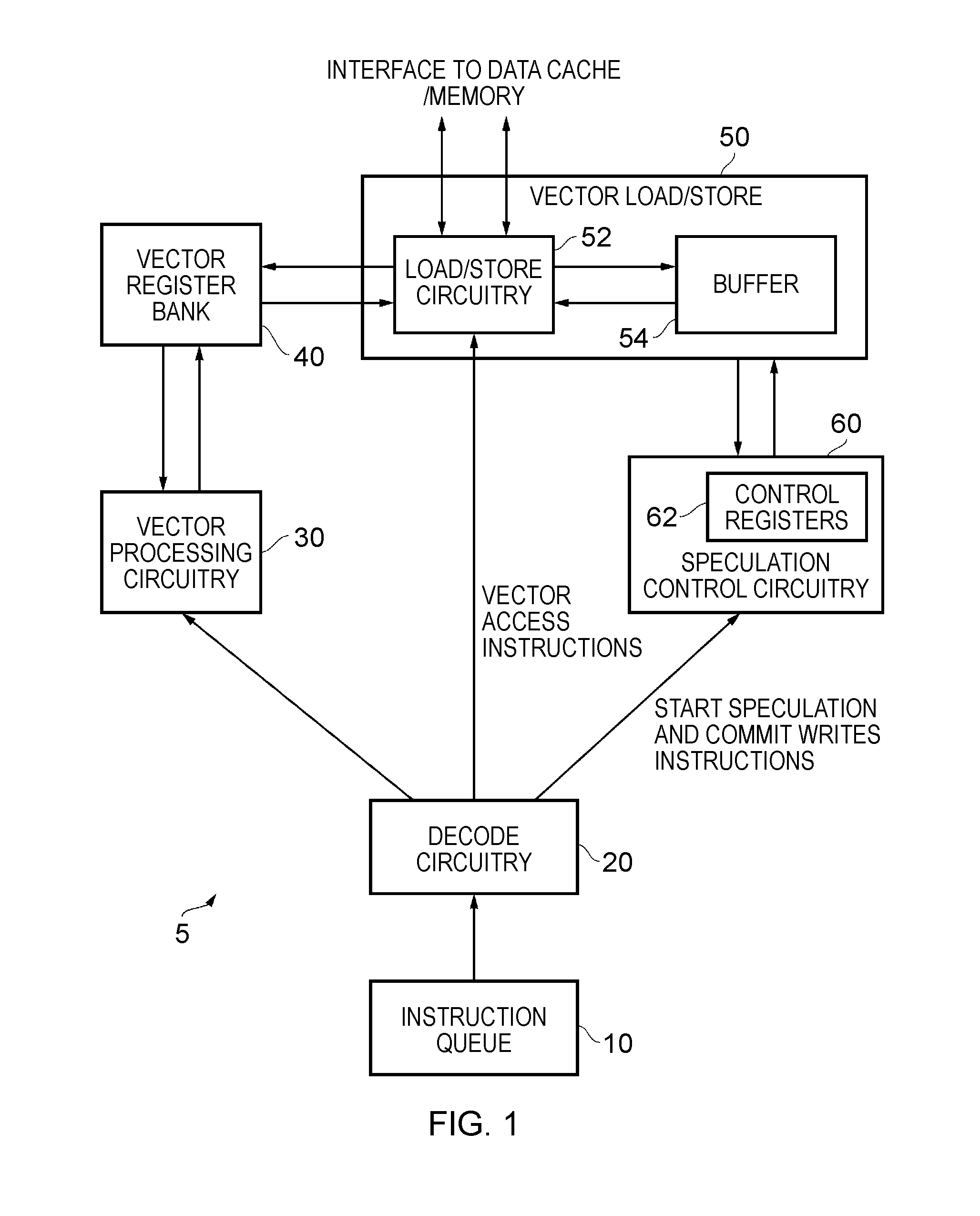

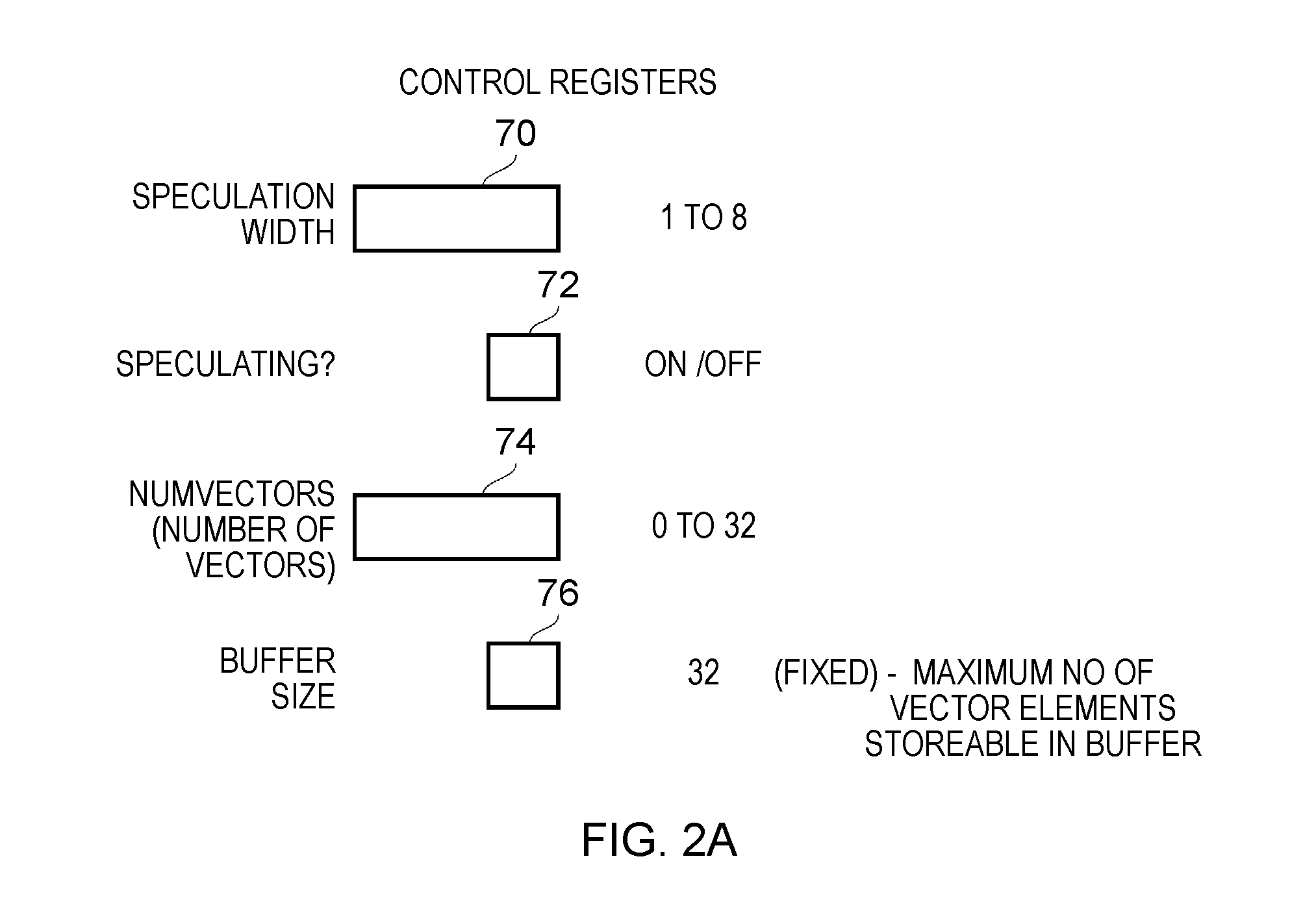

Apparatus and method for controlling the number of vector elements written to a data store while performing speculative vector write operations

ActiveUS9483438B2Reduce in quantityIncrease the number ofRegister arrangementsConcurrent instruction executionProcessor registerVector element

A data processing apparatus and method for performing speculative vector access operations are provided. The data processing apparatus has a reconfigurable buffer accessible to vector data access circuitry and comprising a storage array for storing up to M vectors of N vectors elements. The vector data access circuitry performs speculative data write operations in order to cause vector elements from selected vector operands in a vector register bank to be stored into the reconfigurable buffer. On occurrence of a commit condition, the vector elements currently stored in the reconfigurable buffer are then written to a data store. Speculation control circuitry maintains a speculation width indication indicating the number of vector elements of each selected vector operand stored in the reconfigurable buffer. The speculation width indication is initialized to an initial value, but on detection of an overflow condition within the reconfigurable buffer the speculation width indication is modified to reduce the number of vector elements of each selected vector operand stored in the reconfigurable buffer. The reconfigurable buffer then responds to a change in the speculation width indication by reconfiguring the storage array to increase the number of vectors M and reduce the number of vector elements N per vector. This provides an efficient mechanism for supporting performance of speculative data write operations.

Owner:ARM LTD

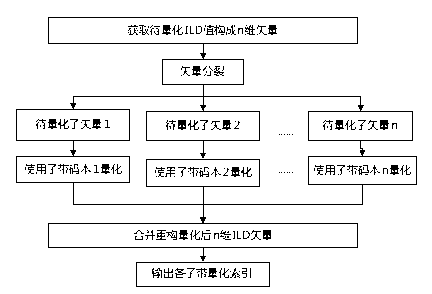

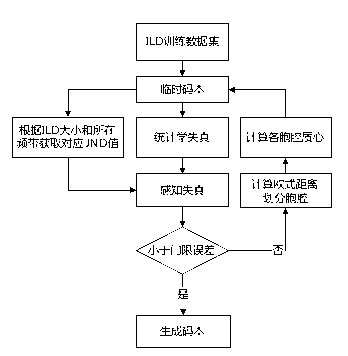

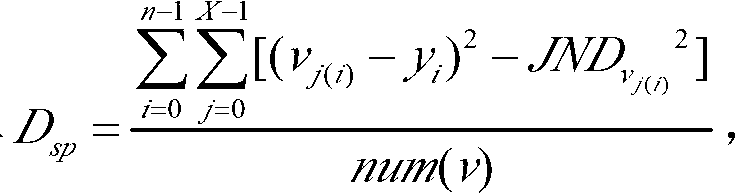

Method for acquiring horizontal azimuth parameter codebook in three-dimensional (3D) audio

ActiveCN102708872AImprove quantitative subjective performanceSpeech analysisAverage distortionGreek letter epsilon

The invention discloses a method for acquiring a horizontal azimuth parameter codebook in a three-dimensional (3D) audio. The method comprises the following steps of: 1, determining the number n of codewords in a required codebook and the dimension number D of each codeword; 2, dividing a horizontal azimuth parameter in a horizontal azimuth parameter training set into D-dimensional vectors to obtain a training vector set, and forming n D-dimensional temporary codebooks by using the first n vectors; 3, dividing the vectors in the training vector set into n cells; 4, calculating subjective average distortion Dsp, comparing the subjective average distortion Dsp and a preset threshold error epsilon, determining a current temporary codebook is a final codebook if Dsp is smaller than epsilon, otherwise executing a step 5; and 5, reselecting a new temporary codebook, and repeating the steps 3 to 4. When the codebook acquired by the method is applied to horizontal azimuth parameter quantification, the whole subjective quantification performance can be improved.

Owner:WUHAN UNIV

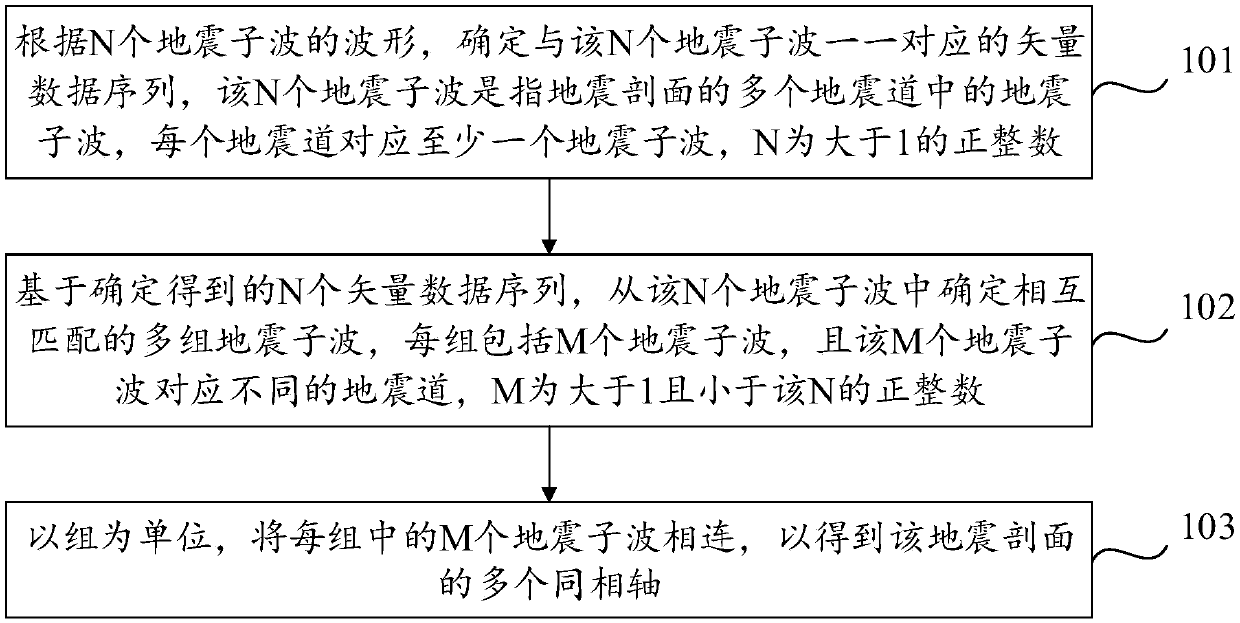

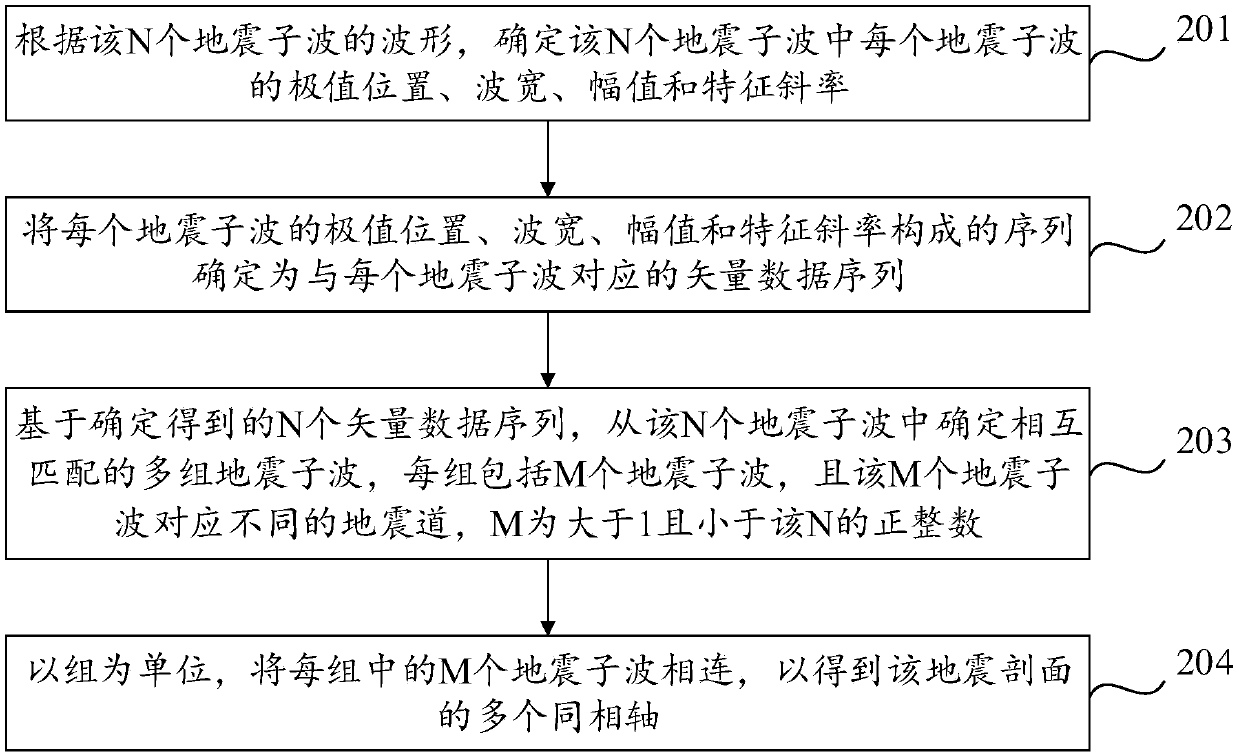

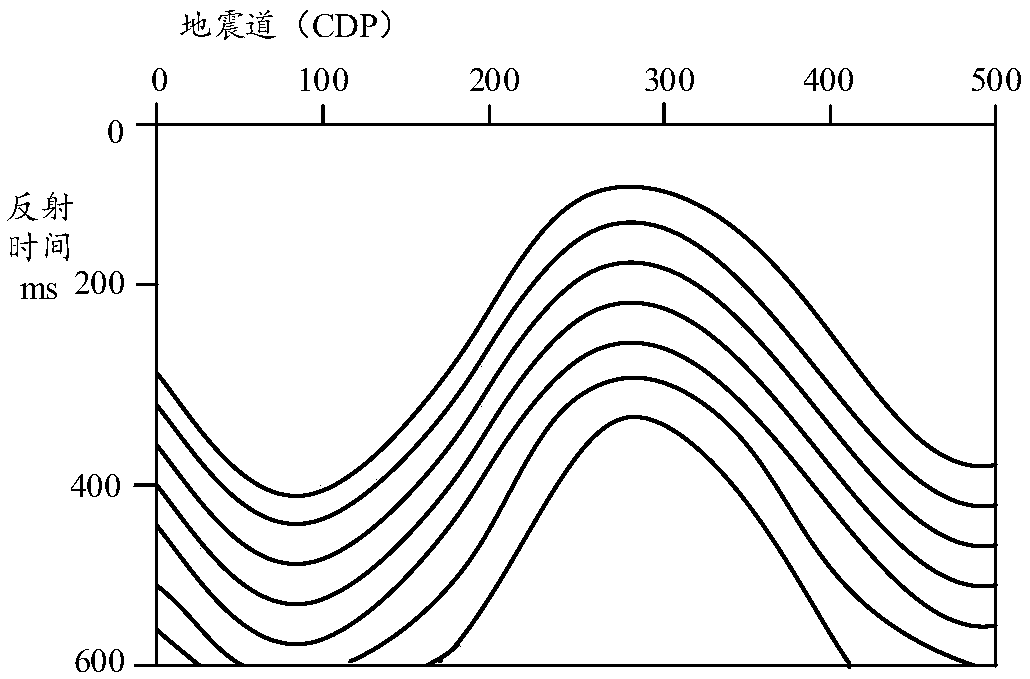

Method and device for automatically acquiring events of seismic section and storage medium

The invention discloses a method and device for automatically acquiring the events of a seismic section and a storage medium, and belongs to the technical field of seismic exploration. The method includes the steps of: determining, according to the waveforms of N seismic wavelets, vector data sequences corresponding to the N seismic wavelets one to one, wherein the N seismic wavelets are seismic wavelets in a plurality of seismic traces of a seismic section, and each seismic trace corresponds to at least one seismic wavelet; based on the determined N vector data sequences, determining mutually-matched group of seismic wavelets from the N seismic wavelets, wherein each group comprises M seismic wavelets and the M seismic wavelets correspond to different seismic traces; and connecting the Mseismic wavelets in each group in units of groups to obtain a plurality of events of the seismic section. The method can quickly and automatically acquire the events of the seismic section according to the vector data sequences corresponding to the seismic wavelets, saves time and lays a foundation for subsequent structural interpretation of the seismic section.

Owner:PETROCHINA CO LTD

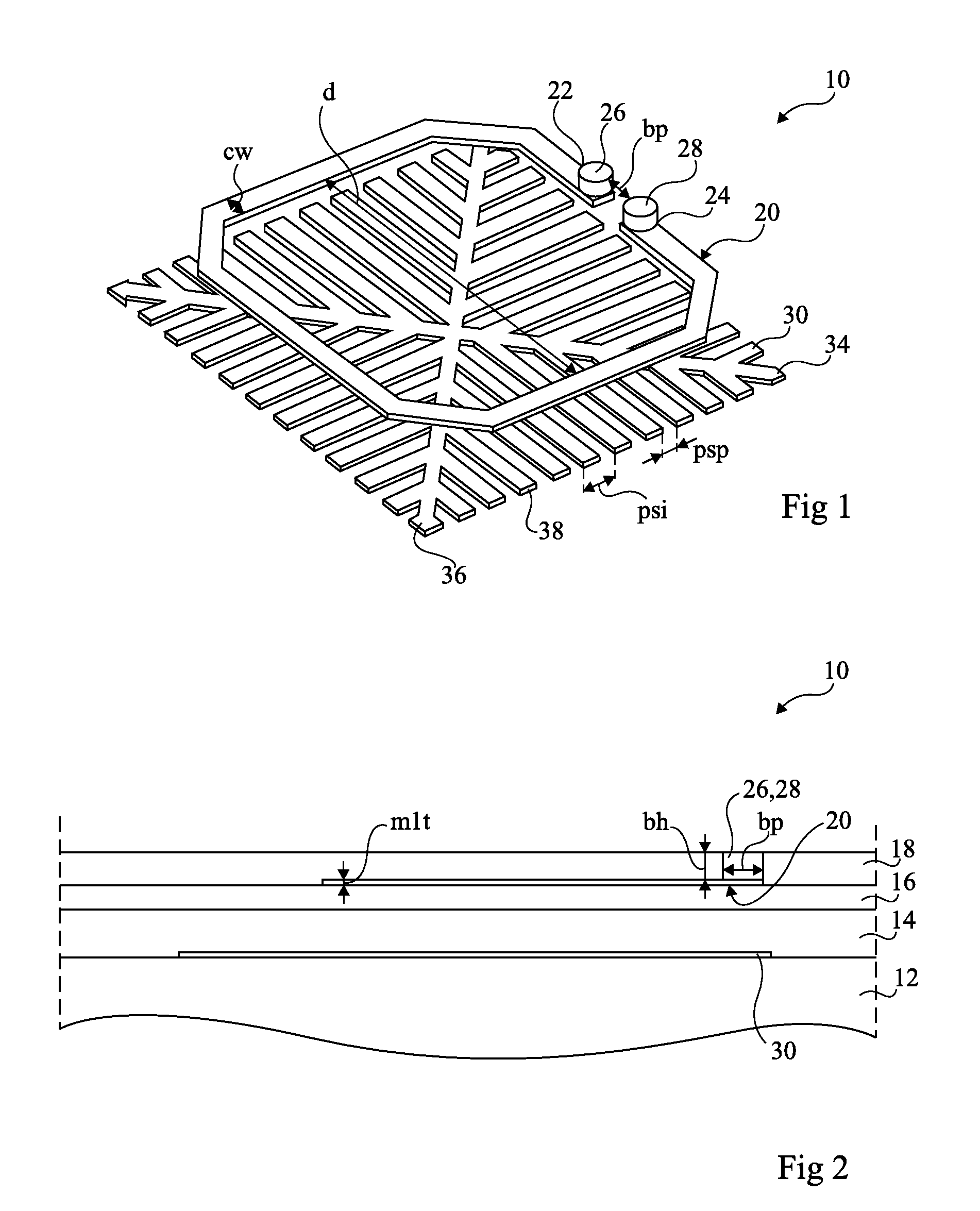

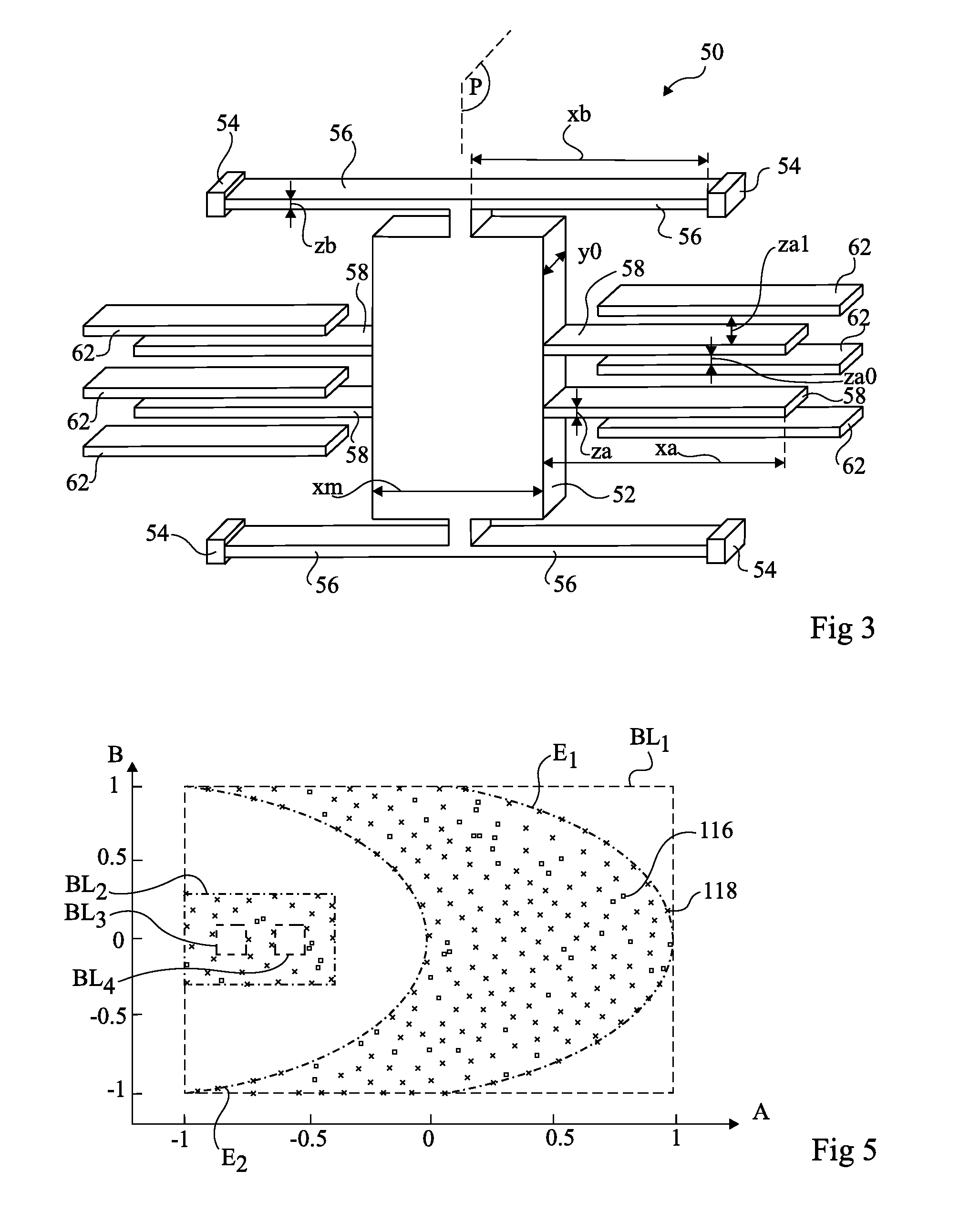

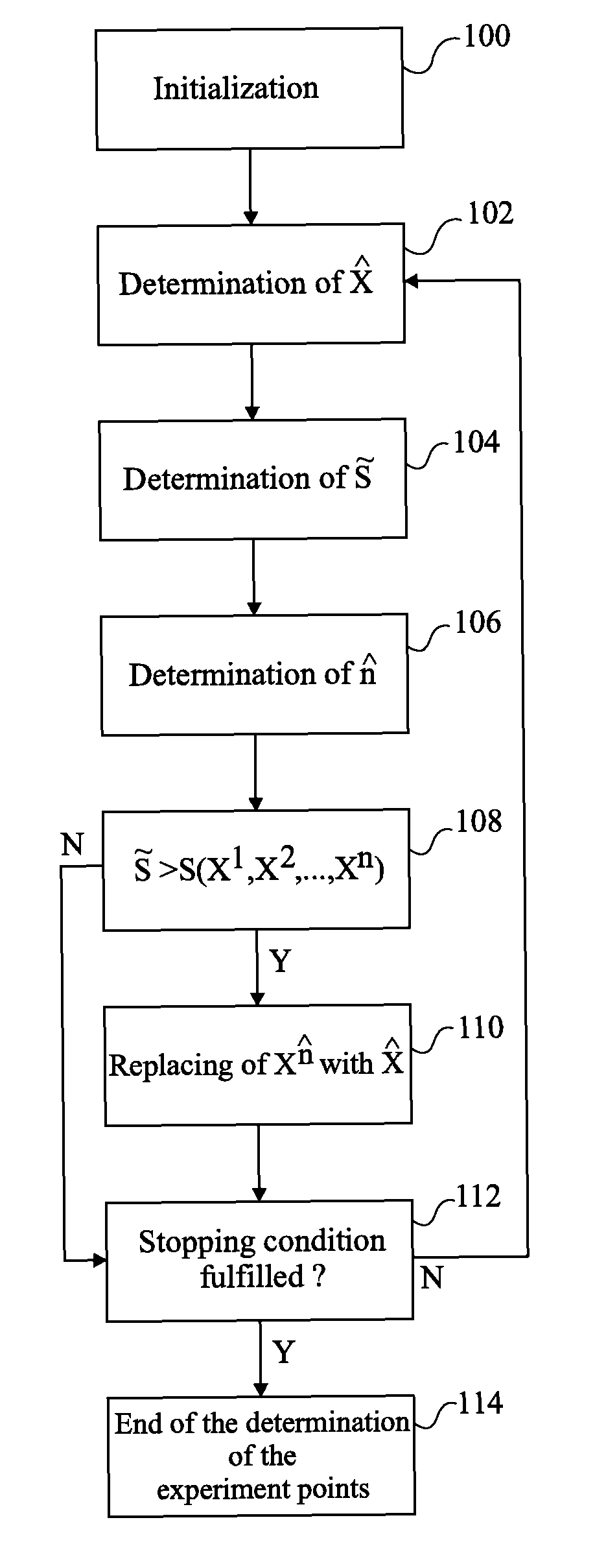

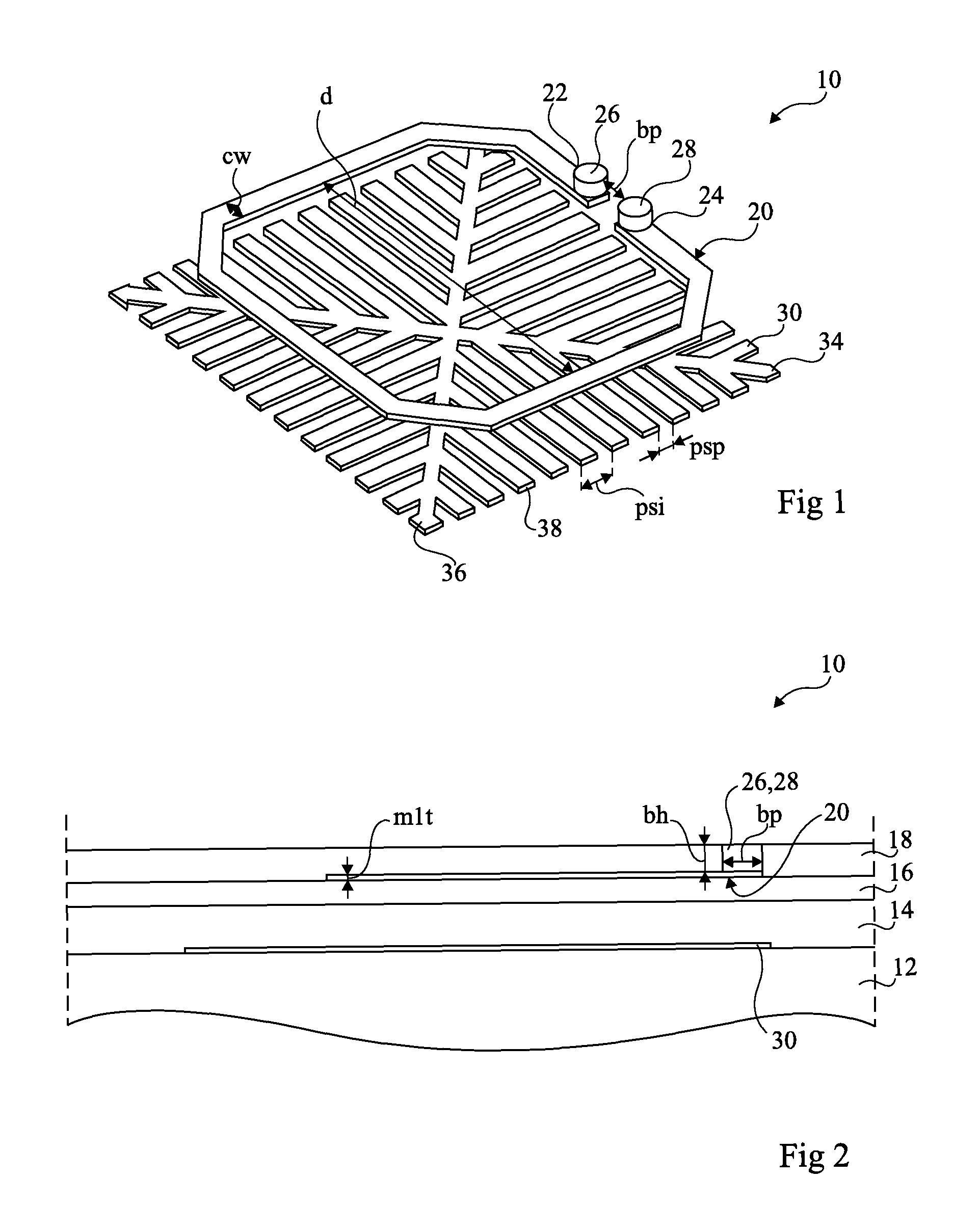

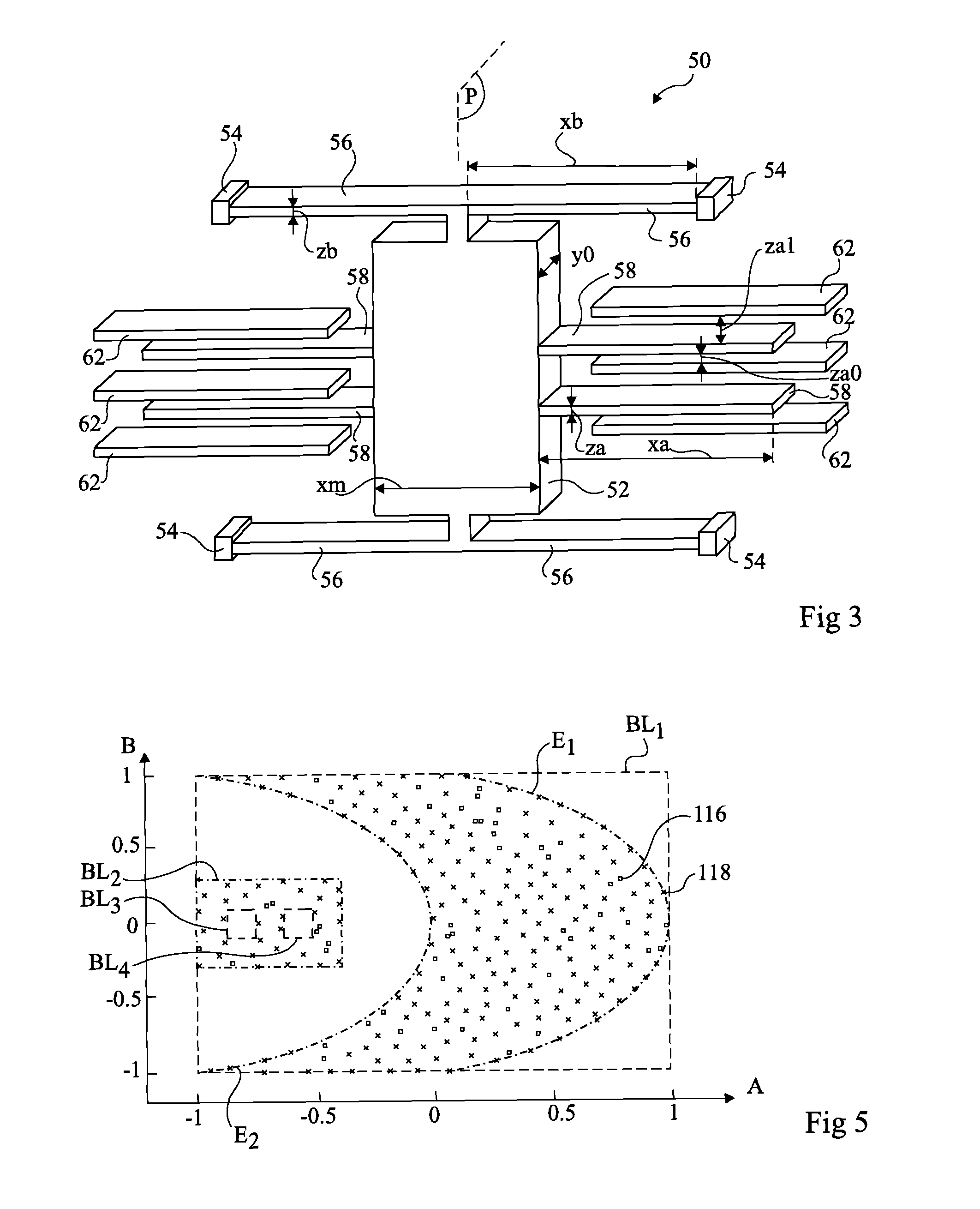

Determination of values of physical parameters of one or several components of an electronic circuit or of a microelectro-mechanical system

ActiveUS20090144672A1Digital computer detailsDigital dataMicroelectromechanical systemsComputer science

A method for determining, for each of at least p physical parameters of one or several components of an electronic circuit or of a microelectromechanical system, a number n of experiment values of the physical parameter includes determining n vectors of dimension p, each component of each of the vectors corresponding to one of n initial values of one of physical parameters; and iteratively modifying at least some of the n vectors to bring to a maximum, at least locally, for each pair of vectors from among pairs of n vectors, the smallest average of the sum of distances between the vectors of said pair projected onto sub-spaces of dimension k, where k belongs to a set of integers ranging between 1 and p and at least comprising 1, 2, and p, the components of each of the n vectors corresponding, at the end of the iterations, to experiment values.

Owner:INFINISCALE

A Fast Gas Identification Algorithm Based on Frequency Domain Feature Extraction

The invention provides a frequency domain feature extraction based rapid gas identification algorithm which is a novel gas identification algorithm. The rapid gas identification algorithm includes that passing gas is subjected to data acquisition and interception through sensors, intercepted data are subjected to Fourier transform to acquire distribution of intercept sequences in a frequency domain, first 20 data values from the 0Hz position are removed to serve as features of the data acquired through single sensors, features of n sensor data are spliced into a 20*n vector according to a certain order, a large number of the vectors are acquired by repeating the previous steps and are given labels of corresponding gas types, the vectors and the labels are mapped to a three-dimensional space by means of an LDA (linear discriminant analysis) algorithm to acquire a mapping matrix, the vectors and labor data acquired through dimensionality reduction are input in an SVM (support vector machine) classifier to perform modeling of the classifier, vectors of the data under the three-dimensional space of the LDA are acquired by multiplying unknown feature vectors with the mapping matrix, and the vectors are input into the established classifier model to perform prediction of the gas types measured currently.

Owner:SHENZHEN UNIV

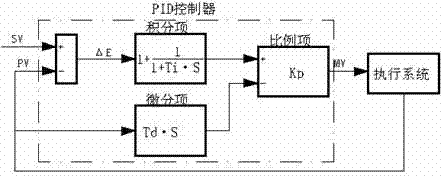

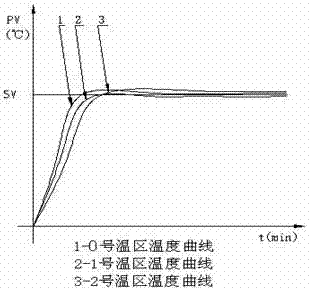

A temperature decoupling master-slave control method for multiple heating zones

ActiveCN104975165BEasy to controlLow costHeat treatment process controlTemperature controlArray data structure

Owner:CHENGDU AIRCRAFT INDUSTRY GROUP

Cipher key negotiating method, enciphering/deciphering method and signature/verification method

InactiveCN101374043BScale upIncreased complexityKey distribution for secure communicationPublic key for secure communicationAlgorithmFunction group

Owner:管海明 +1

Vector clustering method, device and storage medium

ActiveCN110781247BThere will be no double counting problemsReduce computational overheadRelational databasesSpecial data processing applicationsTwo-vectorAlgorithm

The application discloses a vector clustering method, device and storage medium, belonging to the field of data processing. The method includes: dividing the N vectors to be clustered into M groups to obtain M vector groups, combining the M vector groups into M groups, each group including an A vector group, and one or more B vector group, determine the similarity between any two vectors in each A vector group, and the similarity between each vector included in the A vector group and each B vector group included in the same group , to obtain the similarity between every two vectors in the N vectors, and cluster the N vectors according to the similarity between every two vectors in the N vectors. The present application can avoid the problem of repeated calculation, thereby reducing calculation overhead, and does not occupy too much storage space.

Owner:HUAWEI TECH CO LTD

Determination of values of physical parameters of one or several components of an electronic circuit or of a microelectro-mechanical system

A method for determining, for each of at least p physical parameters of one or several components of an electronic circuit or of a microelectromechanical system, a number n of experiment values of the physical parameter includes determining n vectors of dimension p, each component of each of the vectors corresponding to one of n initial values of one of physical parameters; and iteratively modifying at least some of the n vectors to bring to a maximum, at least locally, for each pair of vectors from among pairs of n vectors, the smallest average of the sum of distances between the vectors of said pair projected onto sub-spaces of dimension k, where k belongs to a set of integers ranging between 1 and p and at least comprising 1, 2, and p, the components of each of the n vectors corresponding, at the end of the iterations, to experiment values.

Owner:INFINISCALE

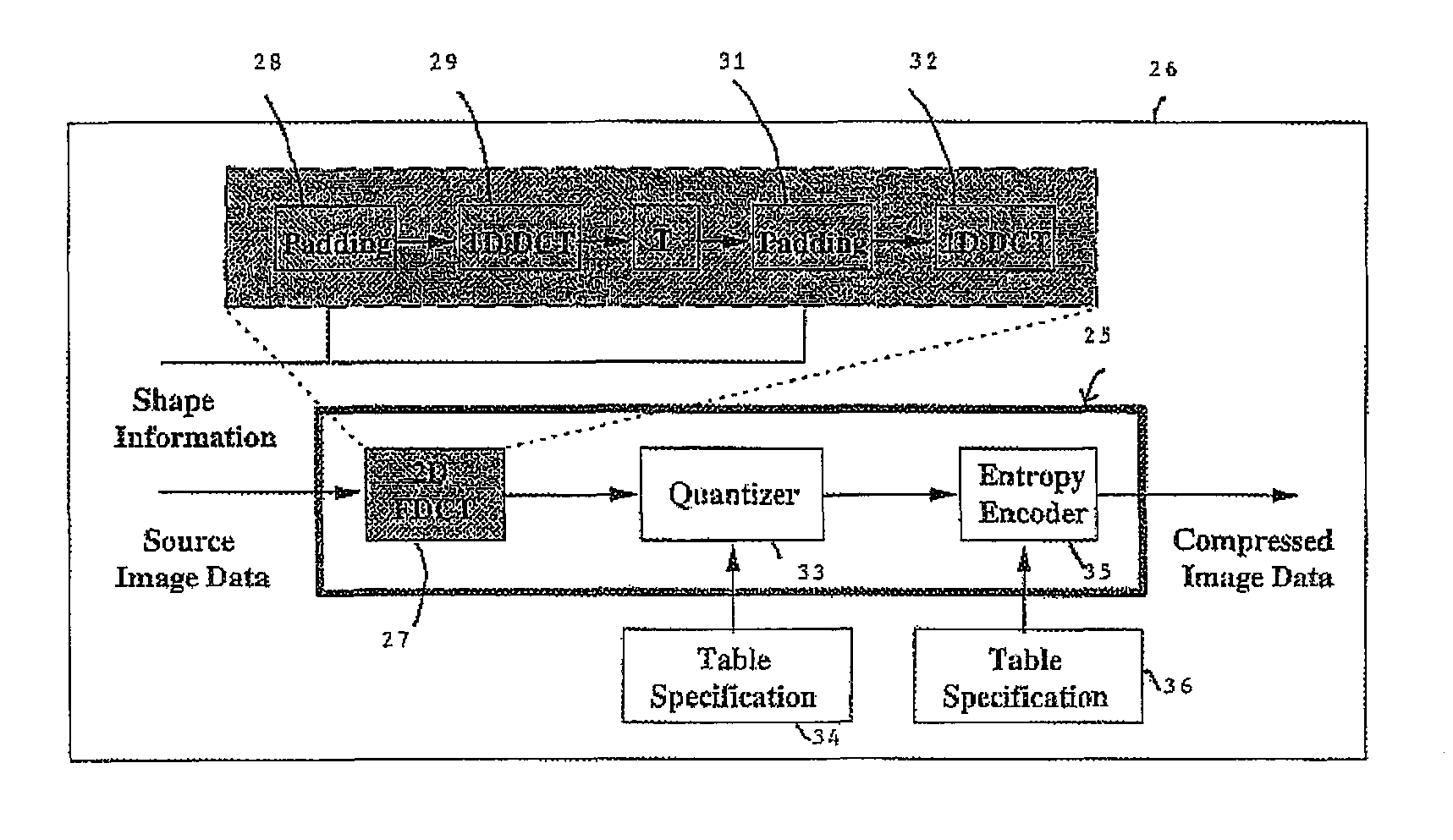

Method and apparatus for coding an image object of arbitrary shape

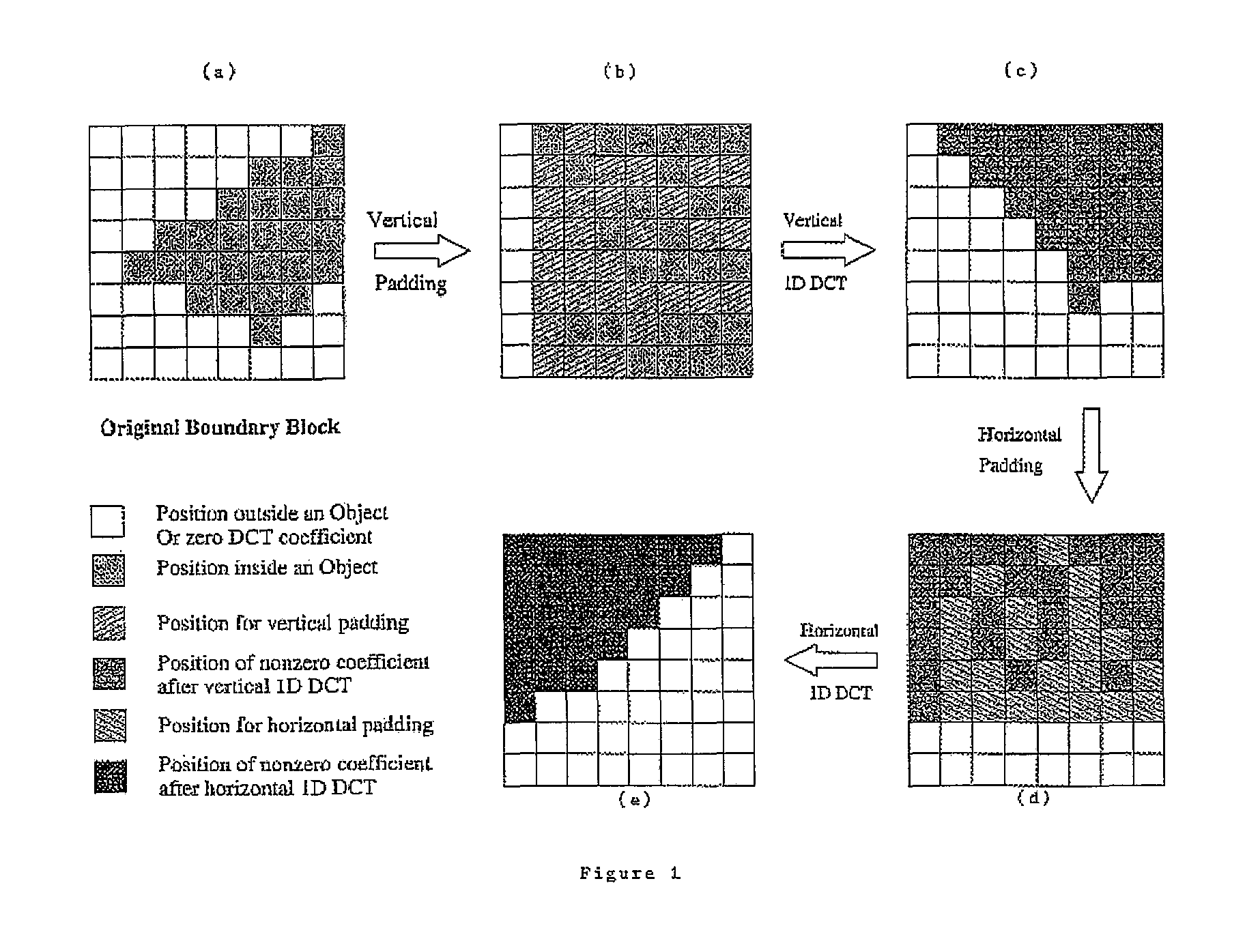

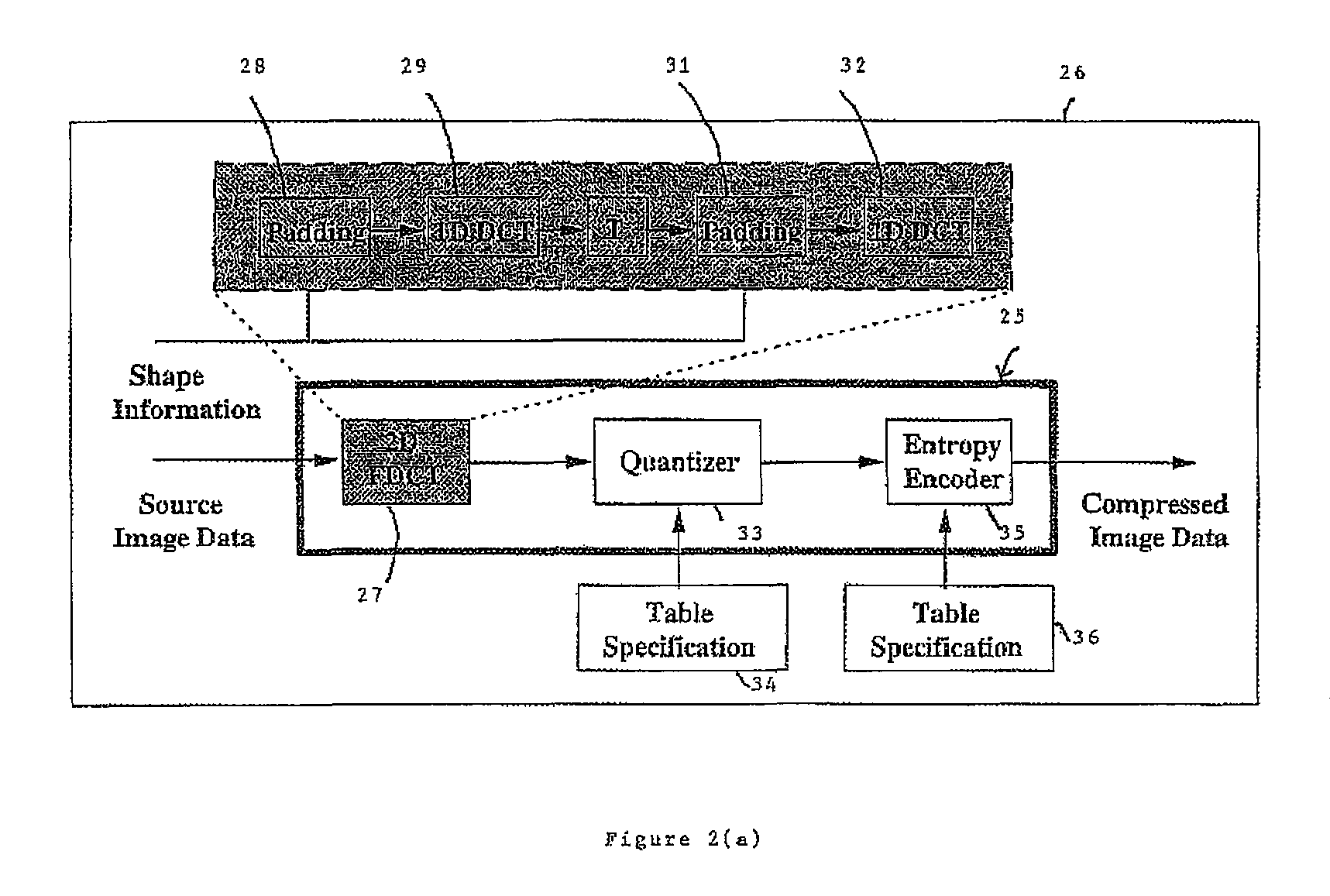

InactiveUSRE42853E1Simple designImprove efficiencyCharacter and pattern recognitionTelevision systemsArray data structureTheoretical computer science

It is known to represent a square block of an image which has a maximum horizontal or vertical extension N as N vectors each representing one column or row, and encode it using an N×N discrete cosine transform matrix. We introduce a technique which transforms an input vector, or array, representing a portion of an arbitrarily-shaped object block in which the maximum horizontal or vertical extension is at most N, by adding to it additional padding elements, to produce a vector or array which can be encoded using an N×N discrete cosine transform. The padding maximises the number of transformed elements which are zero. We propose encoding arbitrarily-shaped objects based on this padding technique.

Owner:THE HONG KONG UNIV OF SCI & TECH