Method of selecting by pass of multiport register pile and equipment

A register file and multi-port technology, which is applied to architectures with multiple processing units, instruments, machine execution devices, etc., can solve problems such as large numbers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

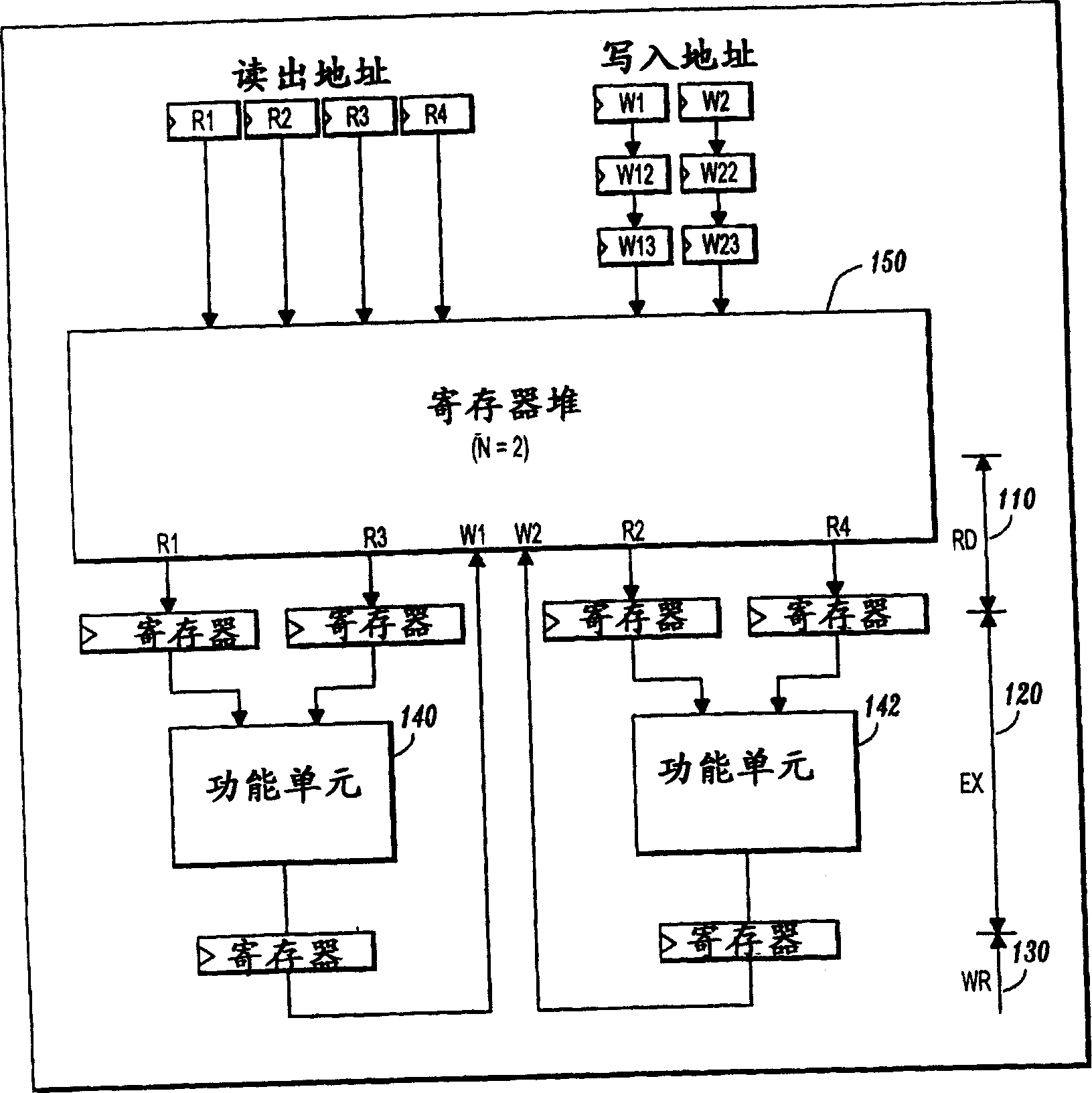

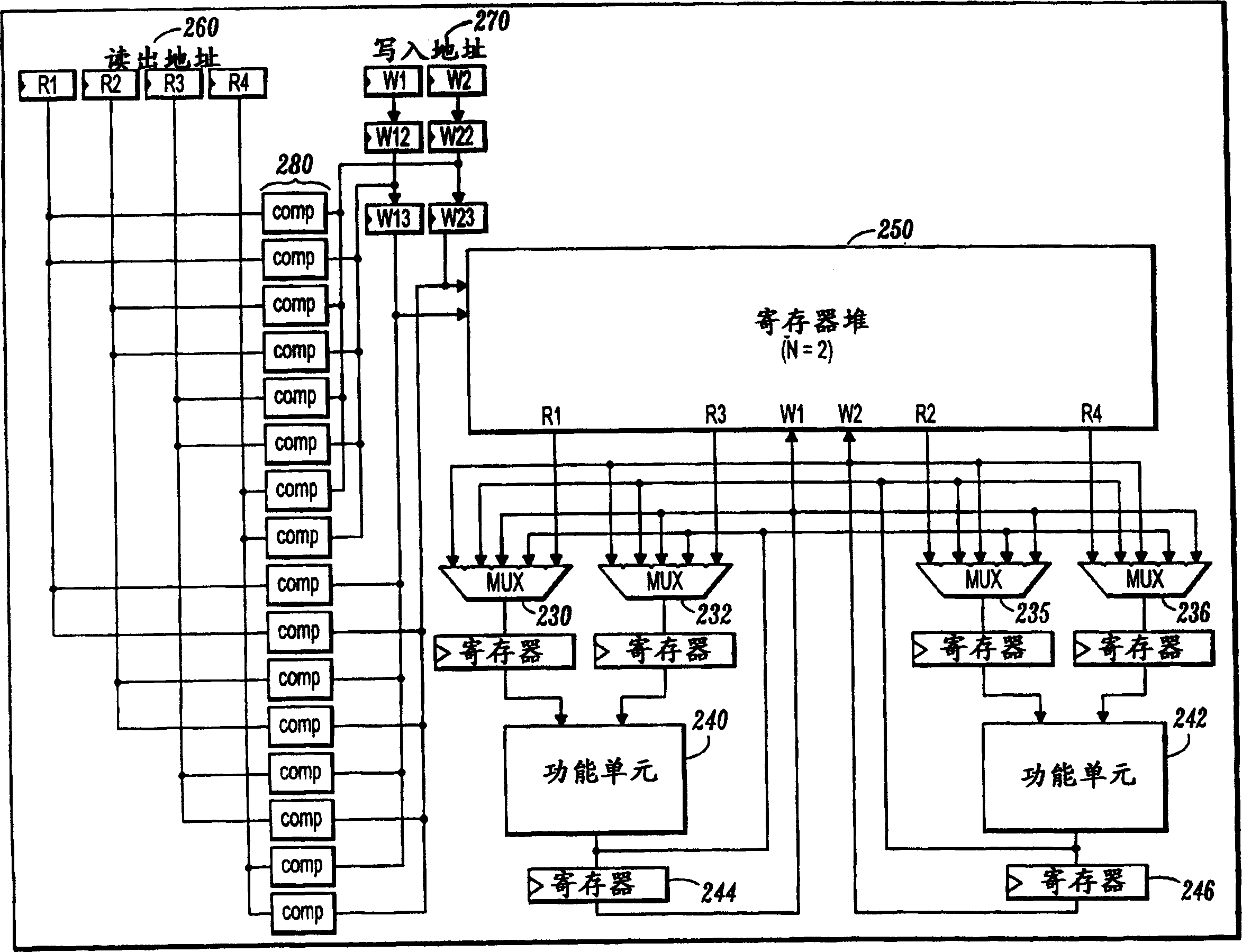

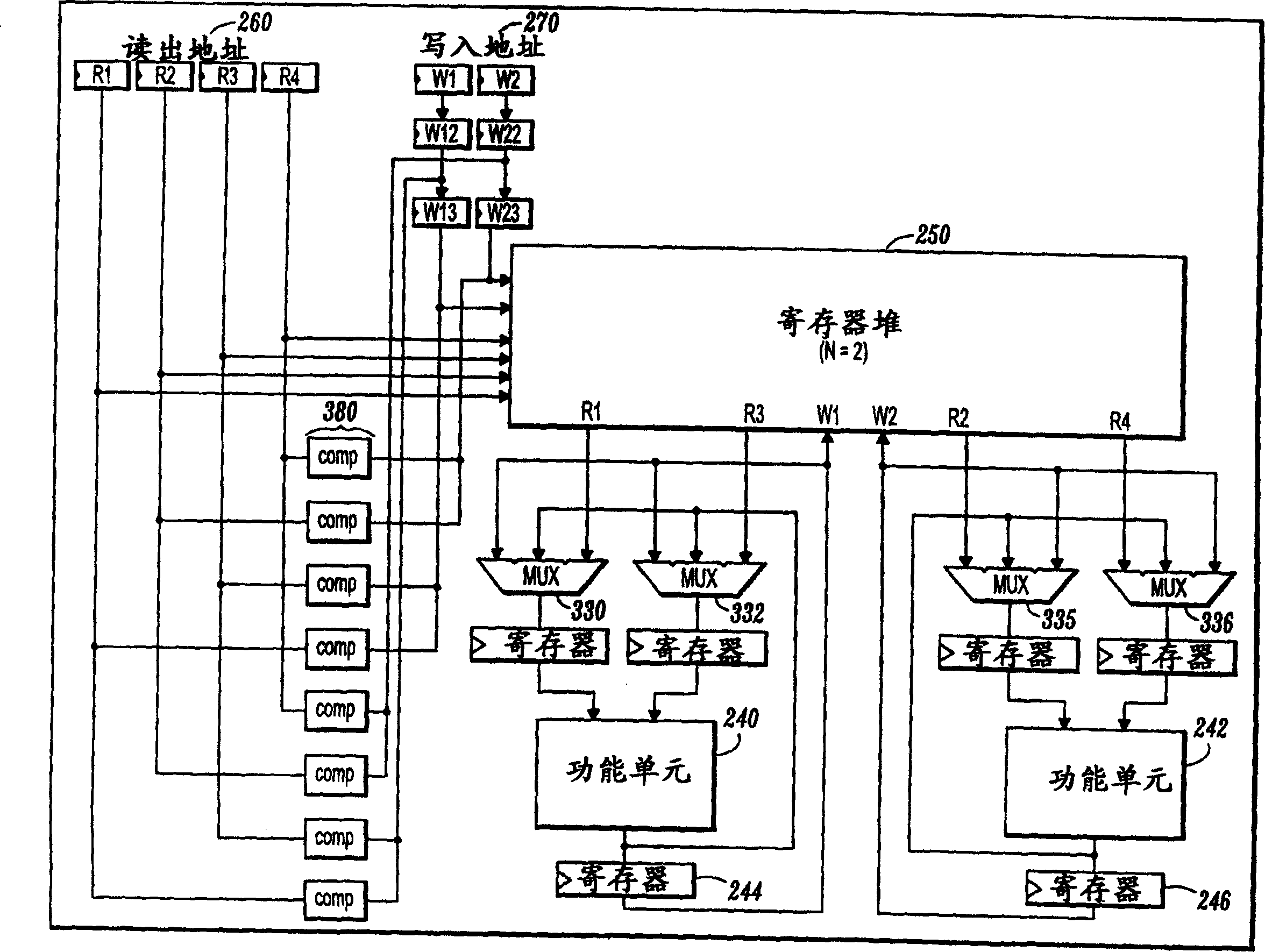

[0013] To allow uninterrupted (i.e., return-forward-return) operations on vector data, where the result of an operation at cycle i is used as an operation for cycle i+1 (bypass) or as an operation for cycle i+2 (write-through) The input of the bypass from the output of the EX and WR stages can be fed back and multiplexed with the output of the RD stage. The full bypass structure allows any cell of the result vector to be bypassed to any cell of either of the two input operand vectors.

[0014] A pipeline with full bypass such as figure 2 shown. During the RD stage, four data elements are either read from the outputs of the multi-ported register file (250), the functional units (240, 242), or written to the outputs of the stage registers (244, 246) . For each read index (260) pointing to a single cell, it is compared with the cell write index (270) using a plurality of comparators (280). If the read index matches any of the write indexes of the last cycle, the data unit is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More