An Optimized Instruction Scheduling and Register Allocation Method on Clustered VLIW Processor

A technology for register allocation and instruction scheduling, applied in resource allocation, concurrent instruction execution, machine execution devices, etc., can solve the problem of increasing basic block scheduling time, achieve the effect of reducing register overflow and optimizing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

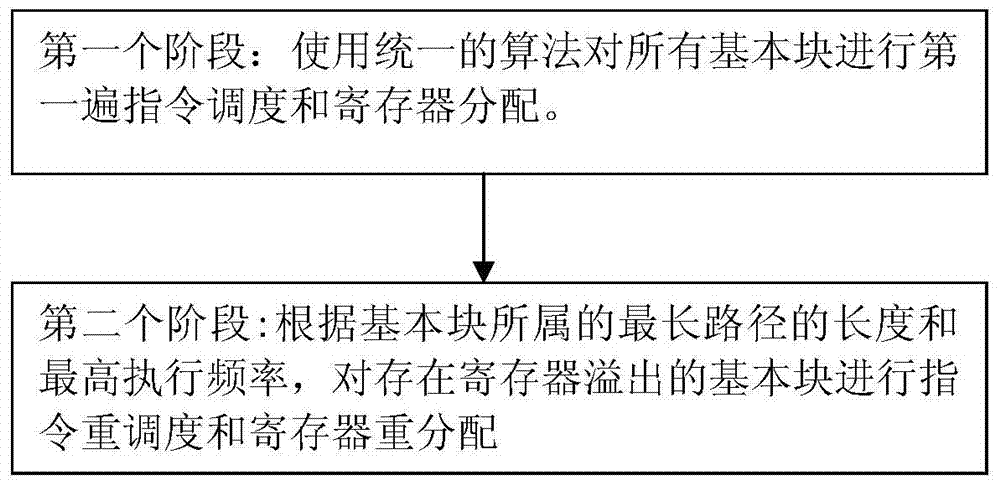

[0032] Such as figure 1 As shown, the instruction scheduling and register allocation method on a kind of optimized sub-clustering VLIW processor of the present invention aims at minimizing the longest execution time of the program, and it includes two stages: in the first stage, using a unified The algorithm performs the first pass of instruction scheduling and register allocation for all basic blocks; in the second stage, according to the length of the longest path to which the basic block belongs and the highest execution frequency, instruction rescheduling and register rescheduling are performed on the basic blocks with register overflow. distribute.

[0033] During specific application, the detailed flow process of the present invention is:

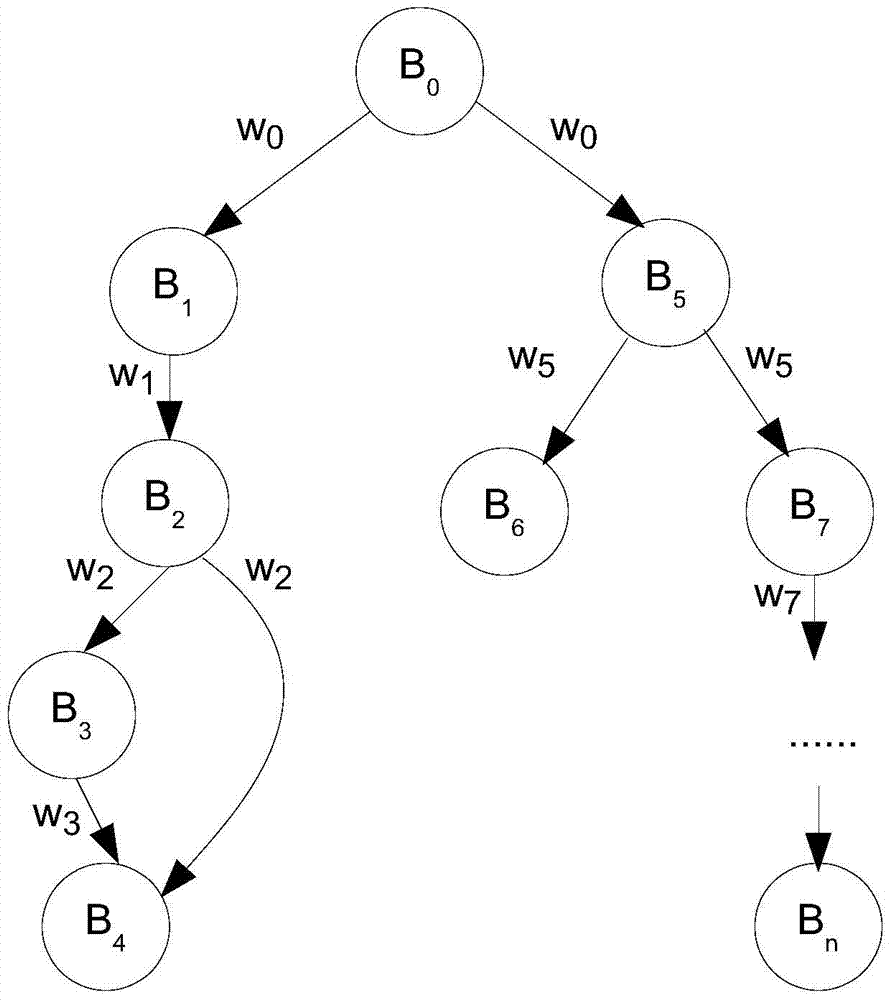

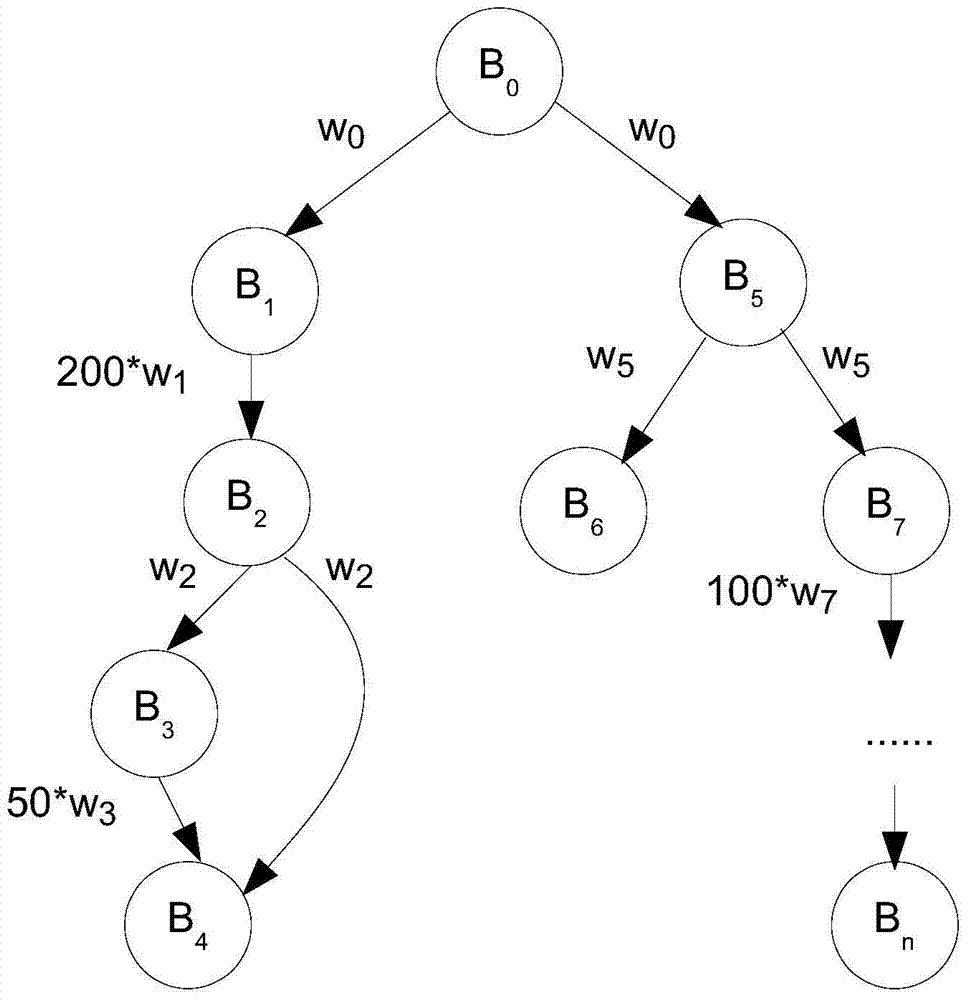

[0034] (1) Construct the authorized control flow graph G of program P, where w i undef...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap