Pixel circuit, driving method thereof and active matrix OLED (organic lighting emitting diode)

A technology of a pixel circuit and a driving method, applied in the field of flat panel display, can solve problems such as uneven brightness, achieve the effects of realizing compensation, avoiding threshold voltage deviation, and realizing IR voltage drop

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

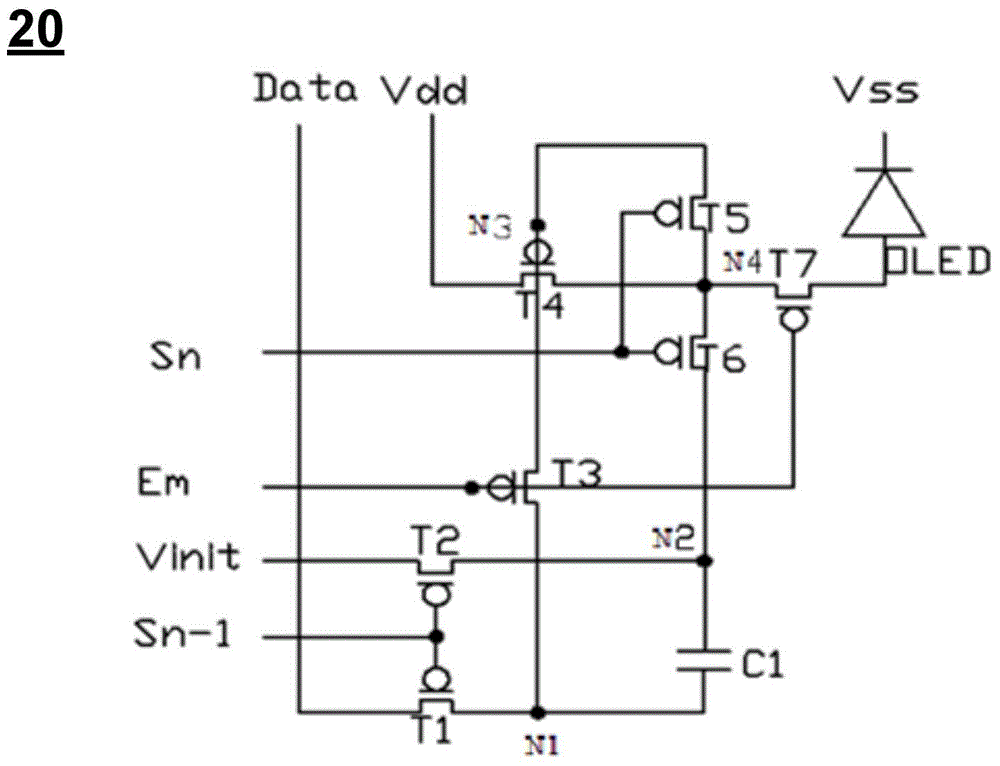

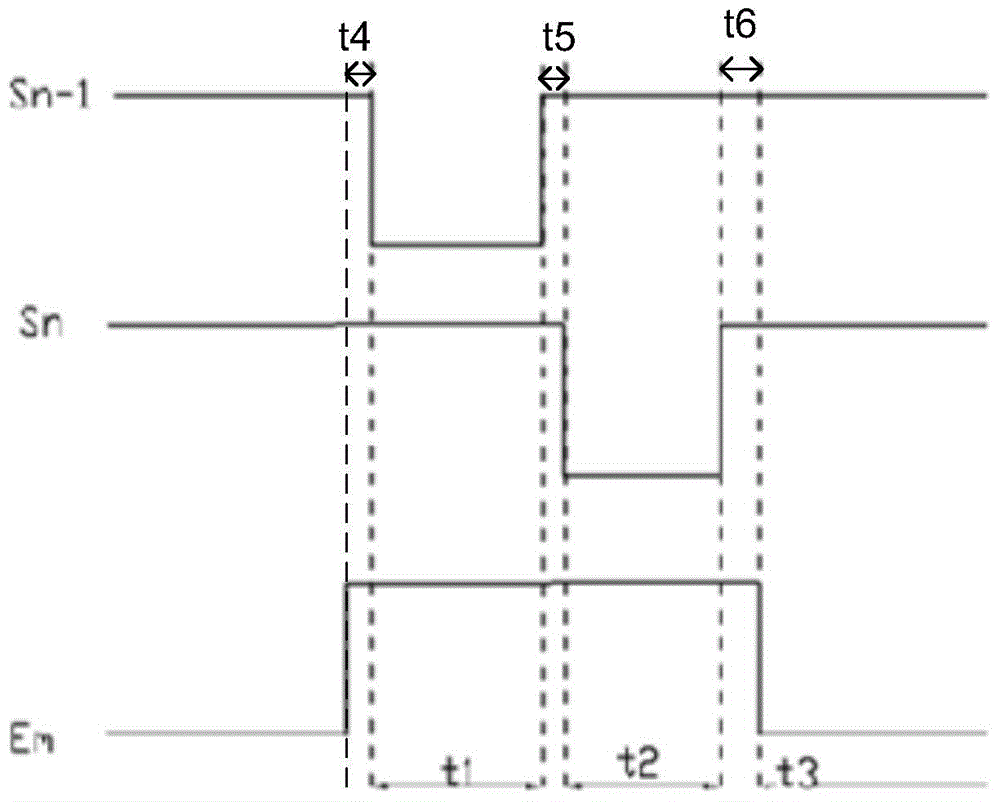

[0041] Please refer to figure 2 , which is a schematic structural diagram of a pixel circuit according to Embodiment 1 of the present invention. Such as figure 2 As shown, the pixel circuit 20 includes: a first thin film transistor T1 connected between the data line Data and the first node N1, the gate of which is connected to the first scan line Sn-1; a second thin film transistor T2 connected to Between the third power supply and the second node N2, its gate is connected to the first scanning line Sn-1; the third thin film transistor T3 is connected between the first node N1 and the third node N3, and its gate is connected to the emitter Control line Em; the fourth thin film transistor T4, connected between the first power supply and the fourth node N4, and its gate connected to the third node N3; the fifth thin film transistor T5, connected between the third node N3 and the fourth node N4 Between, its gate is connected to the second scanning line Sn; the sixth thin film...

Embodiment 2

[0073] Please refer to Figure 4 , which is a circuit diagram of a pixel circuit according to Embodiment 2 of the present invention. Such as Figure 4 As shown, the pixel circuit 30 includes: a first thin film transistor T1 connected between the data line Data and the first node N1, the gate of which is connected to the first scan line Sn-1; a second thin film transistor T2 connected to Between the third power supply and the second node N2, its gate is connected to the first scanning line Sn-1; the third thin film transistor T3 is connected between the first node N1 and the third node N3, and its gate is connected to the emitter Control line Em; the fourth thin film transistor T4, connected between the first power supply and the fourth node N4, and its gate connected to the third node N3; the fifth thin film transistor T5, connected between the third node N3 and the fourth node N4 Between, its gate is connected to the second scanning line Sn; the sixth thin film transistor T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More