Radiation-resistant SRAM self-refresh circuit with high utilizable ratio, and self-refresh method of radiation-resistant SRAM self-refresh circuit

A utilization rate and anti-radiation technology, applied in information storage, static memory, digital memory information, etc., can solve the problems of decreased memory availability, inability to read and write SRAM, error accumulation, etc., and improve the ability to resist multi-bit flipping. , Improve the anti-radiation ability, simplify the design effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

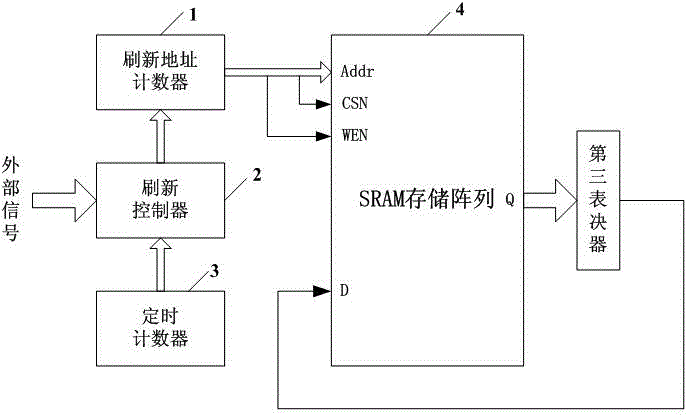

[0024] A radiation-resistant SRAM self-refresh circuit with high availability, including a timing counter 3, a refresh controller 2, and a refresh address counter 1, the output of the timing counter 3 is connected to the input of the refresh controller 2, and the refresh of an external signal is connected The output terminal of the controller 2 is connected with the input terminal of the refresh address counter 1, the output terminal of the refresh address counter 1 is connected with the A, CSN, and WEN terminals of the SRAM storage array 4, and the output terminal Q of the SRAM storage array 4 passes the third voting The device is connected to the D terminal of the SRAM memory array 4, such as figure 1 shown. Refresh address counter 1 is used to generate read and write addresses during refresh; timing counter 3 is used to control the time interval between two rounds of refresh operations; refresh controller 2 according to the signal of timing counter 3, external chip select s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More