A quantization and dequantization hardware multiplexing algorithm and hardware structure suitable for hevc standard

A hardware structure and dequantization technology, applied in the hardware multiplexing algorithm and hardware structure field of quantization and dequantization, can solve the problems of poor compression performance and achieve high performance, high-efficiency real-time encoding, and small hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The method of the present invention will be further specifically described below in conjunction with the accompanying drawings.

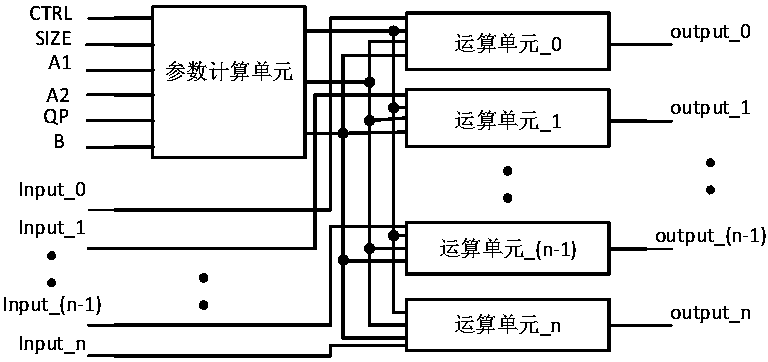

[0037] The quantization and dequantization structure based on the improved algorithm described in the present invention is as follows:

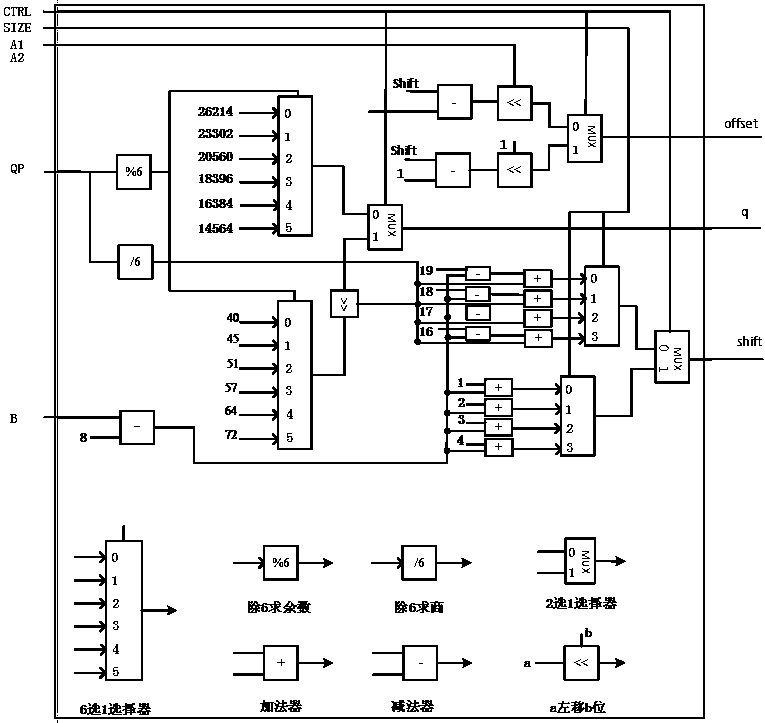

[0038] figure 1 Shown is the unit for calculating the three basic parameters of q, offset, and shift. The input is the quantization step size QP, the control signal CTRL, and B is the bit depth. QP is used to determine the specific parameters of the quantization and dequantization operations; CTRL is used to control the operation Process: CTRL=0 for quantization operation, CTRL=1 for inverse quantization operation. When performing RDOQ, the quantization offset needs to be adjusted, and A1 and A2 are used to determine the compensation amount during quantization.

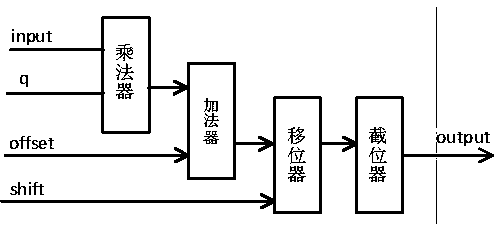

[0039] figure 2 Shown is the operation part of quantization and dequantization. Quantization and dequantization can be divided into four parts:...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More