A time-to-digital converter in a phase-locked loop

A technology of time-to-digital converters, applied in the field of phase-locked loops, can solve the problems of low phase-locking precision of phase-locked loops, and achieve the effects of easy implementation, improved phase-locked accuracy, and improved detection accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

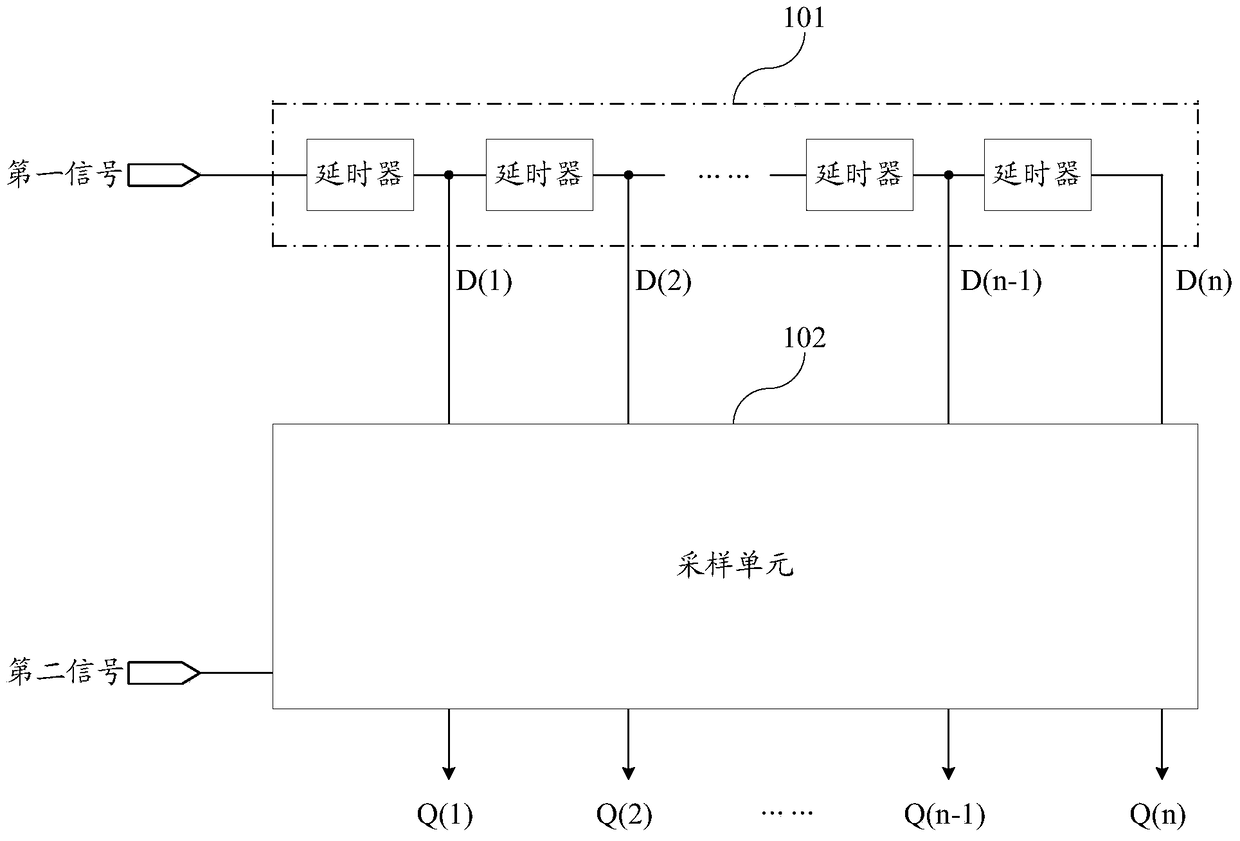

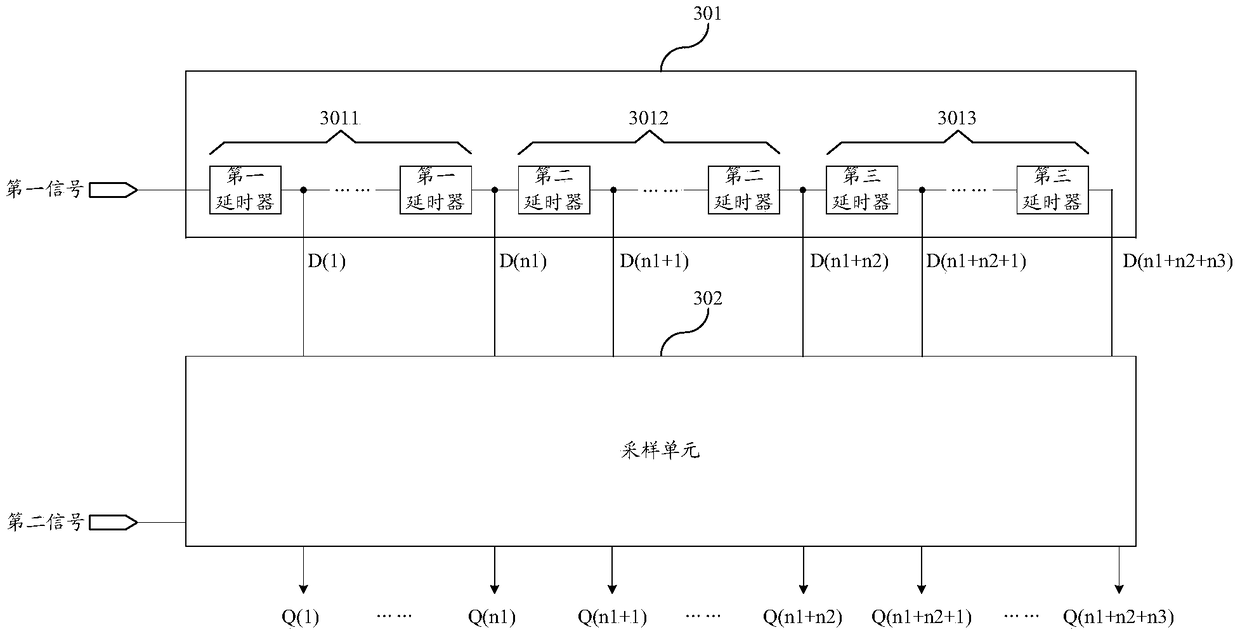

[0045] Embodiment 1 of the present invention provides a time-to-digital converter in a phase-locked loop, such as image 3 As shown, it includes a delay unit 301 that inputs the first signal and a sampling unit 302 that inputs the second signal, wherein:

[0046] The delay unit 301 includes a first delay chain 3011, a second delay chain 3012 and a third delay chain 3013 connected in series, for delaying the first signal; the first delay chain 3011 includes at least one The first delayer, the second delay chain 3012 includes at least three second delayers, the third delay chain 3013 includes at least one third delayer, the delay length of the first delayer and the third delayer The delay length of the timer is greater than the delay length of the second delayer;

[0047] The sampling unit 302 is used to delay each of the first delayers in the first delay chain 3011 in the delay unit 301 and each second delay in the second delay chain 3012 at the preset moment of the second sig...

Embodiment 2

[0066] Based on the same inventive concept, the structure of the time-to-digital converter in the phase-locked loop provided by Embodiment 1 of the present invention is simplified, and Embodiment 2 of the present invention also provides a time-to-digital converter in the phase-locked loop, such as Figure 6 As shown, it includes a delay unit 601 that inputs the first signal and a sampling unit 602 that inputs the second signal, wherein:

[0067] The delay unit 601 includes a first delay chain 6011 and a second delay chain 6012 connected in series, for delaying the first signal; the first delay chain 6011 includes at least one first delayer, and the second delay The time chain 6012 includes at least three second delayers, the delay length of the first delayer is greater than the delay length of the second delayer;

[0068] The sampling unit 602 is used to delay each first delayer in the first delay chain 6011 in the delay unit 601 and each second delay in the second delay chain...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More