Forward error correcting code processor

A processor and generator technology, applied in the direction of forward error control, error prevention, digital transmission system, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The specific embodiments of the invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

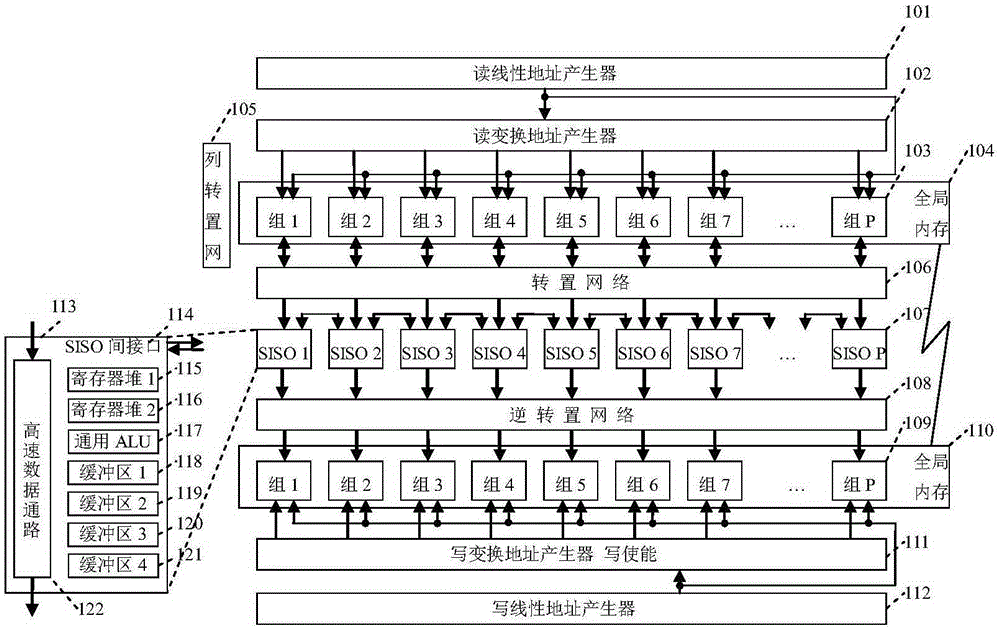

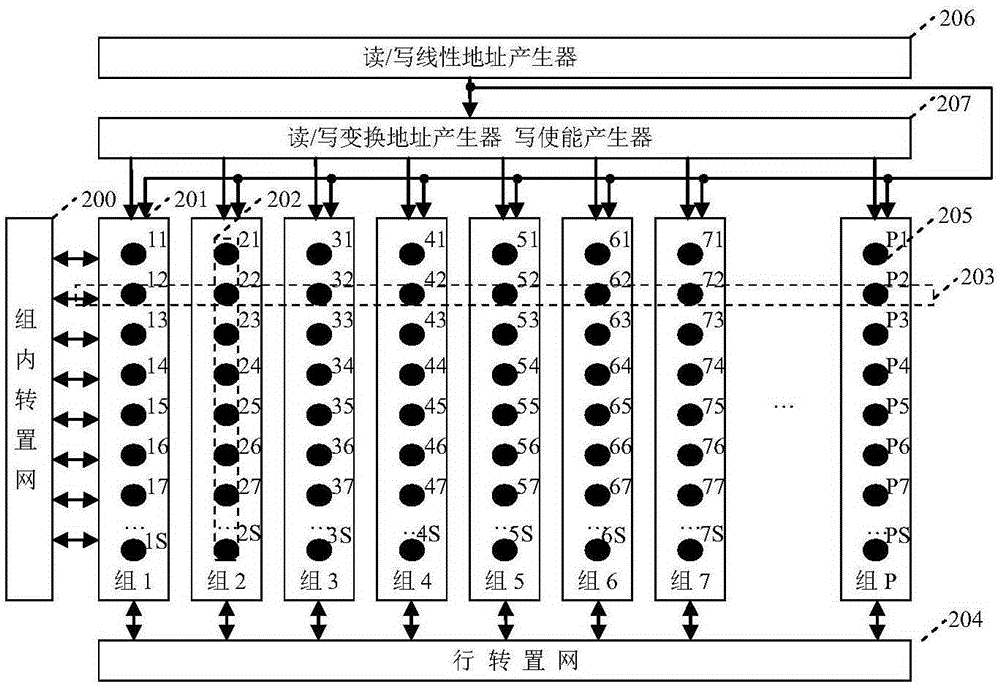

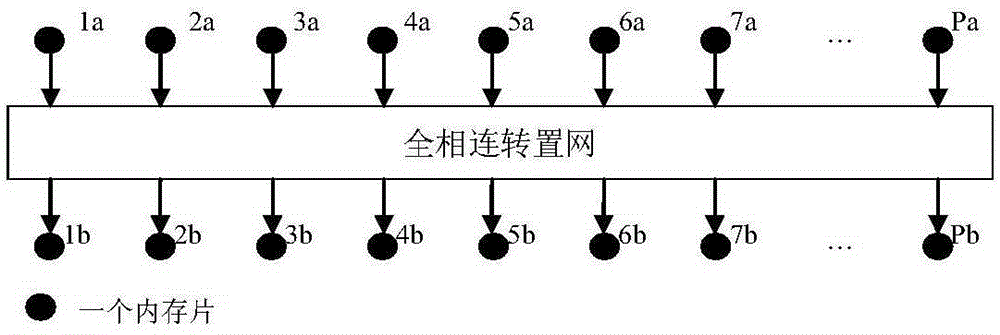

[0033] figure 1 It shows a forward error correction code processor provided by an embodiment of the present invention, such as figure 1 As shown, the processor includes: a read linear address generator, a write linear address generator, a read conversion address generator, a write conversion address generator, a memory group, an operation execution unit, a transpose network and an inverse transpose network;

[0034] The read linear address generator is connected to the read conversion address generator, the read conversion address generator is connected to the memory group, and the memory group is connected to the operation execution unit through the transposition network, s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More