Novel gate structure and manufacture method thereof

A manufacturing method and technology of gate structure, which can be applied to electrical components, circuits, semiconductor devices, etc., and can solve problems such as device damage, device turn-on delay, and large delay.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

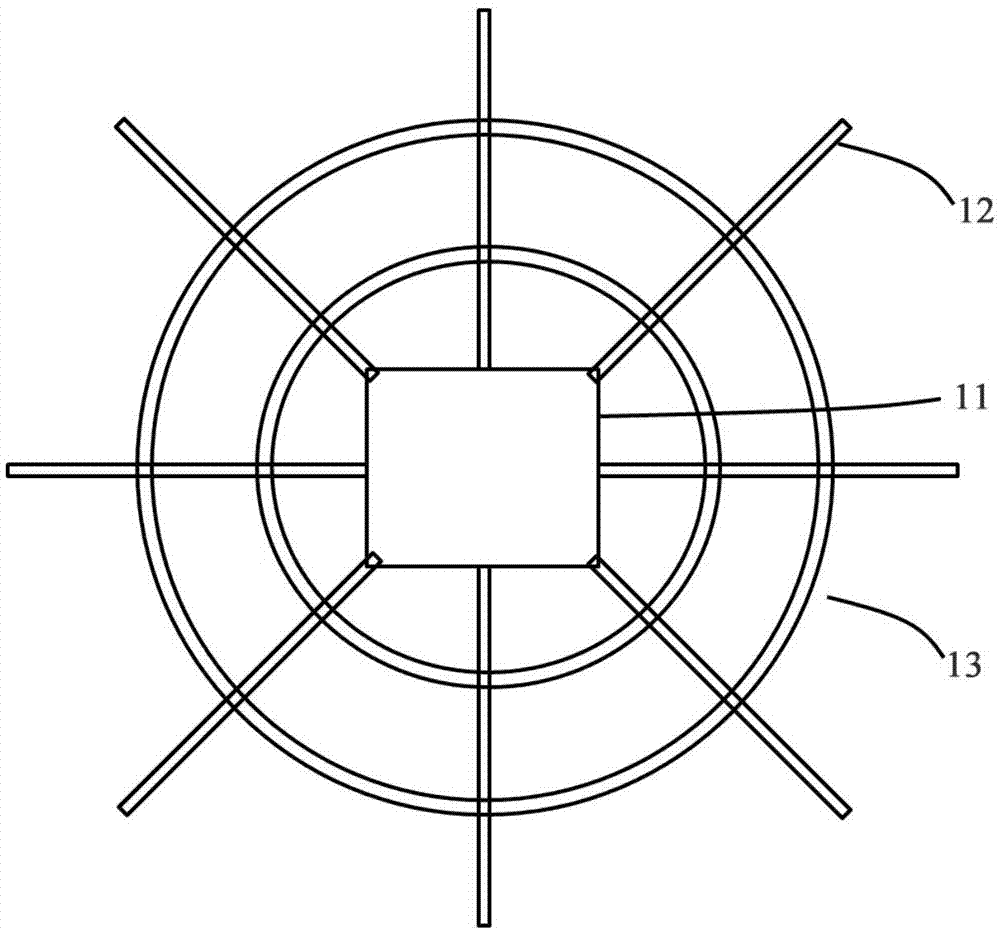

[0021] A novel grid structure includes a grid pad area 11, a radial bus bar 12 emanating from the grid pad area 11, an annular bus bar 13 surrounding the grid pad area 11, and the radial bus bar 12 and the annular bus bar 13 The intersection point is connected to the surrounding cell grid; the number of the radial bus bars is 8, and the width is 20 μm; the number of the ring bus bars is 2, the width of the bus bars is 20 μm, and the distance from the grid pad is relatively close The diameter of the ring is 800 μm, and the diameter of the ring farther from the grid pad is 2000 μm; the structure is as shown figure 1 As shown; the gate pad region 11, the emissive bus bar 12, and the annular bus bar 13 are made of n-type degenerately doped polysilicon.

[0022] The specific manufacturing method of the new gate structure is as follows:

[0023] 1) drawing the layout of the grid pad region 11, the emissive bus bar 12 and the annular bus bar 13 on the same layer;

[0024] 2) prepar...

Embodiment 2

[0027] A novel grid structure includes a grid pad area 11, a radial bus bar 12 emanating from the grid pad area 11, an annular bus bar 13 surrounding the grid pad area 11, and the radial bus bar 12 and the annular bus bar 13 The intersection point is connected with the surrounding cell grid; the number of the radial bus bars is 10, and the width is 18 μm; the number of the ring bus bars is 3, the width of the bus bars is 15 μm, and the diameter of the ring is successively 800μm, 1500μm, 2500μm; structure as shown figure 1 As shown; the gate pad area 11, the emissive bus bar 12, and the annular bus bar 13 are prepared from a single metal layer of Ag.

[0028] The specific manufacturing method of the new gate structure is as follows:

[0029] 1) drawing the layout of the grid pad region 11, the emissive bus bar 12 and the annular bus bar 13 on the same layer;

[0030] 2) deposit and prepare the Ag metal layer of the gate pad region 11, the emissive bus bar 12 and the annular b...

Embodiment 3

[0033] A novel grid structure includes a grid pad area 11, a radial bus bar 12 emanating from the grid pad area 11, an annular bus bar 13 surrounding the grid pad area 11, and the radial bus bar 12 and the annular bus bar 13 The intersection point is connected with the surrounding cell grid; the number of the radial bus bars is 15, and the width is 15 μm; the number of the ring bus bars is 5, the width of the bus bars is 15 μm, and the diameter of the ring is successively 800μm, 1500μm, 2500μm, 3500μm, 4500μm; structure as shown figure 1 As shown; the gate pad area 11, the emissive bus bar 12, and the annular bus bar 13 are prepared from a single metal layer of Ag.

[0034] The specific manufacturing method of the new gate structure is as follows:

[0035] 1) drawing the layout of the grid pad region 11, the emissive bus bar 12 and the annular bus bar 13 on the same layer;

[0036] 2) depositing and preparing a composite metal layer of Ag and Al in the grid pad region 11, th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More