Method and device for monitoring and counting bottom hardware behaviours

A low-level hardware and behavioral technology, applied in the field of smart cards, can solve problems such as poor repeatability, heavy workload, and inaccurate analysis, and achieve the effect of performance optimization and good positioning of performance bottlenecks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

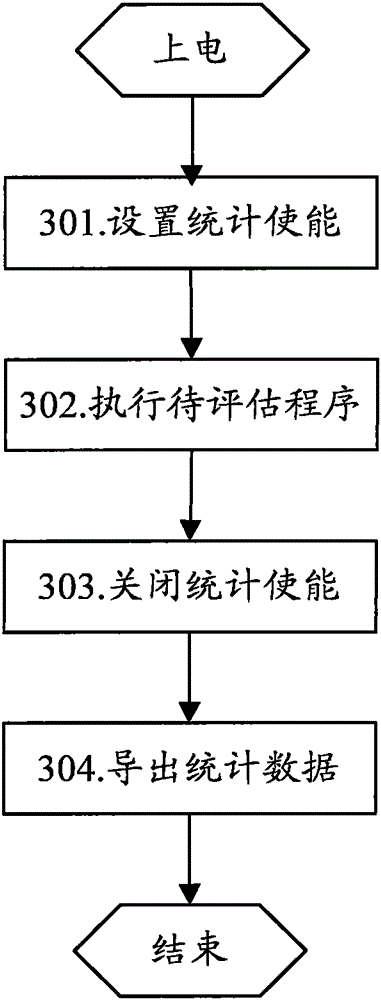

[0023] The technical solutions of the present invention will be further elaborated below in conjunction with the accompanying drawings and specific embodiments.

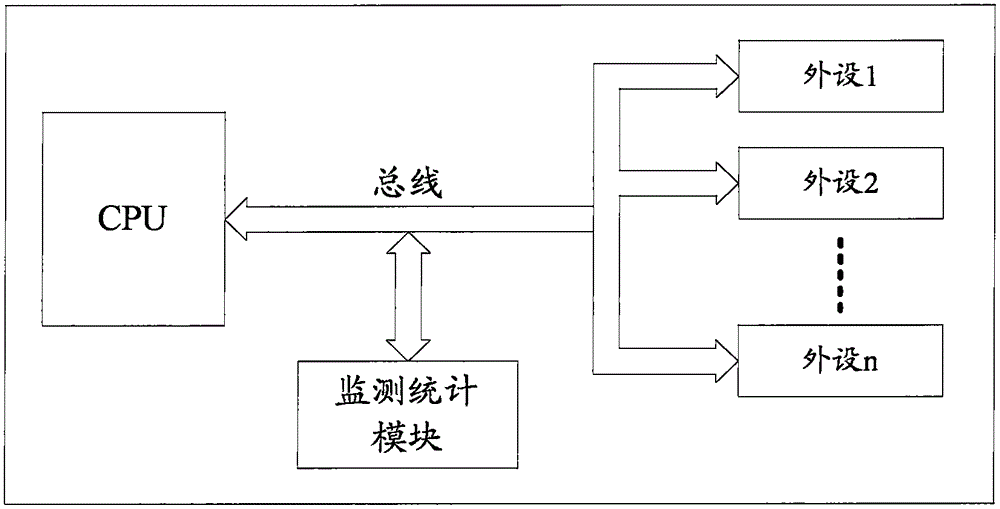

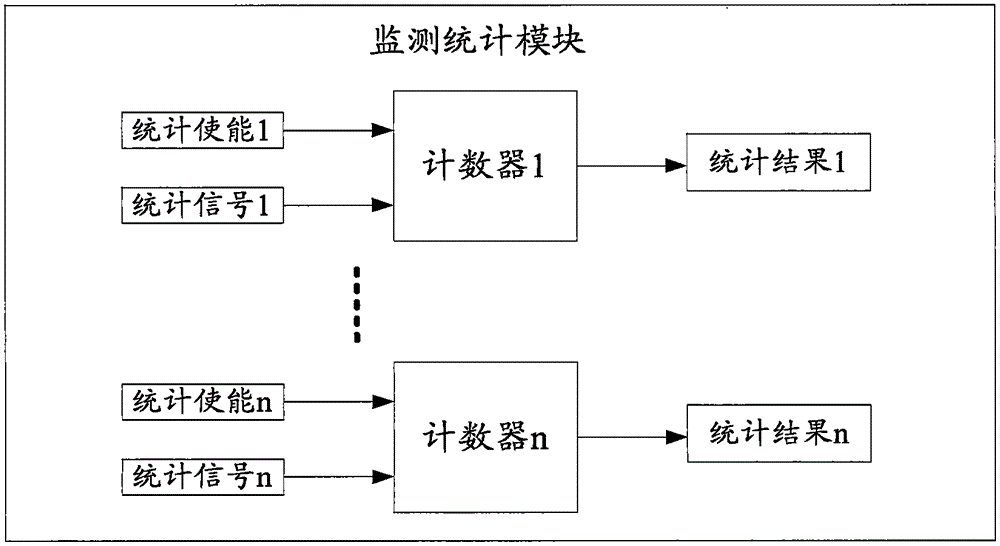

[0024] A method for monitoring and counting bottom-level hardware behaviors provided by an embodiment of the present invention mainly includes: mounting a monitoring and statistics module on a central processing unit (CPU) bus; the monitoring and statistics module counts and monitors bottom-level hardware behaviors of upper-layer applications And classifying and counting the underlying hardware behaviors of the upper-layer applications to obtain classified statistical data of the underlying hardware behaviors of the upper-layer applications.

[0025] The embodiment of the present invention designs a monitoring and statistics module, which is used to obtain the time distribution of the CPU executing instructions and accessing each hardware module during the operation of the chip, as well as the operating times of the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More