FPGA layout method and macro element

A wiring method and layout technology, which is applied in the field of FPGA wiring methods and macro cells, can solve the problems of large memory consumption and increased wiring time, and achieve the effects of reducing wiring time, reducing the number of nodes, and reducing memory consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

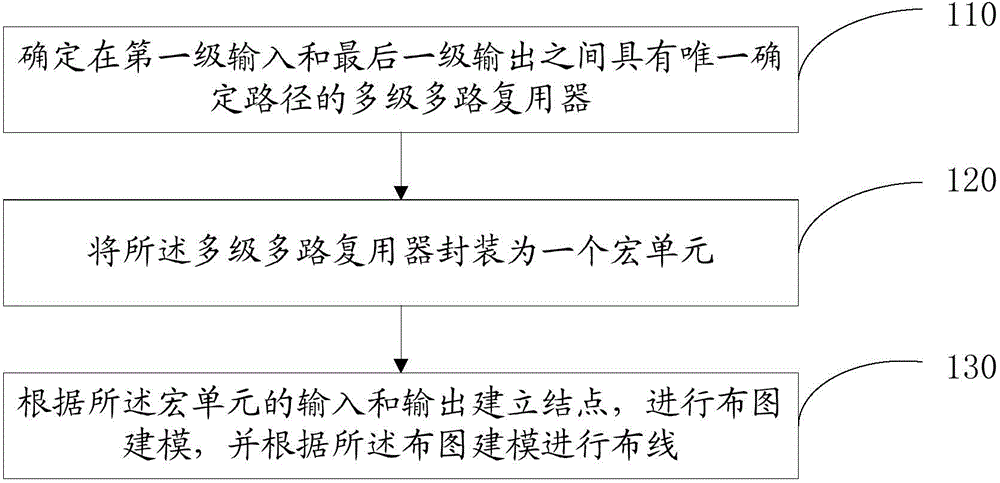

[0023] figure 1 A kind of FPGA wiring method that the embodiment of the present invention provides, described method comprises:

[0024] Step 110, determining a multistage multiplexer with a uniquely determined path (PATH) between the first stage input and the last stage output;

[0025] Wherein, the multi-stage multiplexer includes at least two stages of multiplexers, and each stage of multiplexers includes one or more multiplexers;

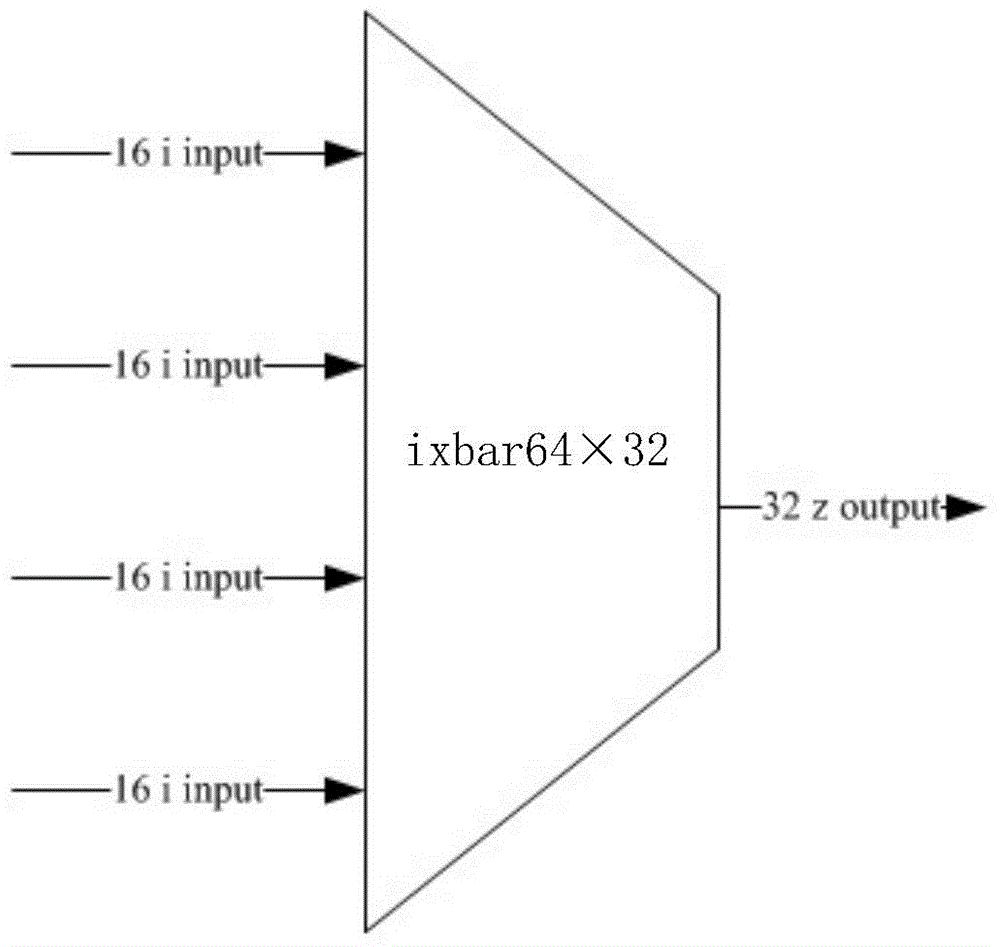

[0026] A case where a multi-stage multiplexer has a uniquely determined path between the input of the first stage and the output of the last stage may be an input crossbar matrix (ixbar) structure composed of multiplexers.

[0027] figure 2 Shown is a specific example of an input crossbar matrix (ixbar) structure with two stages of multiplexers.

[0028] Among them, the first level ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com