Highly-efficient interconnected system capable of configuring chips and realization system thereof and device

An interconnected system and high-efficiency technology, applied in the field of system-on-chip, can solve problems such as adverse power consumption and cost control, increased bus protocol overhead, design and verification impact, etc., to save design time, reduce power consumption, and optimize delays. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

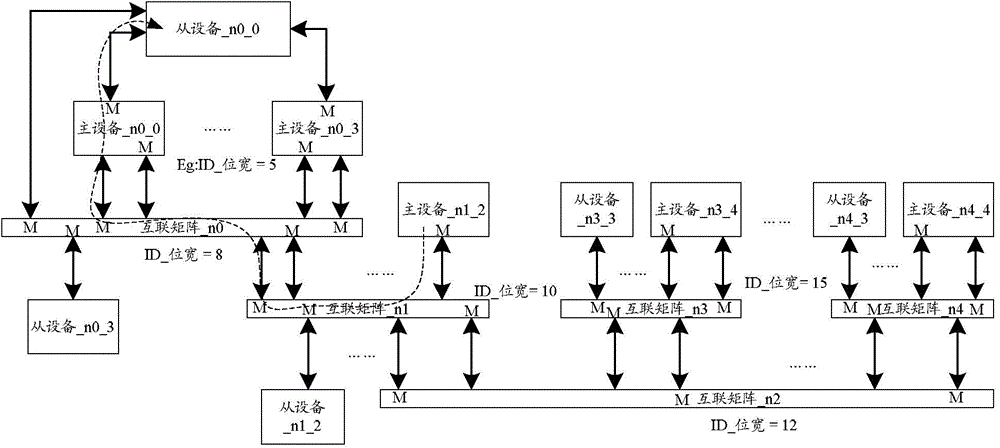

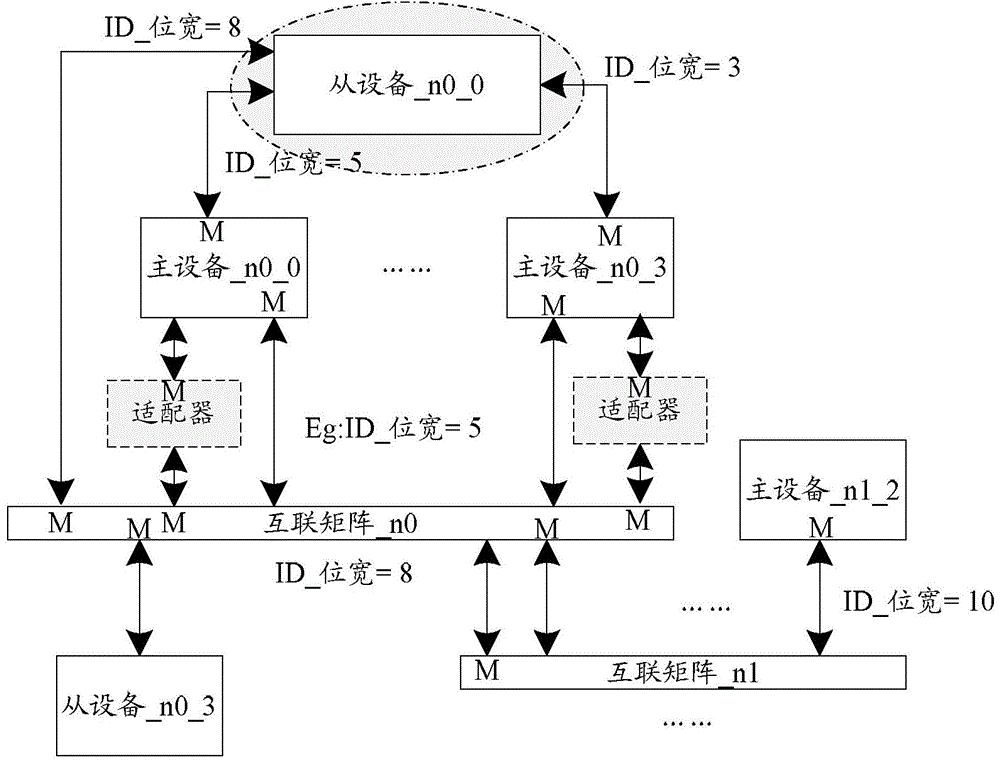

[0034] For the convenience of description, the existing interconnection system adopting ID bit width incremental mode and its communication method are described below.

[0035] Here, the devices connected to the bus (not limited to devices, may also be subsystems) are referred to as components. figure 1 The M shown in the figure represents the master device interface, and the other end of the double-headed arrow represents the slave device interface; some components on the system have only the master device interface, some have only the slave device interface, and some have both master and slave device interfaces. The master device interface for accessing the master device_n0_0 does not need to be interconnected through the Matrix or the Crossbar, therefore, the master device_n0_0 is not included in the scope of interconnected master devices.

[0036] figure 1 Among all the master device interfaces above, it is assumed that the master device _n0_0 has the most different reque...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More