A FPGA-based system timing device and timing method

A time and internal clock technology, applied in the direction of generating/distributing signals, etc., can solve the same problem of card timing, and achieve the effect of high accuracy, high precision and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0023] The application principle of the present invention will be described in detail below in conjunction with the accompanying drawings.

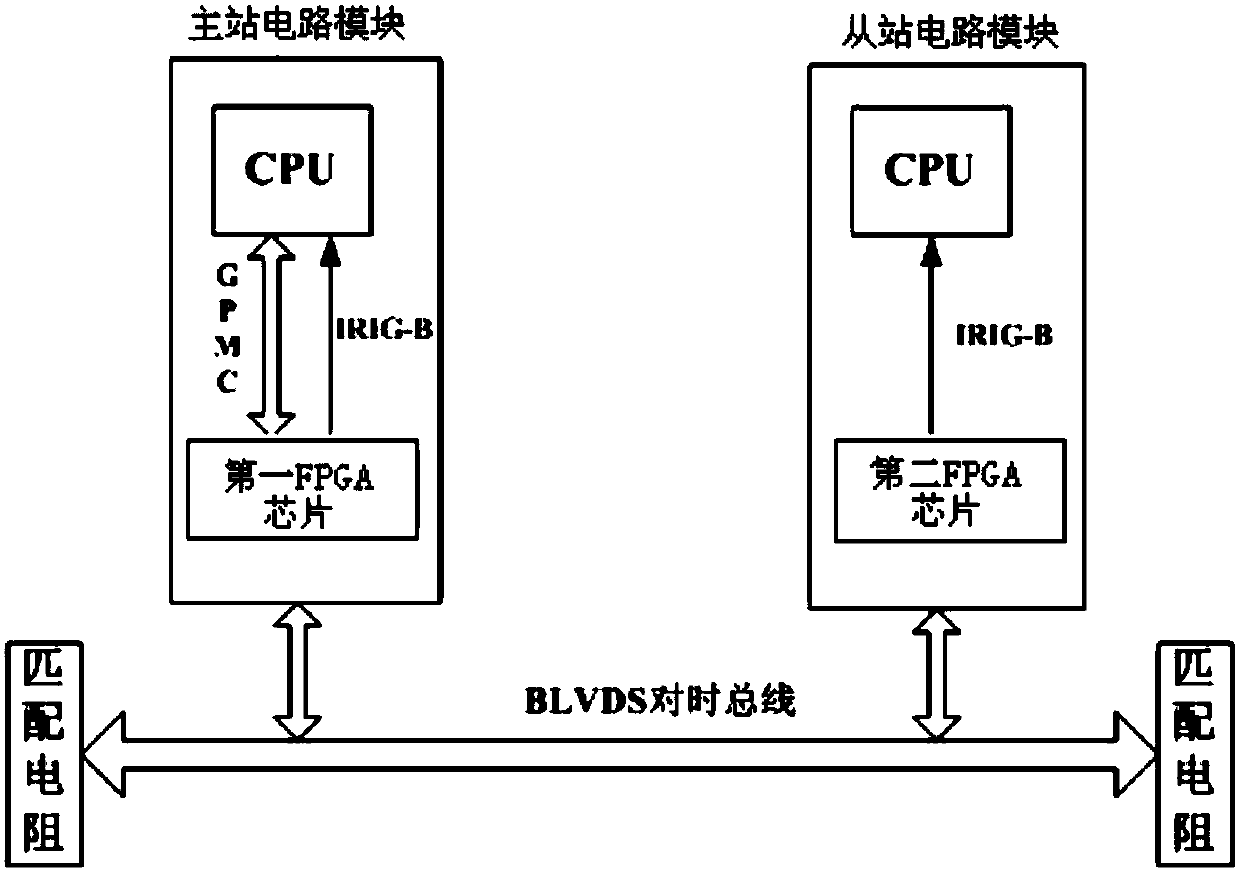

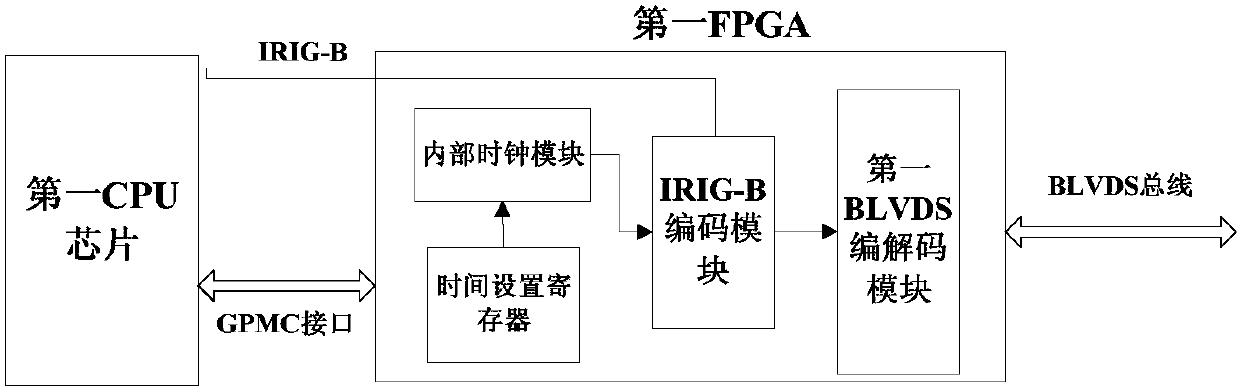

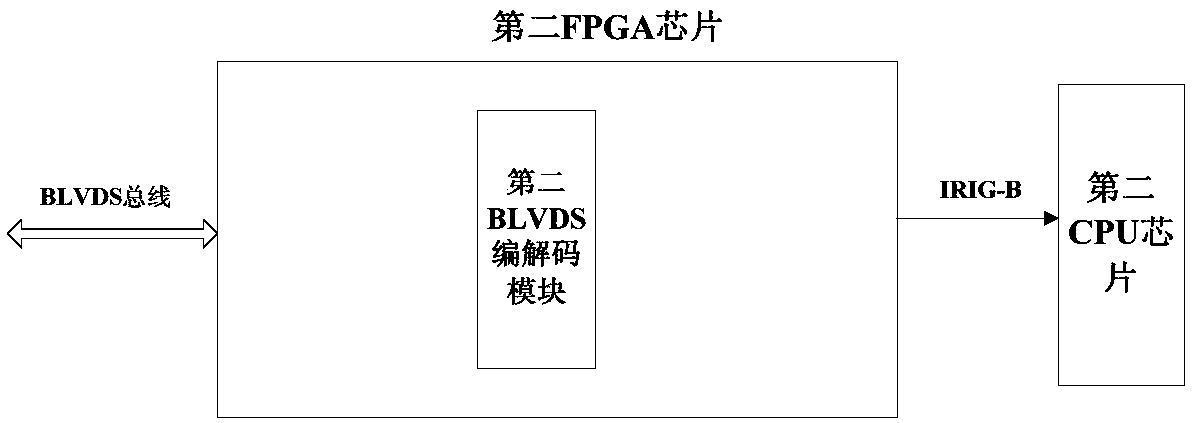

[0024] A system timing device based on FPGA, comprising a master station circuit module and a plurality of slave station circuit modules; the master station circuit module and a plurality of slave station circuit modules are electrically connected by a BLVDS bus; the master station circuit module includes sequentially Connected CPU chip, GPMC interface and the first FPGA chip, the first FPGA chip includes the time setting register, internal clock module, IRIG-B coding module and the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More