System and method for multi-mode e1 interface service processing

A business processing, multi-mode technology, applied in the field of communication, can solve the problem of lack of flexibility and high scalability design module

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

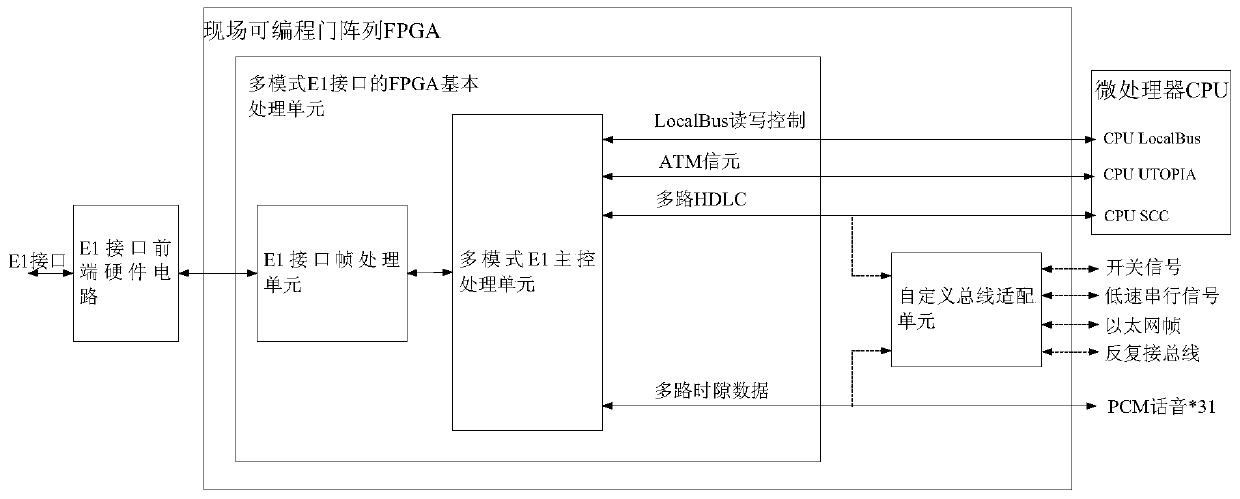

[0061] Such as figure 1 As shown, the present embodiment provides a system for multi-mode E1 interface service processing, and the realization hardware of the system in the E1 interface equipment includes the field programmable gate array FPGA, the microprocessor CPU and the front-end hardware circuit of the E1 interface. part;

[0062] The E1 interface front-end hardware is a standard circuit device of the E1 interface, which can realize the encoding and decoding of the E1 interface front-end AMI code and HDB3 code level;

[0063] Described Field Programmable Gate Array FPGA comprises the FPGA basic processing unit of multi-mode E1 interface and self-defined bus adaptation unit;

[0064] The microprocessor CPU mainly provides subsequent processing of some services (such as ATM, HDLC, etc.) and performs register operation configuration on the FPGA basic processing unit of the multi-mode E1 interface.

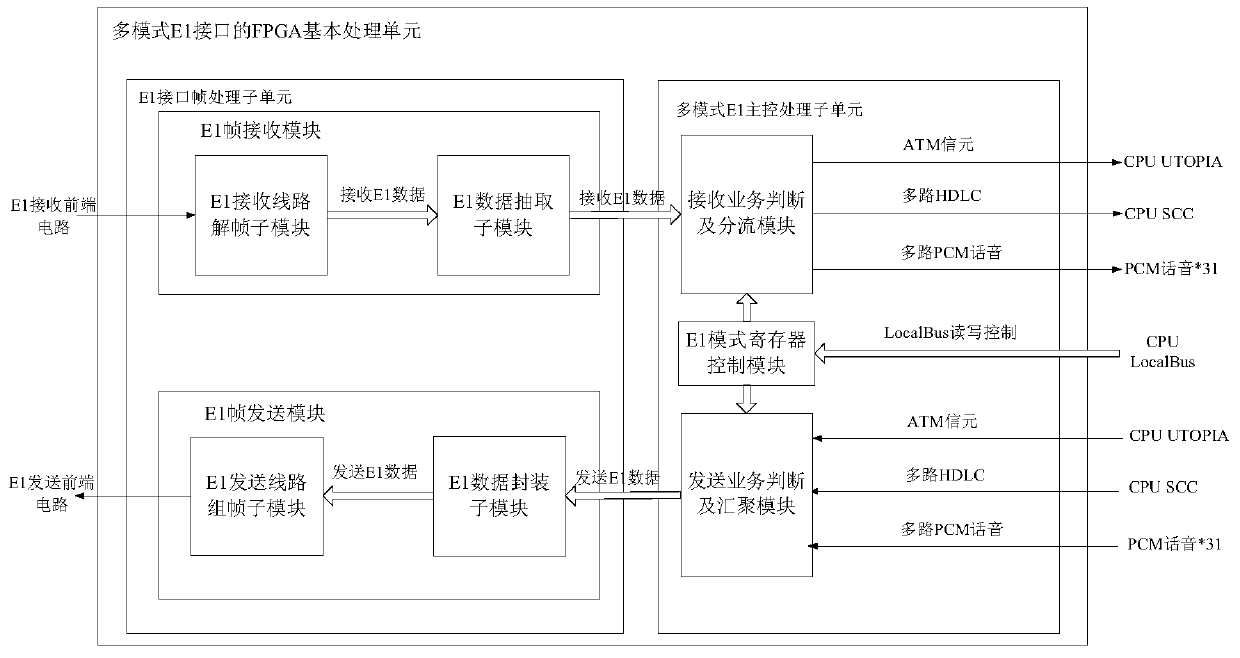

[0065] In the FPGA basic processing unit of the multi-mode E1 interface, ...

Embodiment 2

[0084] The present embodiment provides a kind of method of multi-mode E1 interface business processing, and this method is realized based on the system of above-mentioned embodiment 1, comprises the following steps:

[0085] S1. Implement a compatible E1 interface frame processing subunit inside the FPGA device behind the E1 interface front-end hardware circuit to realize E1 non-framing / framing / multi-framing frame processing;

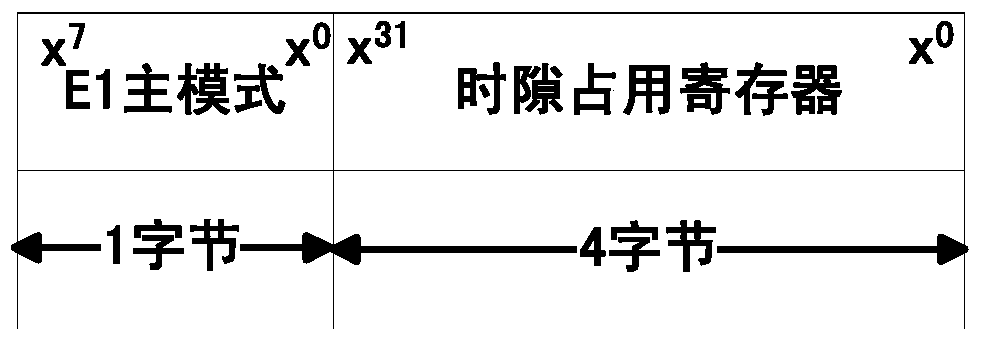

[0086] S2, in the multi-mode E1 main control processing subunit, through the register soft switch inside the FPGA, the 32 road time slots of the E1 frame are carried out to the marking process of the business mode, and the data of each frame is extracted according to the corresponding marking of the register soft switch. Connect to the corresponding processing modules and aggregate them into the final business flow data;

[0087] S3. According to the current business needs, it is necessary to provide standard E1 interface (PCM30 / 31), E1UNI mode (transmi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More