Static superscale DSP cycle simulation method

A simulation method and superscalar technology, applied in the field of DSP cycle simulation, can solve the problems of inaccuracy and slow speed of DSP simulation method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

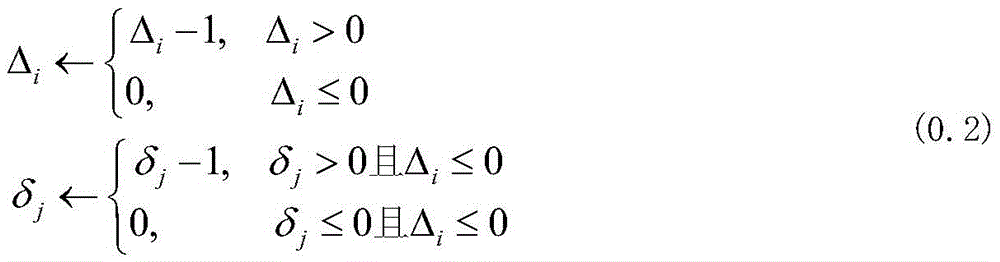

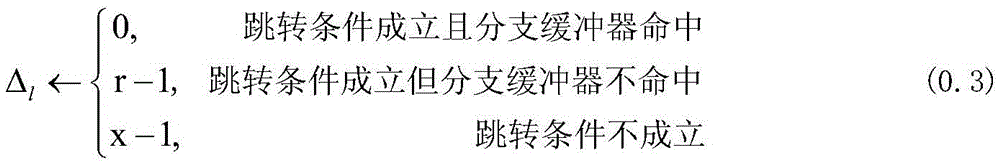

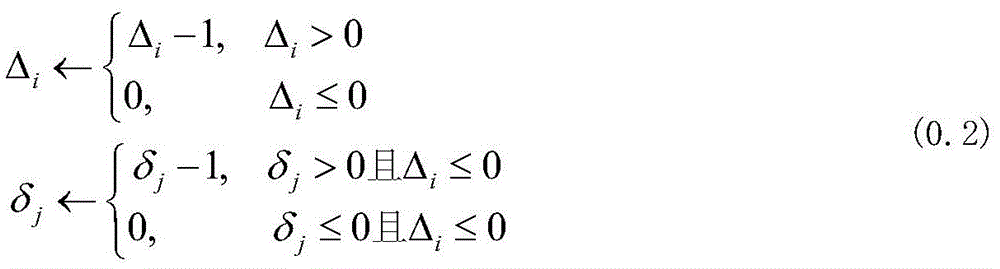

[0031] The specific steps of a static superscalar DSP cycle simulation method are:

[0032] Take the static superscalar DSP TS101 of ADI's 8-stage pipeline as an example,

[0033] The first step is to build a static superscalar DSP cycle simulation system

[0034] Static superscalar DSP cycle simulation system, including instruction preparation module and instruction execution module.

[0035] The functions of the instruction preparation module are: analyze the control flow relationship and data flow relationship between instructions, control the instruction sequence and pipeline progress entering the pipeline, and realize the simulation of DSP instruction timing, that is, the simulation of TS101 instruction timing.

[0036] The functions of the instruction simulation module are: translate the instruction semantics, update the DSP software visible register status and internal pipeline status, and realize the simulation of the DSP instruction set function, that is, the simulat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More