Patents

Literature

165 results about "Bitwise operation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In digital computer programming, a bitwise operation operates on one or more bit patterns or binary numerals at the level of their individual bits. It is a fast and simple action, directly supported by the processor, and is used to manipulate values for comparisons and calculations.

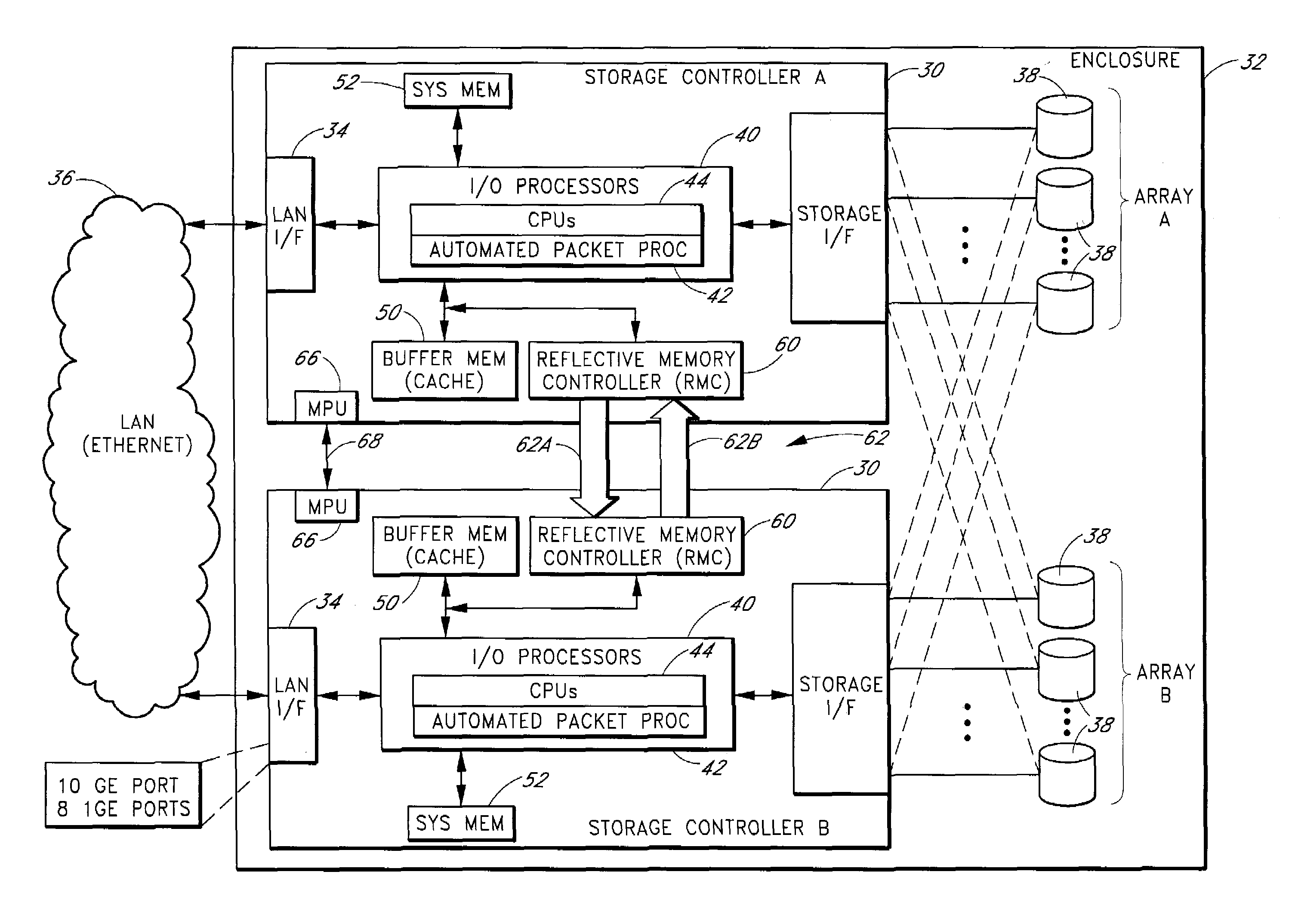

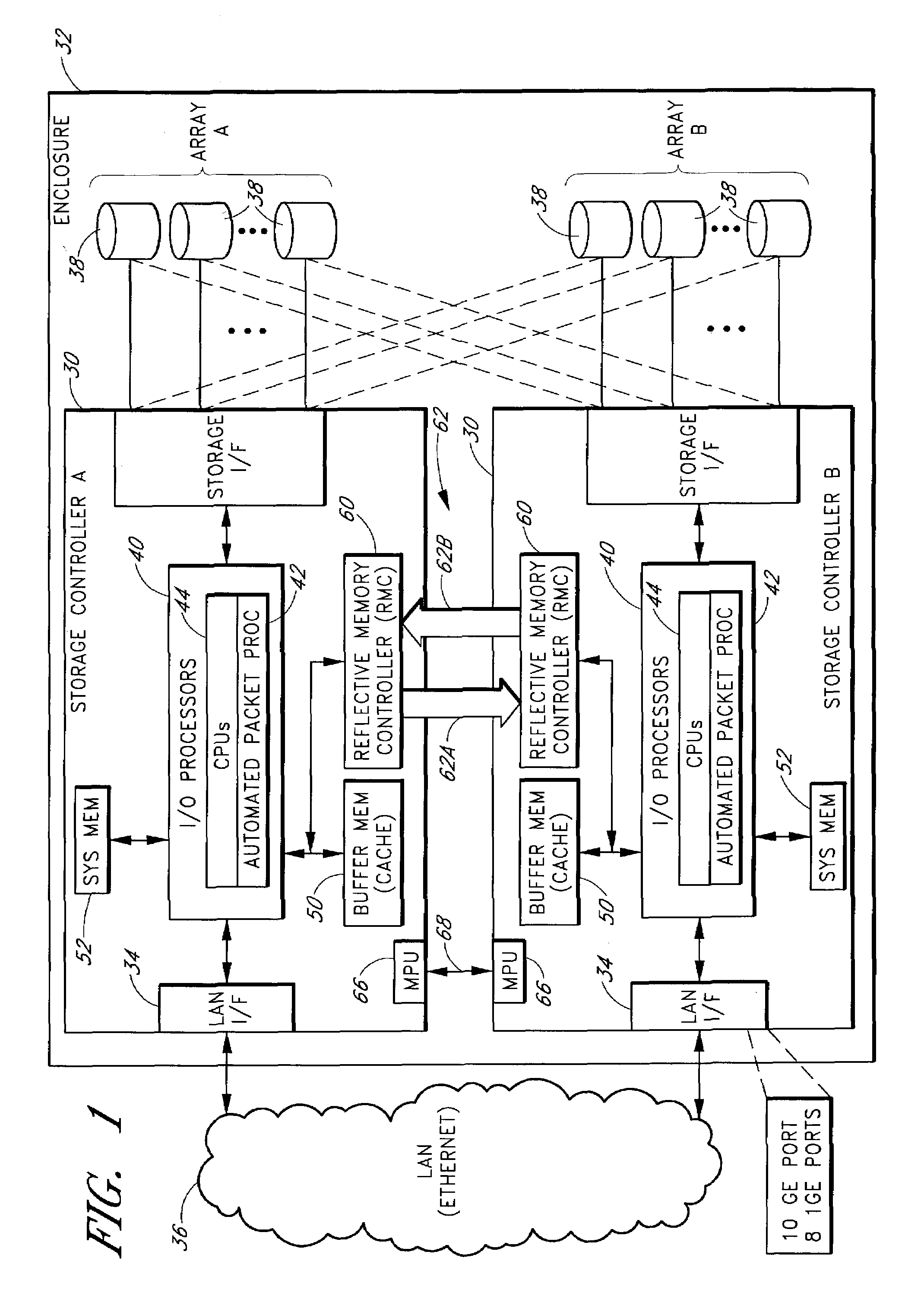

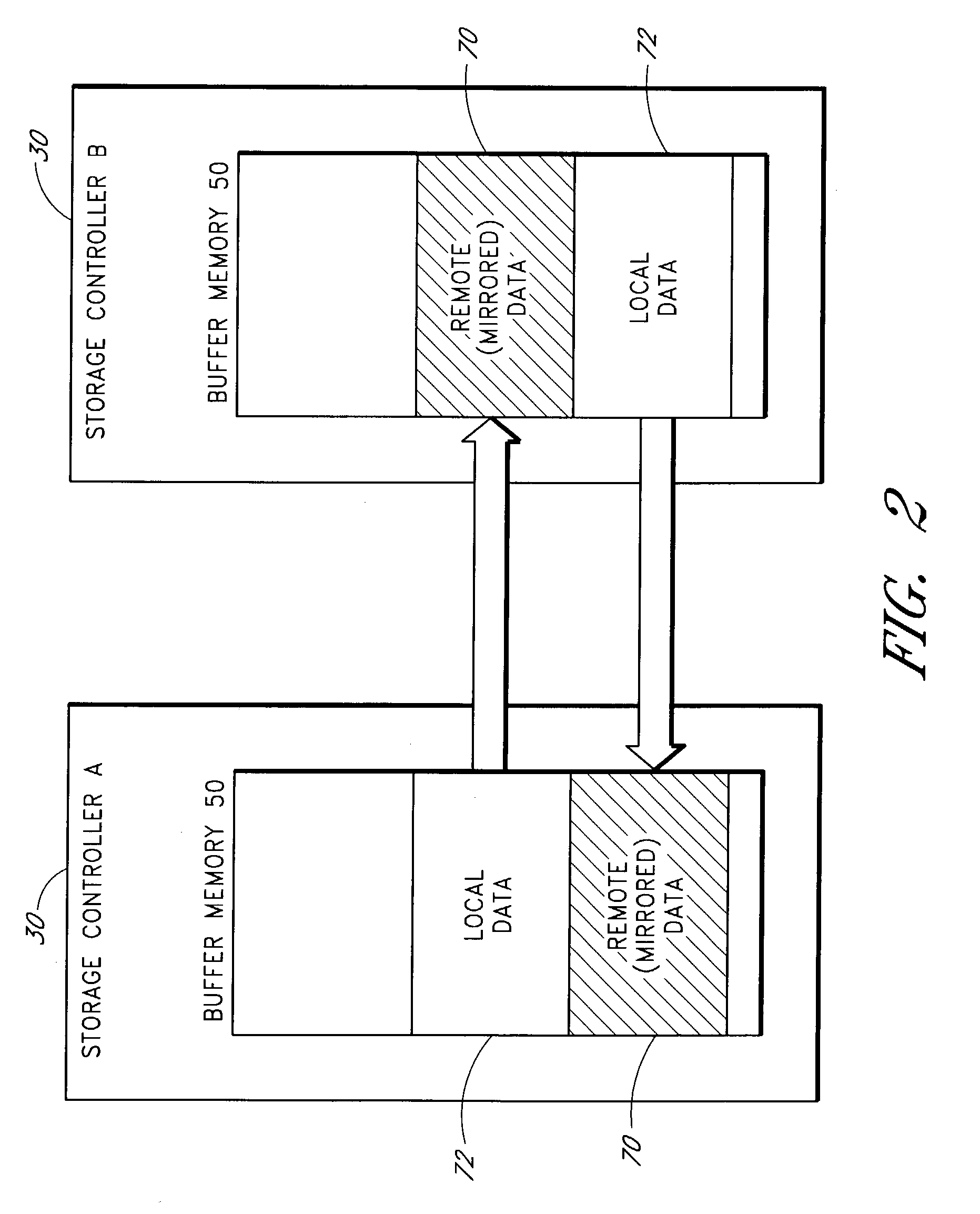

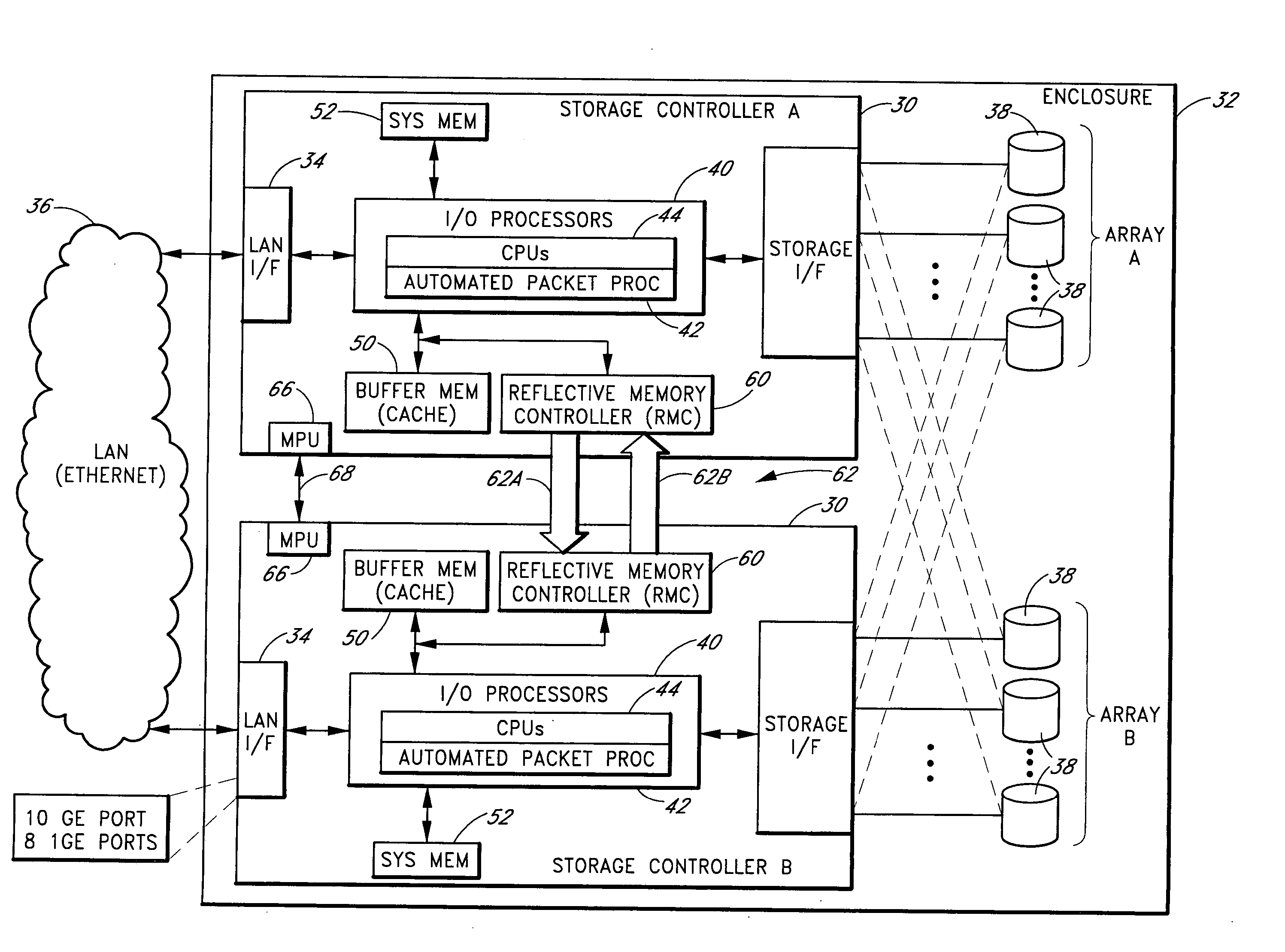

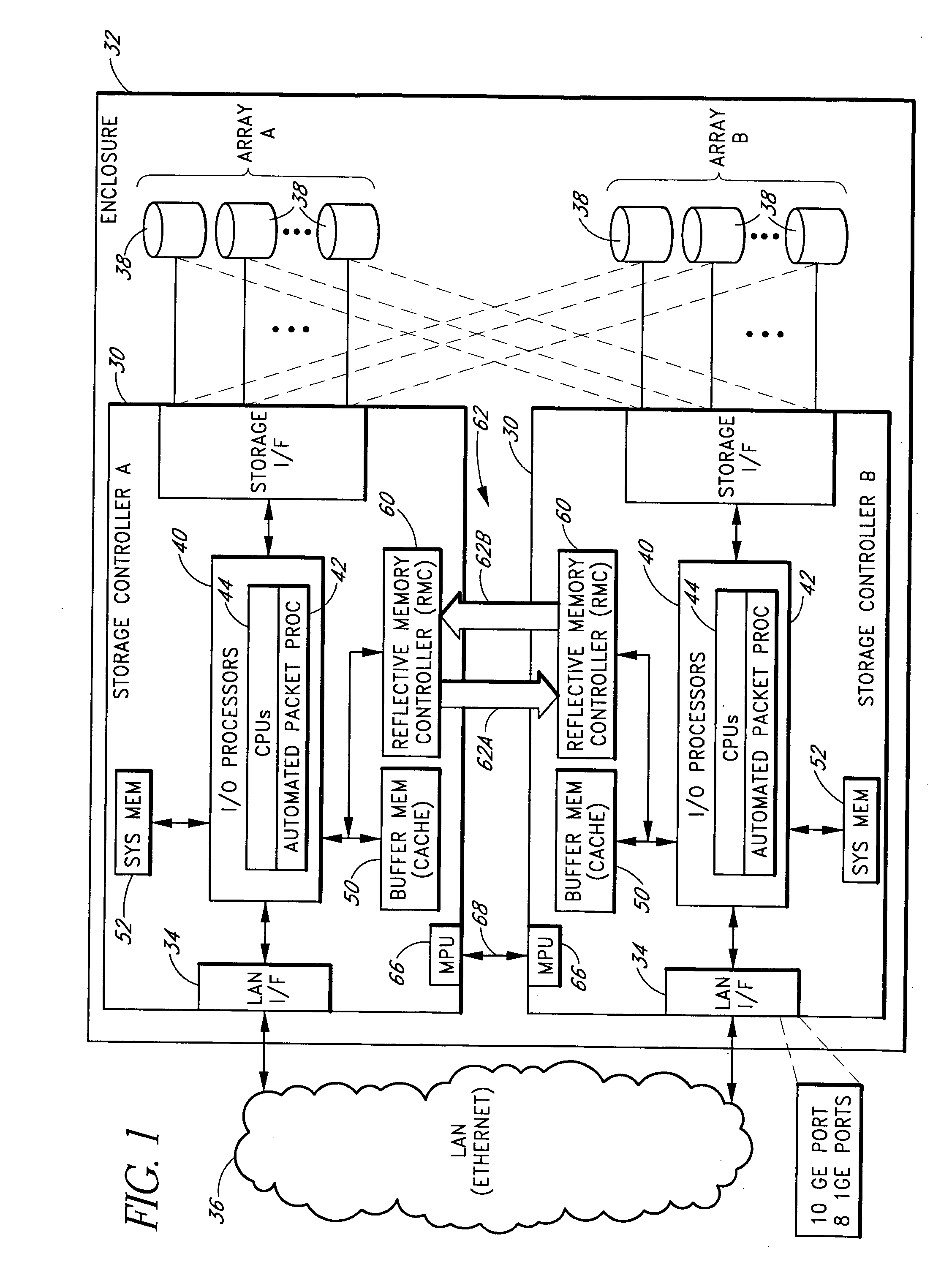

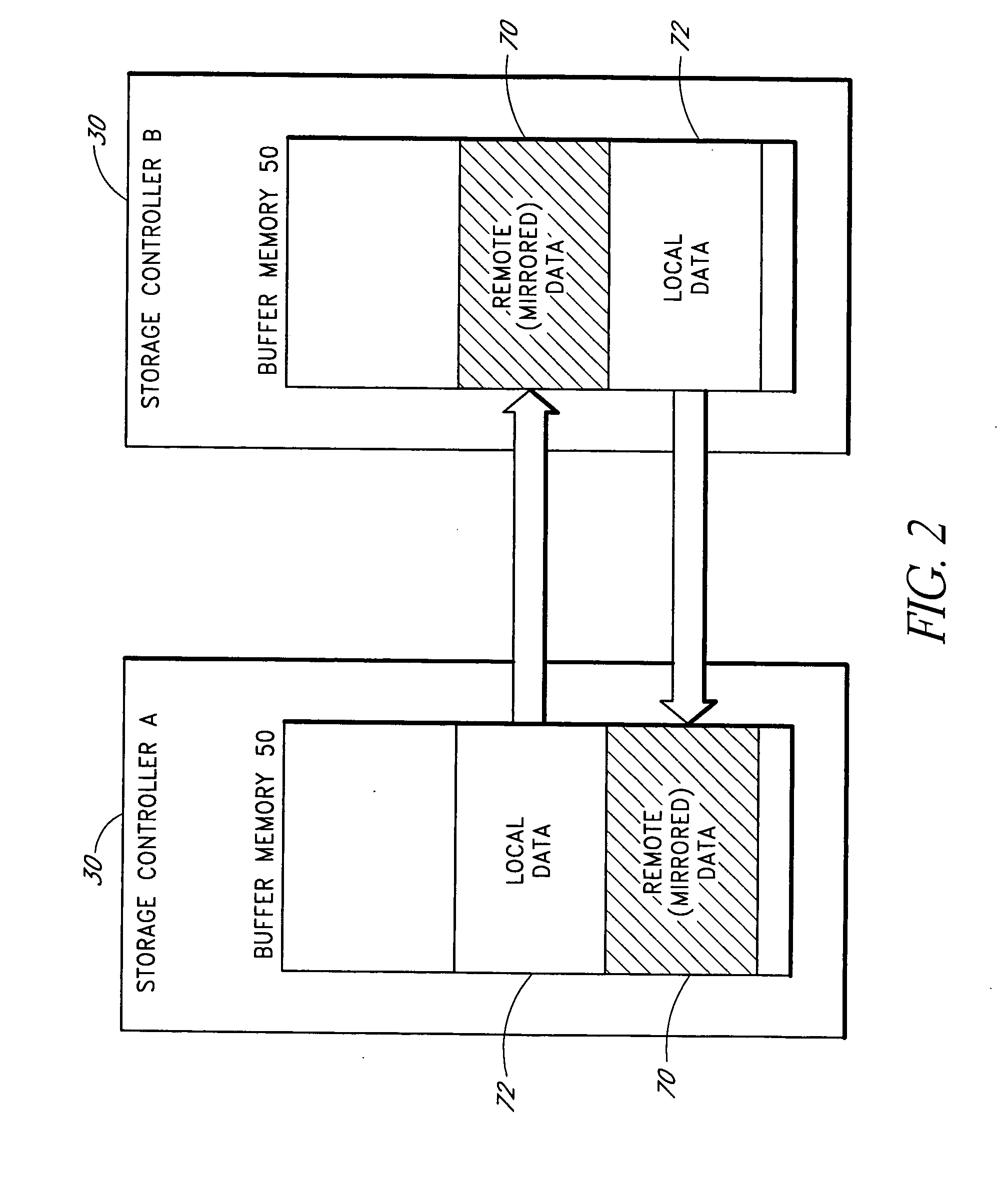

Storage controller redundancy using bi-directional reflective memory channel

InactiveUS6941396B1Reduce protocol overheadRapid generation of packet CRC valuesInput/output to record carriersData processing applicationsError checkingFailover

A bi-directional reflective memory channel between a pair of storage controllers is used to maintain a mirrored copy of each storage controller's native buffer contents within the buffer of the other storage controller. To maintain such mirrored copies, buffer write operations that fall within a reflective memory segment of one storage controller are automatically reflected across this channel to the other storage controller for execution, and vice versa. The write operations are preferably transmitted across the reflective memory channel using a protocol that provides for error checking, acknowledgements, and retransmissions. This protocol is preferably implemented entirely in automated circuitry, so that the mirrored copies are maintained without any CPU intervention during error-free operation. When a failover occurs, the surviving storage controller uses the mirrored copy of the failed storage controller's native buffer contents to assume control over the failed storage controller's disk drives.

Owner:SUPRO STORTEK CO LTD

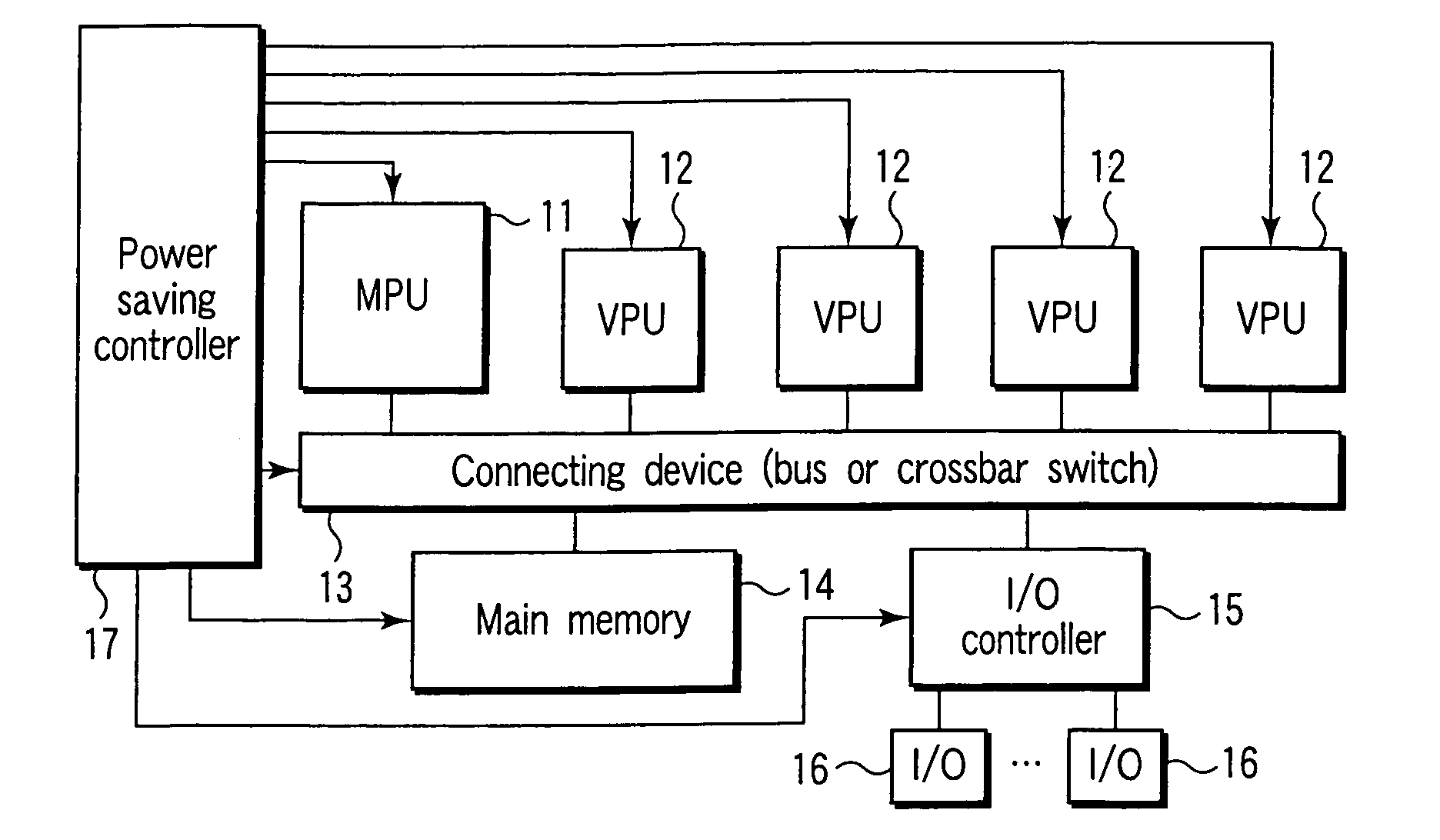

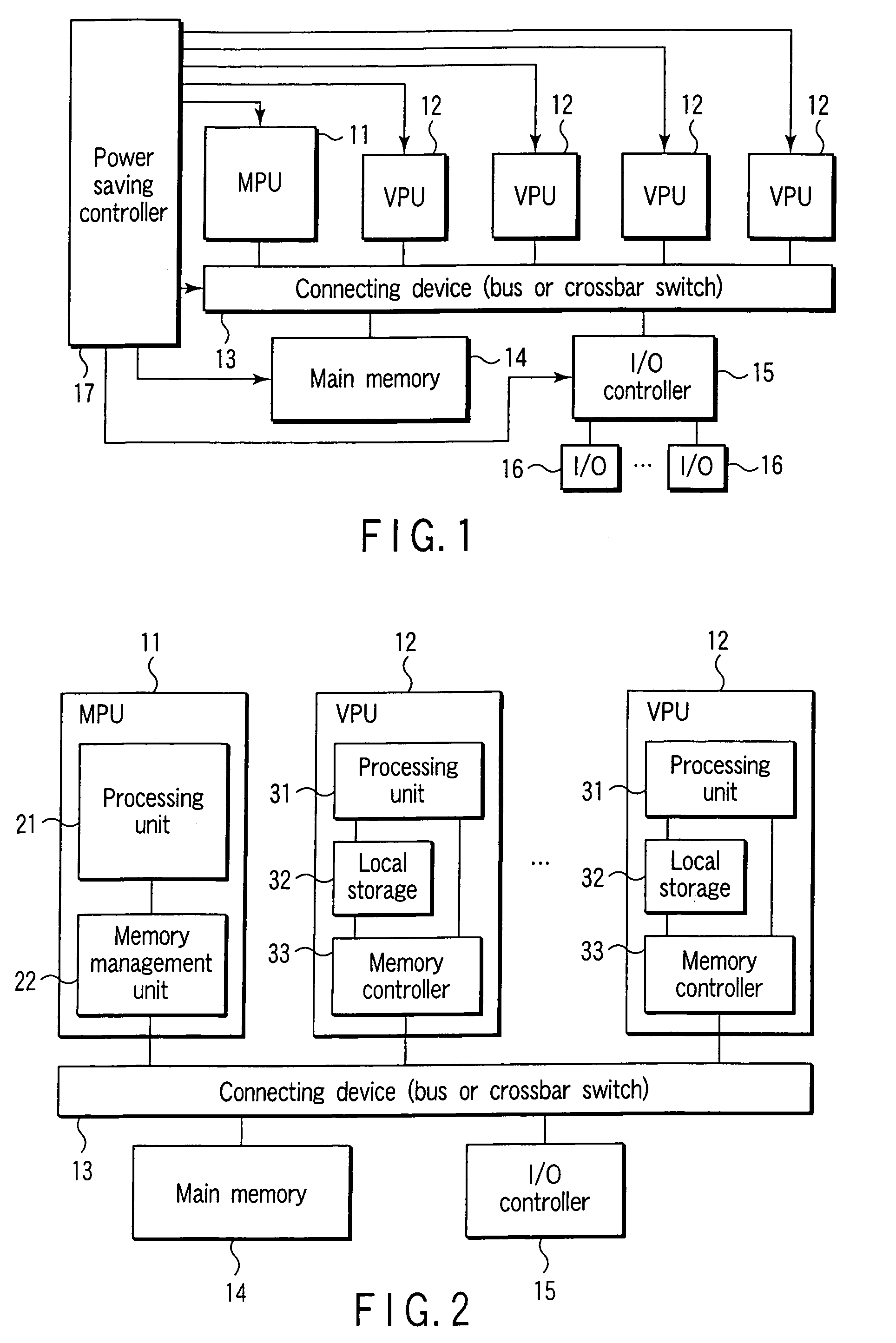

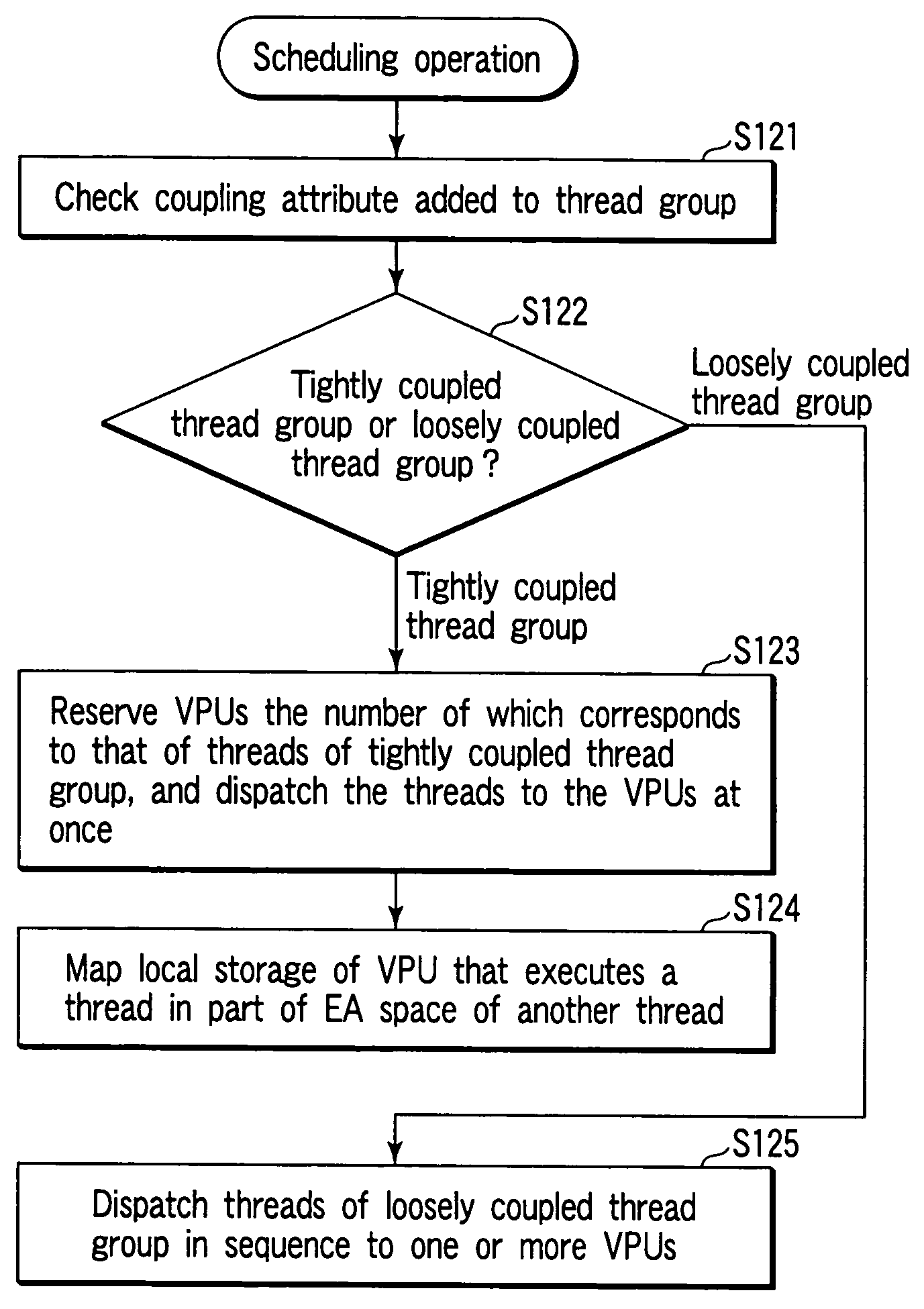

Method and system for performing real-time operation using processors

InactiveUS20040268354A1Resource allocationMultiple digital computer combinationsBitwise operationCoupling

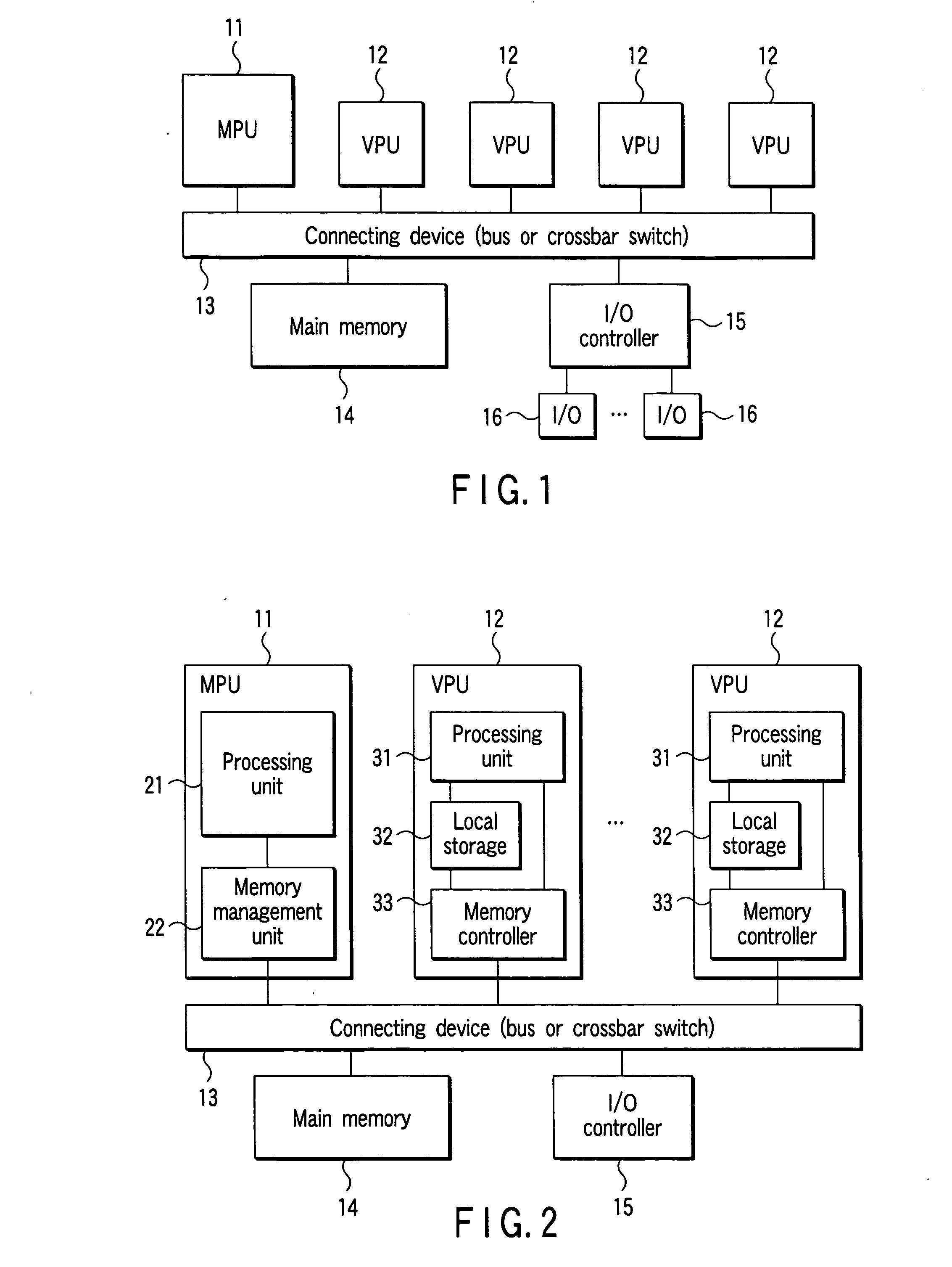

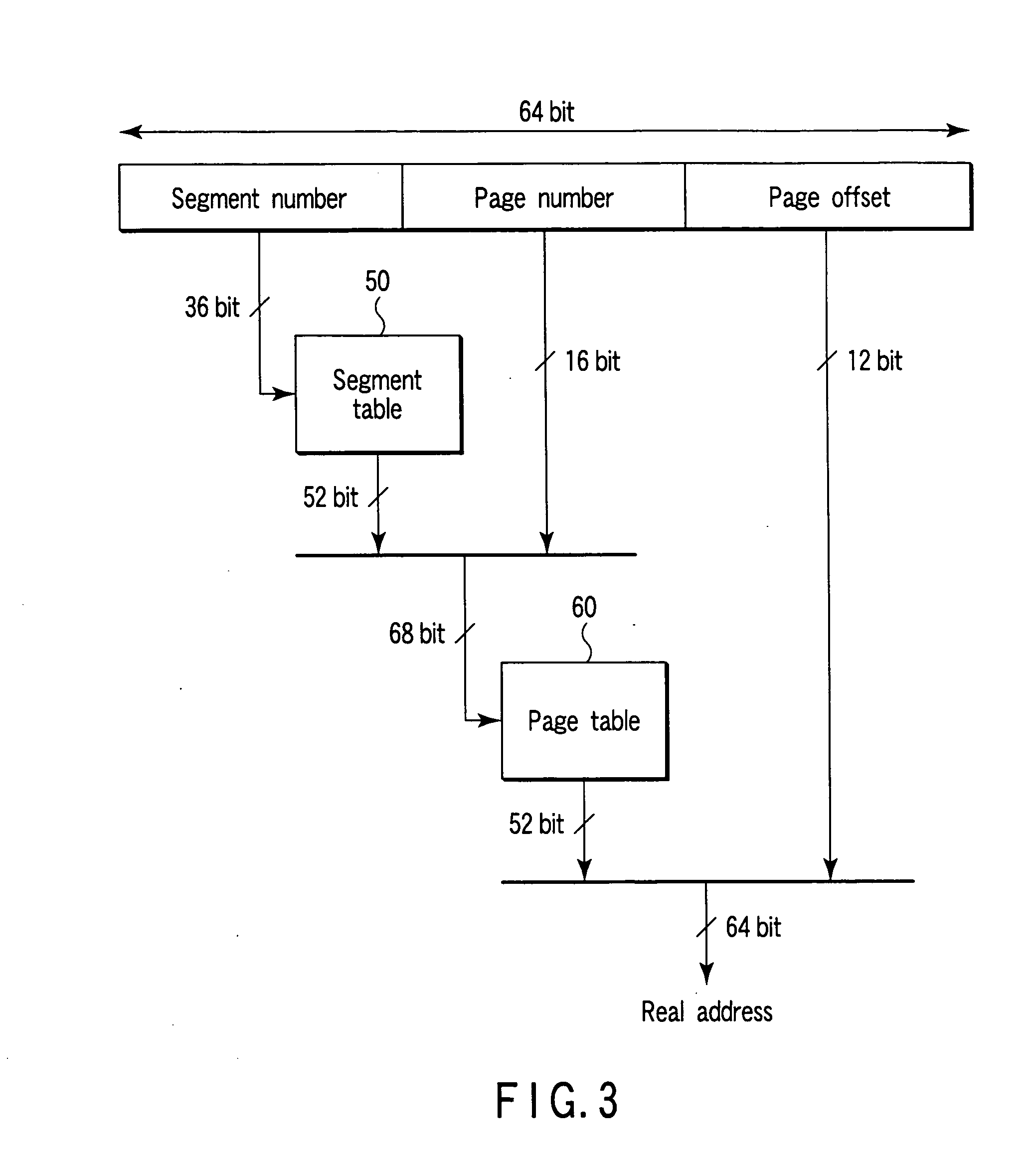

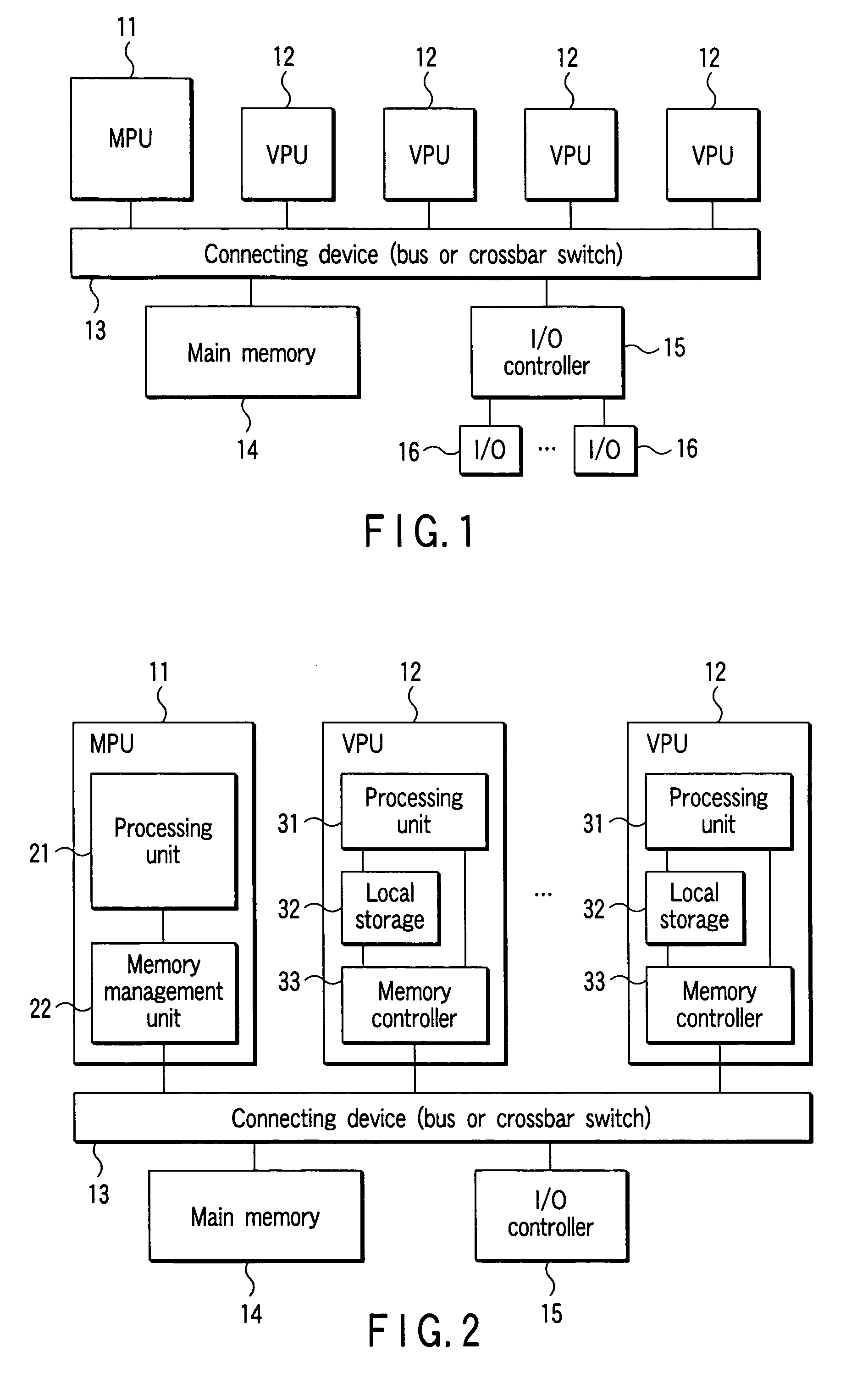

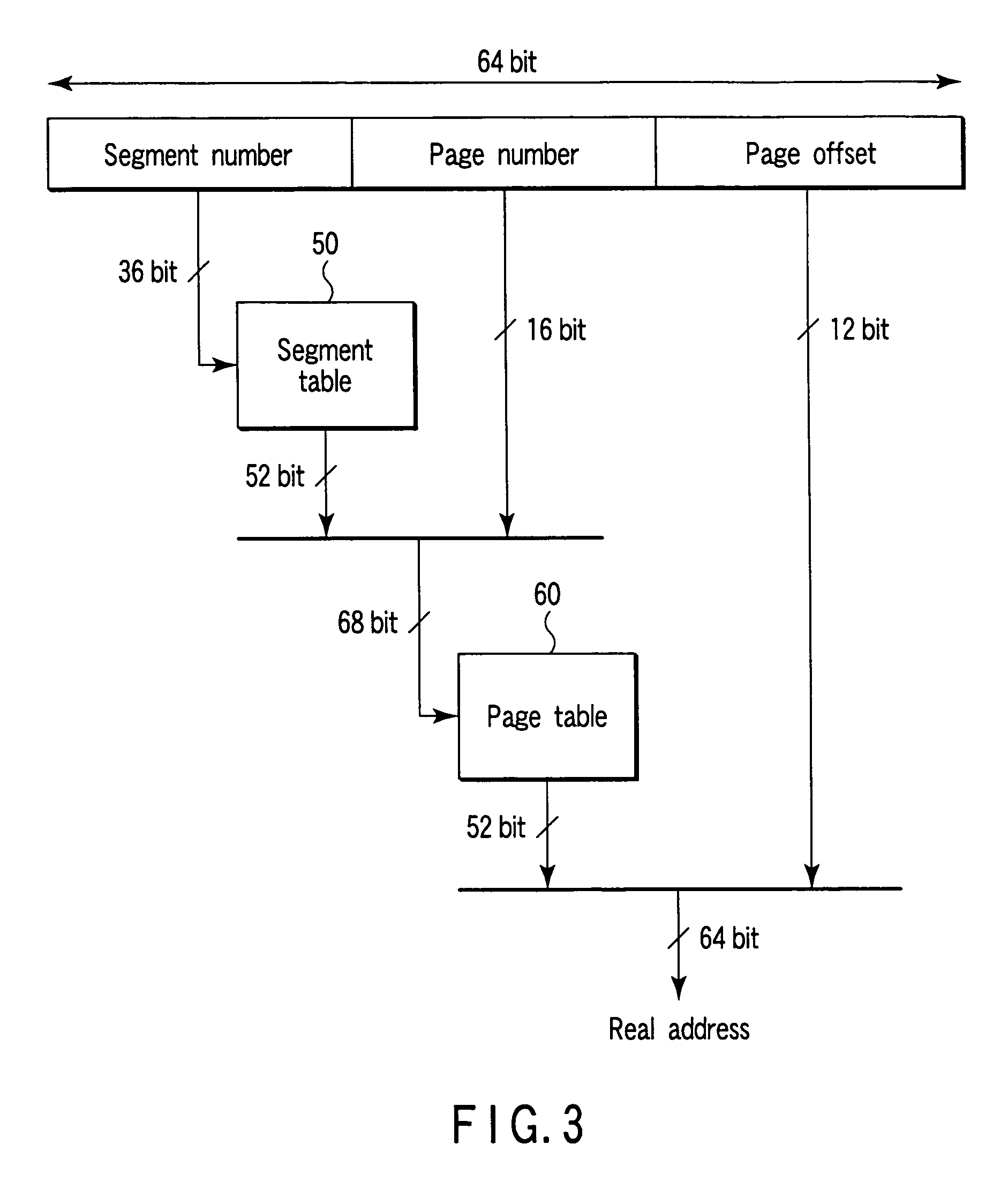

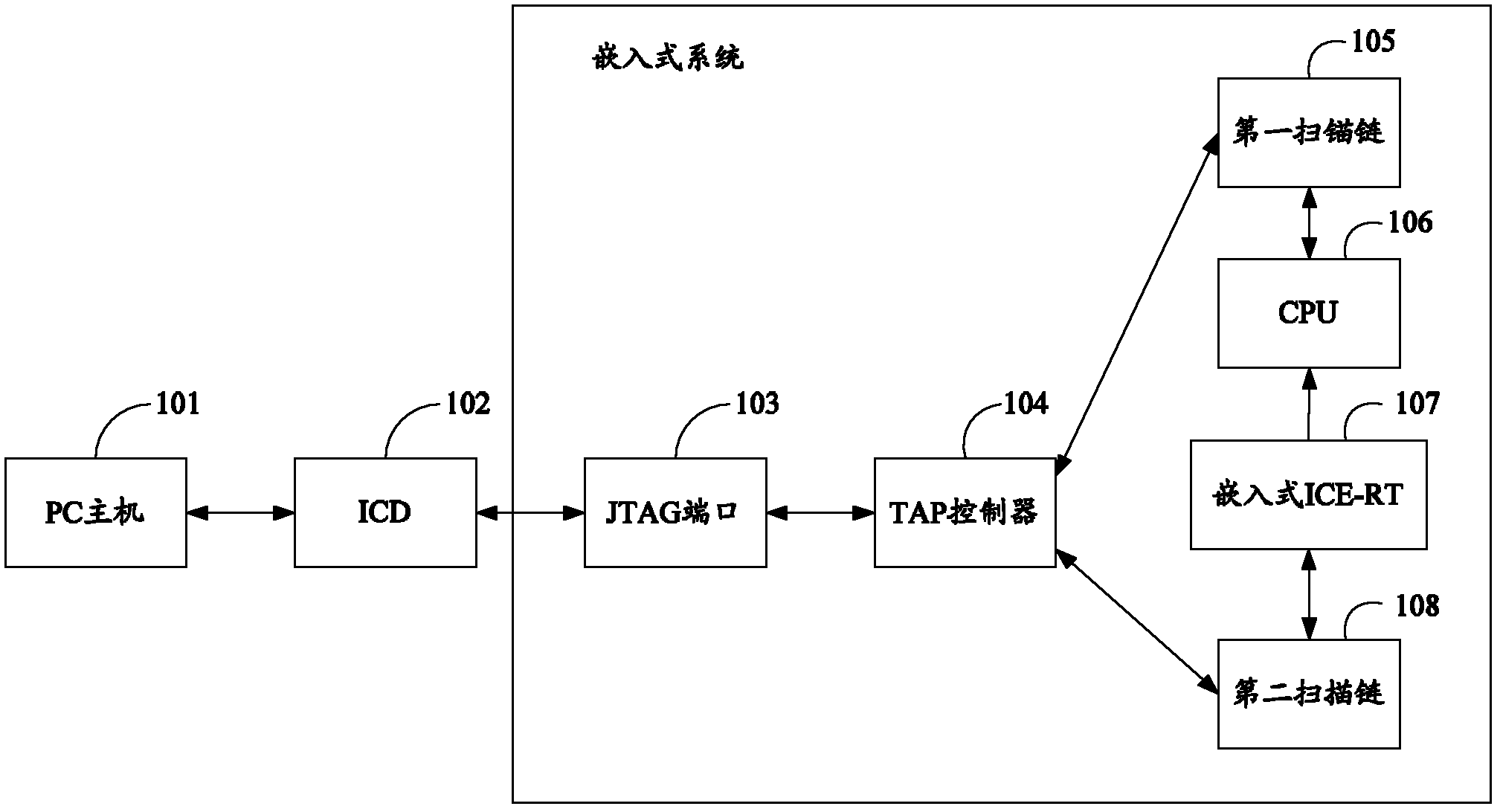

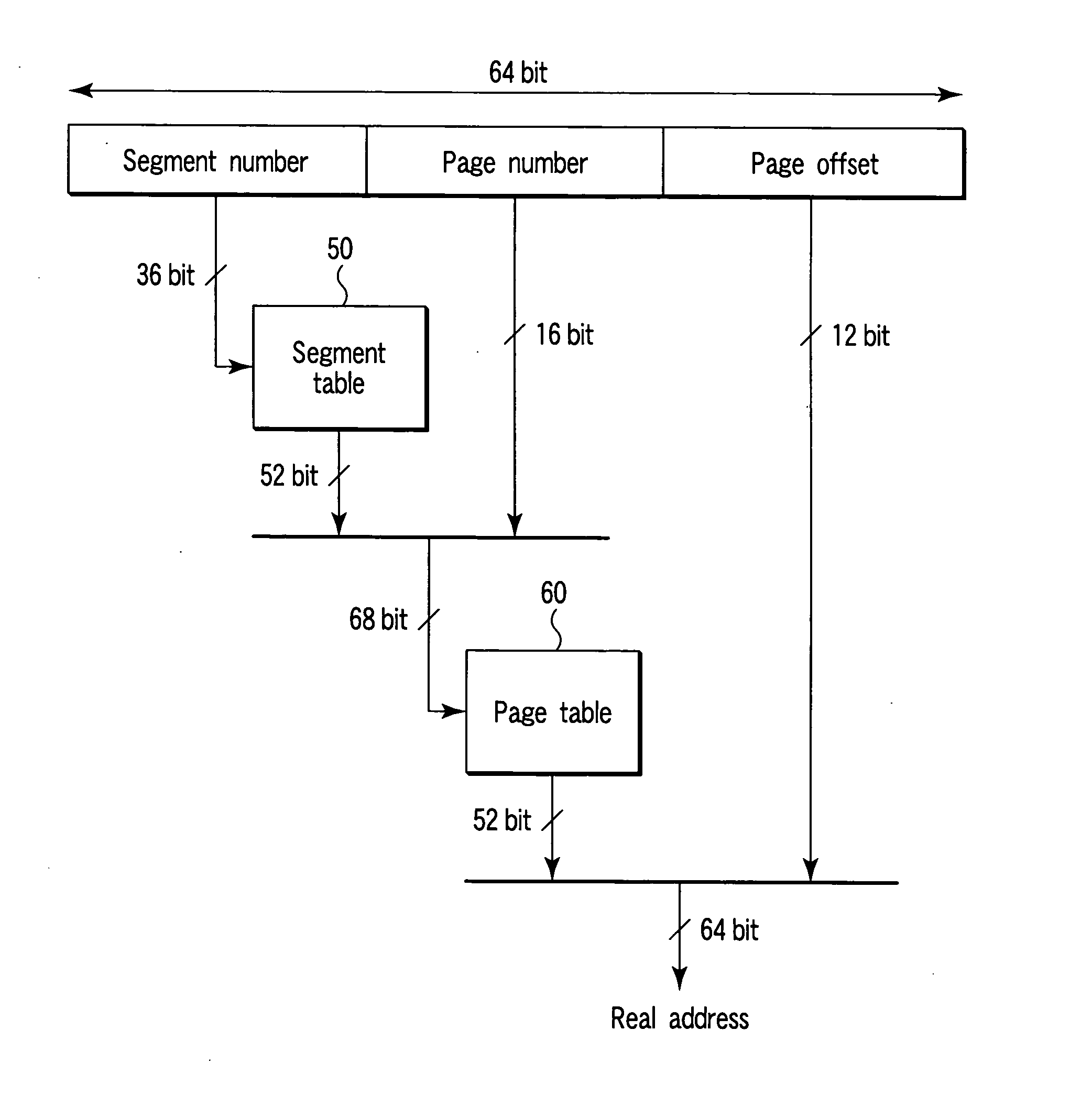

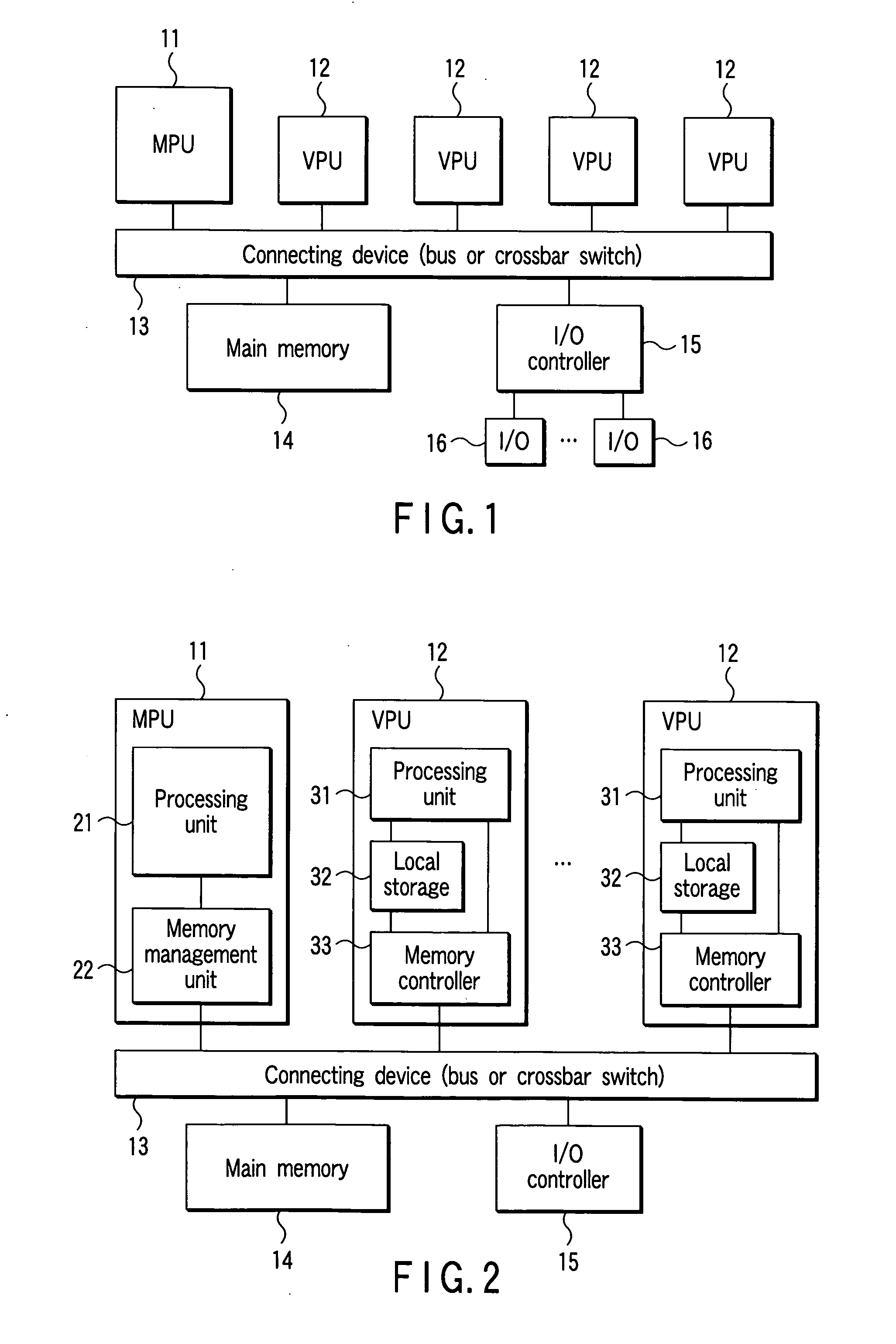

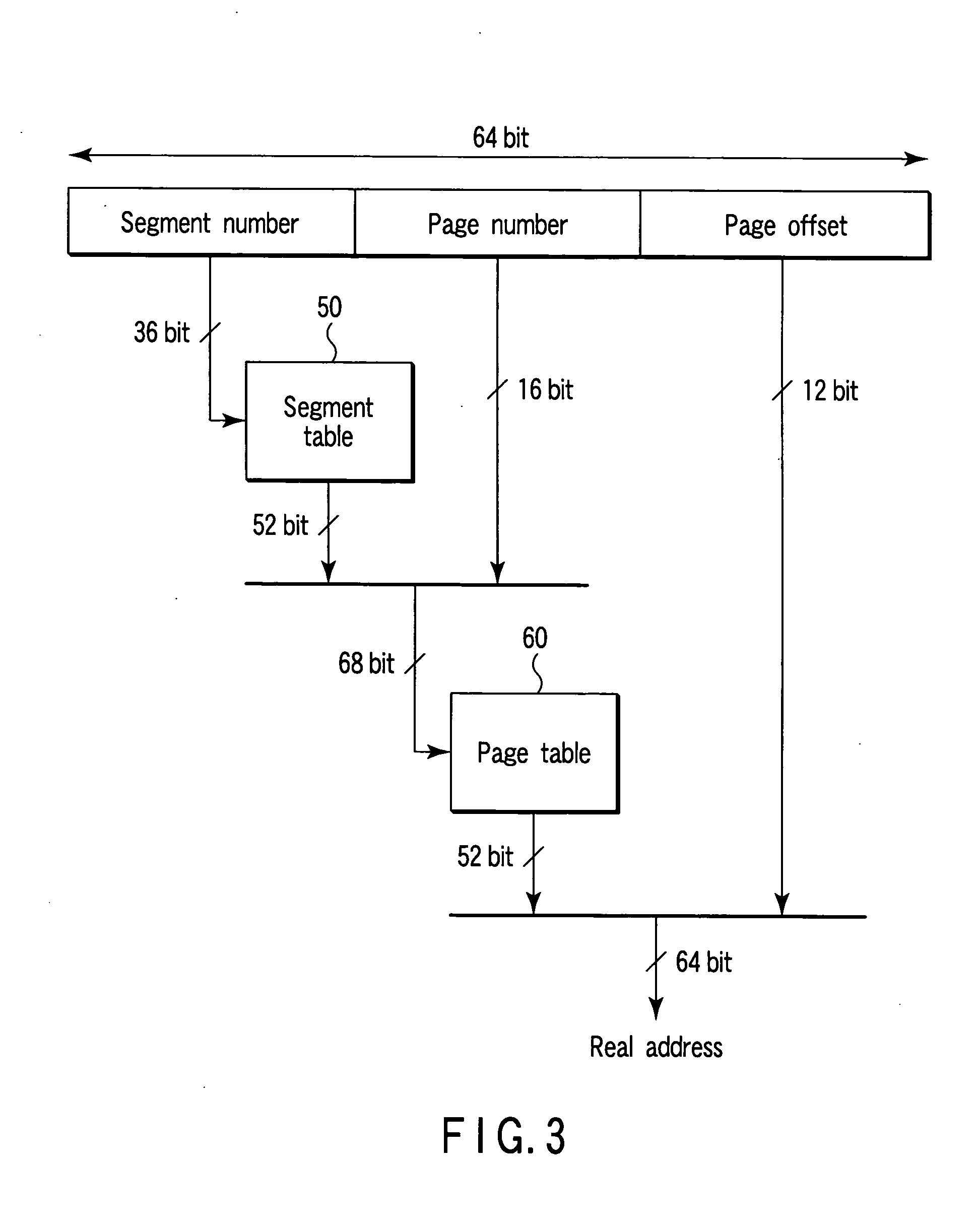

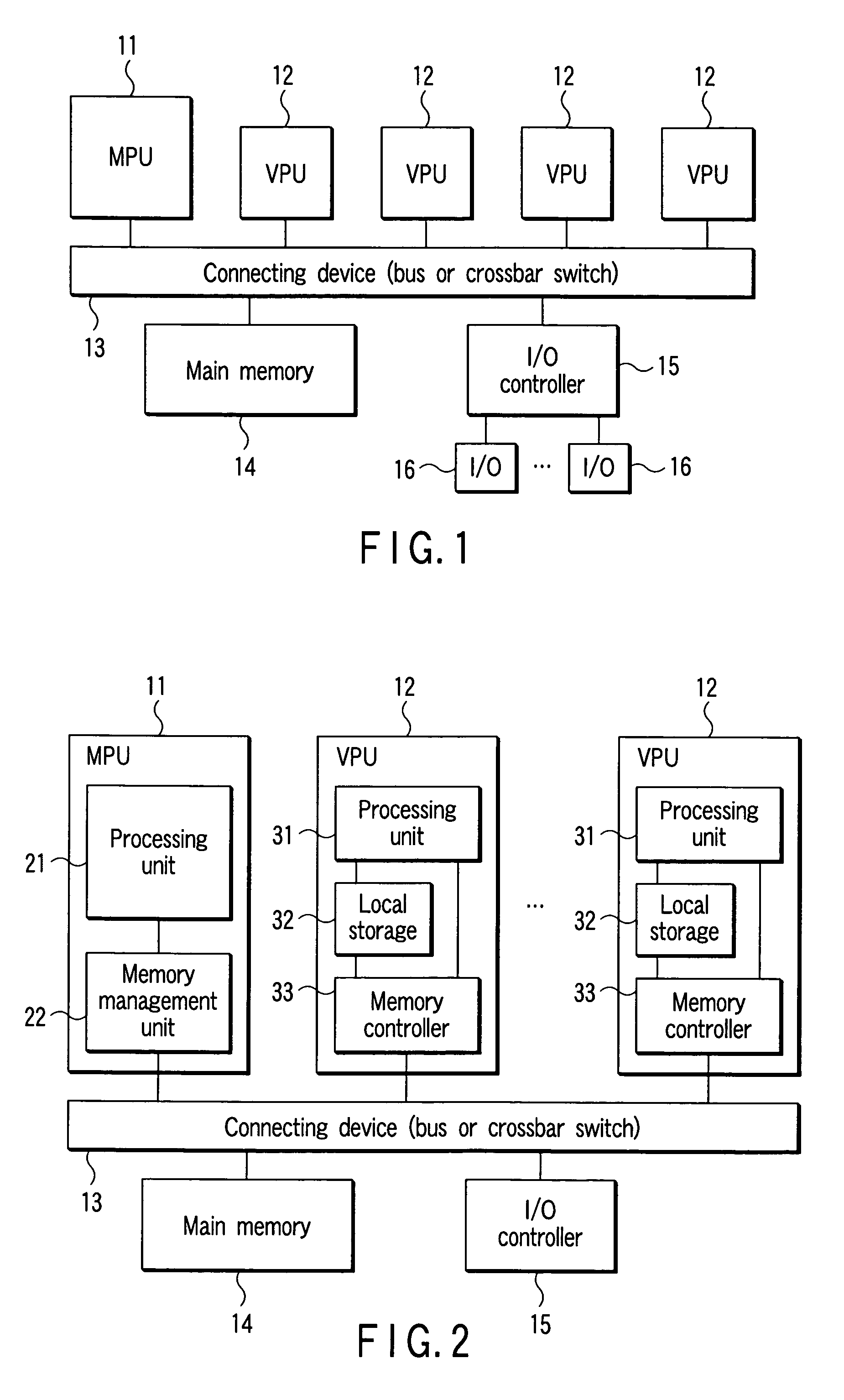

A real-time processing system that executes a plurality of threads, each of the threads being a unit of execution of a real-time operation, comprises a plurality of processors, a unit which selects a tightly coupled thread group from among the threads based on coupling attribute information indicative of a coupling attribute between the threads, the tightly coupled thread group including a set of tightly coupled threads running in cooperation with each other, and a unit which performs a scheduling operation of dispatching the tightly coupled threads to several of the processors that are equal to the tightly coupled threads to simultaneously execute the tightly coupled threads by the several of the processors.

Owner:KK TOSHIBA

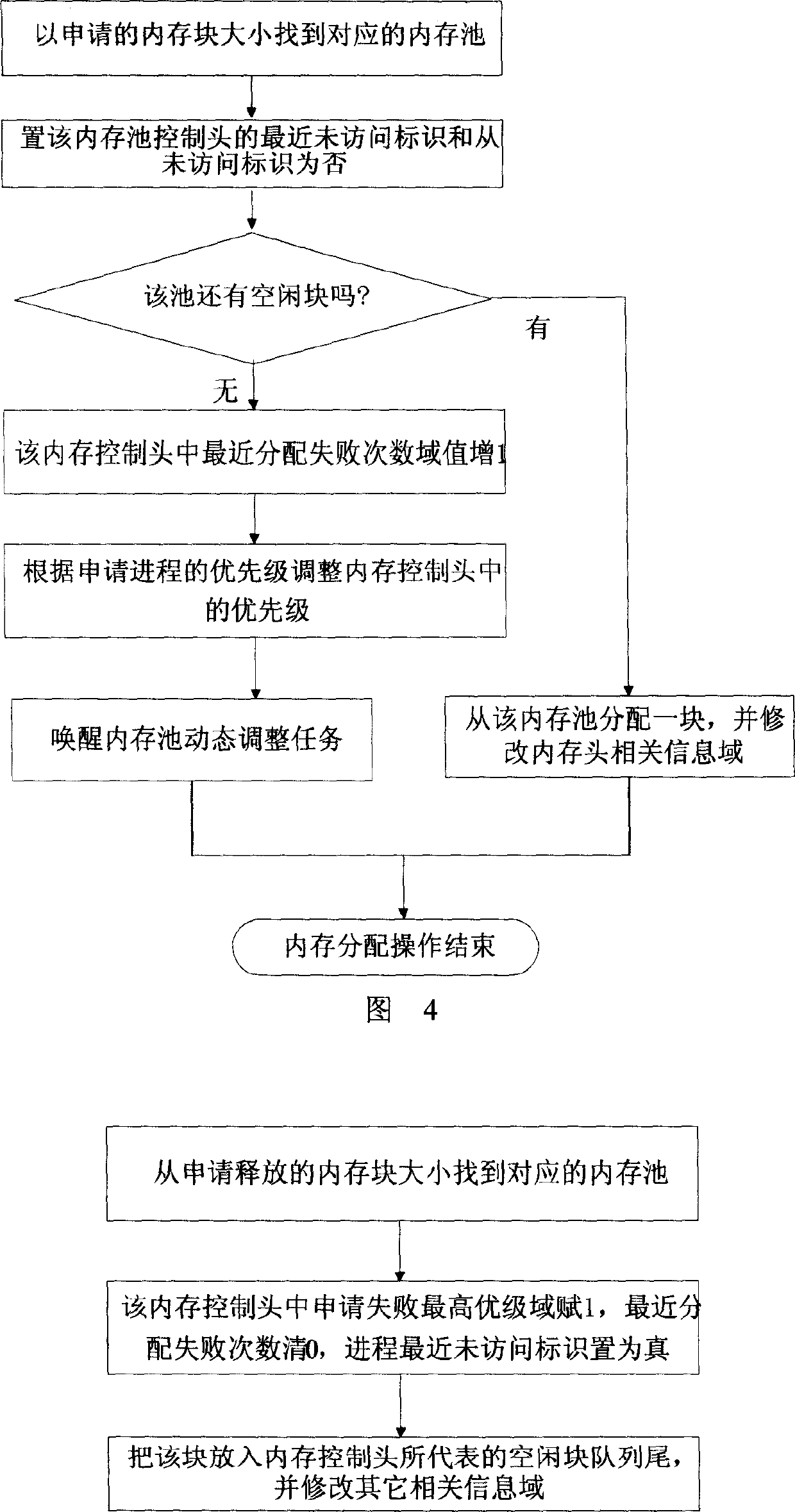

Method for internal memory allocation in the embedded real-time operation system

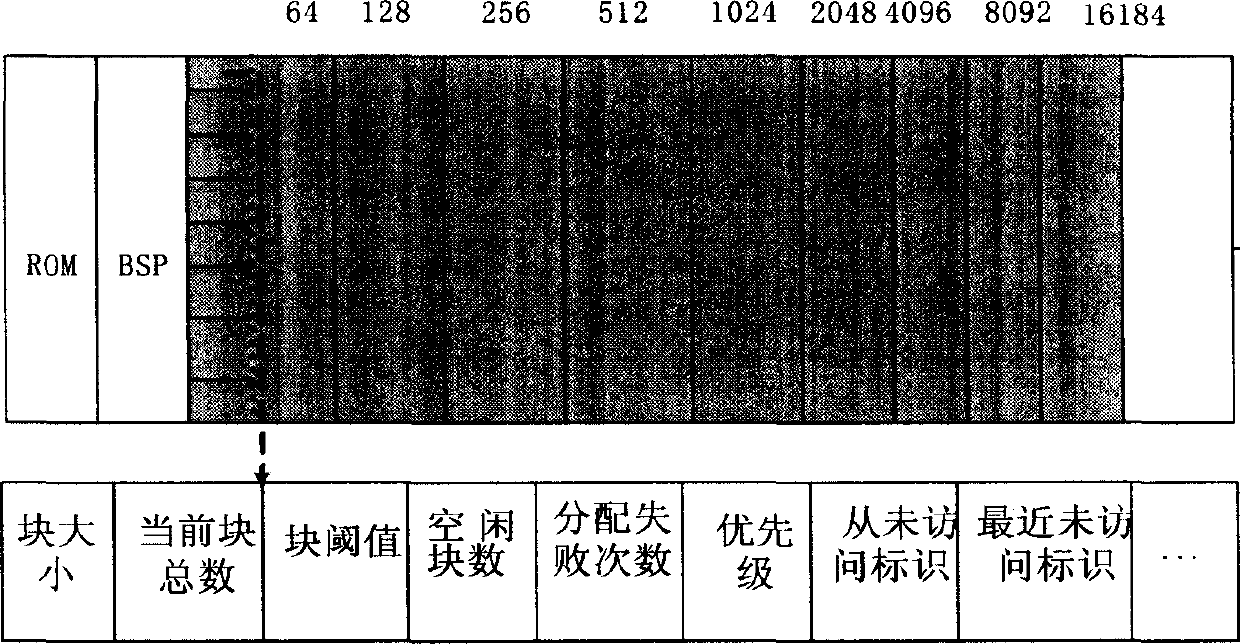

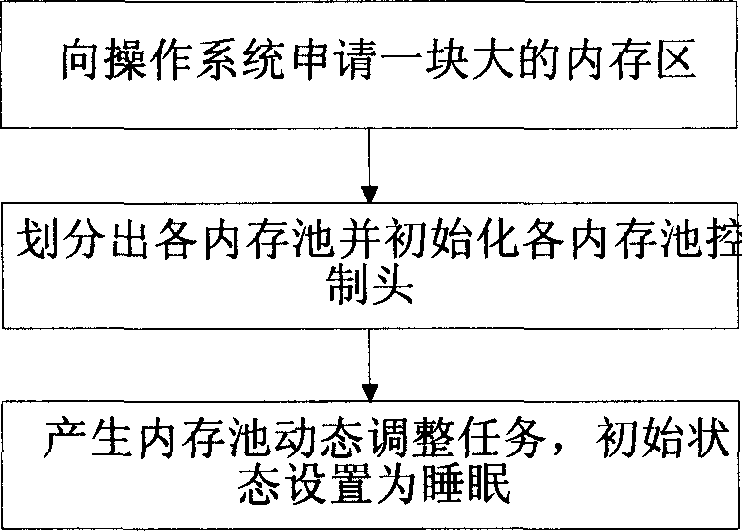

InactiveCN1722106AGuaranteed real-timeImprove reliabilityMultiprogramming arrangementsMemory systemsInternal memoryOperational system

The invention relates to a method for allocating internal memory of real time operating system, which comprises the following steps: applying a big internal memory area from operating system, dividing the big internal memory area into internal memory polls with different sizes and the same internal memory poll comprises internal memory block with the same size, initialing each internal memory poll controlling bar. When it needs internal memory block, it finds the corresponding internal memory poll according to the size of internal memory block, and quotes weather the internal memory poll has free block, if it has free block, it fetches a block from the head of the team and modifies the referent information of internal memory poll controlling bar, and then the allocation finishes; if not, it dose dynamic adjustment to internal memory; when it releases the internal memory, it finds the corresponding internal memory poll according to the size of internal memory and returns it into the tail of the team and rewrites the referent information of internal memory poll controlling bar.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

Method and system for performing real-time operation

ActiveUS7464379B2Save powerEnergy efficient ICTProgram initiation/switchingInformation processingBitwise operation

Owner:KK TOSHIBA

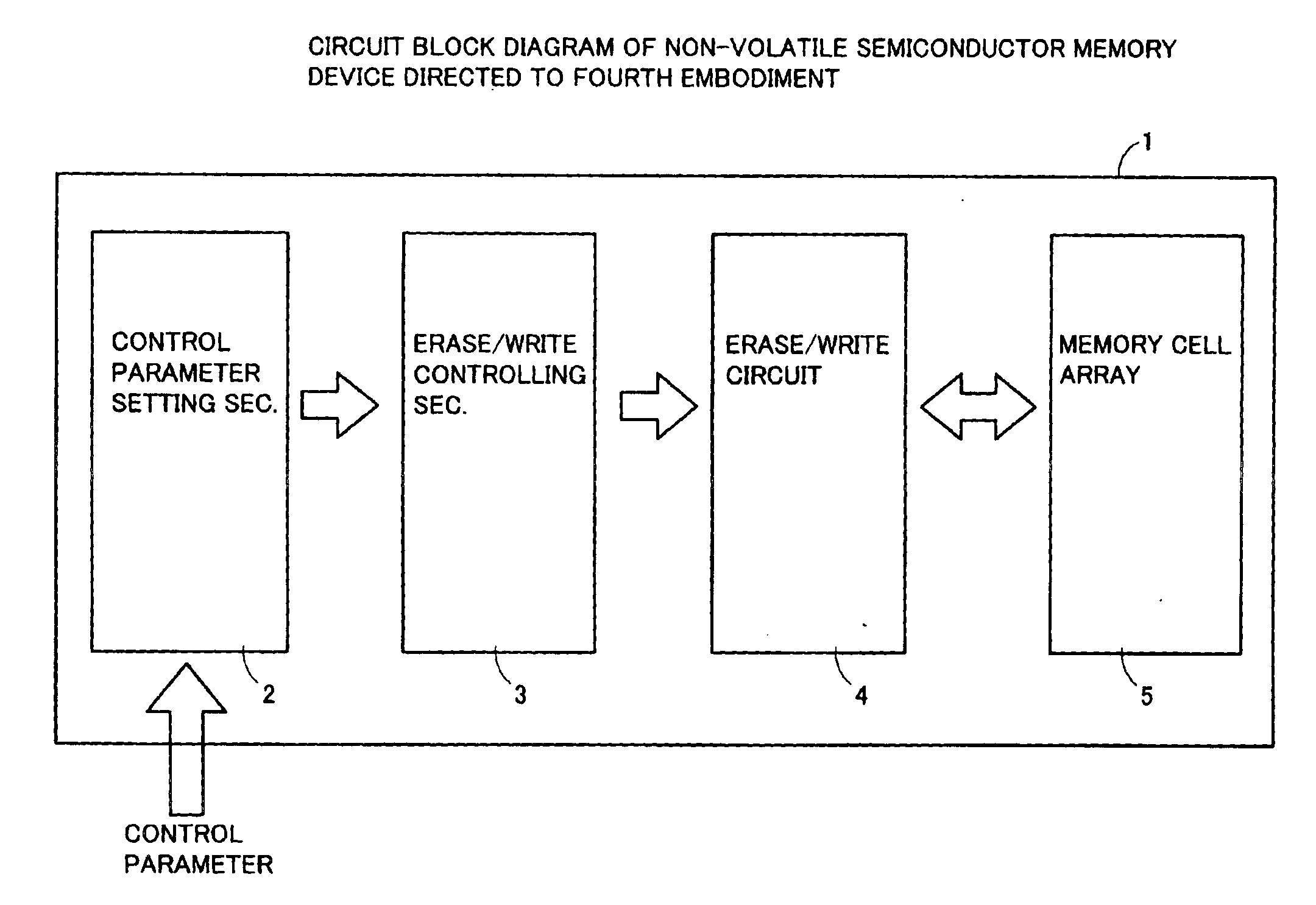

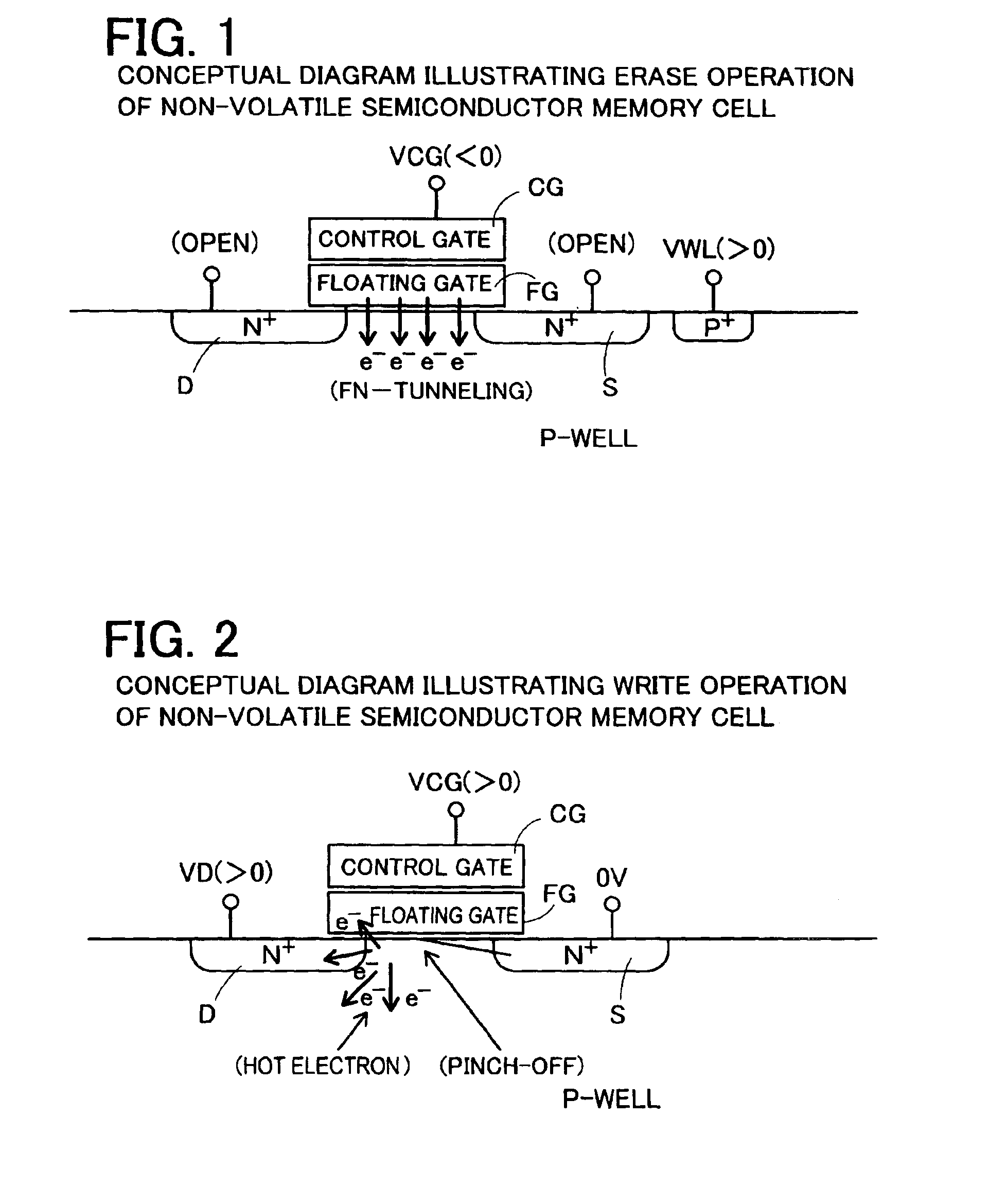

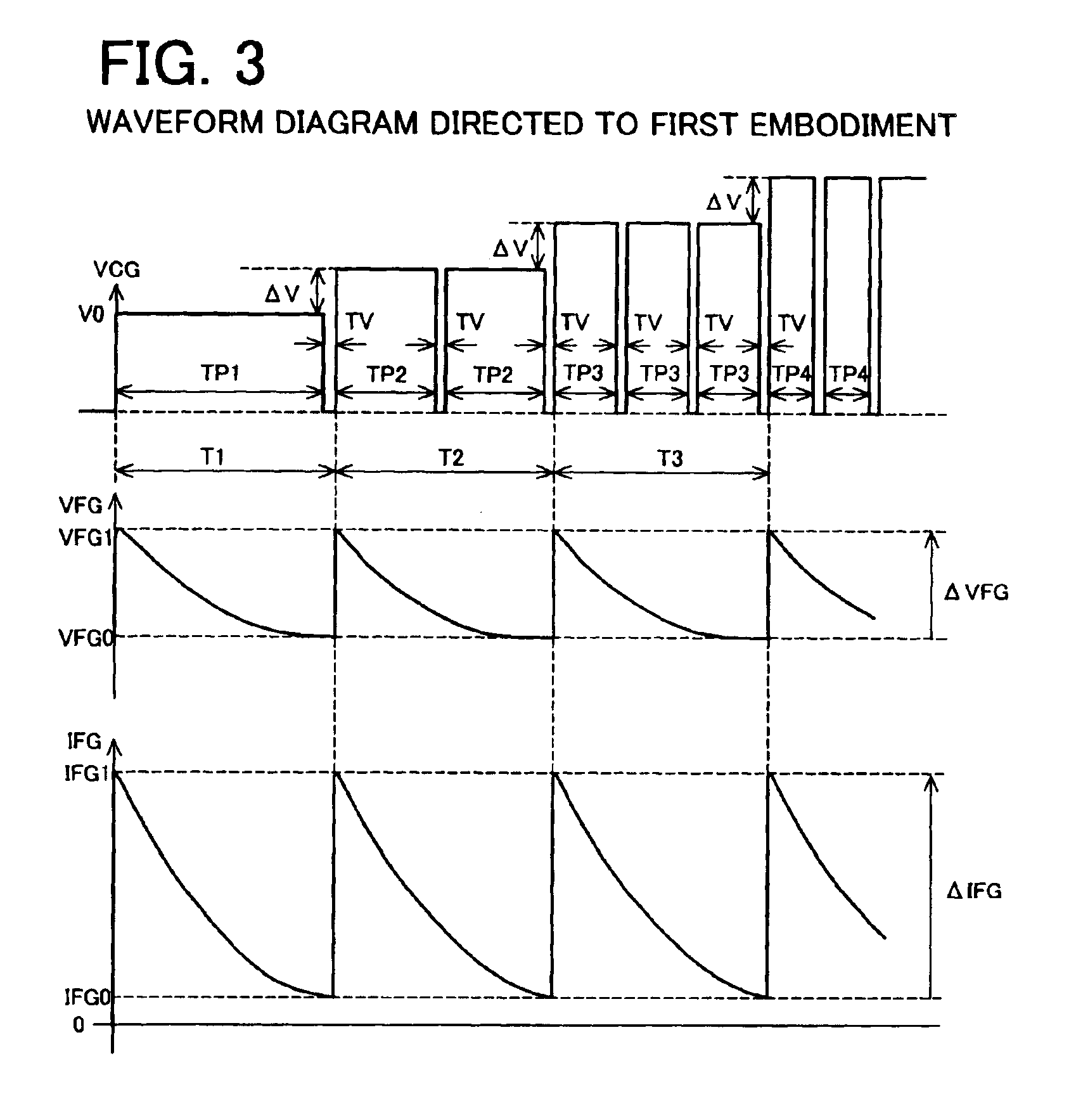

Control method of non-volatile semiconductor memory cell and non-volatile semiconductor memory device

It is intended to provide control method and a nonvolatile semiconductor memory device capable of erase operation or write operation in high speed securing reliability without applying excessive electric field. An operation unit consists of a plurality of operation cycles each of which has a bias-application period and a verification period. Addition voltage ΔV is added to each operation unit as bias voltage, whereby a write operation can be carried out with characteristic of injected current IFG that is uniform among respective operation units duration of which are generally same. In this case, duration of operation cycles are shortened by each operation unit and duration of verification periods are shortened so as to avoid a situation such that a write operation completes in the middle of a bias-application period and after that, another write operation continues to cause excessive voltage stress on non-volatile semiconductor memory cells.

Owner:MONTEREY RES LLC

Scheduling system and method in which threads for performing a real-time operation are assigned to a plurality of processors

InactiveUS7657890B2Improve performanceResource allocationMultiple digital computer combinationsBitwise operationCoupling

A real-time processing system that executes a plurality of threads, each of the threads being a unit of execution of a real-time operation, comprises a plurality of processors, a unit which selects a tightly coupled thread group from among the threads based on coupling attribute information indicative of a coupling attribute between the threads, the tightly coupled thread group including a set of tightly coupled threads running in cooperation with each other, and a unit which performs a scheduling operation of dispatching the tightly coupled threads to several of the processors that are equal to the tightly coupled threads to simultaneously execute the tightly coupled threads by the several of the processors.

Owner:KK TOSHIBA

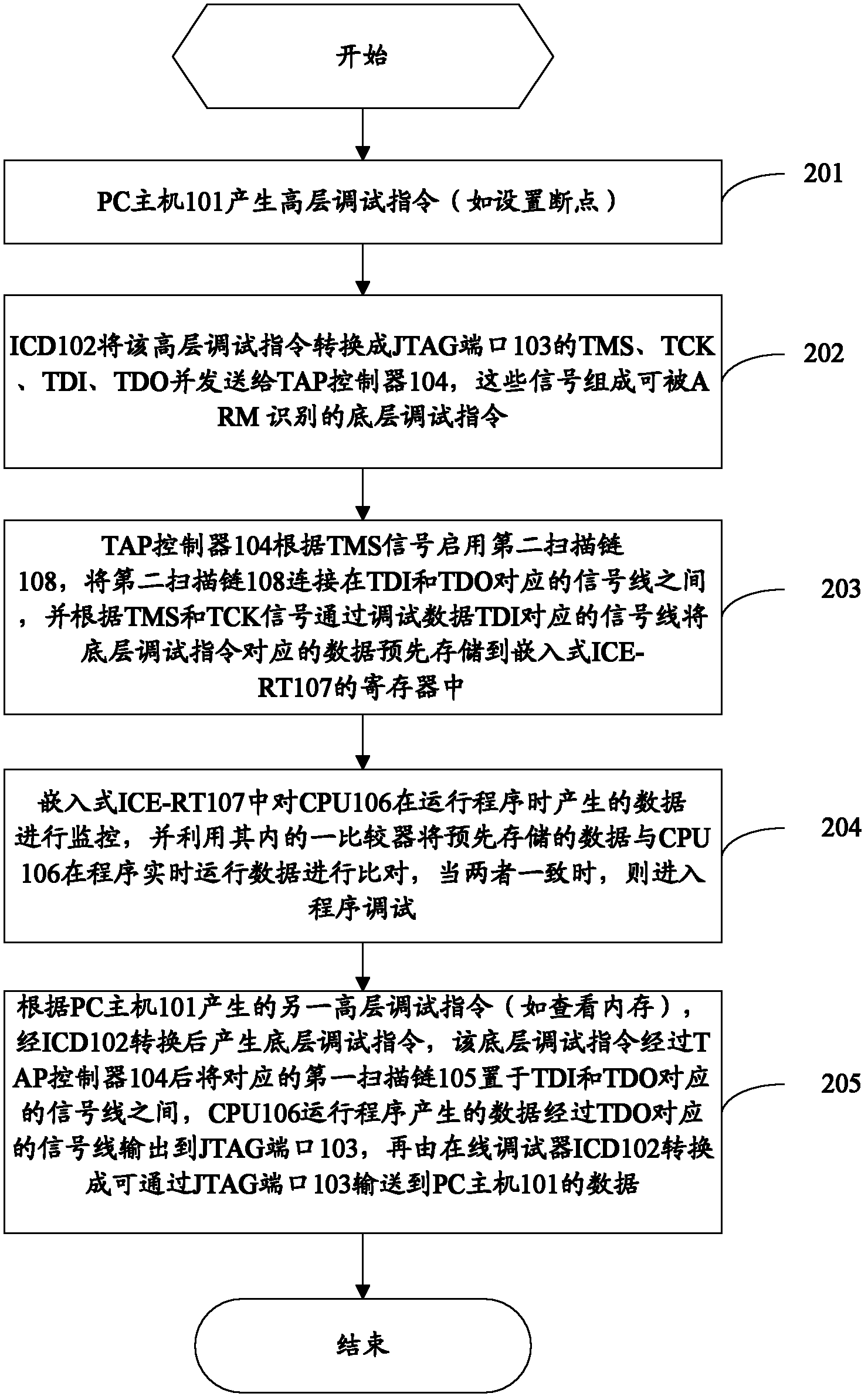

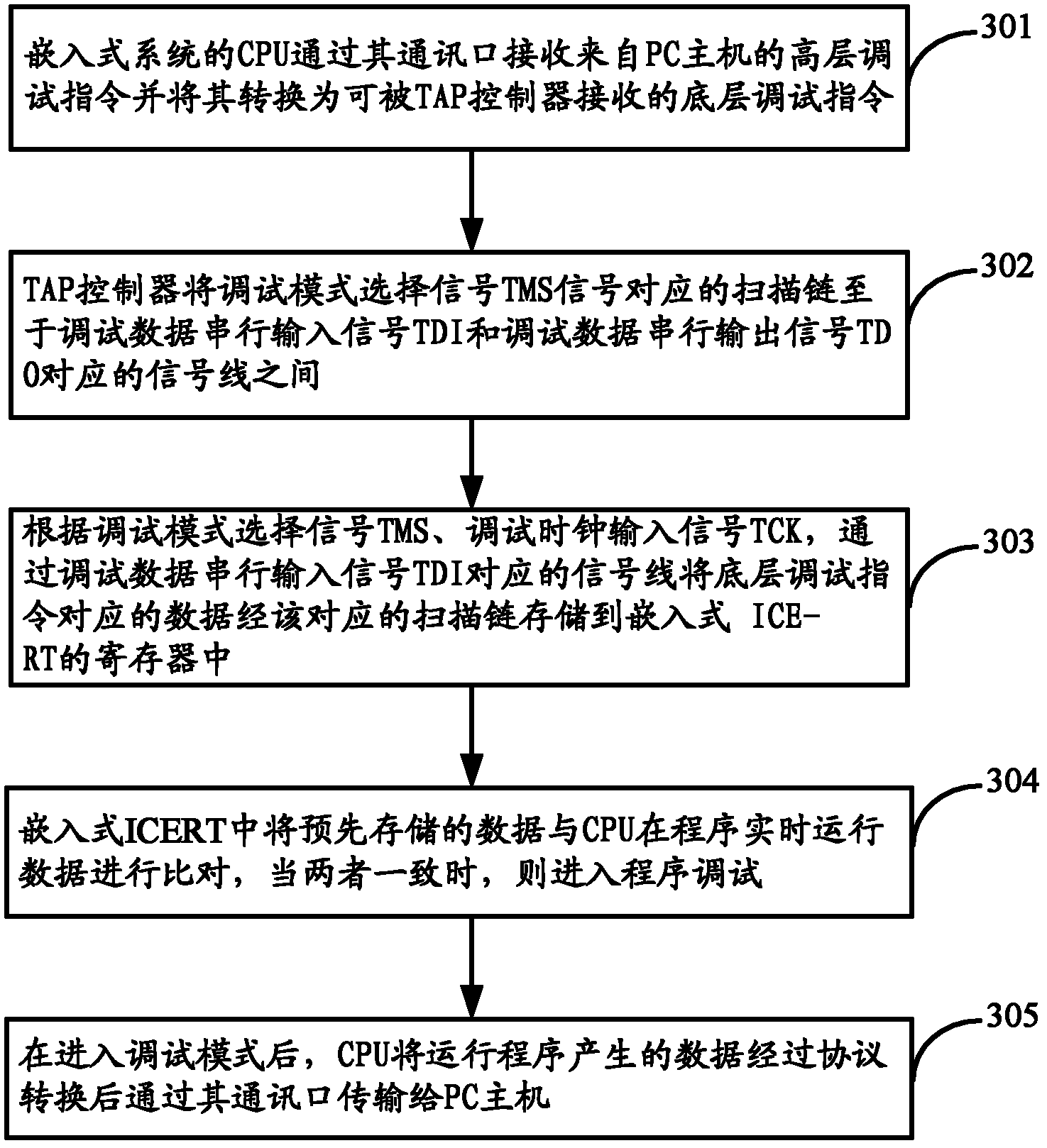

Program debugging method of embedded system and embedded system

InactiveCN102662835AReduce commissioning costsSoftware testing/debuggingBitwise operationProcessor register

The invention provides a program debugging method of an embedded system and the embedded system, belonging to the field of program debugging. The method comprises the steps that: the CPU (central processing unit) of the embedded system receives a higher-level debugging command from a debugging host computer by the communication port of the CUP and converts the higher-level debugging command into a bottom-level debugging command; a testing access port controller stores the data corresponding to the bottom-level debugging command to a register of an embedded real-time on-line circuit simulator in advance; the embedded real-time on-line circuit simulator compares the data stored in the register in advance with the data of the CPU at the time of program real-time operation, and enters the program into a debugging mode when the two data are consistent; and then the CPU carries out protocol conversion on the data generated by the program real-time operation and transmits to the debugging host computer by the communication port of the CPU. According to the invention, the CPU transmits the higher-level debugging command by the communication port of the CPU, converts the higher-level debugging command into the bottom-level debugging command, and outputs the data by the communication port of the CPU after entering the debugging mode, so that the debugging cost is lowered.

Owner:SUNPLUS TECH CO LTD +1

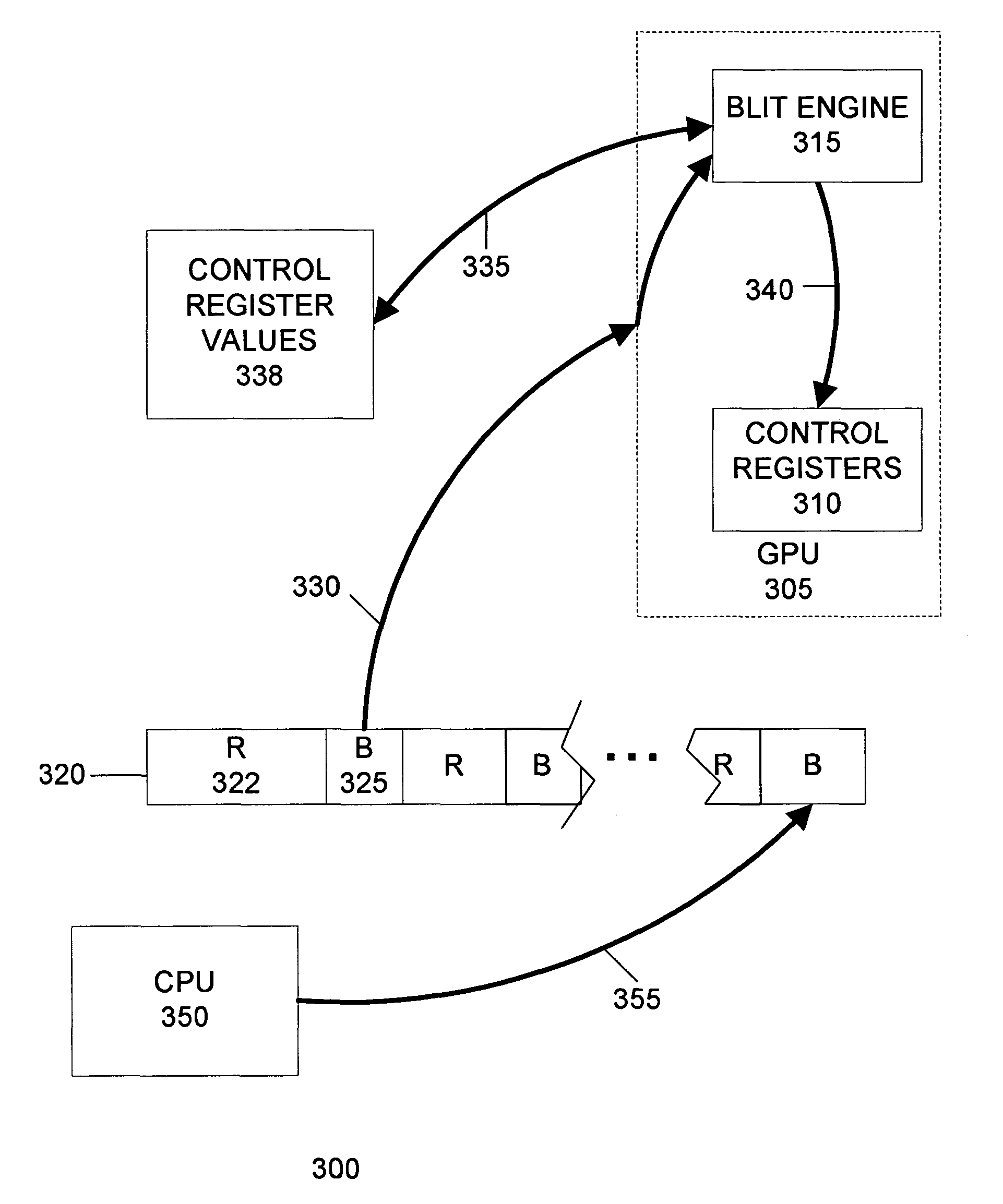

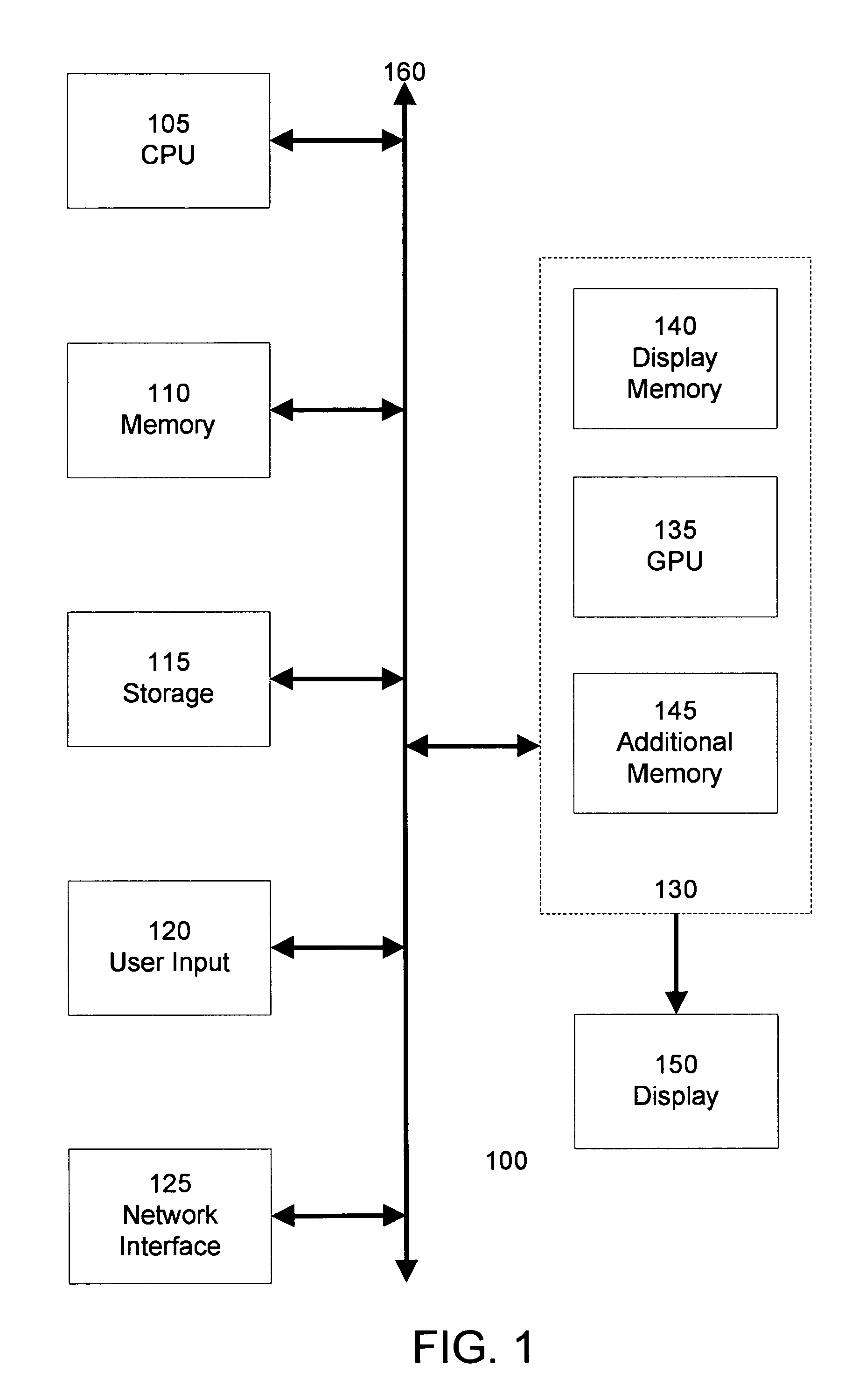

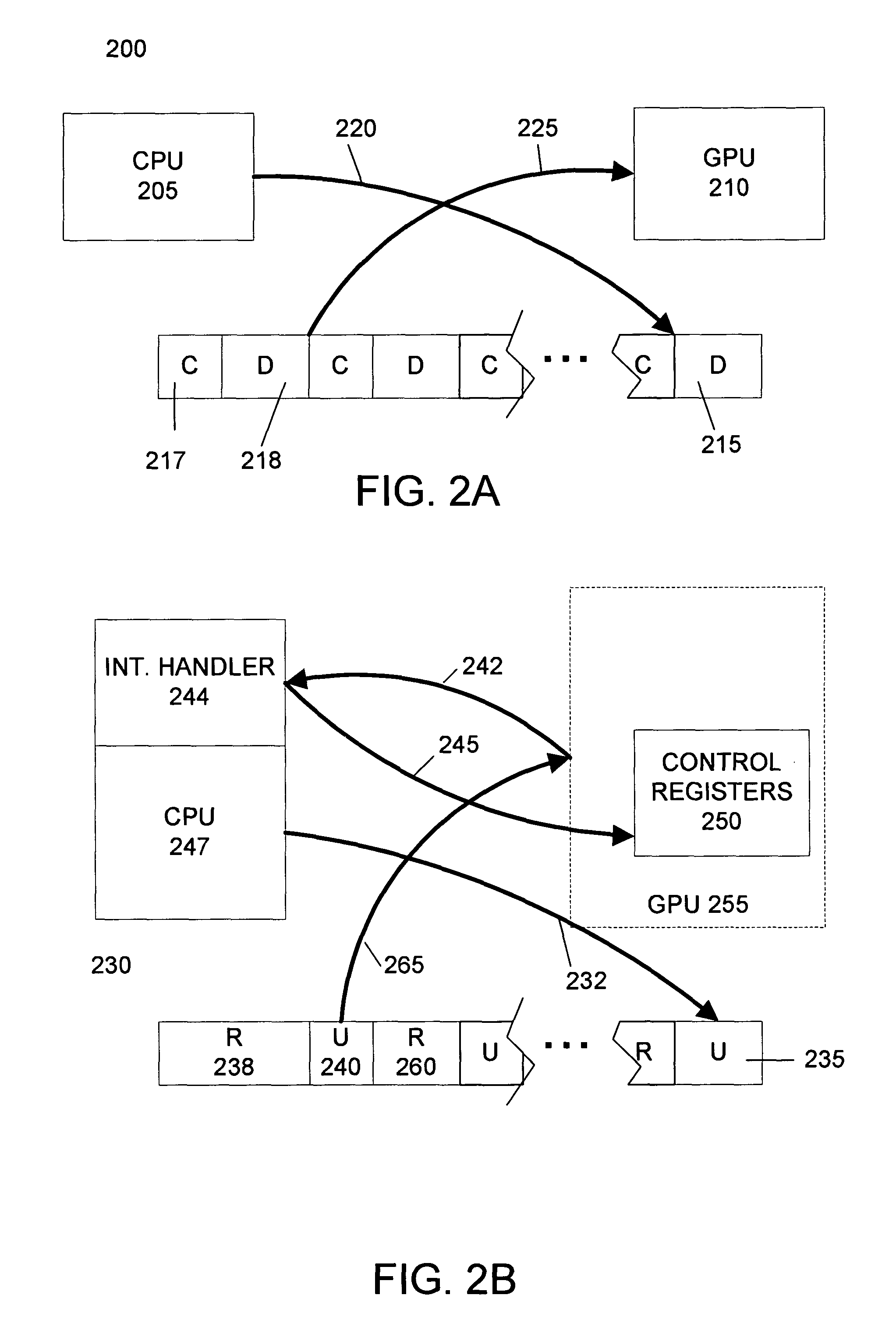

Graphics processing unit self-programming

ActiveUS6952217B1Cathode-ray tube indicatorsProcessor architectures/configurationMemory addressGraphics

A method of self-programming a graphics processing unit (GPU) includes receiving a blit instruction defining a blit operation and storing a first control value in a control register, which determines the behavior of the GPU, using the blit operation. The blit instruction is read by the GPU from a command buffer asynchronously with the CPU. The blit operation is applied to a second control value to determine the first control value. The second control value can be stored in a memory, such as a second control register or a table of control values accessed by an index value. In one application, the second control value is a starting memory address for a display buffer, while in another application, second control value is a clip plane distance. The blit operation can include a copy operation, a colorkey operation, a logic operation, and / or a pattern copy operation on the first control value.

Owner:NVIDIA CORP

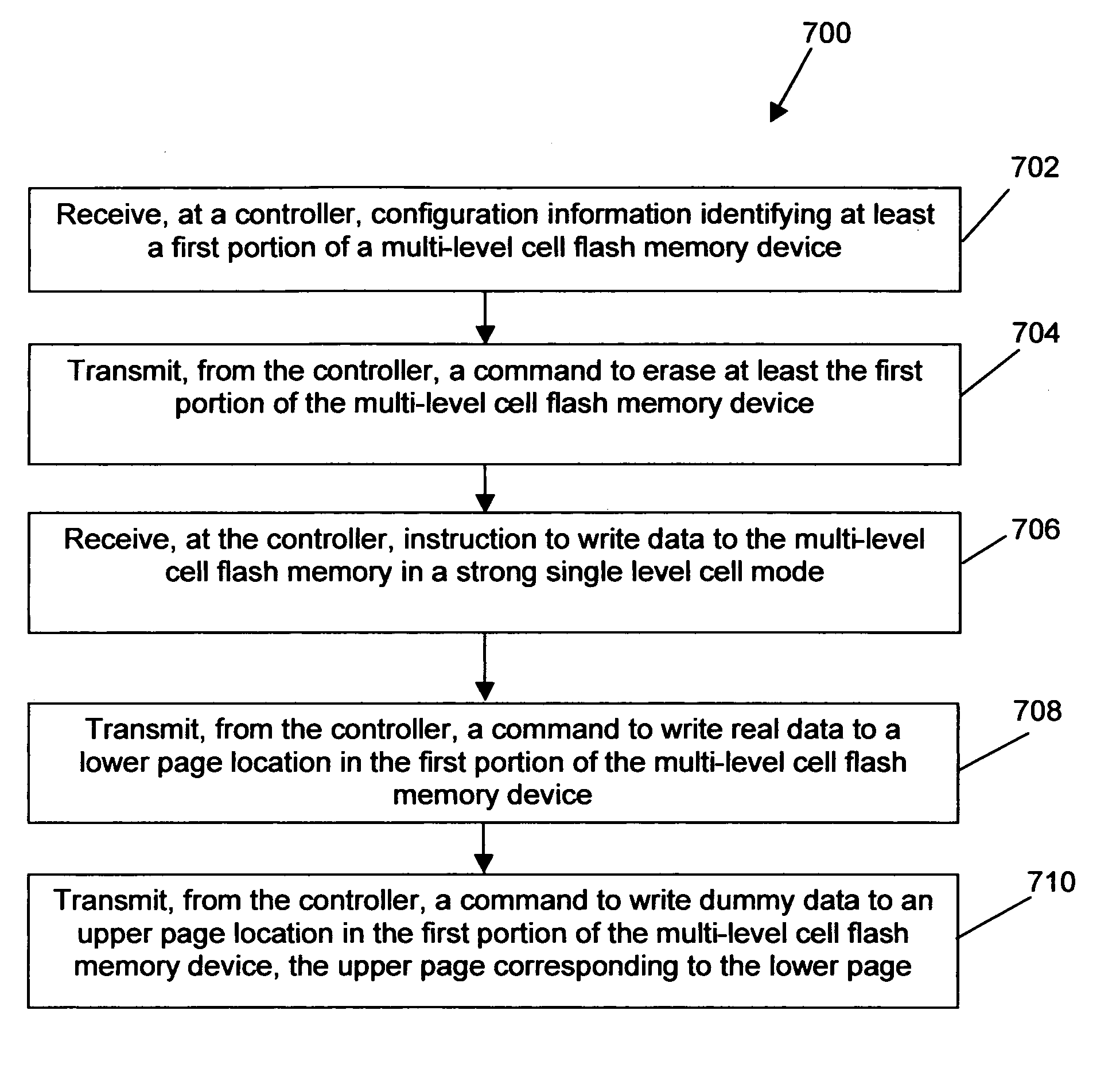

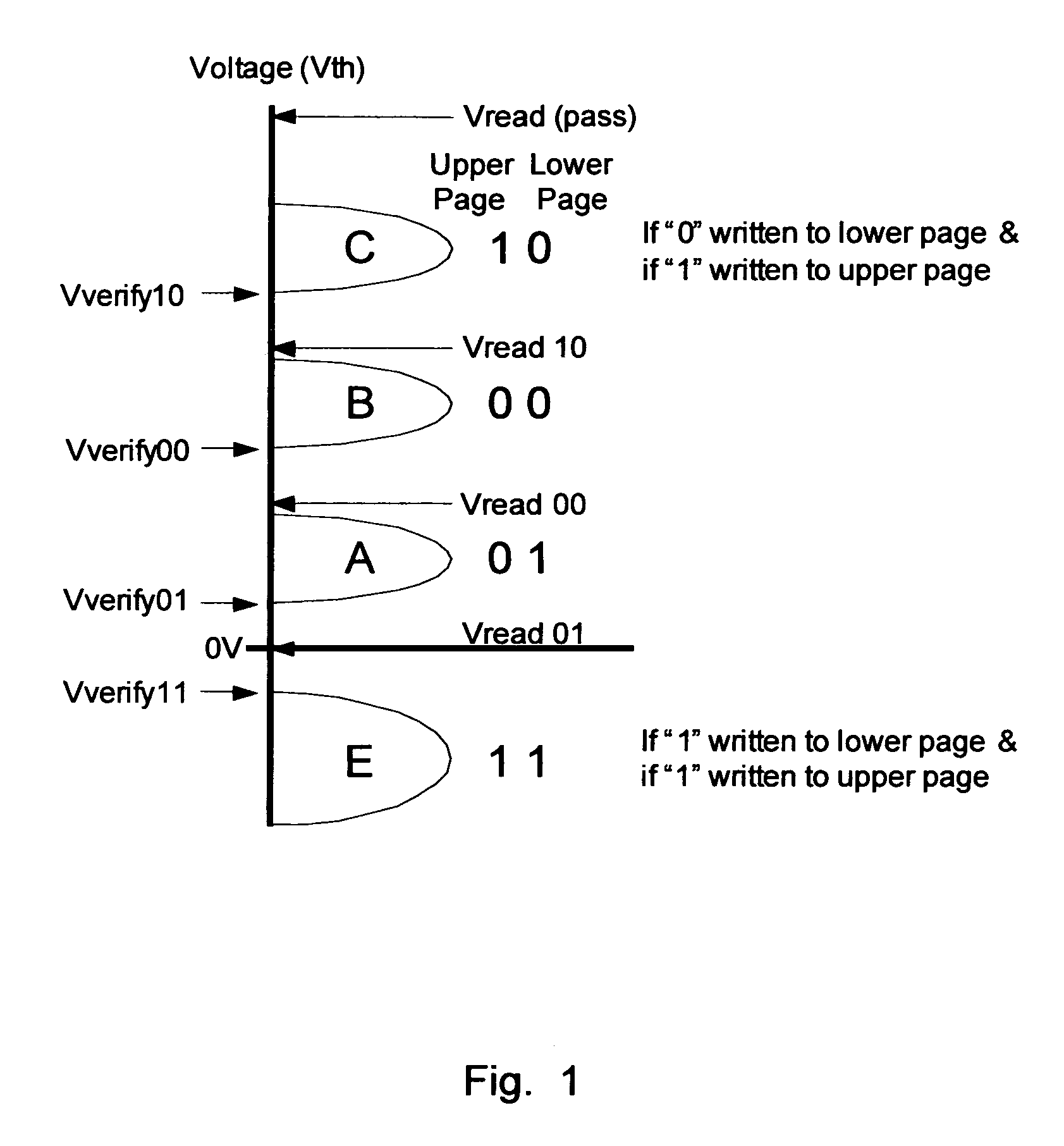

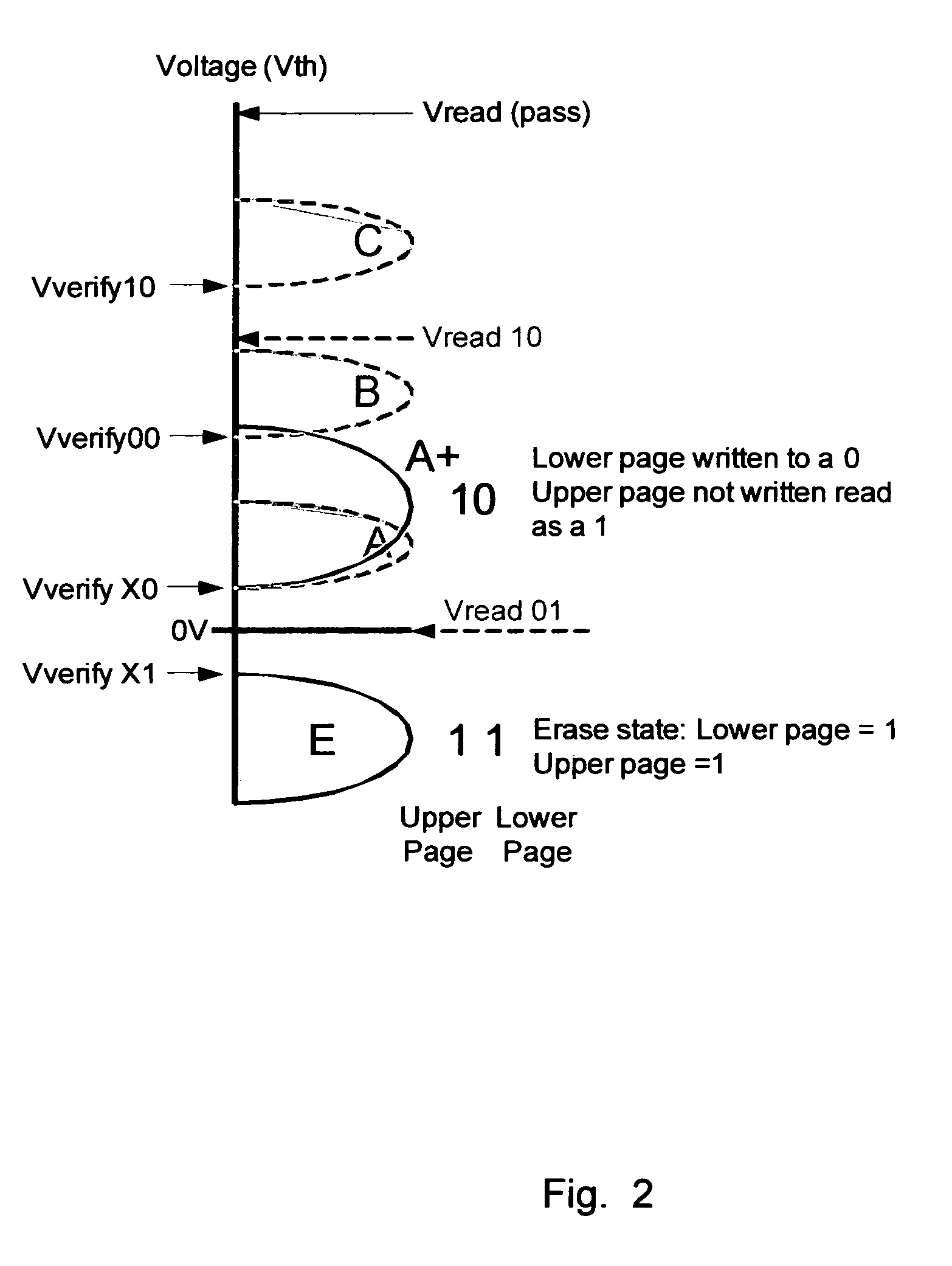

Method and apparatus for high reliability data storage and retrieval operations in multi-level flash cells

InactiveUS7941592B2Increase charge levelIncrease the differenceRead-only memoriesDigital storageBitwise operationSingle level

One or more multi-level NAND flash cells are operated so as to store only single-level data, and these operations achieve an increased level of charge separation between the data states of the single-level operation by requiring a write to both the upper and lower pages, even though only one bit of data is being stored. That is, the second write operation increases the difference in floating gate charge between the erased state and the programmed state of the first write operation without changing the data in the flash memory cell. In one embodiment, a controller instructs the flash memory to perform two write operations for storing a single bit of data in an MLC flash cell. In another embodiment, the flash memory recognizes that a single write operation is directed a high reliability memory area and internally generates the required plurality of programming steps to place at least a predetermined amount of charge on the specified floating gate.

Owner:KK TOSHIBA +1

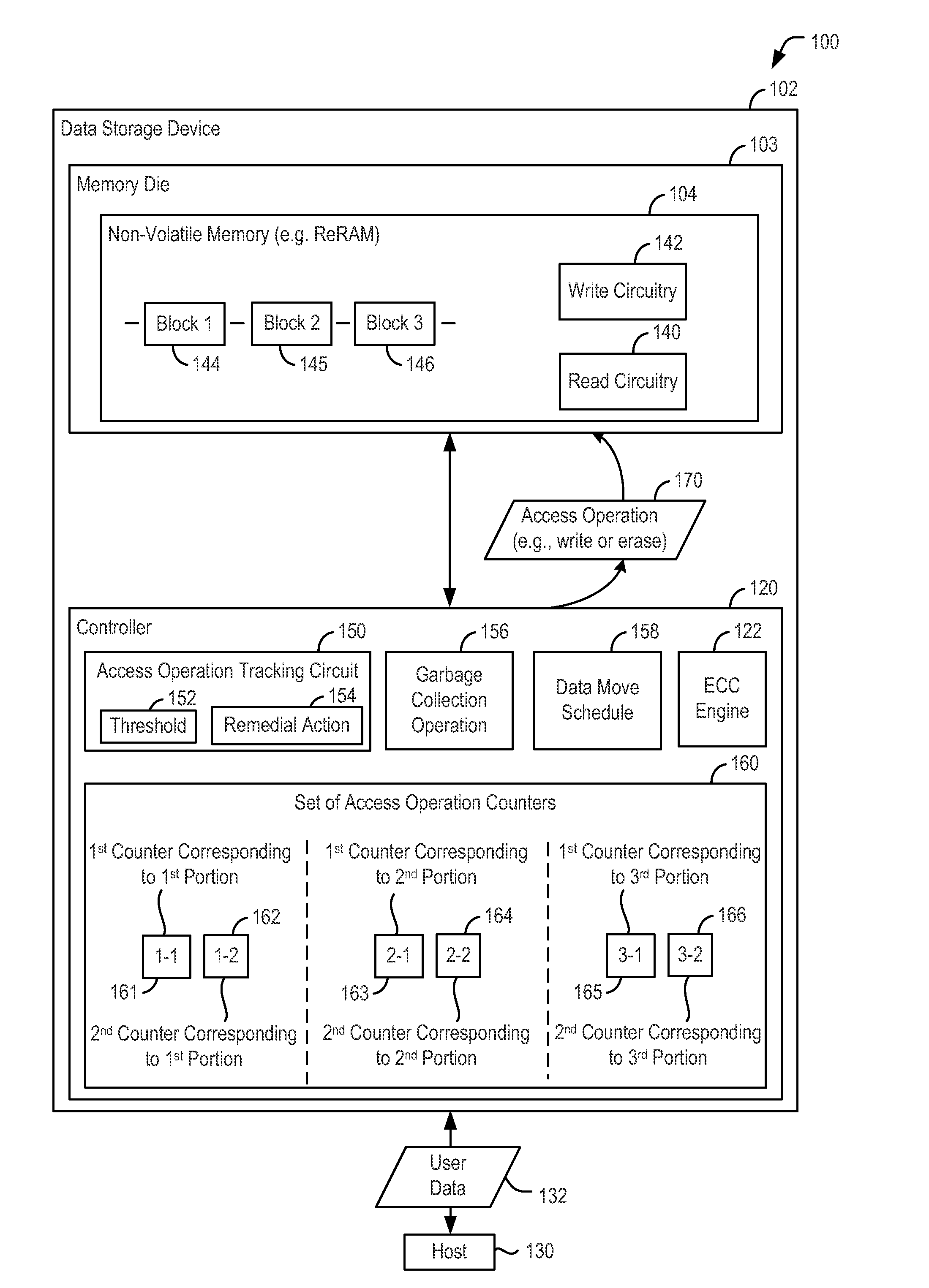

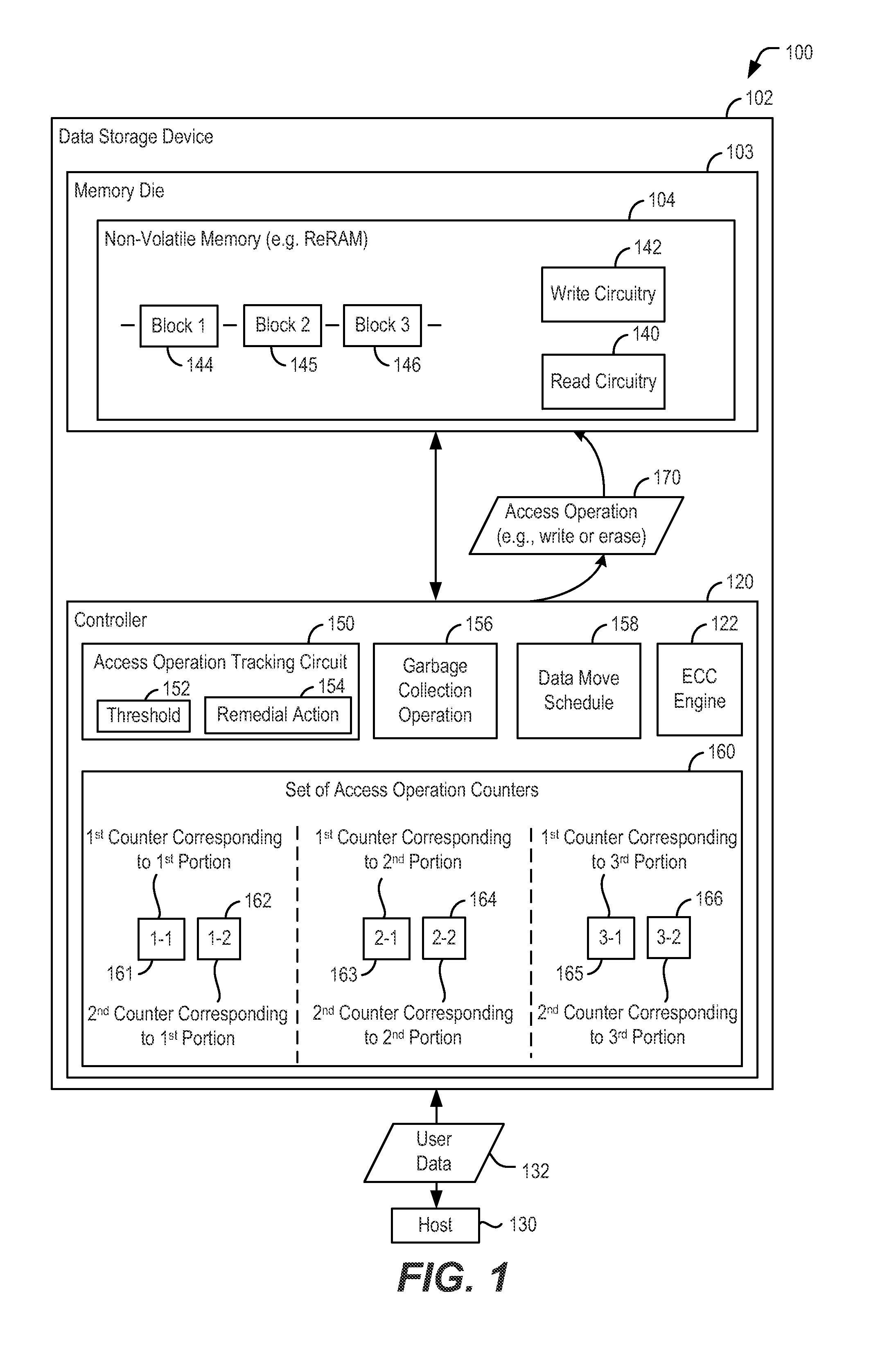

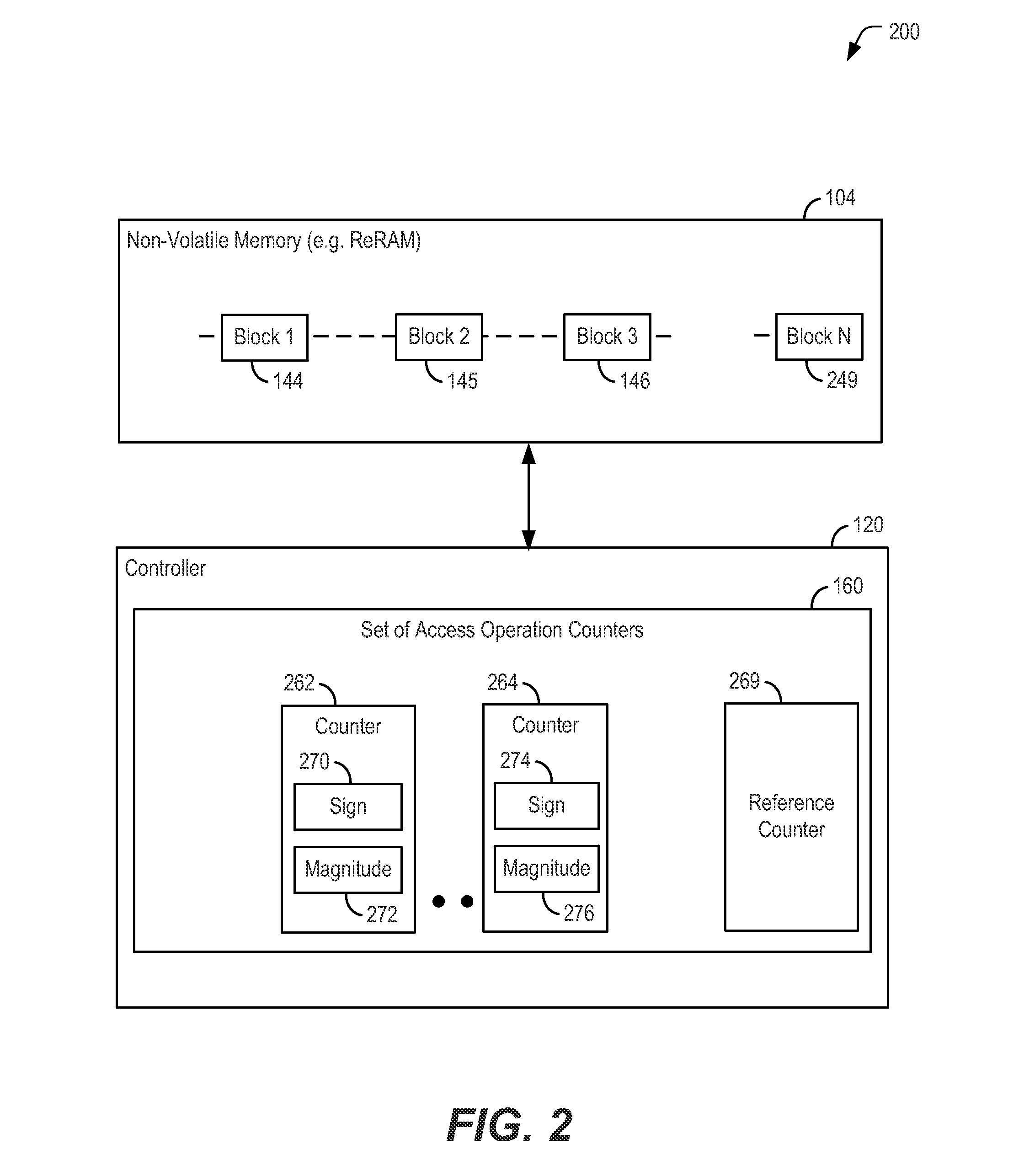

Mitigating disturb effects for non-volatile memory

A method includes adjusting a counter value to indicate an access operation to a first portion of a non-volatile memory. The access operation is an erase operation or a write operation. The adjusted counter value indicates that a number of access operations to the first portion have been performed since an access operation to a second portion of the non-volatile memory has been performed. The method also includes selectively initiating a remedial action to the second portion in response to a comparison of the number of access operations to a threshold.

Owner:SANDISK TECH LLC

Storage controller redundancy using bi-directional reflective memory channel

InactiveUS20050210317A1Reduce protocol overheadRapid generation of packet CRC valuesData processing applicationsInput/output to record carriersError checkingFailover

Owner:PROMISE TECHNOLOGY

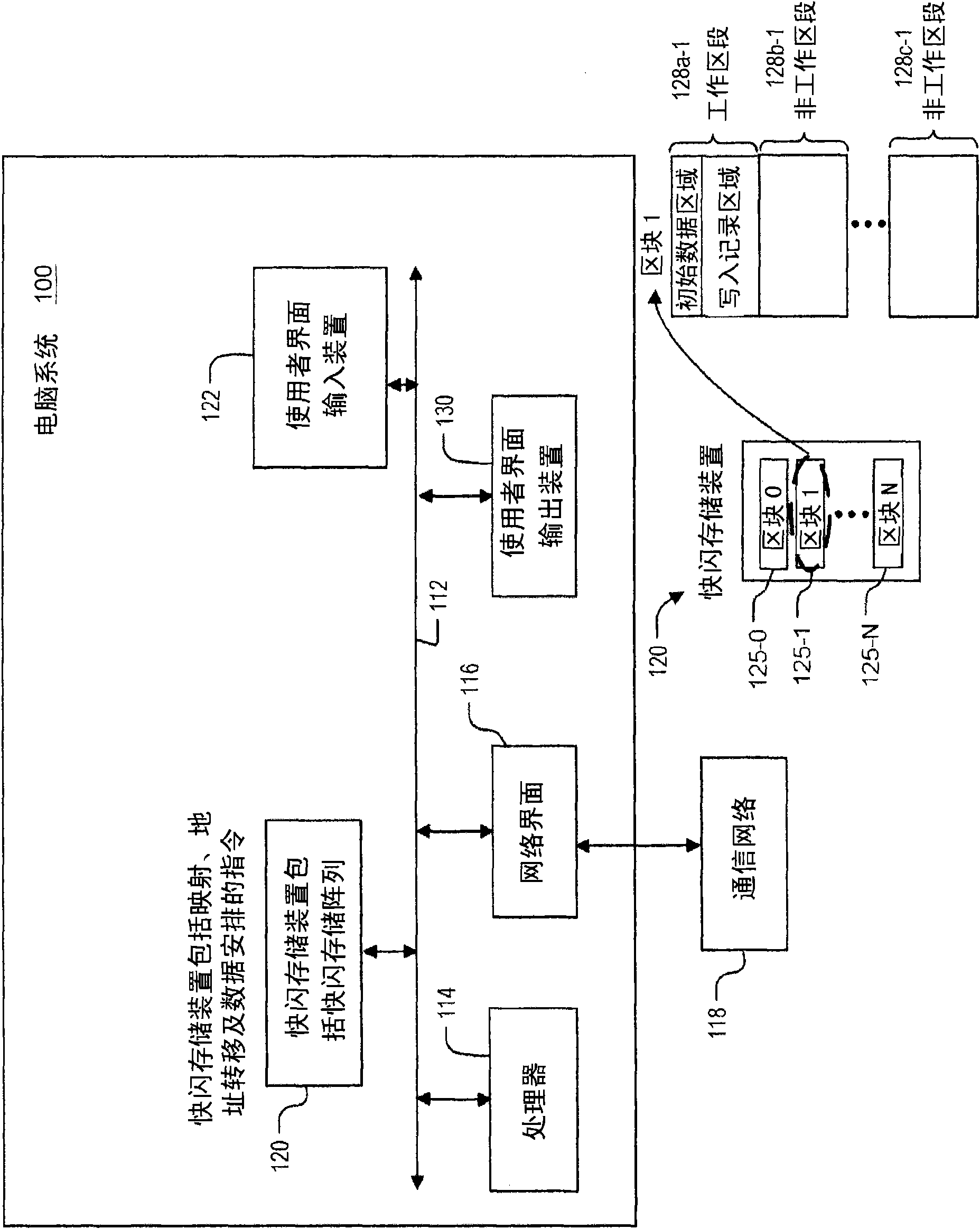

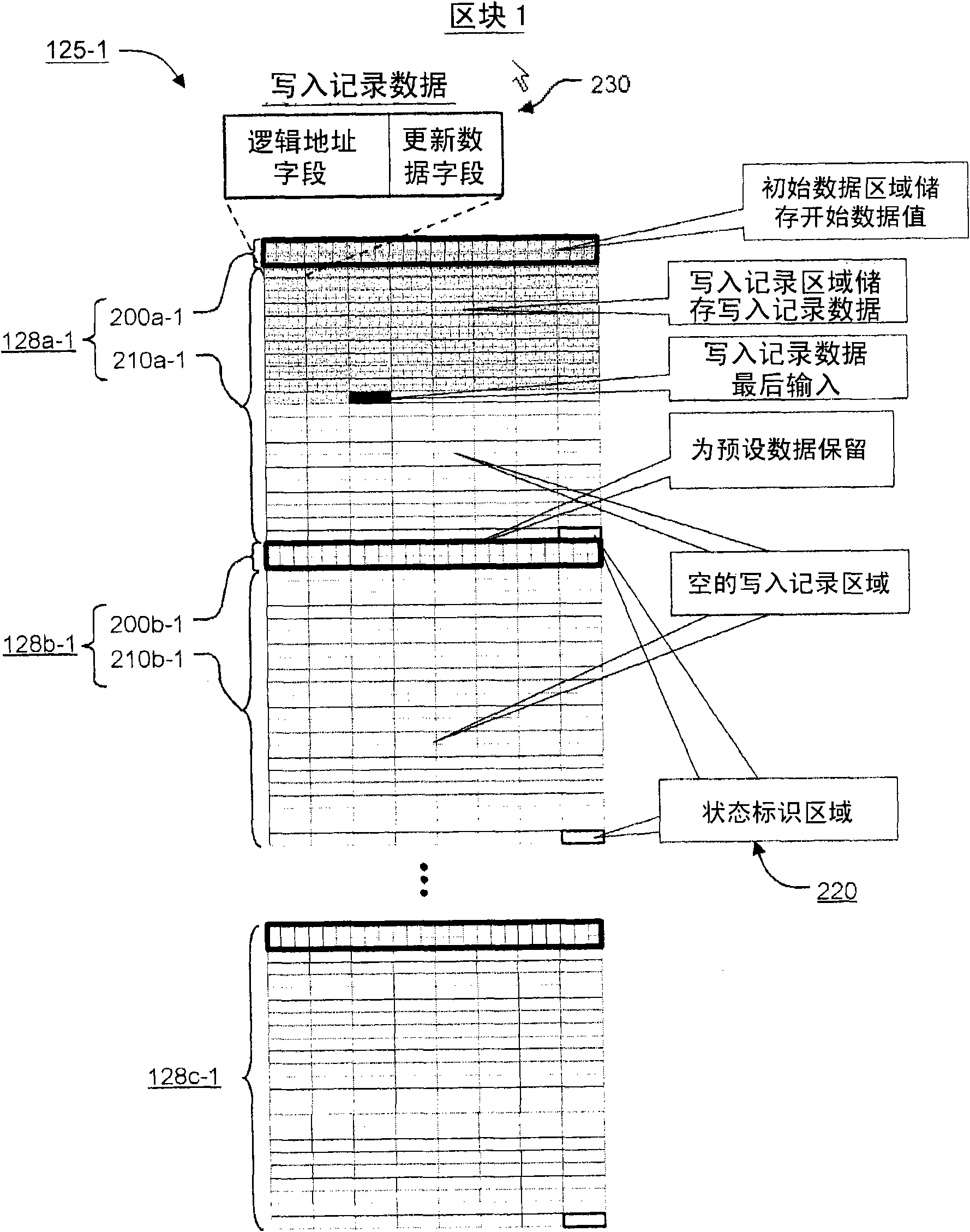

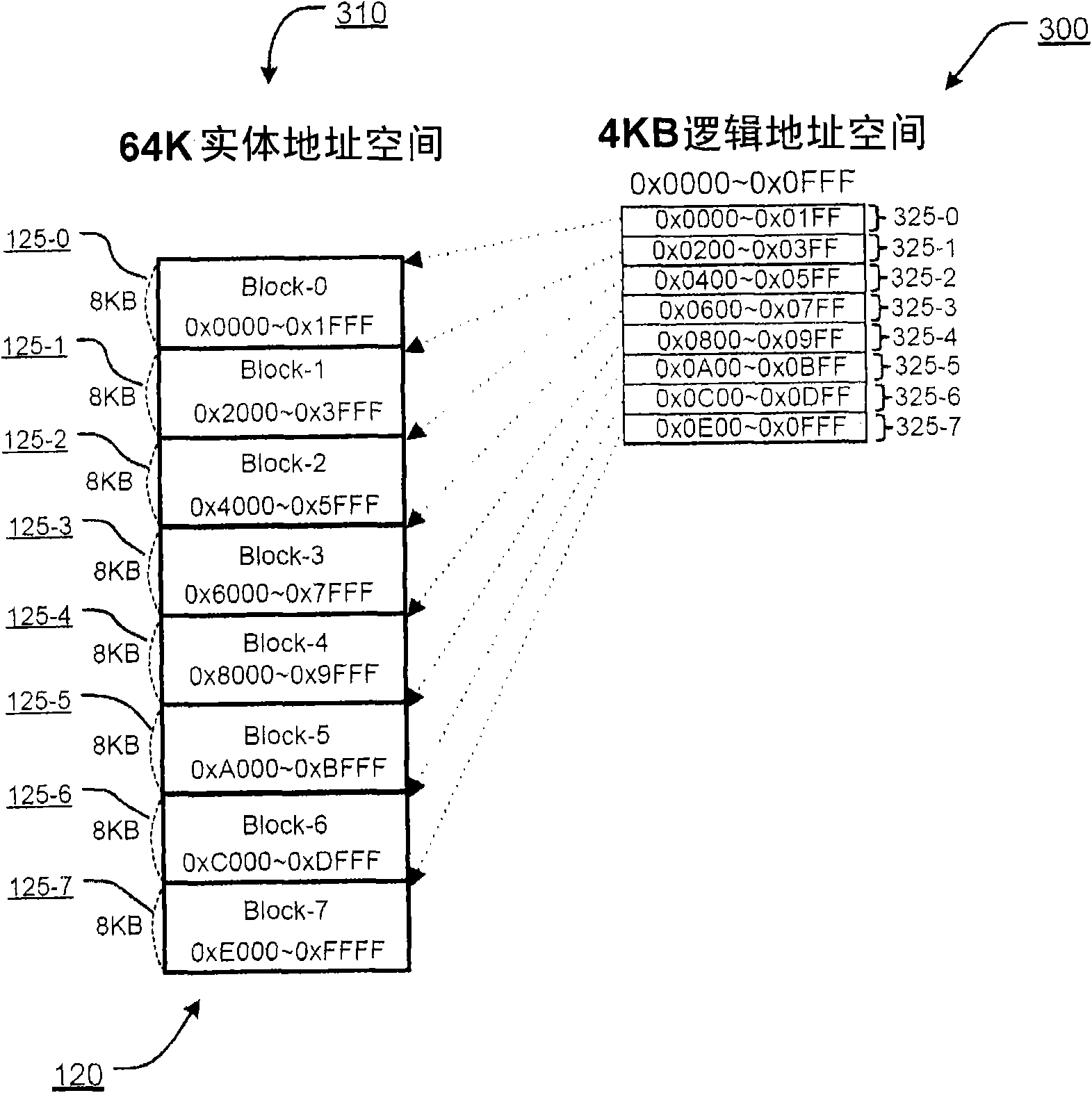

Block-based flash memory and its operation method

ActiveCN101923516AEfficient managementKeep staticMemory architecture accessing/allocationMemory adressing/allocation/relocationProgrammable read-only memoryBitwise operation

The invention discloses a block-based flash memory and its operation method. Techniques are described herein for managing data in a block-based flash memory device which avoid the need to perform sector erase operations each time data stored in the flash memory device is updated. As a result, a large number of write operations can be performed before a sector erase operation is needed. In addition, the block-based flash memory can emulate both programming and erasing on a byte-by-byte basis, like that provided by an EEPROM.

Owner:MACRONIX INT CO LTD

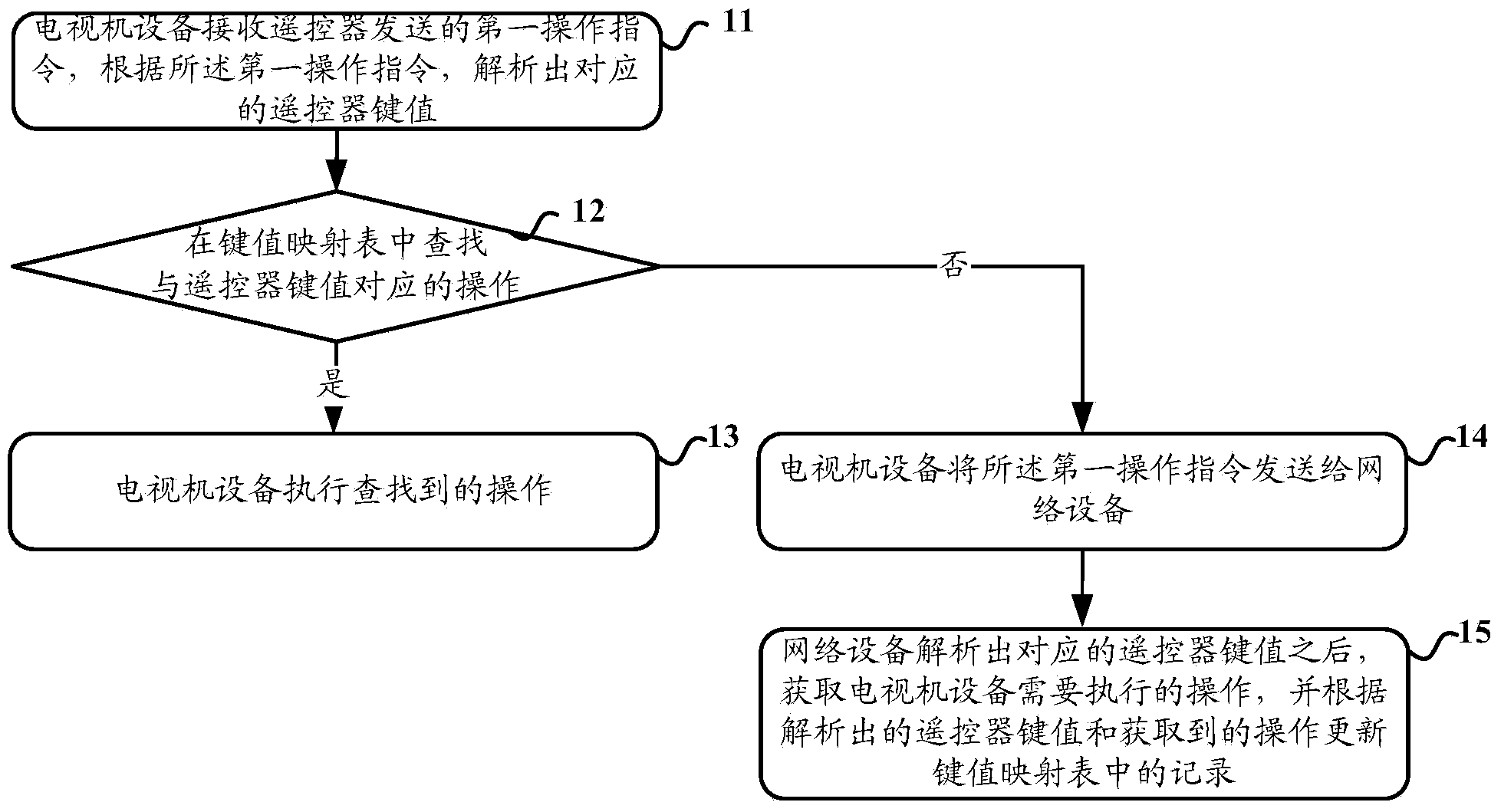

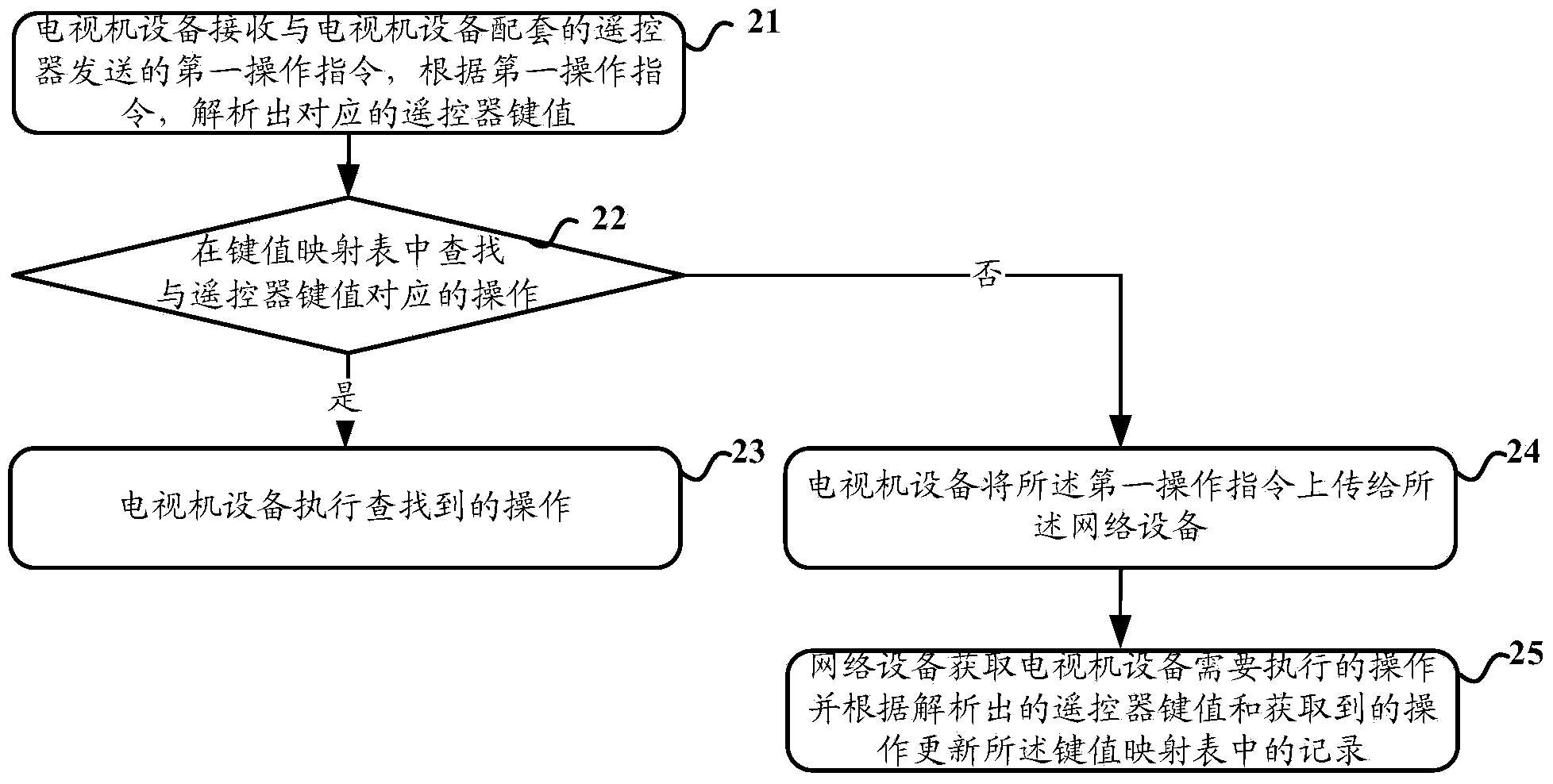

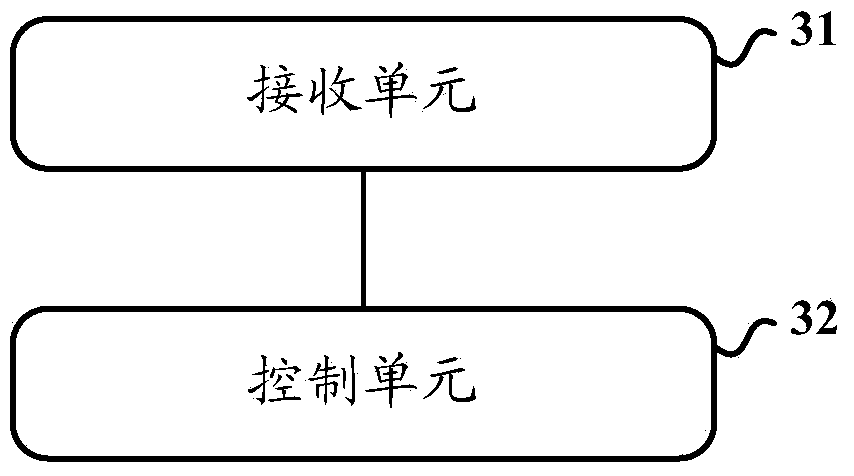

Television device control method and system and television device

The invention discloses a television device control method and system and a television device, relates to the field of wireless communication and provides a method for performing custom function setting on press keys of a remote-control unit. According to the television device control method and system and the television device, the television device receives a first operating instruction which is sent by the remote-control unit, and corresponding remote-control unit key values are obtained through analysis according to the first operating instruction; the television device searches for operations which are executed by the television device and correspond to the analyzed remote-control unit key values in a key value mapping table that is obtained in advance, if the operations are found out, the corresponding operations are executed, if the operations are not found out, the first operating instruction is sent to a network device, thereby, the network device is instructed to analyze the corresponding remote-control unit key values and obtain the operations which are required to be executed by the television device, and records in a key value mapping table are updated according to the analyzed remote-control unit key values and the obtained operations; the key value mapping table at least includes records of a corresponding relation between the remote-control unit key values and the operations which are executed by the television device, and custom function setting can be achieved.

Owner:HISENSE

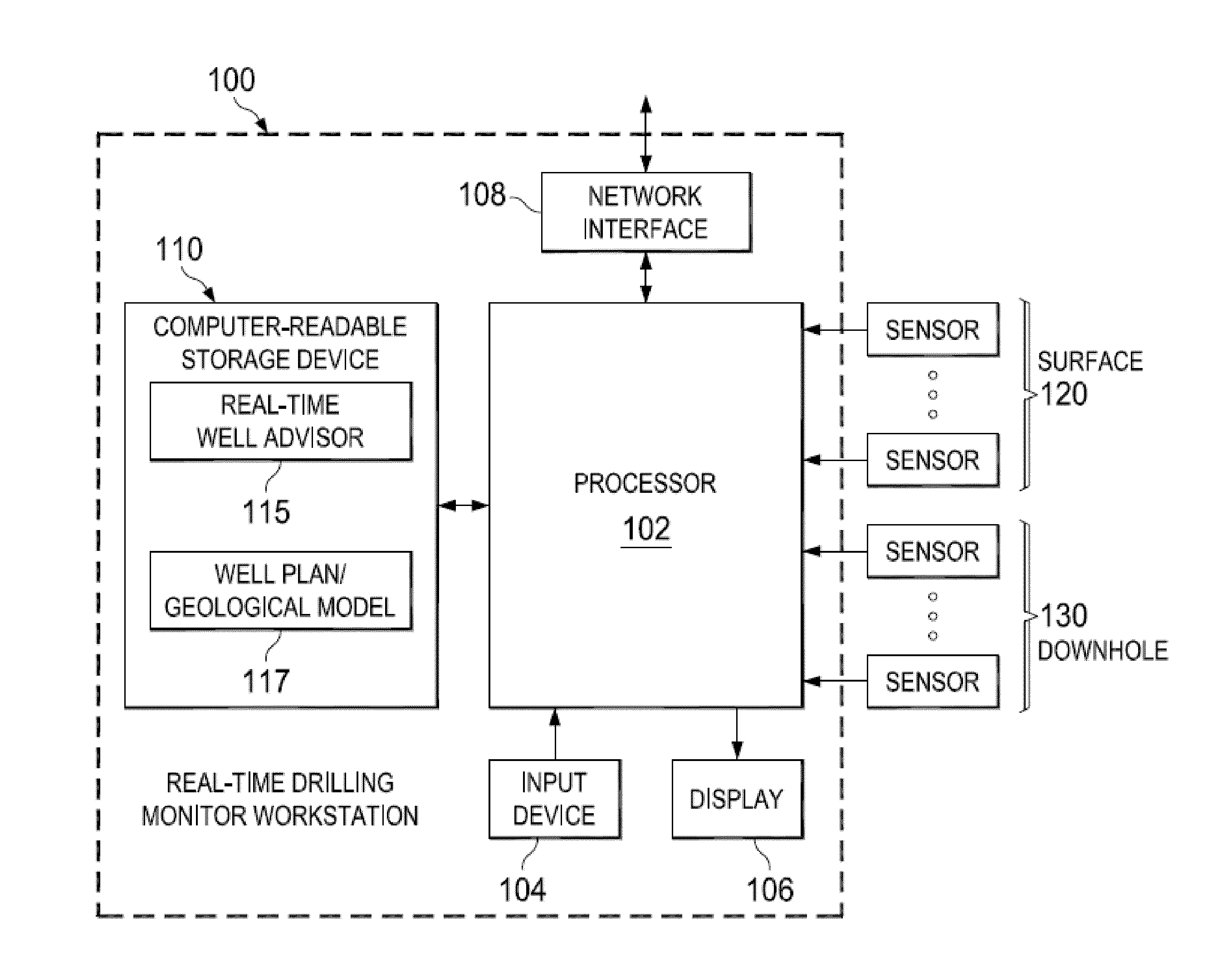

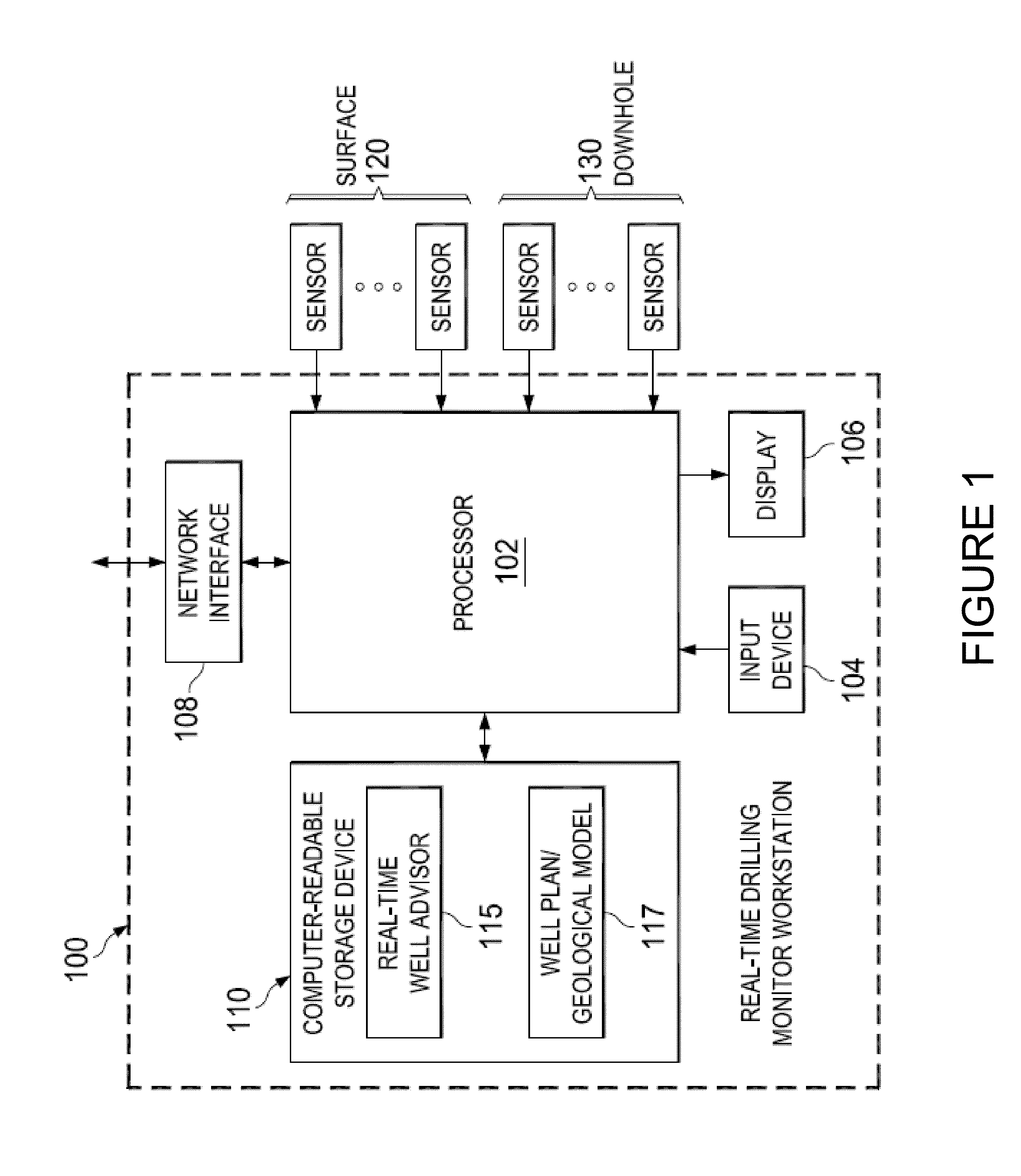

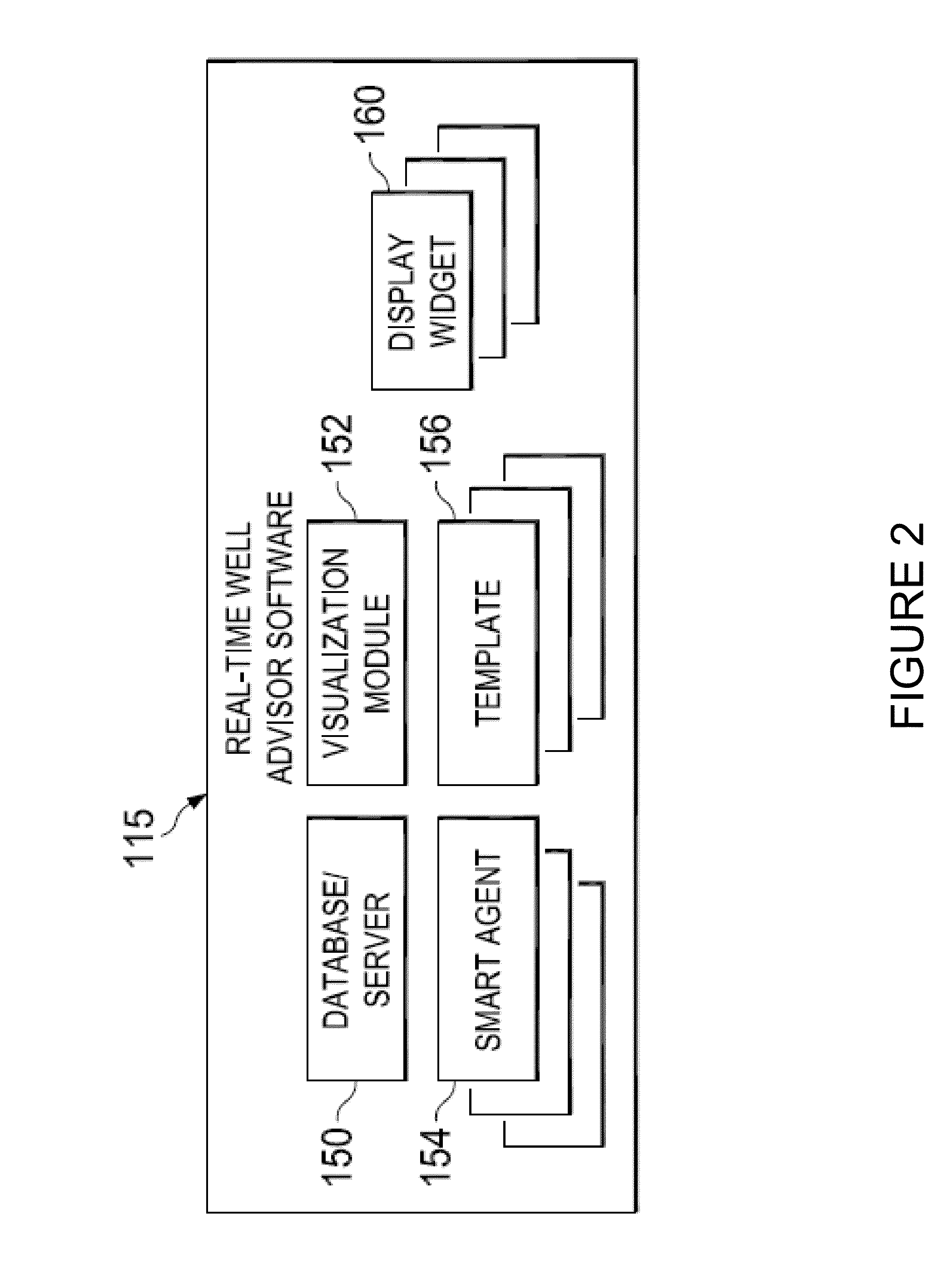

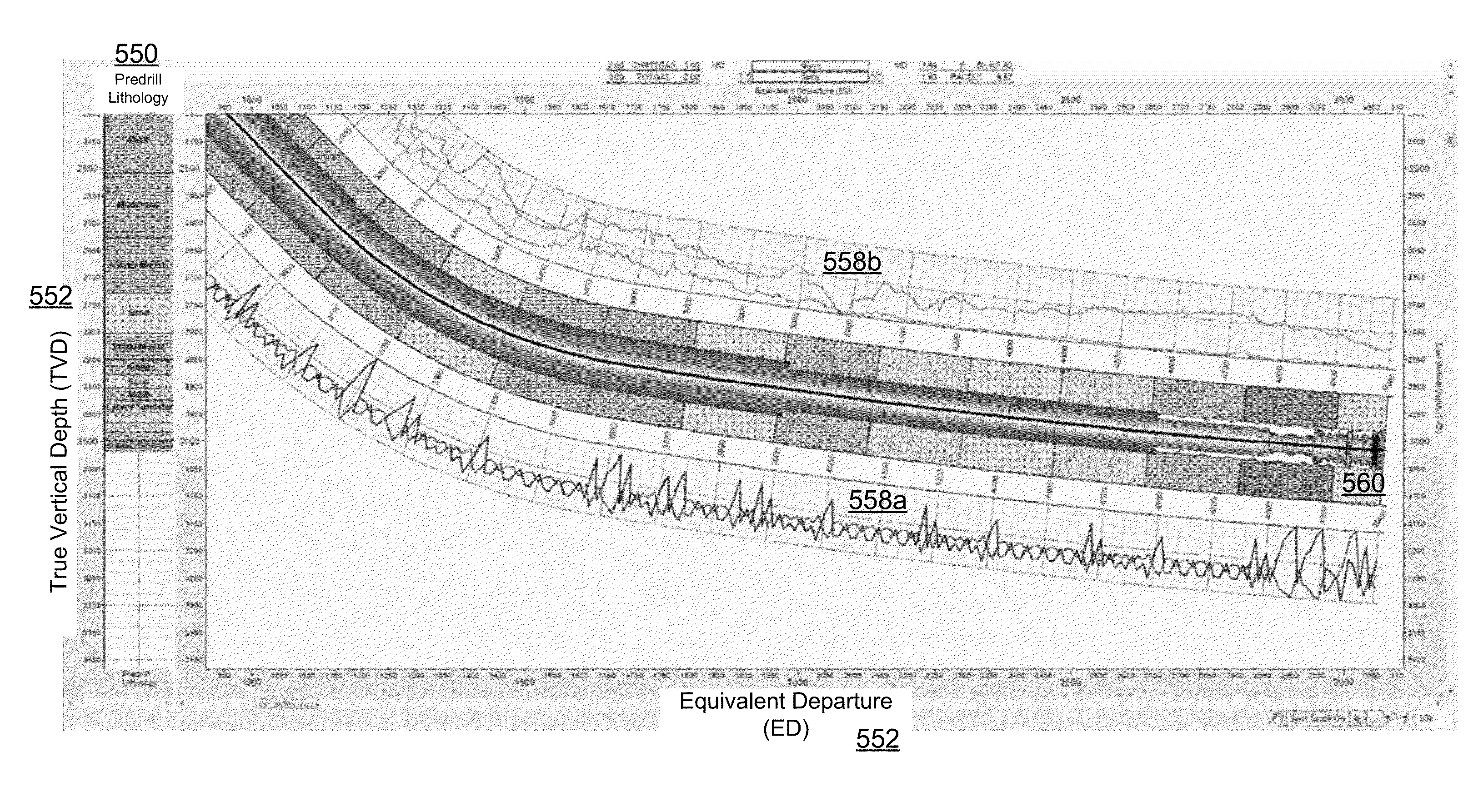

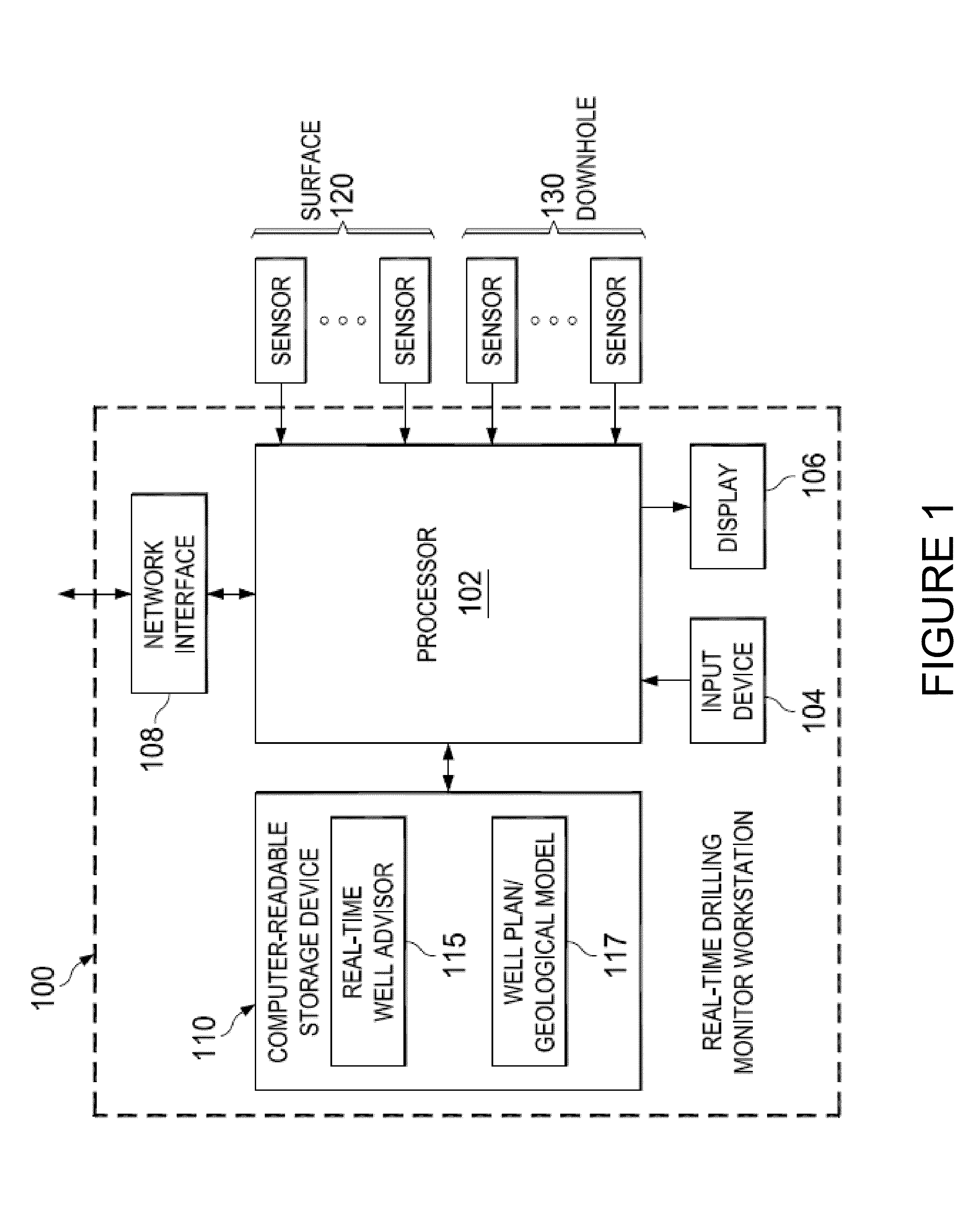

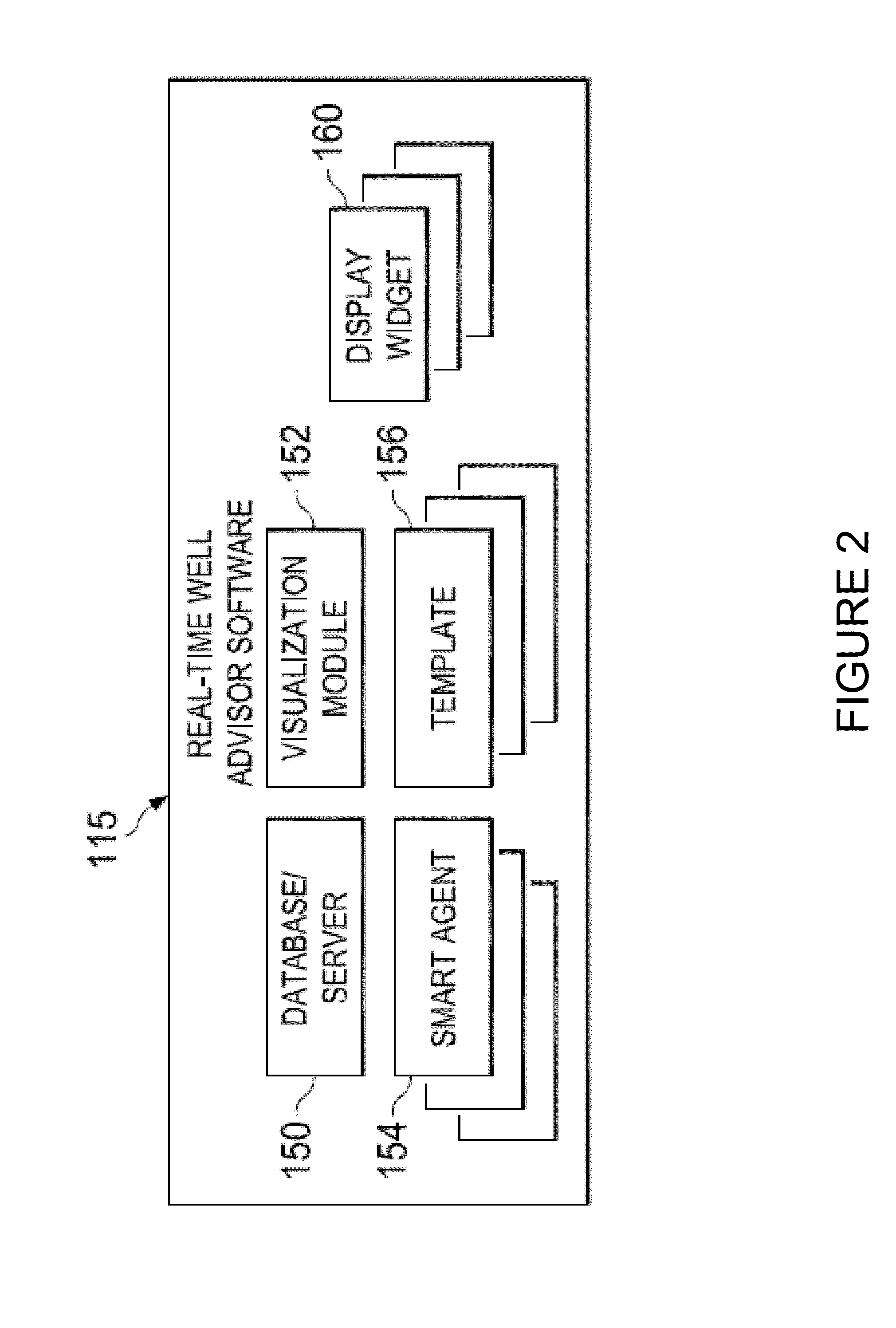

System and console for monitoring and managing well site operations

ActiveUS20150029034A1Reduces potential inaccuracyReduce delaysSurveyConstructionsGraphicsGraphical user interface

A well advisor system and console for monitoring and managing well drilling and production operations. The system may be accessed through one or more workstations, or other computing devices, which may be located at a well site or remotely. The system is in communication with and receives input from various sensors. It collects real-time sensor data sampled during operations at the well site. The system processes the data, and provides nearly instantaneous numerical and visual feedback through a variety of graphical user interfaces (“GUIs”), which are presented in the form of an operation-specific console. The input and data provides information related to geologic uncertainty concerning a well being drilled, with a focus on the safety of the drilling operation.

Owner:ABBASSIAN FEREIDOUN +13

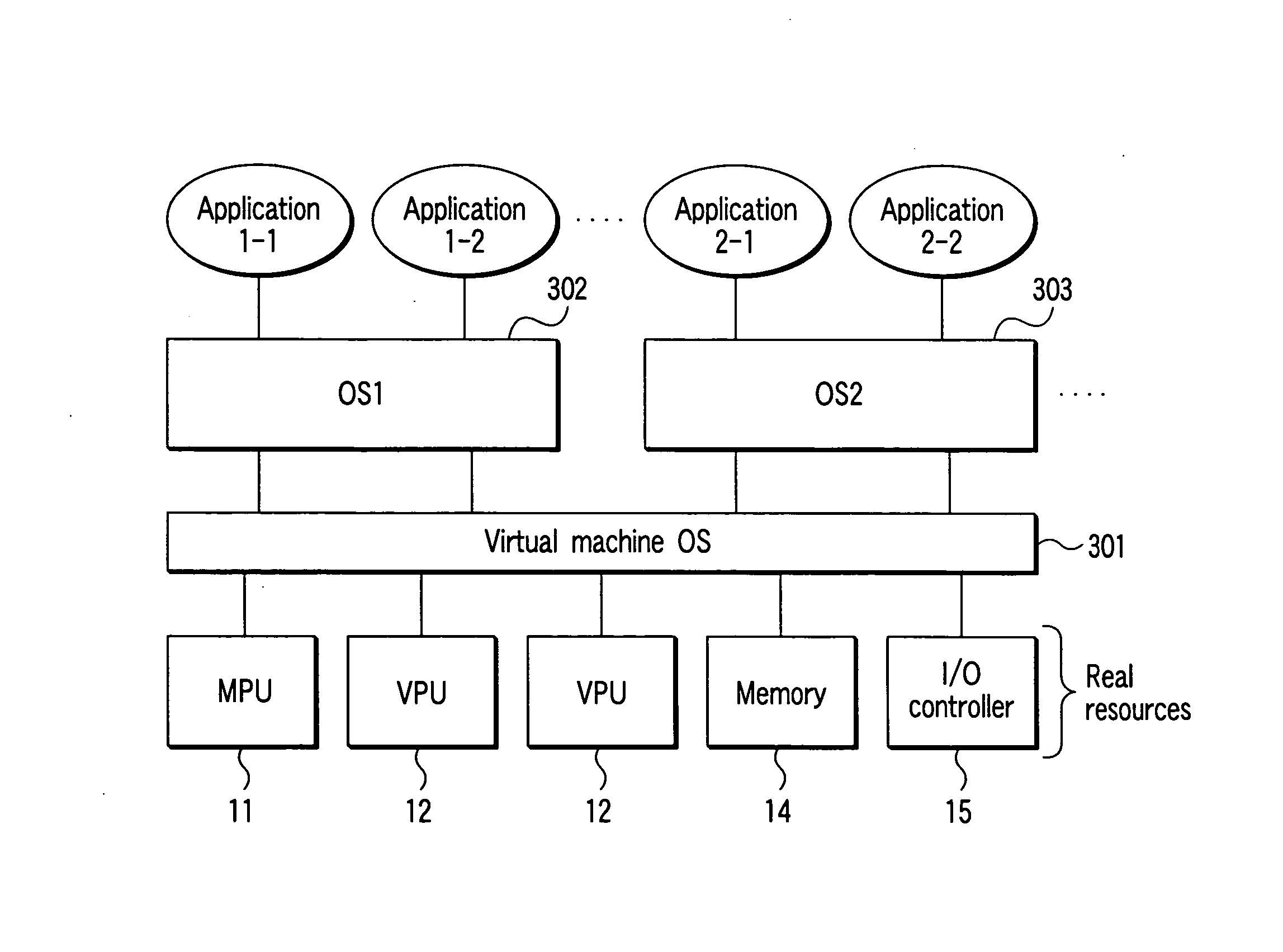

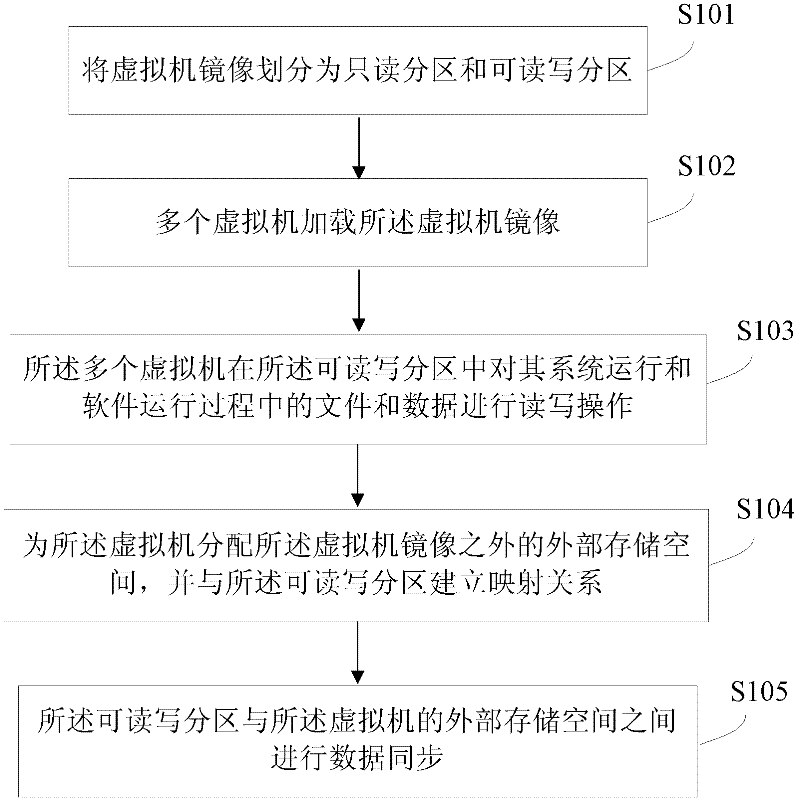

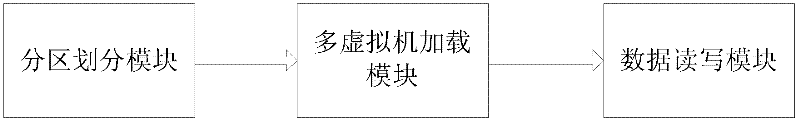

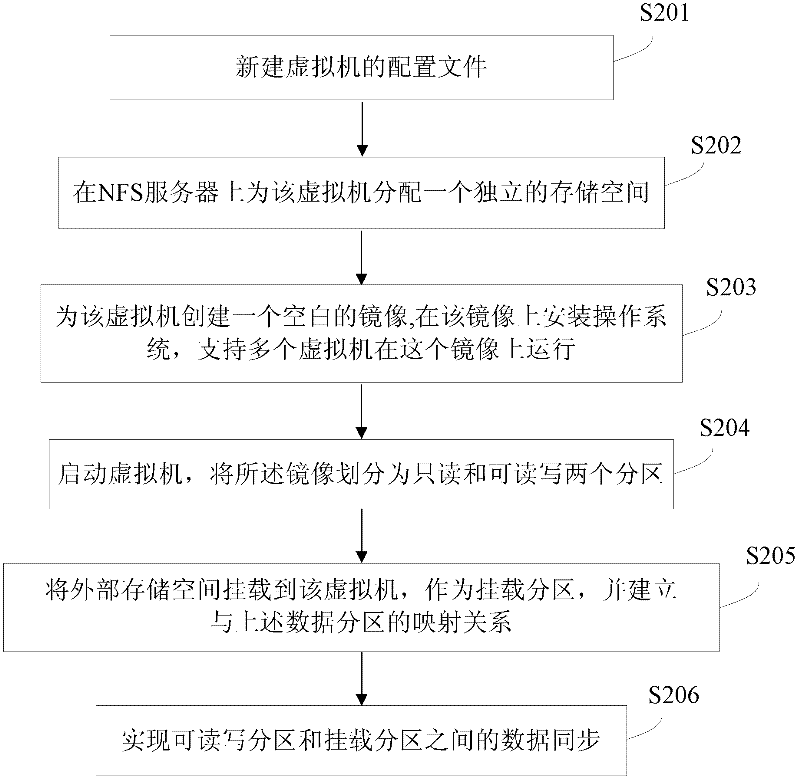

Method and system for operating multiple virtual machines

InactiveCN102521016APromote migrationEasy maintenanceSoftware simulation/interpretation/emulationWrite protectionBitwise operation

The invention discloses a method and a system for operating multiple virtual machines. The method comprises: a virtual machine mirror image is divided into a read-only partition and a read-write partition, wherein the read-only partition stores data which needs write-protection in a virtual machine mirror image; multiple virtual machines upload the virtual machine mirror image, wherein the multiple virtual machines perform reading / writing operation to files and data during system operation and software operation in the read-write partition. The system comprises a partition dividing module, a multiple virtual machine uploading module and a data reading / writing module. With the method and the system provided by the invention, the problem of file reading / writing conflict when multiple virtual machines operate on one same mirror image is avoided. In addition, updating and upgrade of virtual servers can be only performed to one mirror image to be synchronized to all nodes, such that not only the maintenance cost of virtual servers is saved, but also the maintenance time is shortened, furthermore, error possibility during updating and upgrade can be reduced or completely avoided.

Owner:ZTE CORP

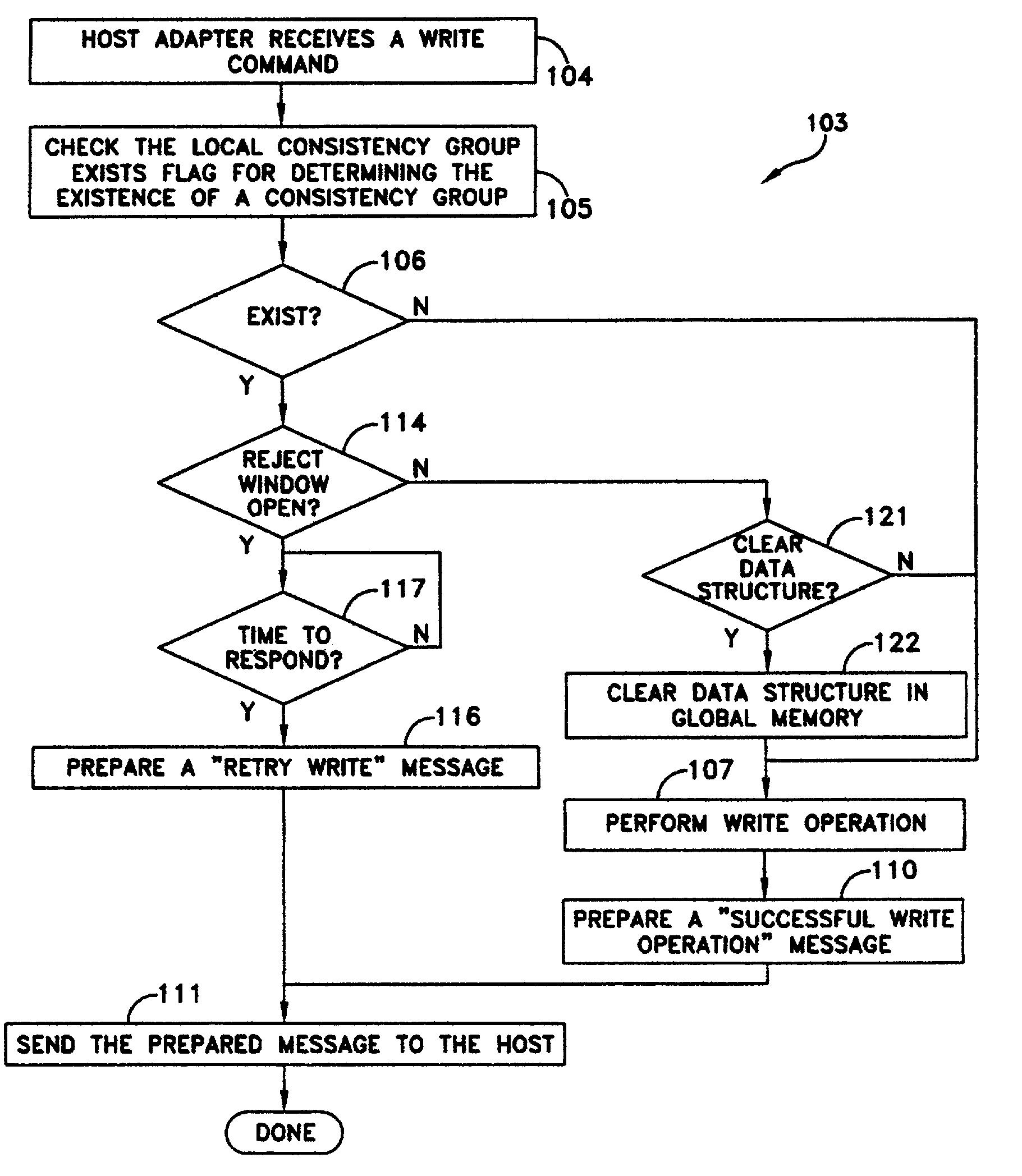

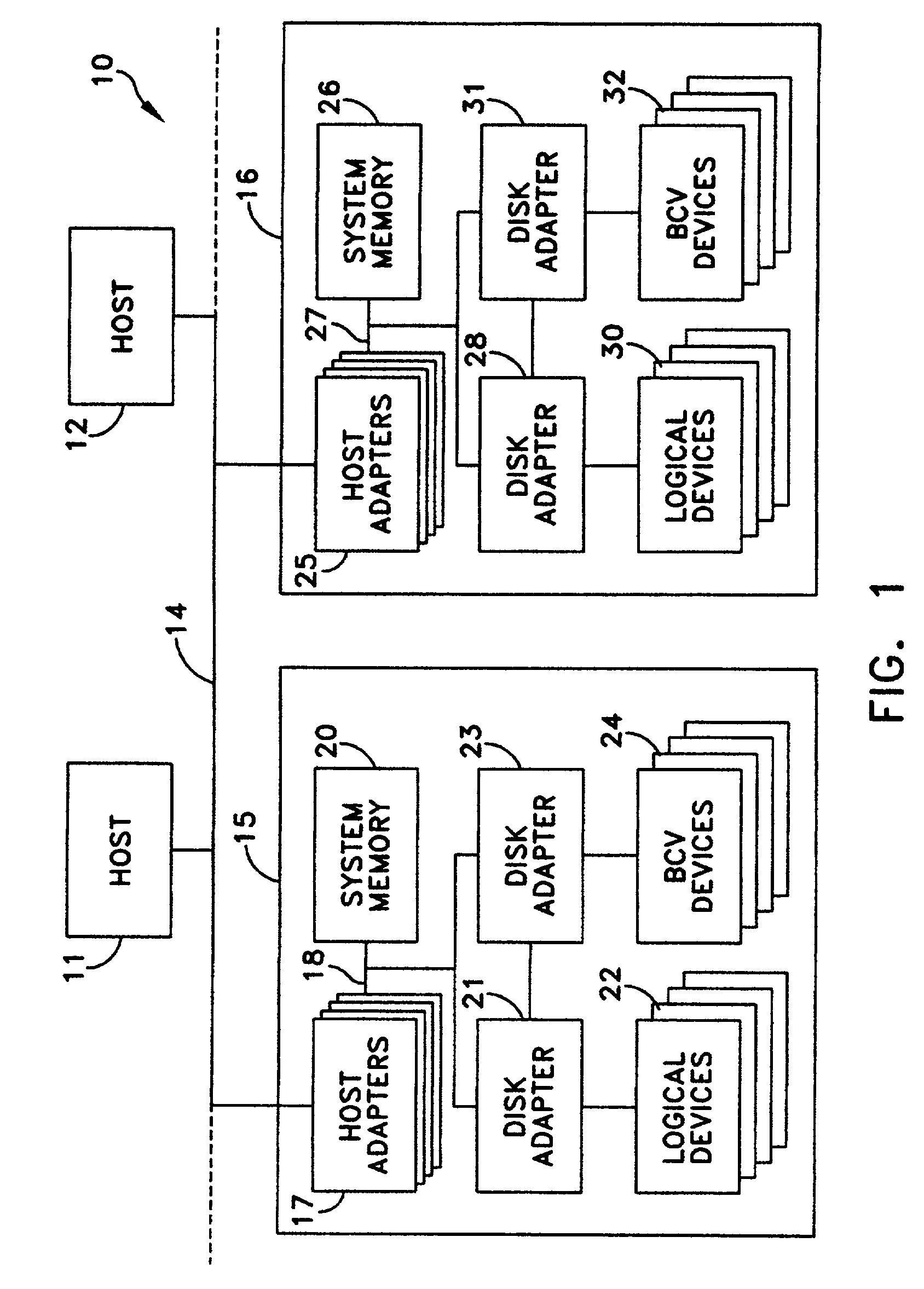

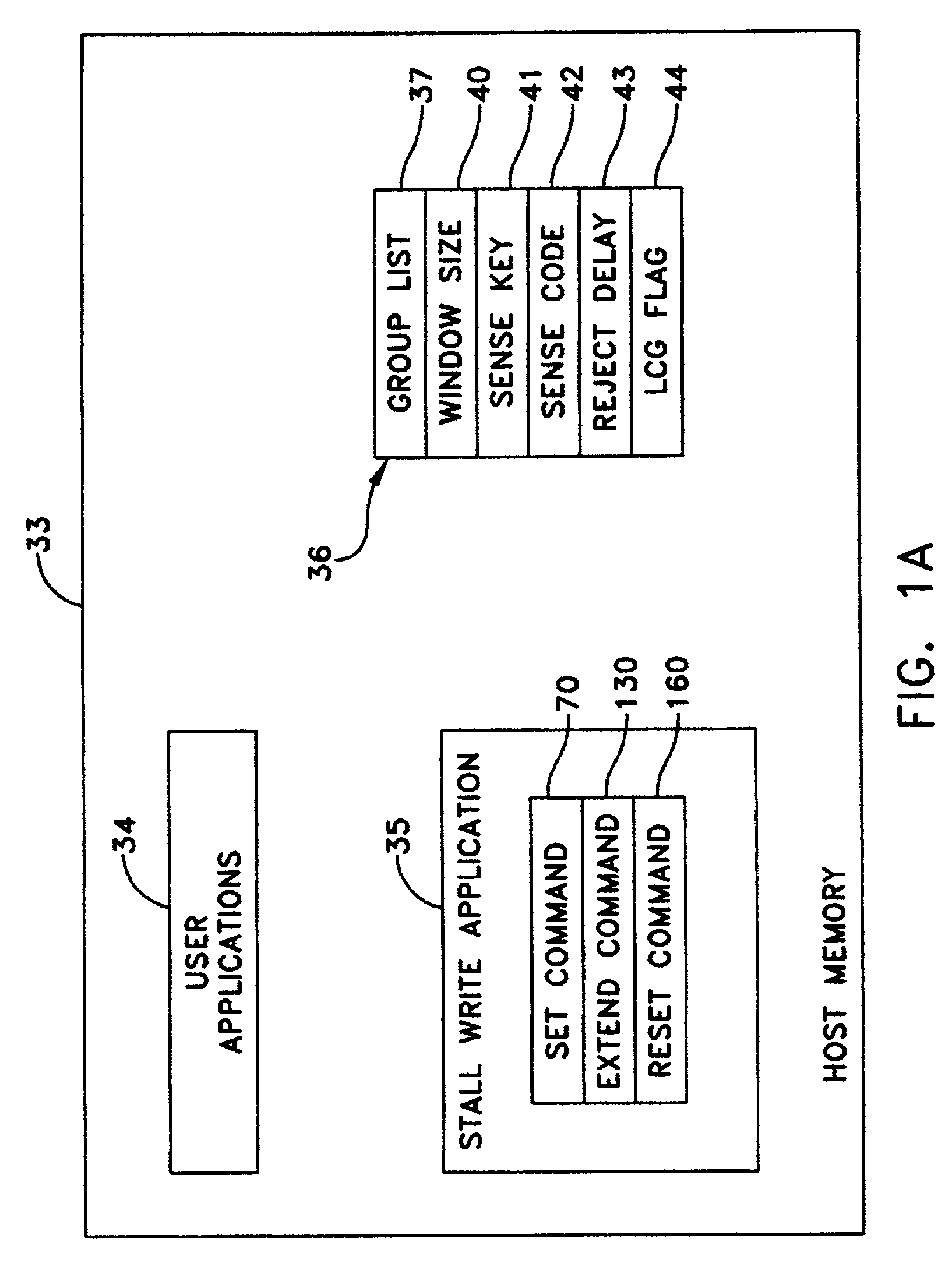

Method and apparatus for enhancing operations in disk array storage devices

InactiveUS6983353B2Easy to operateMinimizing certain delayInput/output to record carriersUnauthorized memory use protectionBitwise operationLocal consistency

A method and apparatus for assuring data consistency during certain operations involving dependent input / output sequences. During such operations a stall application blocks write operations to specified logical devices in a local consistency group while allowing read operations to all devices and write operations to non-specified logical devices. When a write command is directed to a logical device in local consistency group, the host adapter associated with the logical device returns a message to the host that initiates a write command retry. Retries generally continue until a write command is successful.

Owner:EMC IP HLDG CO LLC

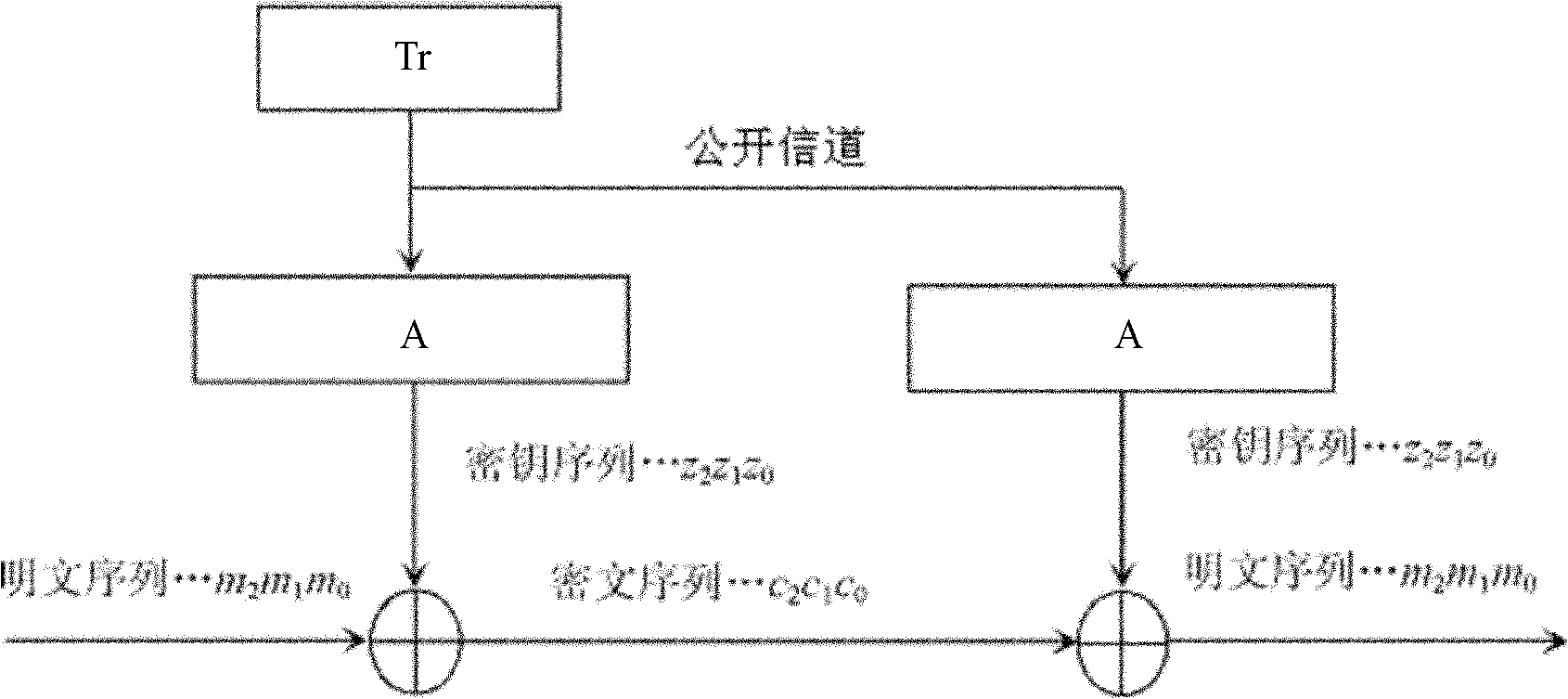

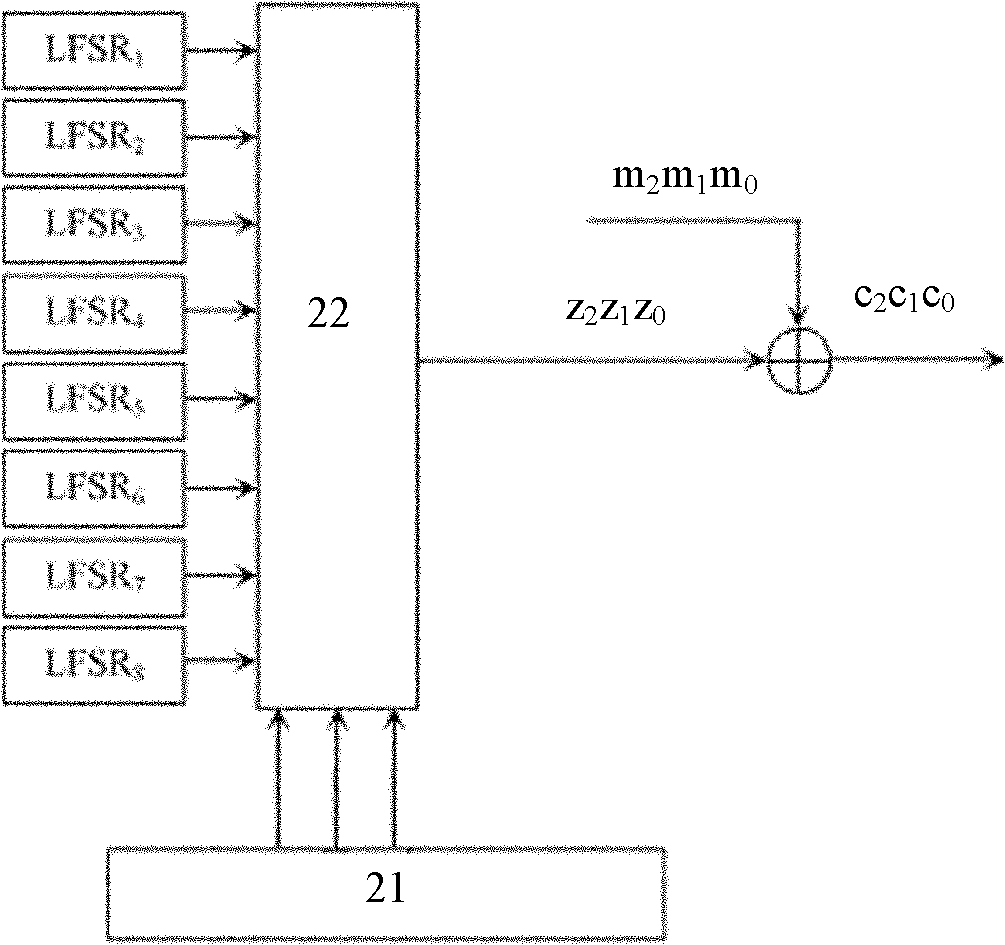

Public key cipher encrypting and decrypting method based on neural network chaotic attractor

ActiveCN101977112APublic key for secure communicationUser identity/authority verificationPlaintextDigital signature

The invention provides a public key cipher encrypting and decrypting method based on a neural network chaotic attractor with high safety and high encrypting speed, relating to the information encrypting technology. The public key cipher encrypting method is implemented as the following steps: inputting secret keys; generating a secret key sequence; and generating a cipher text. The public cipher decrypting method is implemented as the following steps: authenticating the identity of a sender by a receiver; decrypting the cipher text in case of a legal user by checking the digital signature andverifying the identity of the opposite side based on the identity information of the sender; otherwise, notifying a system administrator; and calculating a new synapsis connection matrix, generating a secret key sequence, performing xor bitwise operation on secret key sequences and cipher texts at random, and recovering a plaintext until the plaintext is completely recovered.

Owner:XIAMEN UNIV

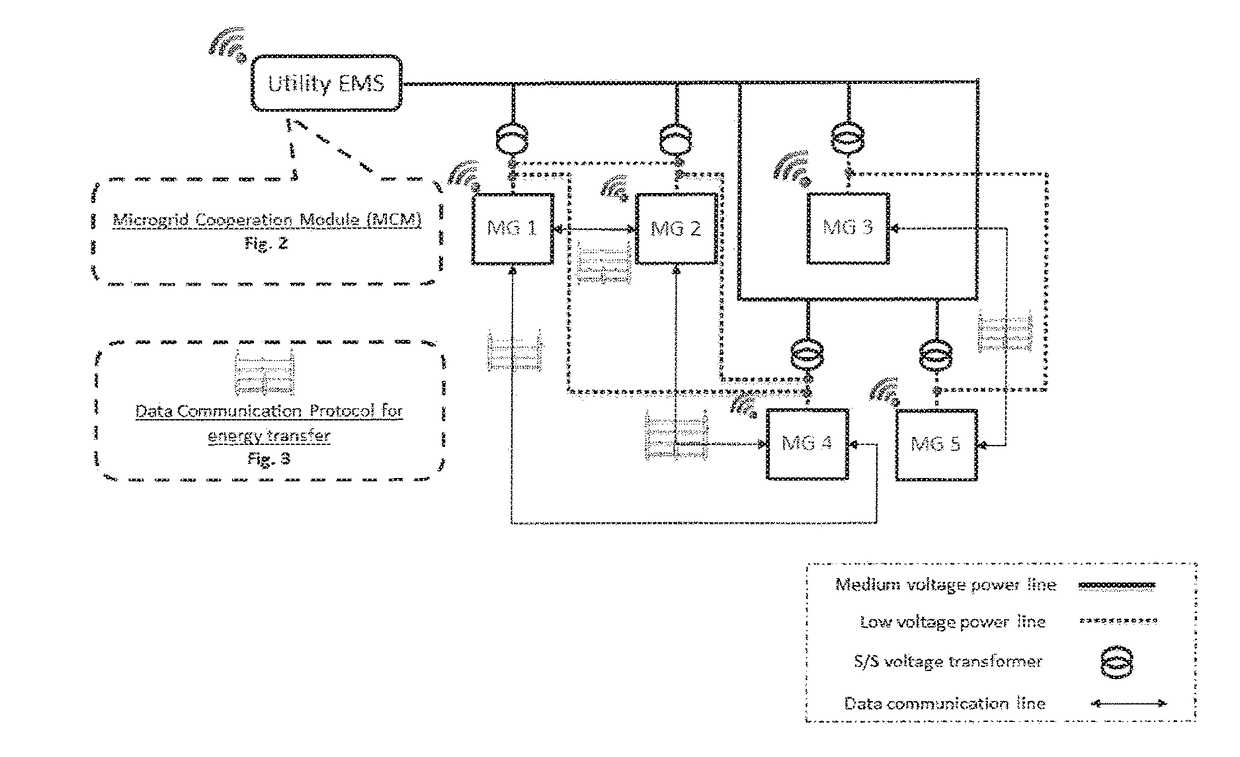

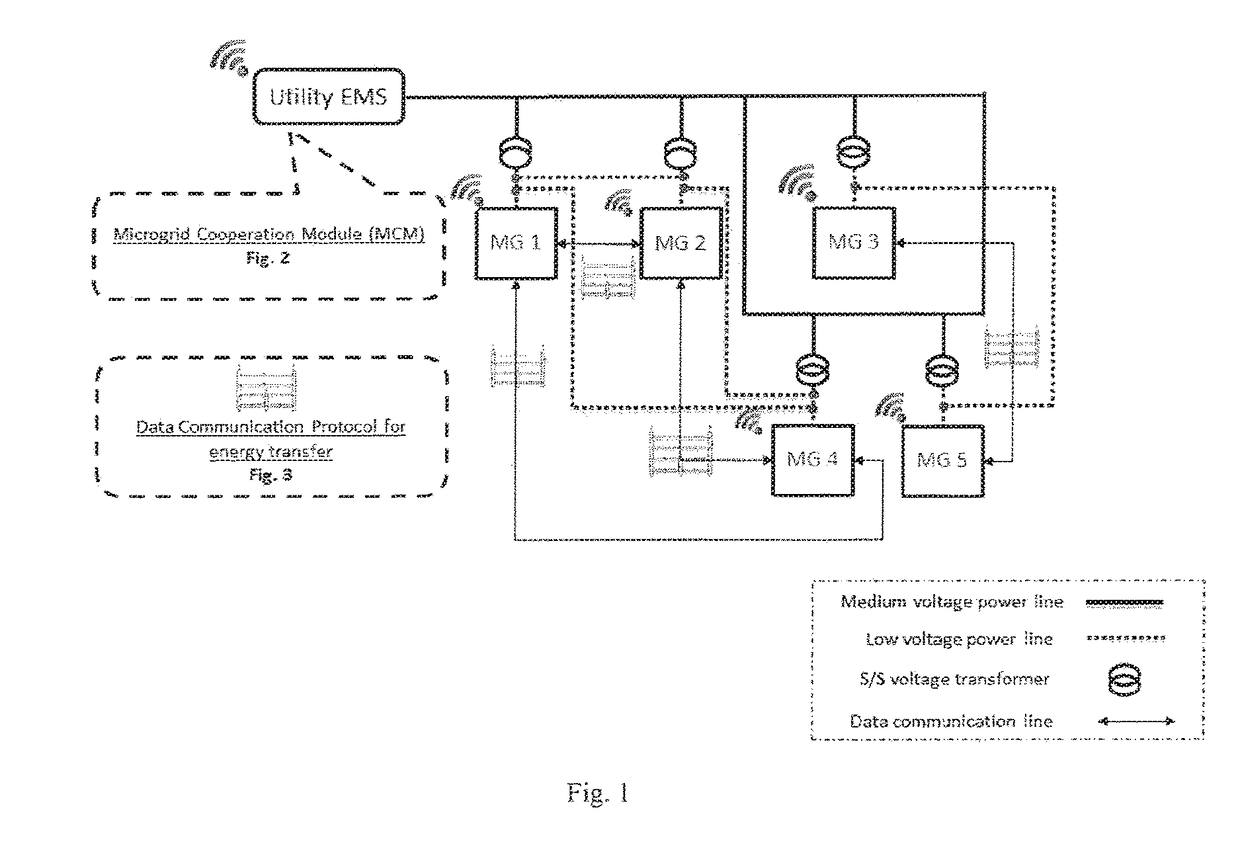

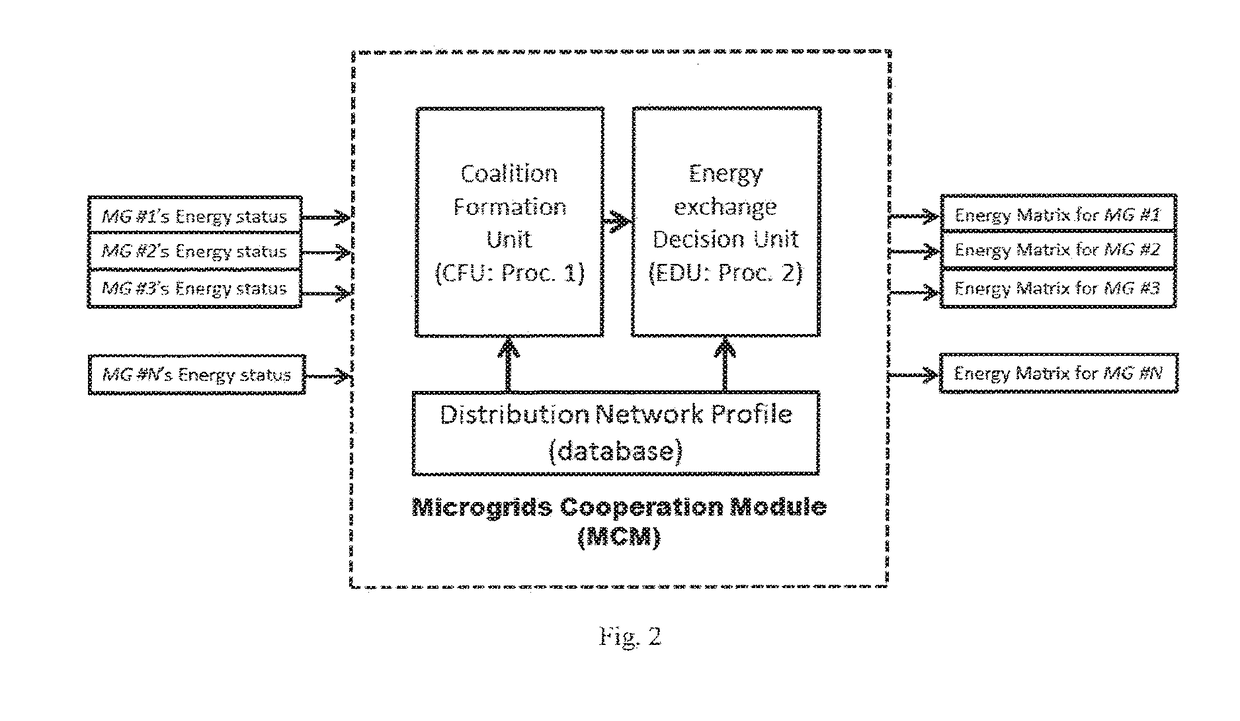

Electricity distribution system with dynamic cooperative microgrids for real-time operation

InactiveUS20170194814A1Reduce the burden onReduces equivalent power lossSingle network parallel feeding arrangementsResourcesMicrogridEngineering

System and methods for performing microgrids cooperation by optimal coalition formation in a distribution network are disclosed. A Microgrid Cooperation Module (MCM) is designed for utility EMS. MCM contains a coalition formation unit and an energy exchange decision unit. Furthermore, a communication protocol for energy exchange between two microgrids is designed. The coalition formation unit applies an innovative hierarchical coalition formation algorithm to provide optimal coalition for real time operation. The real time energy status of microgrids will be provided to coalition formation unit which will determine the coalitions (given a distance threshold) among microgrids to minimize the power loss. Energy exchange decision unit then determine actual energy transfer between pairs of microgrids within a coalition. Upon receiving the energy transfer information through a communication channel, the microgrids will start communicating and process energy transfer. The optimality of the formed coalitions is ensured by performing coalitional game theoretical analysis.

Owner:NEC CORP

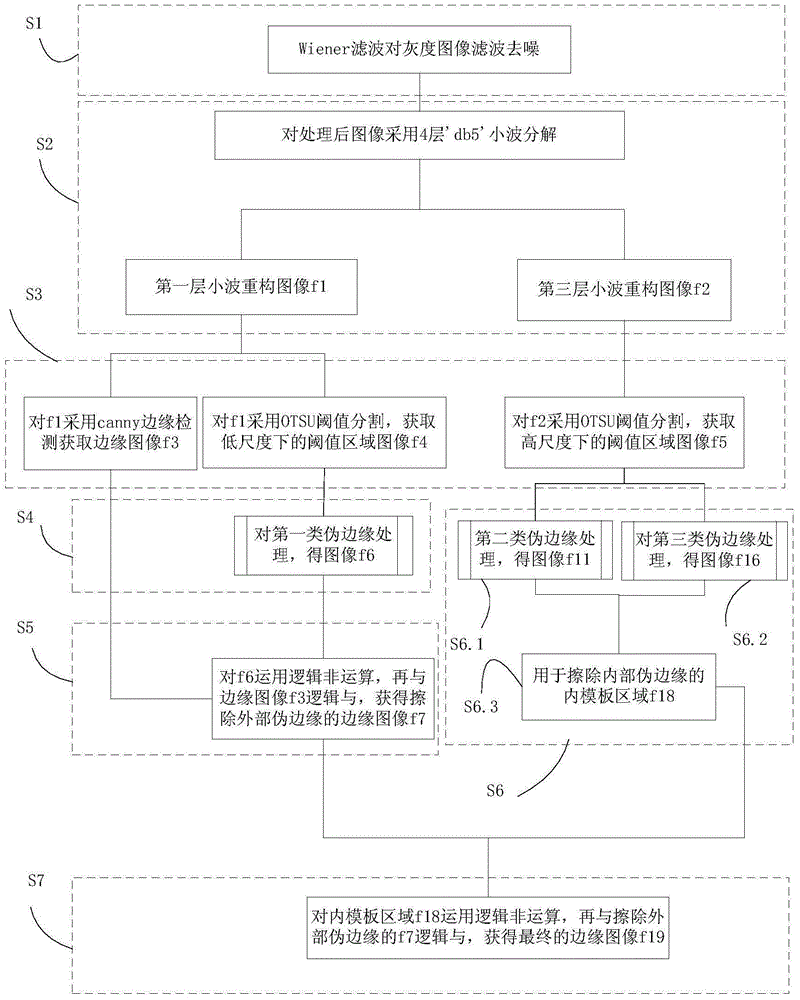

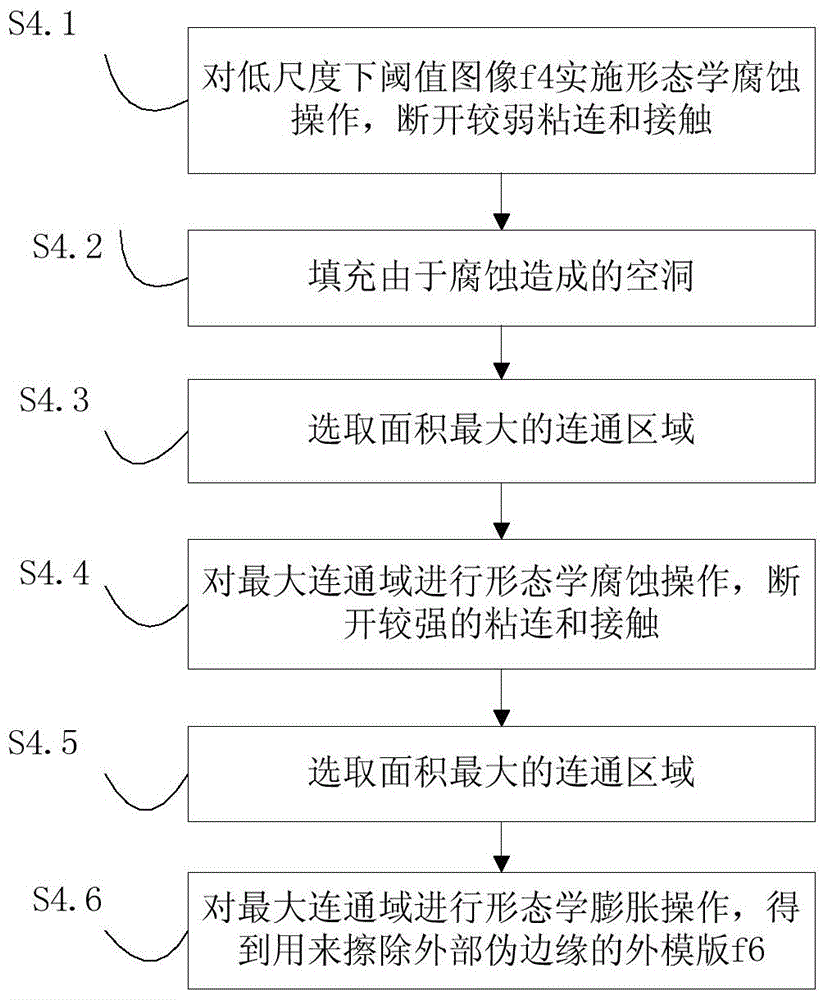

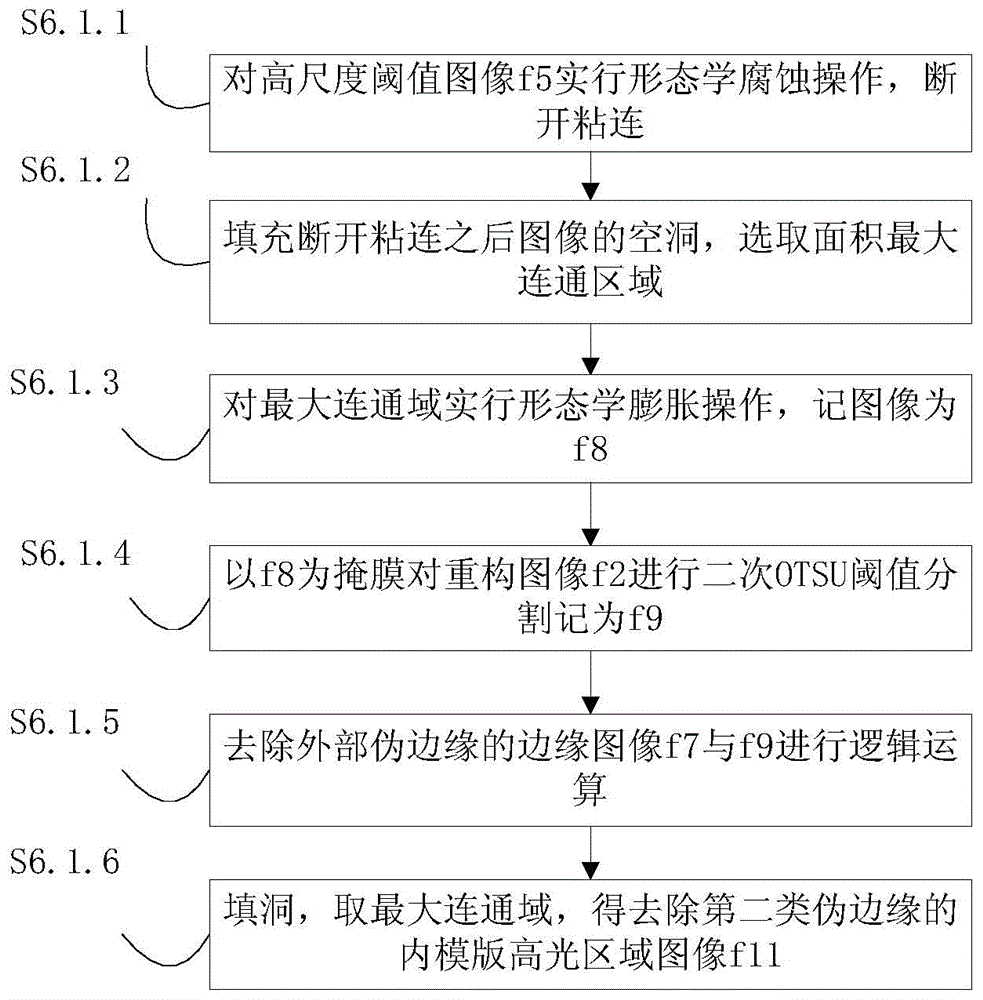

Multi-scale analysis-based greenhouse field plant leaf margin extraction method and system

ActiveCN104318546AReduce false recognition rateImprove edge detection accuracyImage enhancementImage analysisMultiple-scale analysisLeaf recognition

The invention belongs to the digital image processing technical field and relates to a multi-scale analysis-based greenhouse field plant leaf margin extraction method and system. According to the method, differences of information of images in different scale spaces are utilized, and different segmentation methods are selected, and comprehensive analysis is performed, and as a result, ideal segmentation results can be obtained; after an experimental image is obtained, proper smoothing filtering is performed on the image, and classified processing is performed on different types of pseudo edges in the image; and based on different situations of Canny edge detection in a comprehensive scale space and OTSU threshold segmentation in different scales and different characteristics of various kinds of pseudo edges, with methods such as morphological processing and logical operation methods adopted, internal and external pseudo edges are removed through utilizing bitwise operation, and therefore, edge detection accuracy can be improved, and leaf recognition error rate can be reduced.

Owner:CHINA AGRI UNIV

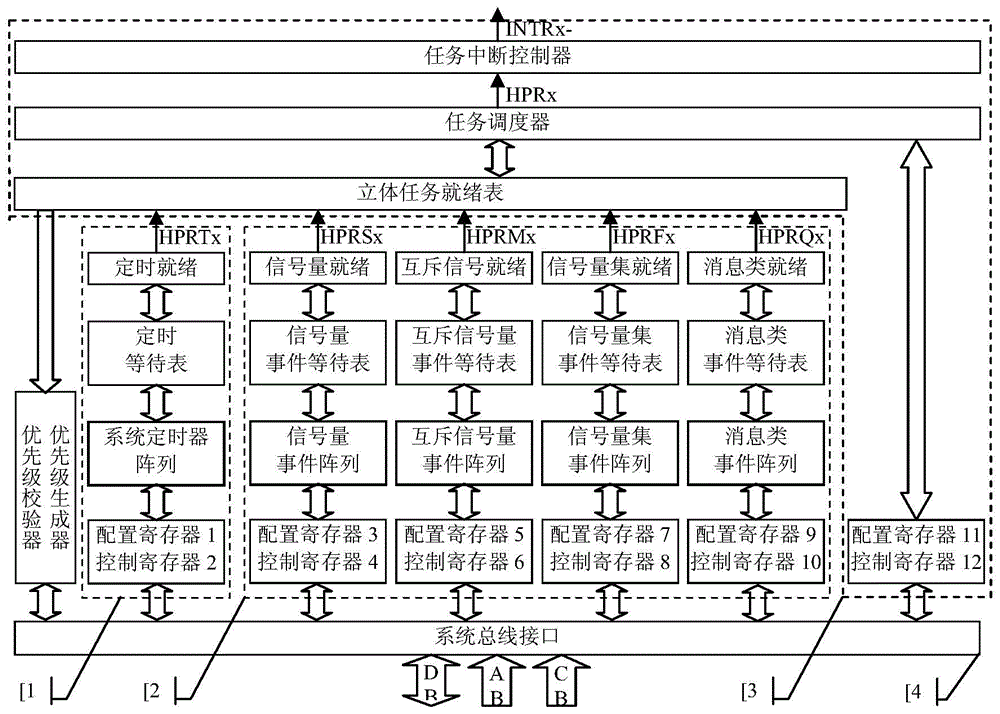

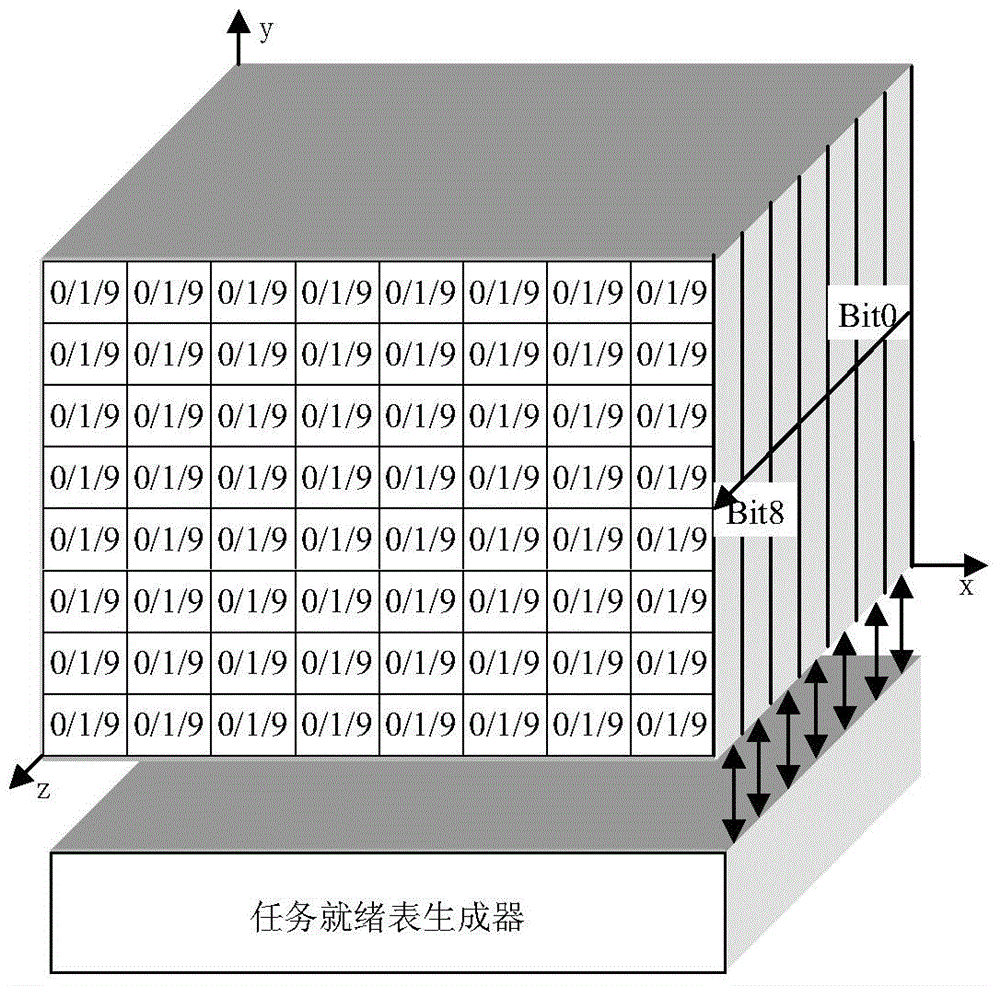

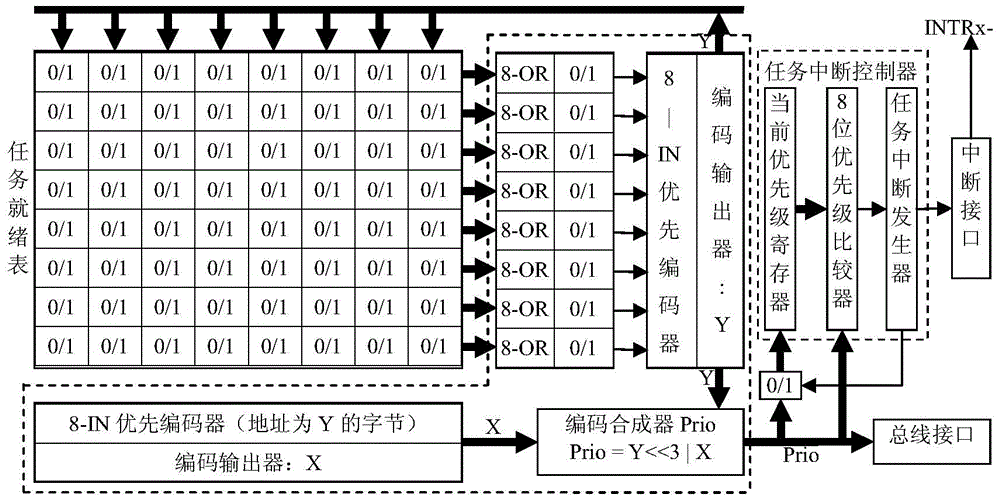

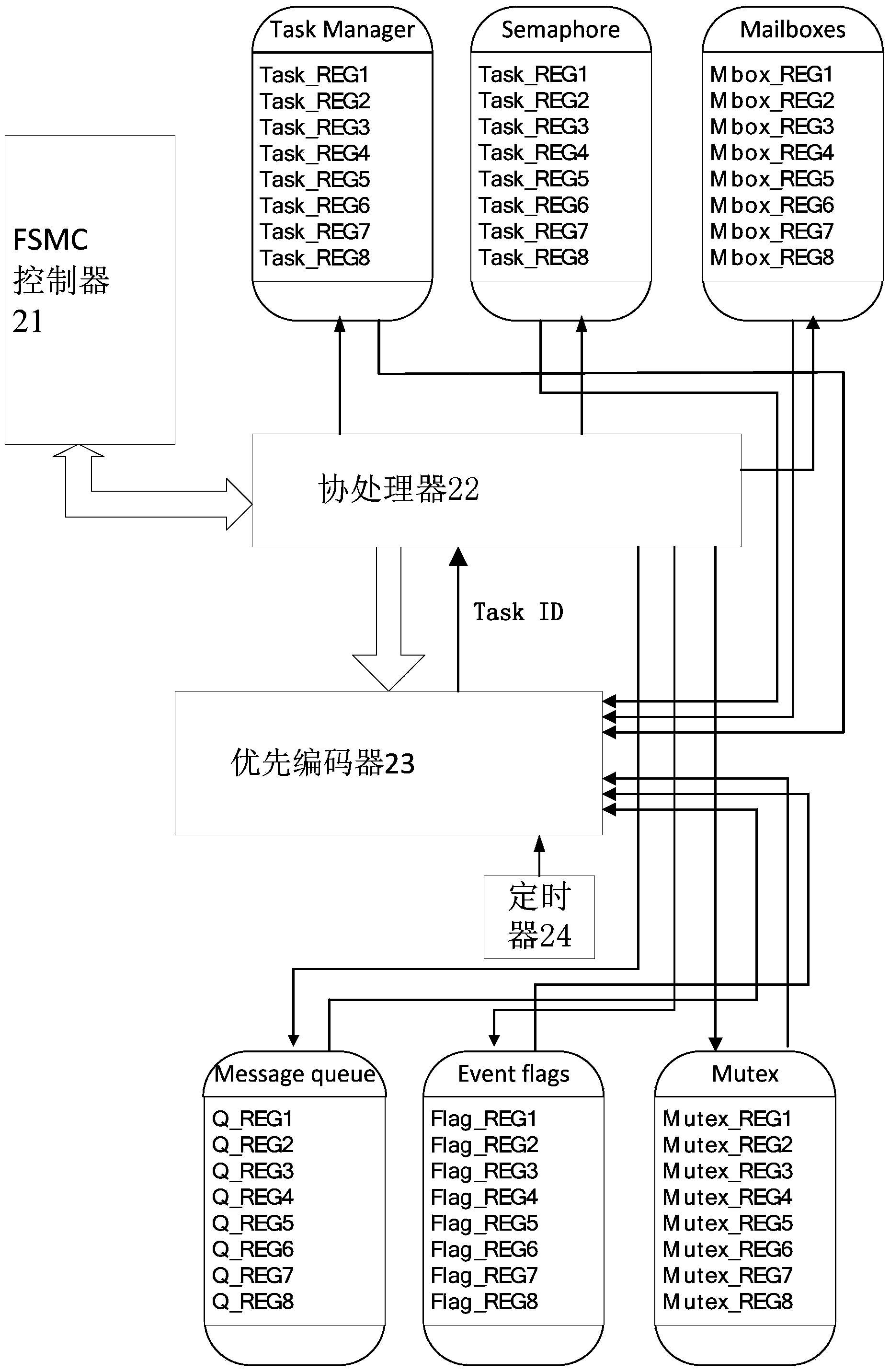

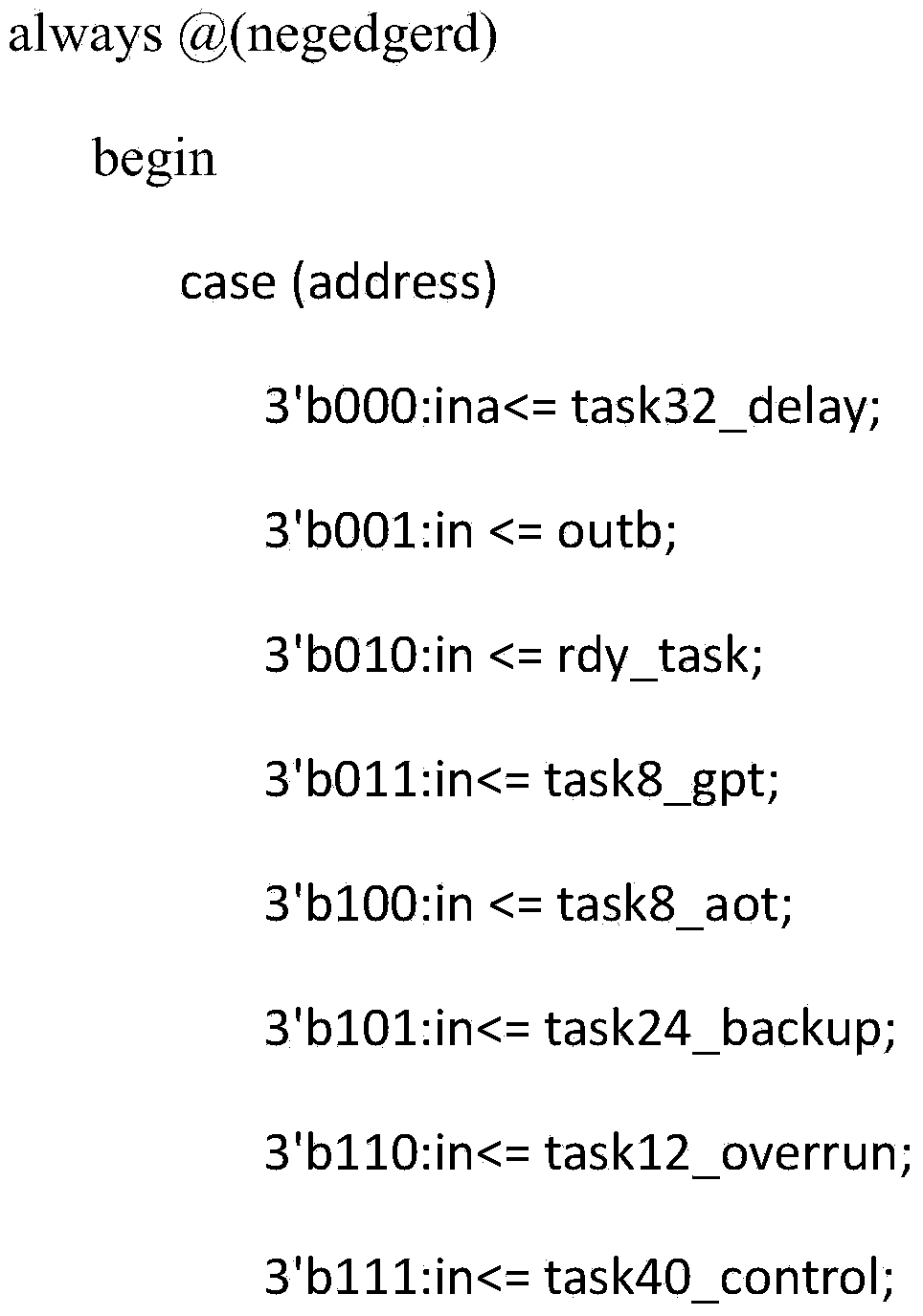

Hardware real-time operation system

InactiveCN103559045AImplement task switchingReduce couplingSpecific program execution arrangementsEmbedded technologyOperational system

The invention belongs to the technical field of computer equipment and relates to a hardware real-time operation system. A timing manager is used for realizing time delay and periodic execution of a task through a hardware timer; a task manager is used for realizing operation management of a task control block queue; an event manager is used for realizing operation and management of a semaphore control block, a mutually exclusive semaphore control block, a semaphore set control block, a message mailbox control block and an event control block of a message queue control block; and a bus interface manager is used for realizing data transmission and control between a processor and the real-time operation system. The hardware real-time operation system has a reliable design principle, an advanced design concept and a scientific contract technical means, adopts a cross embedded technology and an integrated circuit technology to achieve a hardware real-time operation system IC (integrated circuit), effectively improves real-time performance, reliability and stability of the real-time operation system, and has wide development and application values.

Owner:QINGDAO UNIV

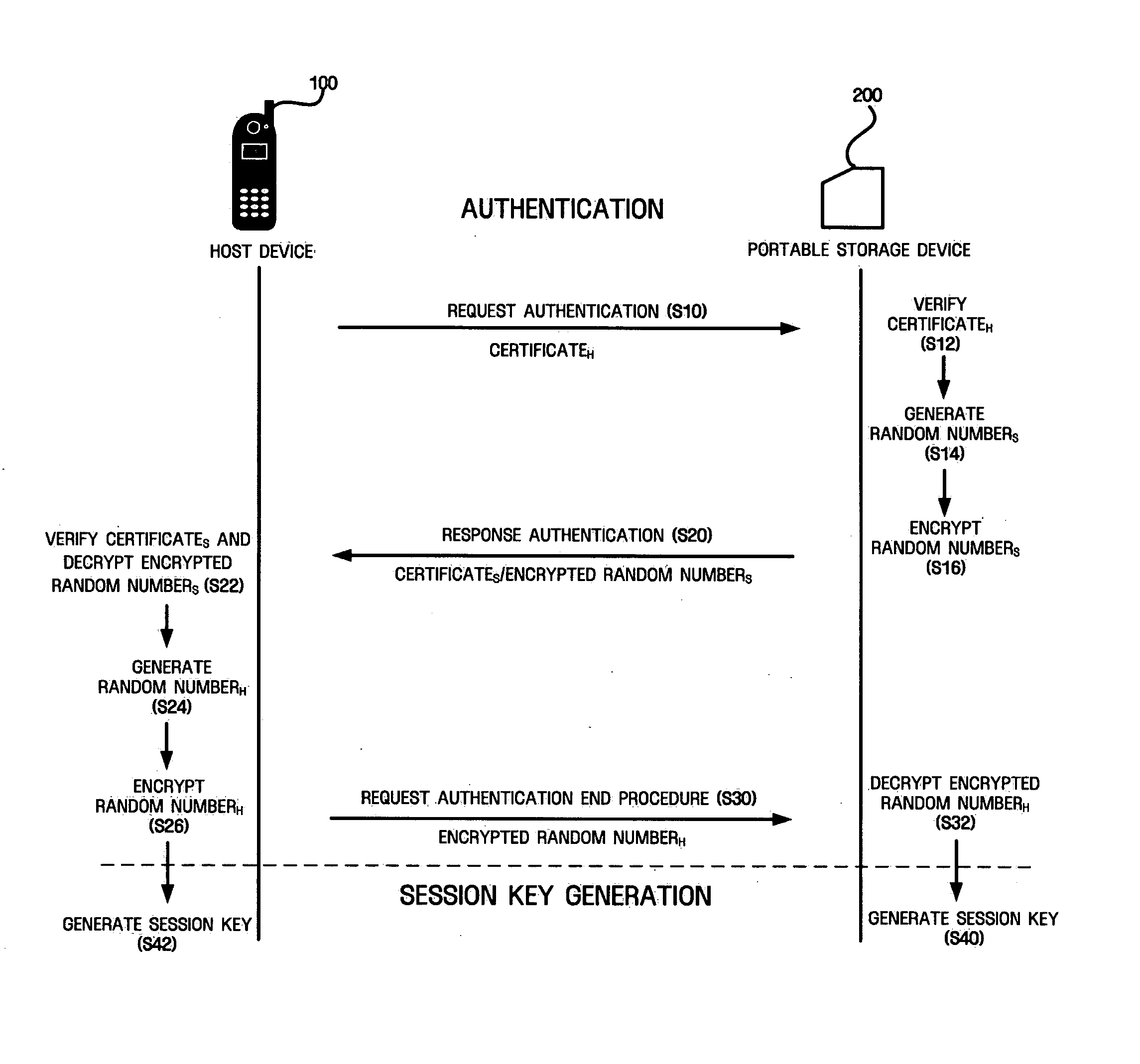

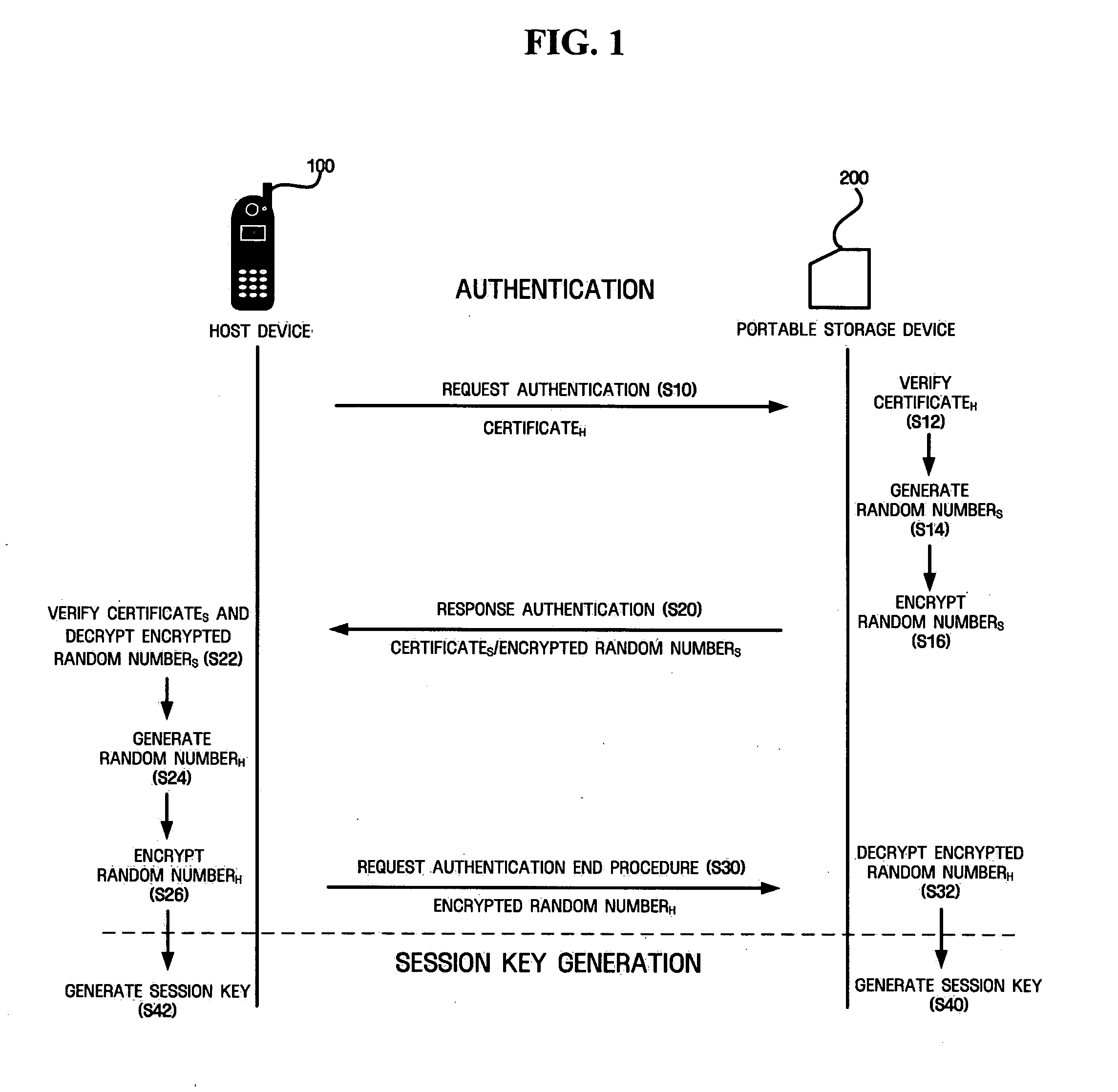

Host device, portable storage device, and method for updating meta information regarding right objects stored in portable storage device

ActiveUS20060156413A1Operation quantity can be reducedReduce in quantityTelevision system detailsDigital data processing detailsComputer hardwareBitwise operation

A host device, a portable storage device, and a method of updating an RO stored in the portable storage device are provided. The method includes receiving a predetermined bitmap from a host device, performing a bitwise operation on the received bitmap and meta information indicating a state of the RO, and updating the meta information using a result of the bitwise operation.

Owner:SAMSUNG ELECTRONICS CO LTD

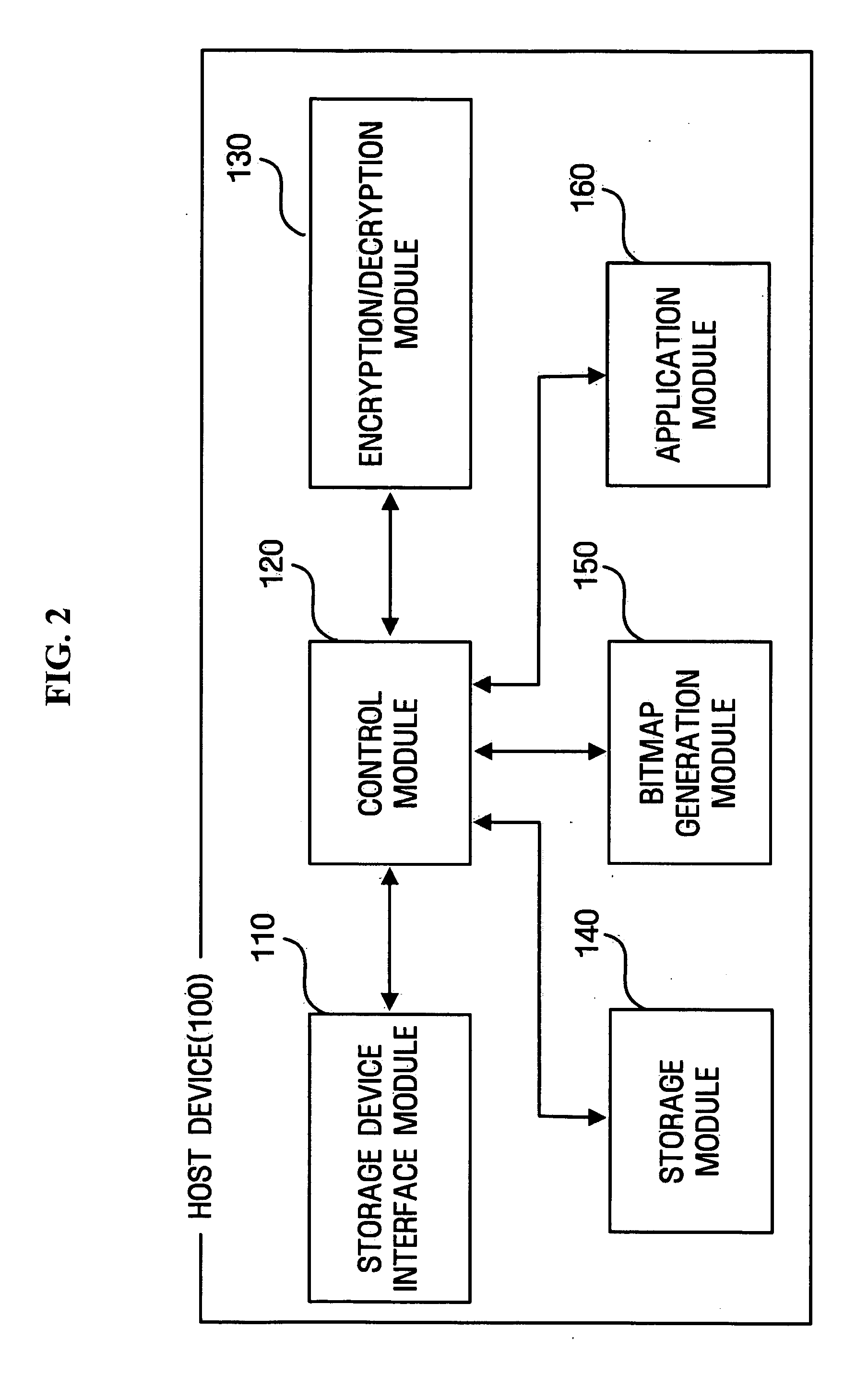

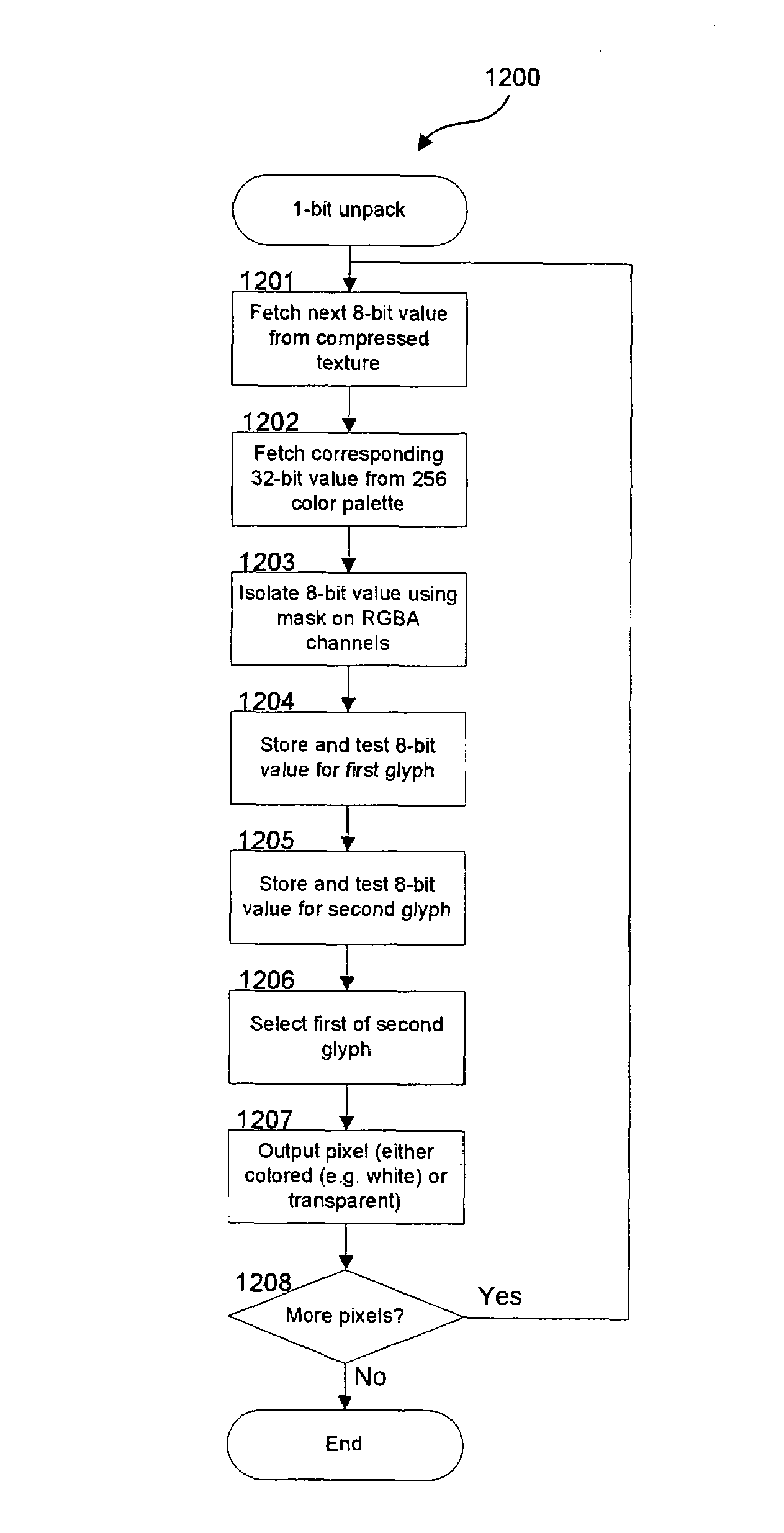

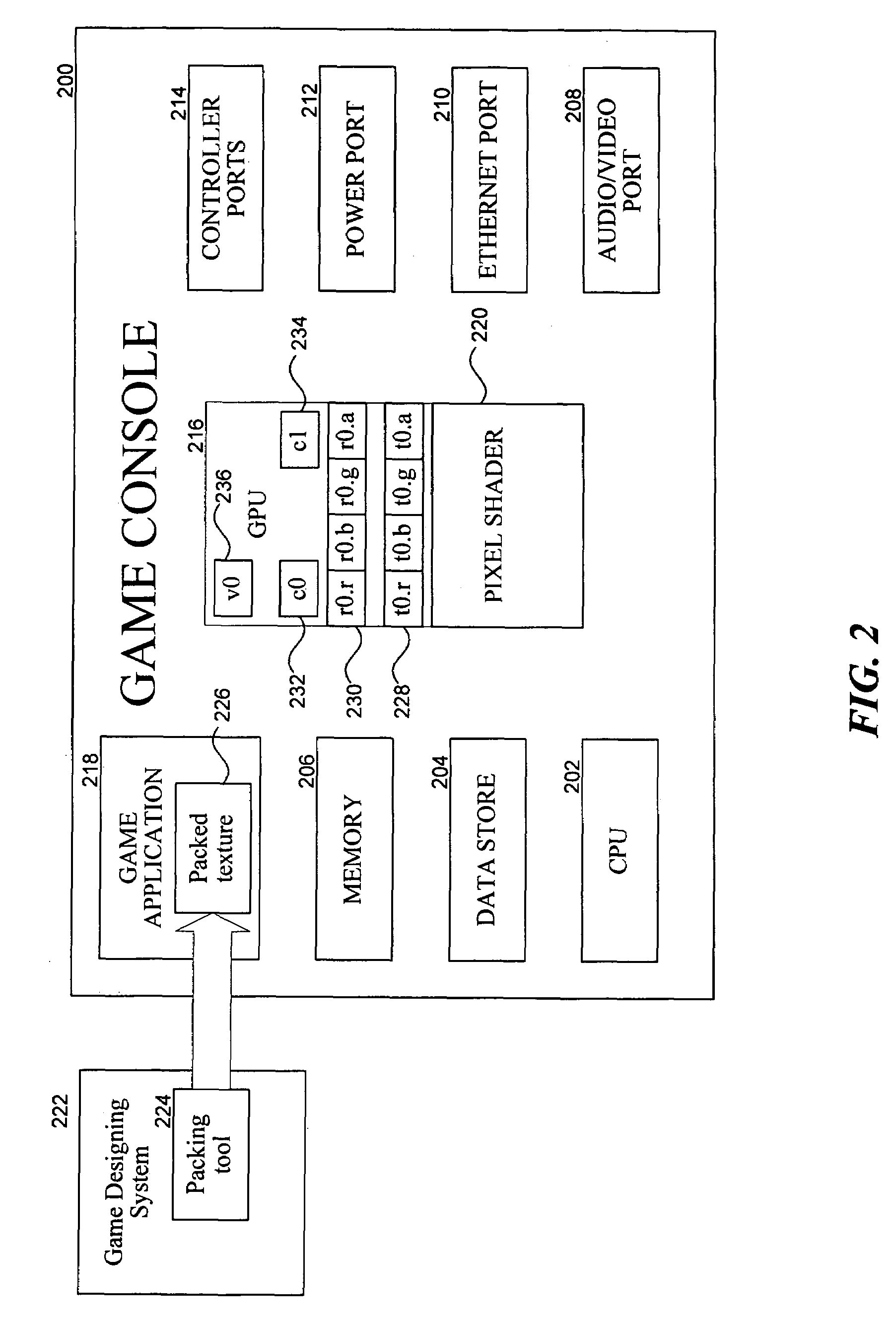

Texture-based packing, such as for packing 8-bit pixels into two bits

InactiveUS7643032B2Easy to processCharacter and pattern recognitionCathode-ray tube indicatorsPattern recognition8-bit color

A method and system for rendering three-dimensional graphics, including text, provide a compressed texture bitmap. The texture bitmap may represent multiple symbols, each comprised of multiple pixels. Each pixel in the texture bitmap may store information for more than one symbol, including compressed pixels corresponding to multiple distinct symbols. For example, the compressed texture bitmap may have n-bit pixels (e.g., 8-bit pixels) that each store m (e.g., four) n / m-bit (e.g., 2-bit) compressed values. The compressed texture bitmap may be configured for unpacking by a conventional pixel shader, such as a pixel shader that does not typically perform bitwise operations. The unpacking may include matching a fetched pixel to a value in a lookup table, such as a 32-bit value from a 256-color palette. The looked-up value can be separated into separate sub-values to facilitate processing by the pixel shader. For example, the looked-up value can be split into RGBA values conventionally used in processing colored pixels.

Owner:MICROSOFT TECH LICENSING LLC

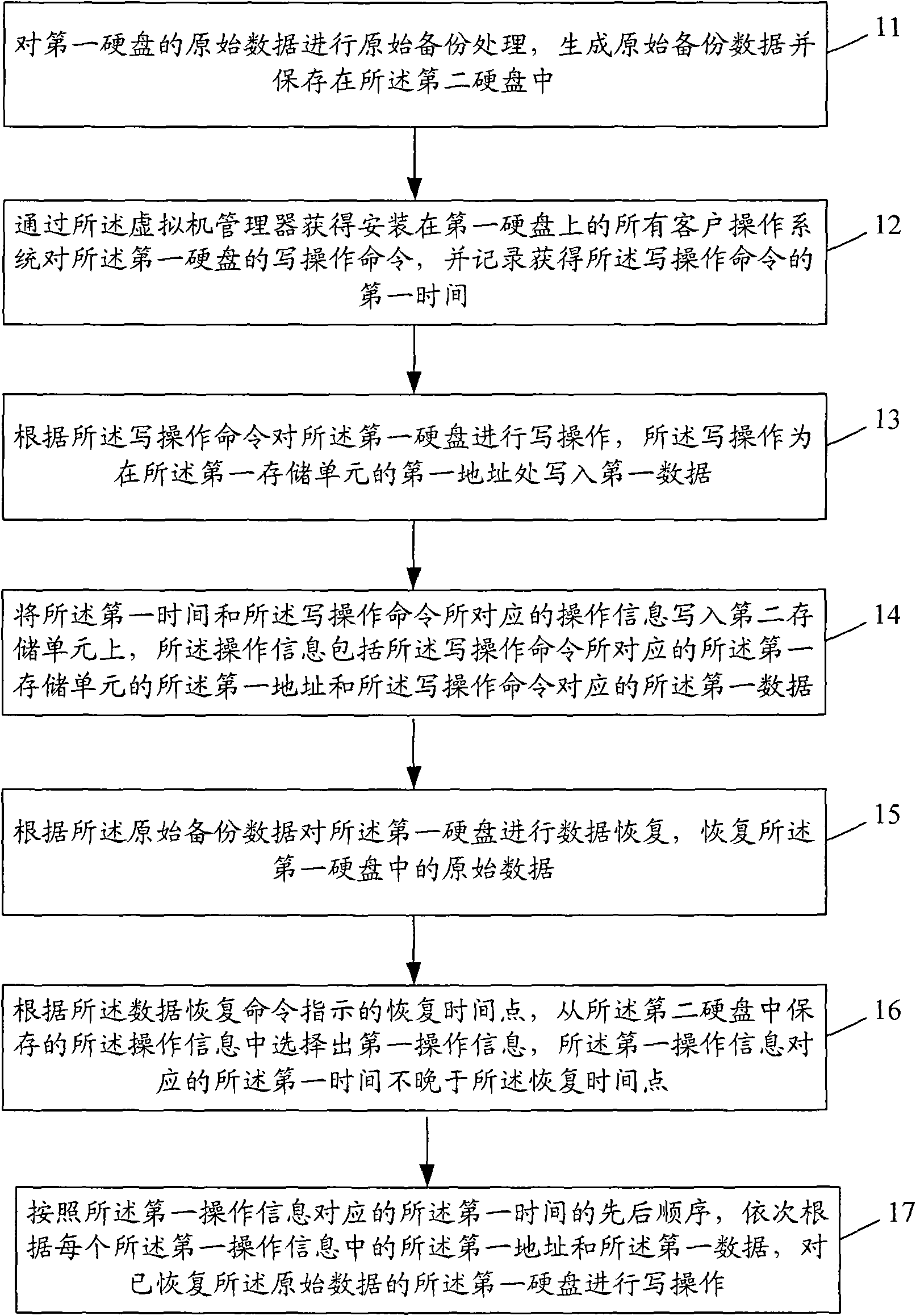

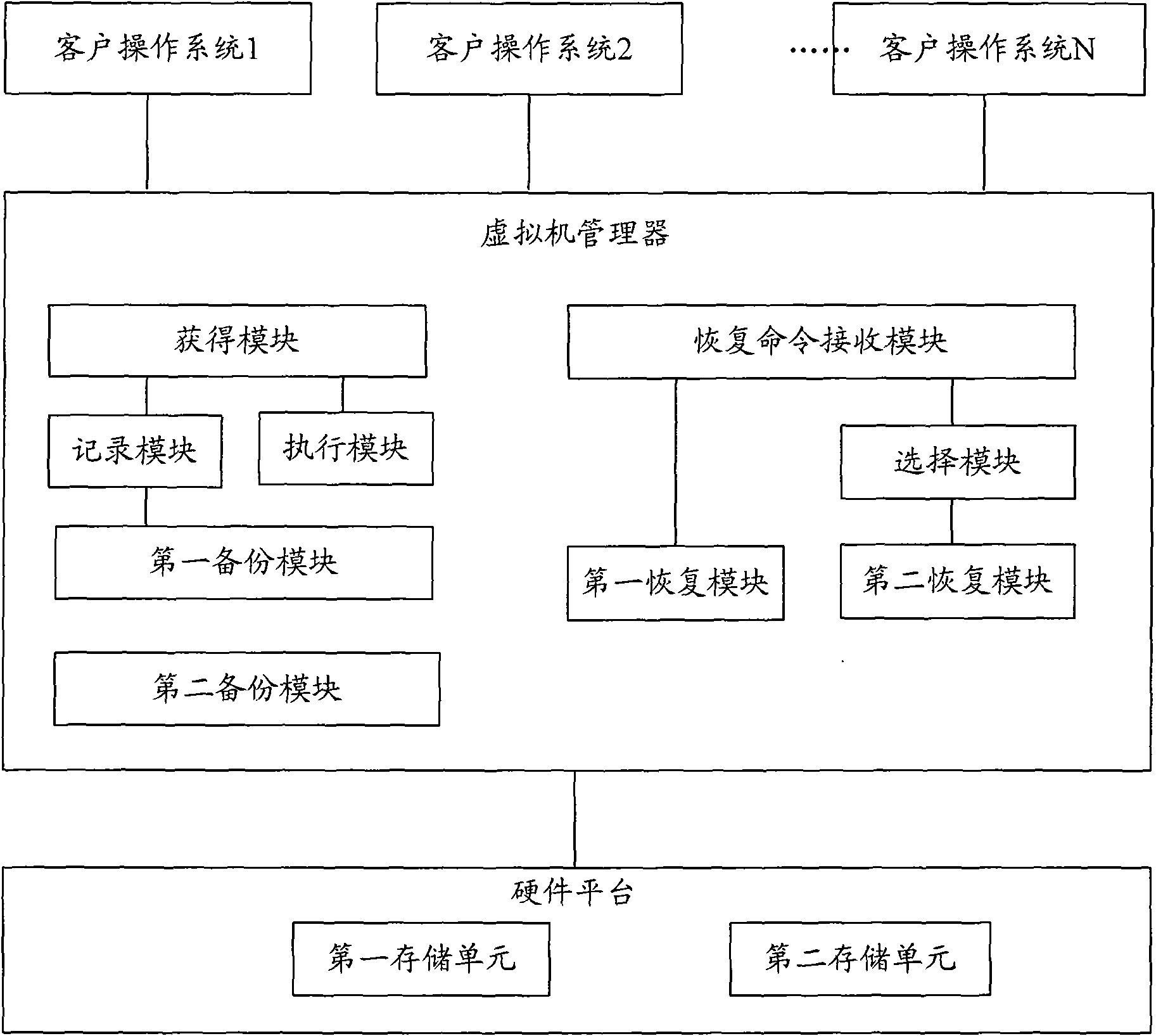

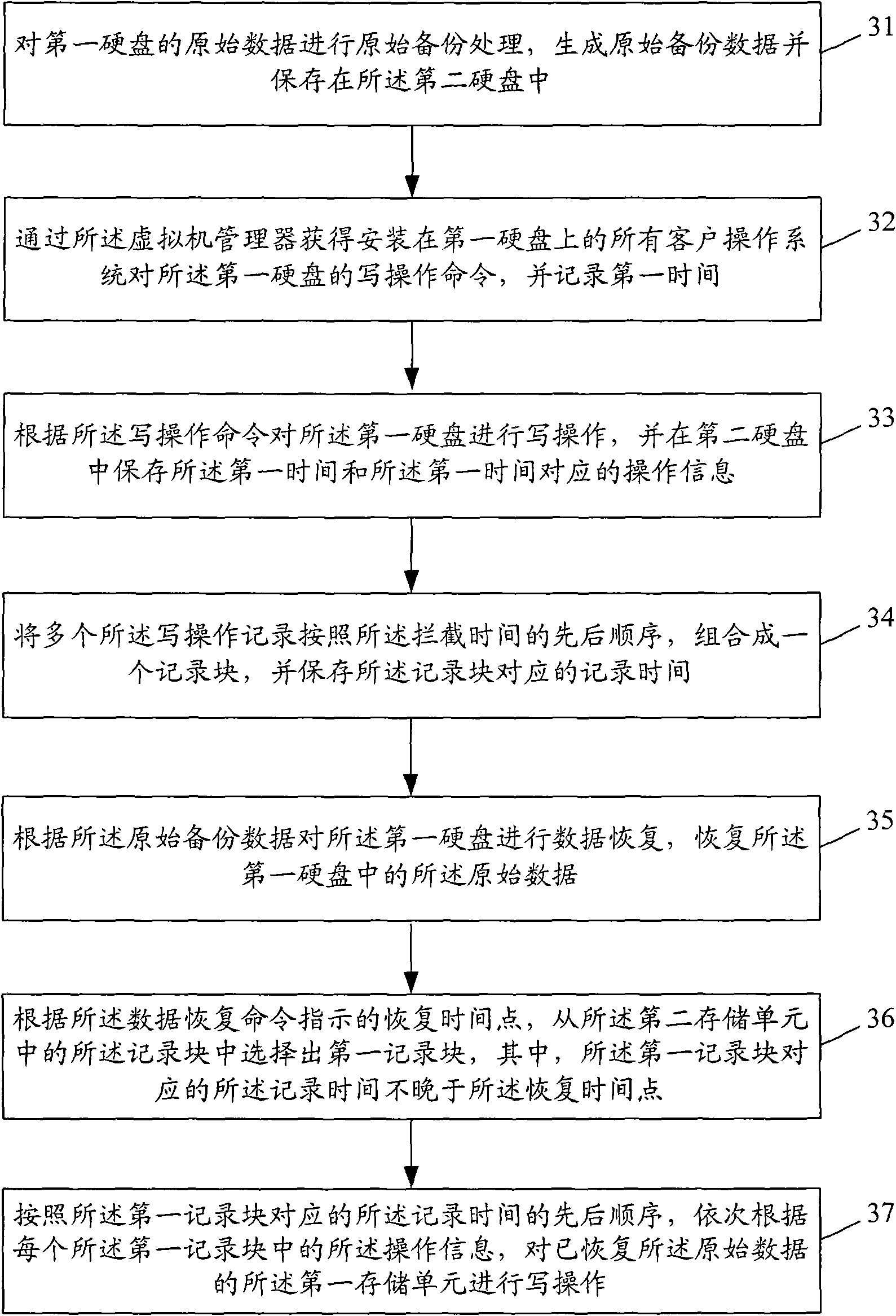

Method for carrying out back-up protection on data of storage equipment and computer system

ActiveCN101937378AEasy to manageSave storage spaceRedundant operation error correctionThird partyOperational system

The invention provides a method for carrying out back-up protection on the data of storage equipment and a computer system. The method comprises the following steps of: obtaining a write operation command of at least one client operation system for a first storage unit; recording the first time for obtaining the write operation command; carrying out write operation on the first storage unit according to the write operation command, wherein the write operation is used for writing first data at the first address of the first storage unit; and writing the operation information corresponding to the first time and the write operation command onto a second storage unit, wherein the operation information comprises the first address of the first storage unit corresponding to the write operation command and the first data corresponding to the write operation command. The method can realize continuous data back-up protection supporting the concurrency of multiple operation systems, without depending on the operation systems and third-party software.

Owner:LENOVO (BEIJING) CO LTD

Method and system for performing real-time operation

InactiveUS20040268353A1Program initiation/switchingResource allocationInformation processingBitwise operation

An information processing system performs a real-time operation including a combination of a plurality of tasks. The system includes a plurality of processors, a unit which stores structural description information and a plurality of programs describing procedures corresponding to the tasks, the structural description information indicating a relationship in input / output between the programs and including cost information concerning time required for executing each of the programs, a unit which determines an execution start timing and execution term of each of a plurality of threads for execution of the programs based on the structural description information, and a unit which performs a scheduling operation of assigning the threads to at least one of the processors according to a result of the determining.

Owner:KAISHA

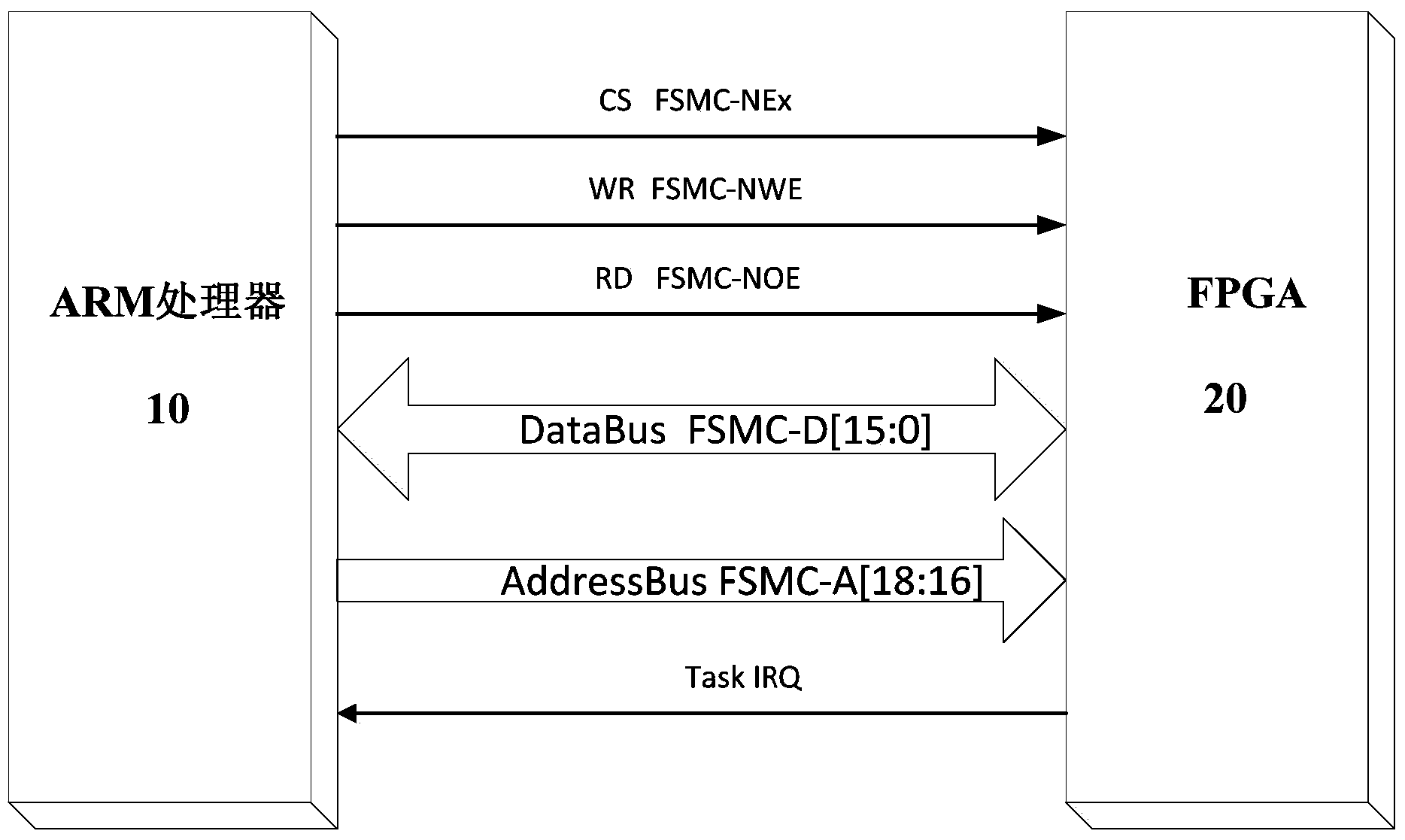

Hardware real-time operation system

InactiveCN103412755AReduce overheadEffectively provide utilizationSpecific program execution arrangementsOperational systemFuzzy sliding mode control

The invention discloses a hardware real-time operation system. The hardware real-time operation system comprises an ARM (advanced RISC machines) processor and an FPGA (field programmable gate array) which are connected via an FSMC (fuzzy sliding mode control) bus, wherein the FPGA is used for realizing a preemptive scheduler, and managements on tasks, a signal quantity, an oil tank, a message queue, a mutual exclusion signal quantity and an event flag group based on the preemptive scheduler; and the ARM processor is used for executing the tasks and realizing task switchover. By implementing the technical scheme of the invention, the FPGA does not occupy the processing time of the ARM processor because of running independently from the ARM processor, and the saved time is used for executing task programs, thus successfully reducing the system expense of the ARM processor; in particular, the utilization rate of the ARM processor is effectively increased in applications needing rapid task switchover. Therefore, via the operation system realized by hardware, the schedulability and real-time performance of the task set are improved.

Owner:SHENZHEN DONG YUAN ELECTRONICS CO LTD

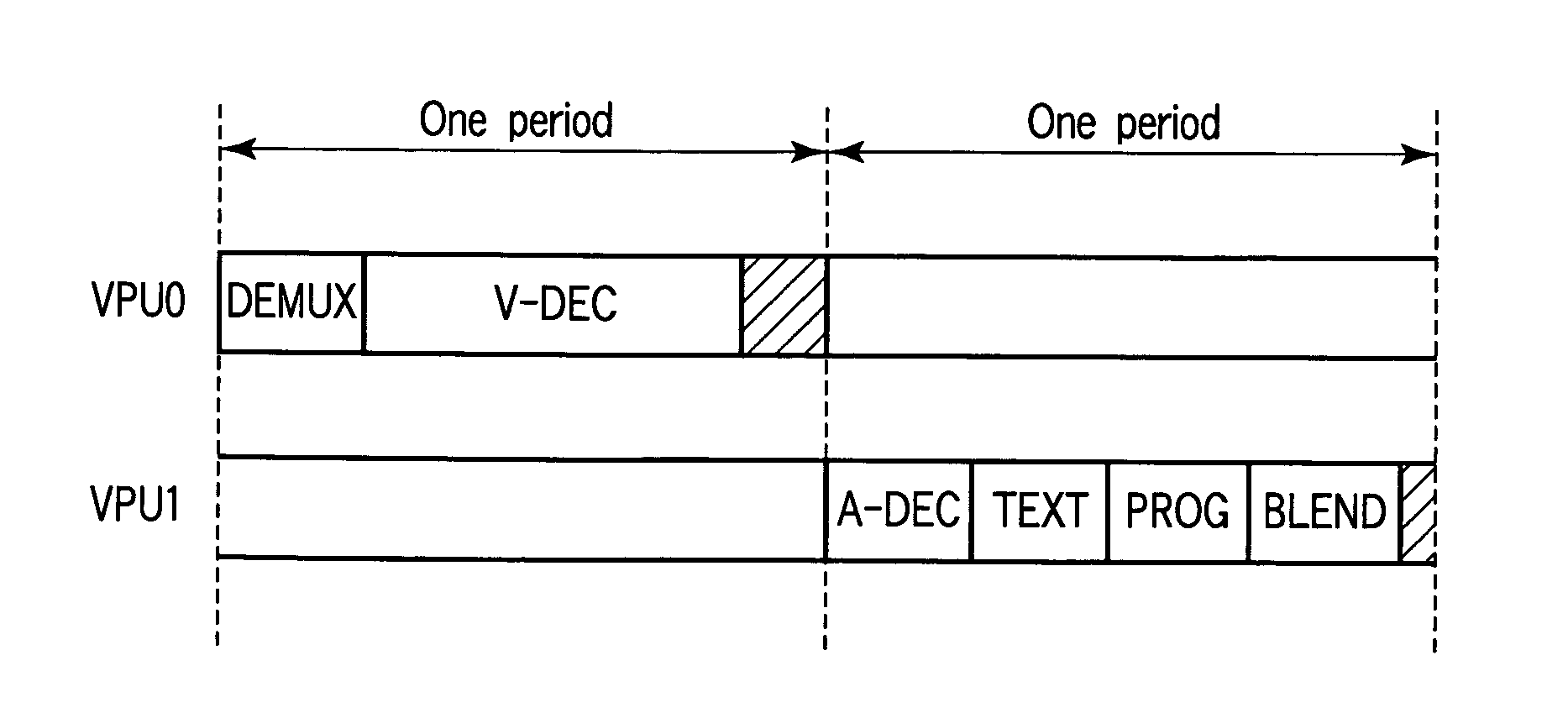

Method and system for performing real-time operation including plural chained tasks using plural processors

InactiveUS8495651B2Program initiation/switchingDigital computer detailsInformation processingBitwise operation

An information processing system periodically performs a real-time operation including a plurality of chained tasks. The system includes a plurality of processors, a unit for dividing the chained tasks into a first task group and a second task group based on a relationship in order of execution among the tasks, the second task group being executed after the first task group, and a unit for performing a scheduling operation of periodically assigning each of the first task group and the second task group to at least one of the processors to periodically execute the first task group at regular time intervals and periodically execute the second task group at the regular time intervals with a one-period delay relative to the first task group.

Owner:KK TOSHIBA

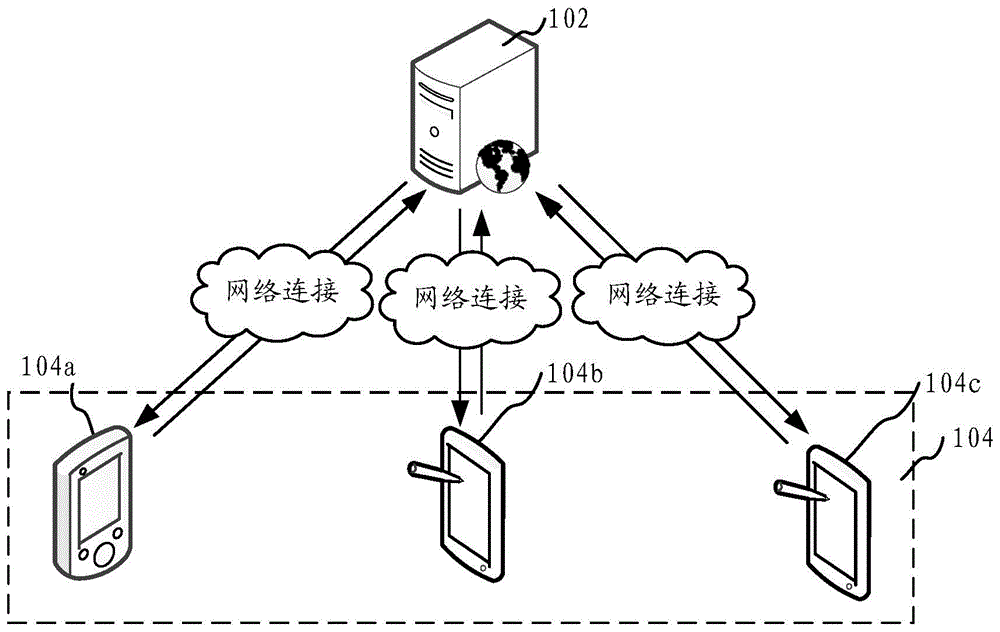

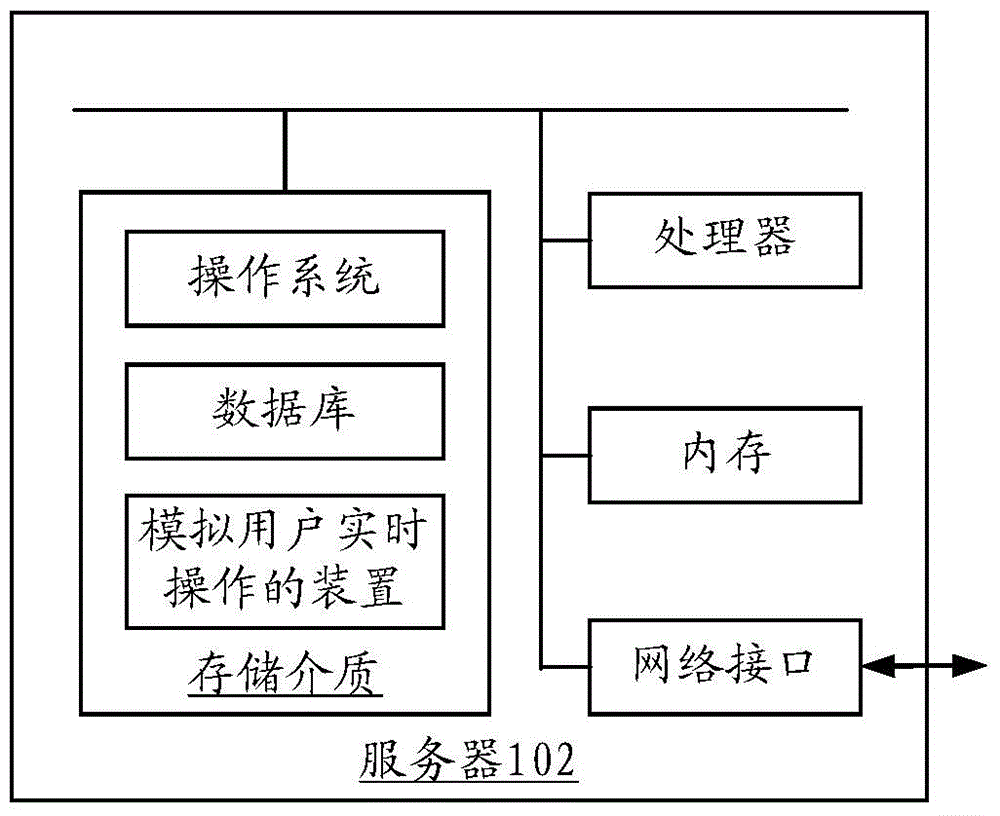

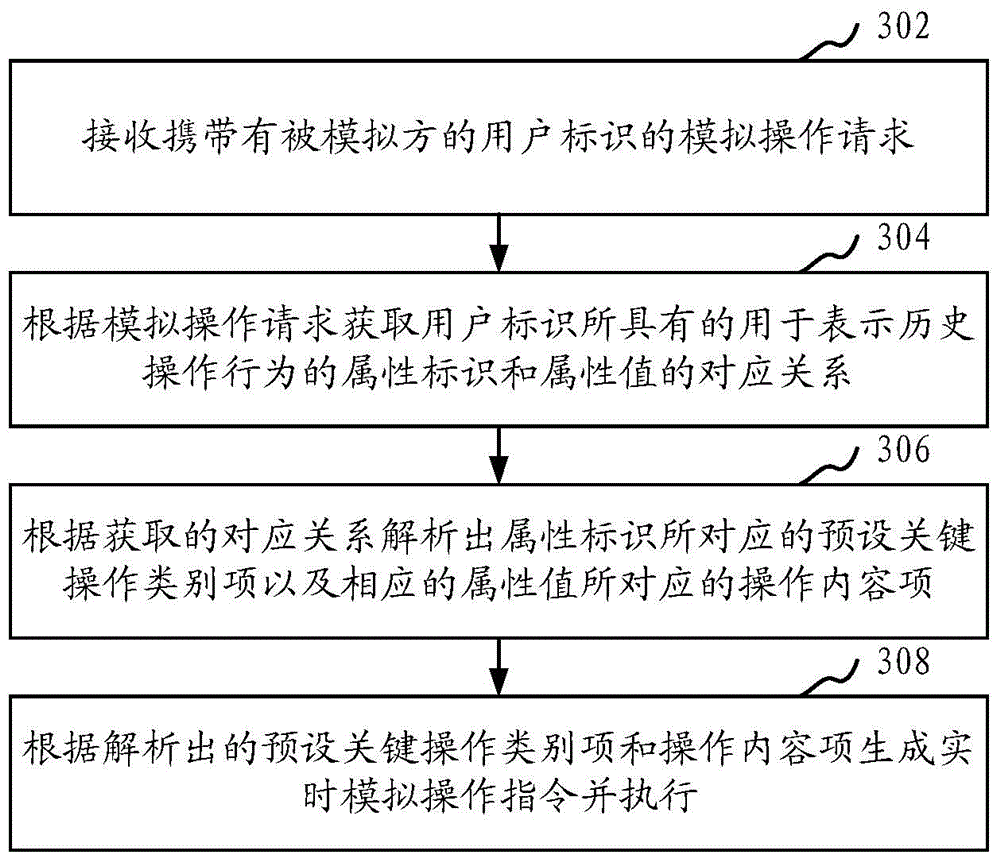

Method and apparatus for simulating user real-time operation

ActiveCN104965695AHigh degree of artificial intelligenceSpecific program execution arrangementsSpecial data processing applicationsReal-time simulationBitwise operation

The invention provides a method and apparatus for simulating user real-time operation. The method comprises following steps: receiving simulation operation requests carrying user identification of a simulated user; acquiring corresponding relations of attribute identification and attribute values according to the simulation operation requests, wherein the attribute identification and the attribute values belong to the user identification and are used for representing history operation behaviors; working out preset key operation items corresponding to the attribute identification and operation content items corresponding to the attribute values according to the acquired corresponding relations; and generating real-time simulation operation commands and executing the commands according to the acquired preset key operation items and the operation content items. By employing the method for simulating user real-time operation, real-time operation commands which ought to be triggered by the simulated user can be accurately simulated, the artificial intelligence degree is high, and the real user can be better substituted for real-time operation.

Owner:SHENZHEN TENCENT COMP SYST CO LTD

System and console for monitoring and managing well site operations

ActiveUS20140299378A1Reduces potential inaccuracyReduce delaysSurveyConstructionsGraphicsGraphical user interface

A well advisor system for monitoring and managing well drilling and production operations. The system may be accessed through one or more workstations, or other computing devices, which may be located at a well site or remotely. The system is in communication with and receives input from various sensors. It collects real-time sensor data sampled during operations at the well site, which may include drilling operations, running casing or tubular goods, completion operations, or the like. The system processes the data, and provides nearly instantaneous numerical and visual feedback through a variety of graphical user interfaces (“GUIs”), which are presented in the form of operation-specific consoles. The visual feedback includes a geometric performance metric display of the current status of selected parameters based upon established threshold values

Owner:ABBASSIAN FEREIDOUN +14

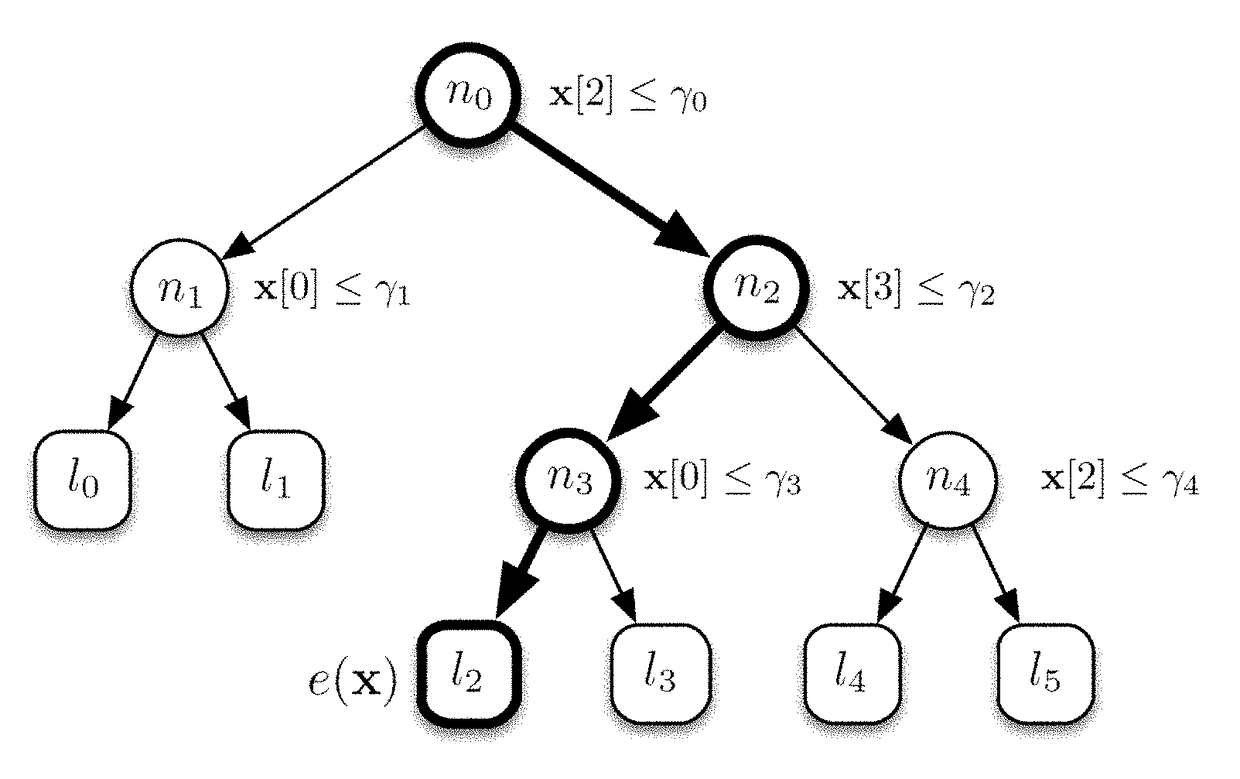

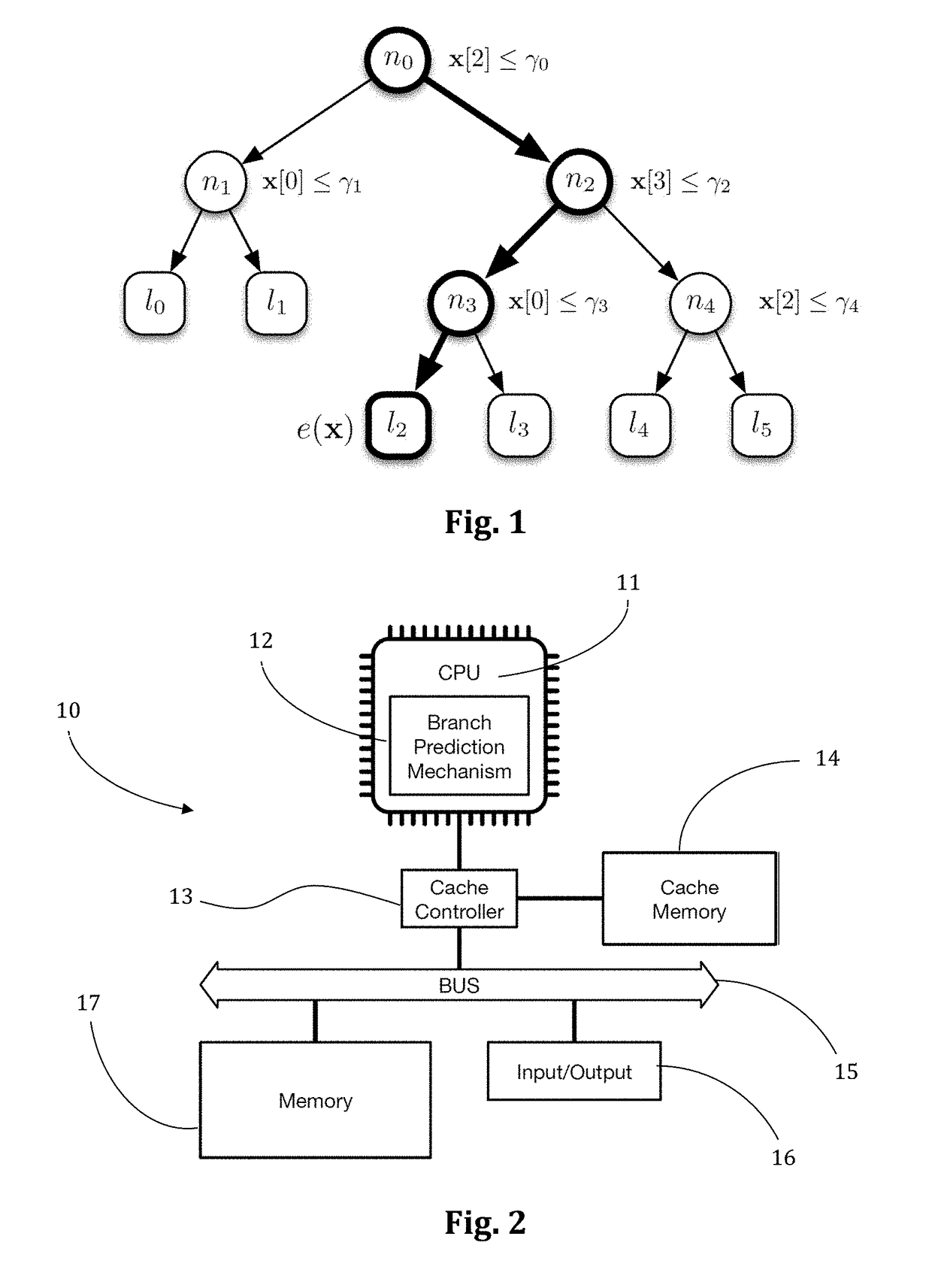

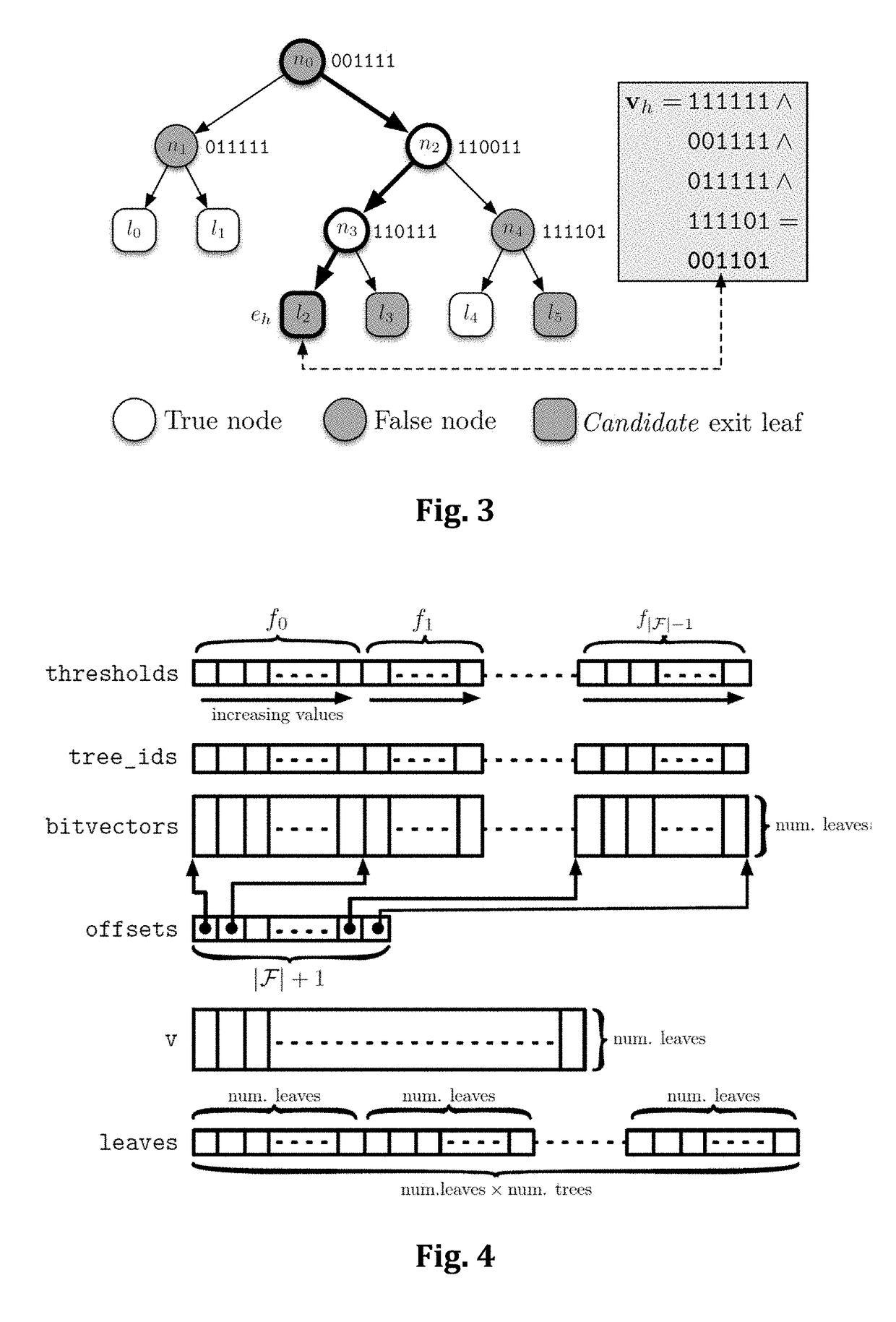

A method to rank documents by a computer, using additive ensembles of regression trees and cache optimisation, and search engine using such a method

ActiveUS20180217991A1Reduce scoring timeImprove recallEnsemble learningInference methodsDocumentation procedureData set

The present invention concerns a novel method to efficiently score documents (texts, images, audios, videos, and any other information file) by using a machine-learned ranking function modeled by an additive ensemble of regression trees. A main contribution is a new representation of the tree ensemble based on bitvectors, where the tree traversal, aimed to detect the leaves that contribute to the final scoring of a document, is performed through efficient logical bitwise operations. In addition, the traversal is not performed one tree after another, as one would expect, but it is interleaved, feature by feature, over the whole tree ensemble. Tests conducted on publicly available LtR datasets confirm unprecedented speedups (up to 6.5×) over the best state-of-the-art methods.

Owner:TISCALI SPA

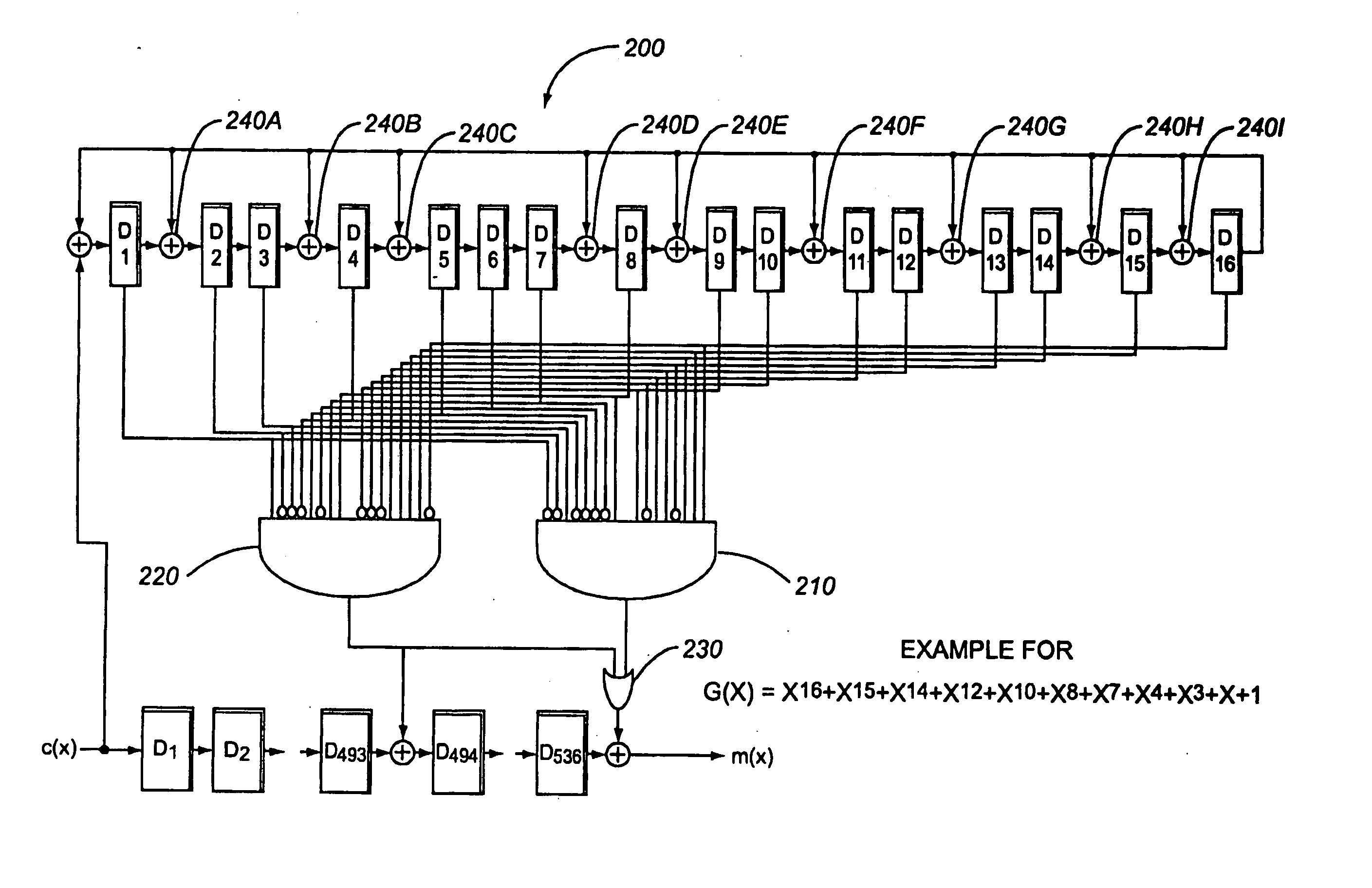

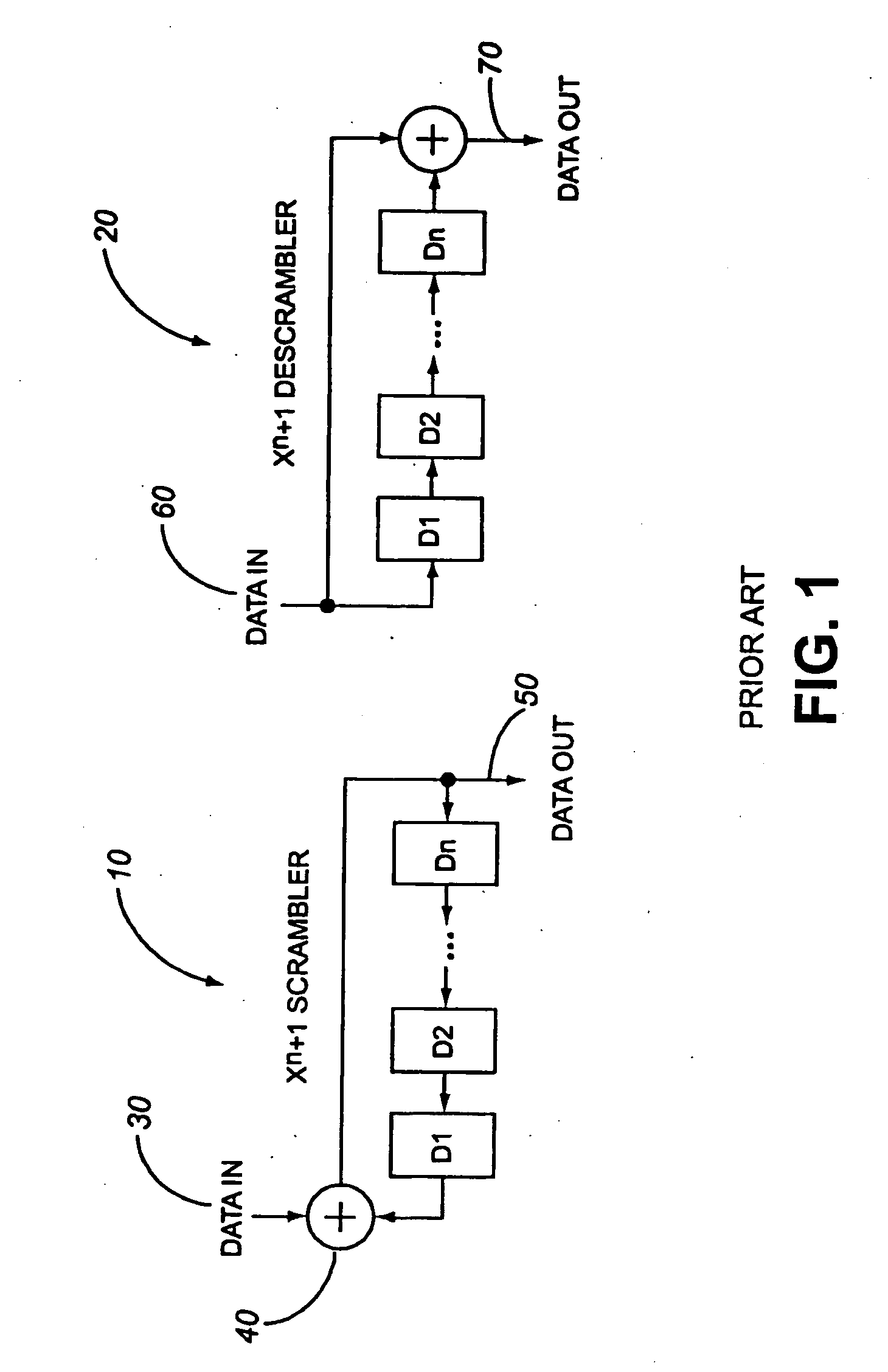

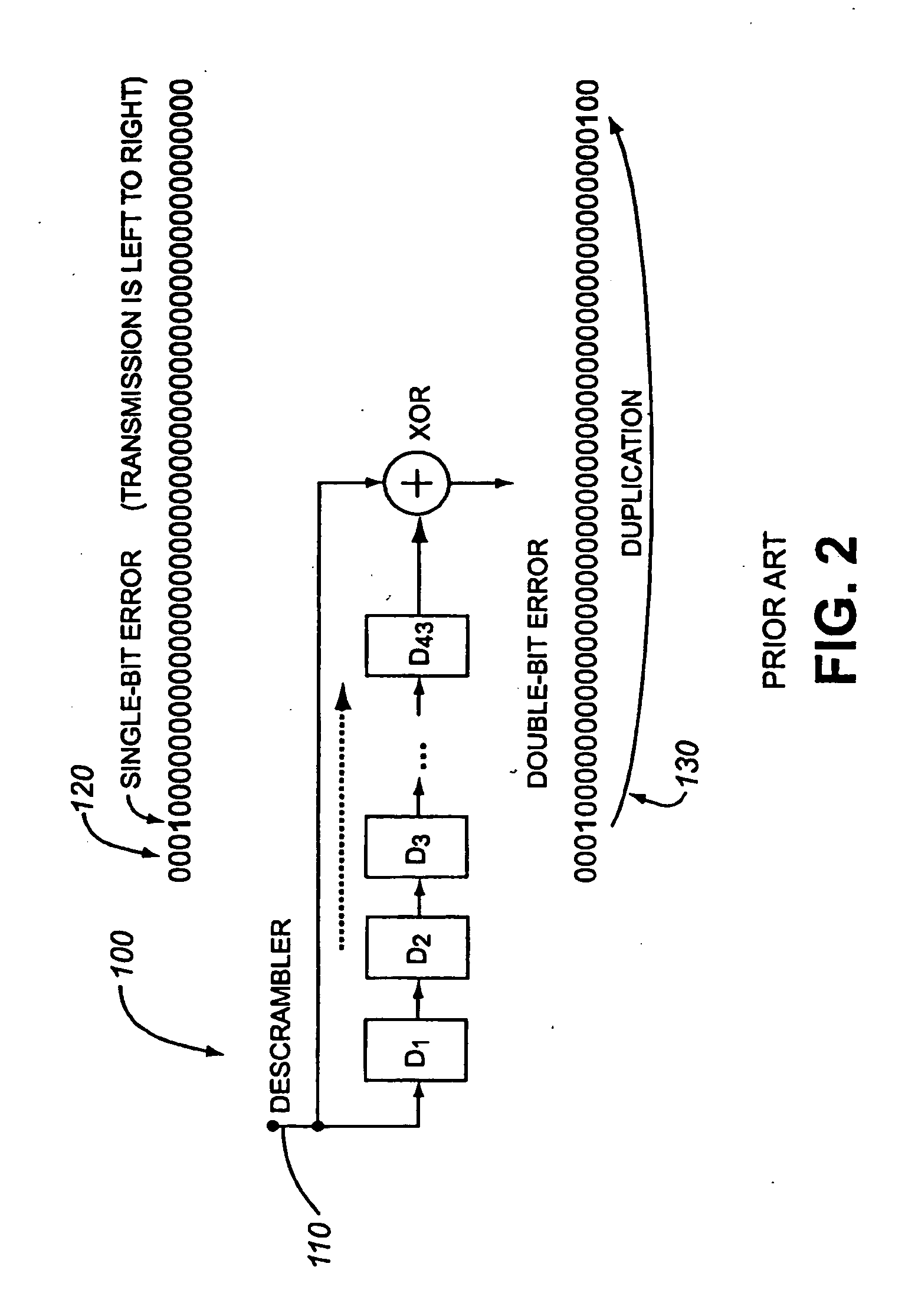

Cyclic redundancy check circuit for use with self-synchronous scramblers

The present invention provides a circuit for detecting and correcting errors in a bit stream. The circuit consists of a plurality of circuit elements, a least one operation circuit means, and at least two logic gates. The logic gates receive inputs from the plurality of circuit elements. The plurality of circuit elements are coupled to receive and store a portion of a bit stream. The operation circuit elements perform bitwise operations on the contents of at least two of the circuit elements. The bitwise operations are dictated by a cyclical redundancy check (CRC) polynomial and are used to perform the CRC error detection division operation. At the end of the division process for the data to be checked, each circuit element corresponds to a bit in a bit error pattern syndrome and the logic gates determine if the contents of the circuit elements match specific bit error patterns. The circuit causes the state of at least one bit in the bit stream to change if the contents of the plurality of circuit elements match one of the specific bit patterns. The circuit is advantageous in that it may detect single bit errors, and double bit errors that may be caused by error duplication characteristic of a scrambler.

Owner:MICROSEMI STORAGE SOLUTIONS