A data communication synchronization method based on a shared memory

A shared memory and data communication technology, applied in memory systems, electrical digital data processing, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Below in conjunction with accompanying drawing, the present invention will be further described.

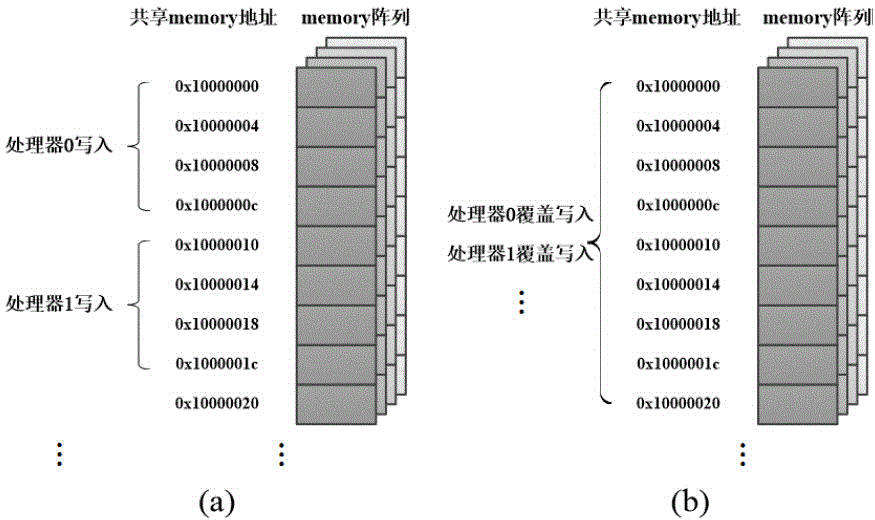

[0024] The invention is based on the realization of a parallel GPDT algorithm on a multi-core SOC. First, each data block that needs to be shared is allocated an address space in the shared memory. For the communication process of the result splicing, the shared address space is divided according to the workload assigned to each processor, so that each processor and the divided Each processor only needs to write the data blocks calculated by the core into the corresponding address space of the core; for the communication process of result accumulation, there is no need to divide the address space, and each processor from The same starting address starts overwriting, such as figure 1 shown.

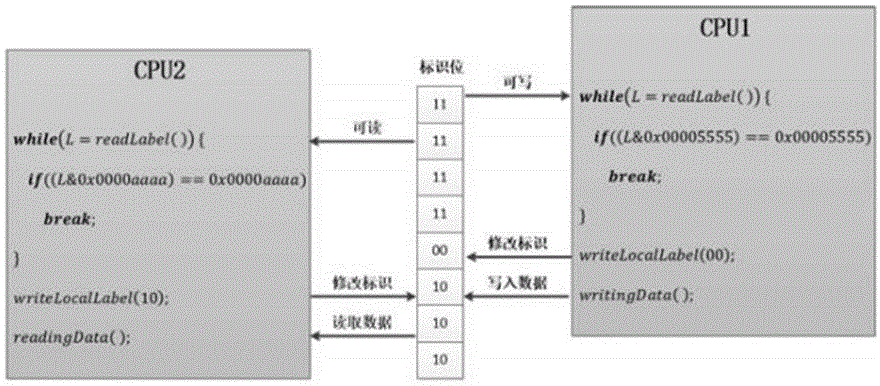

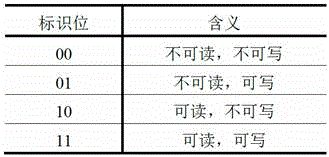

[0025] Design a 2-bit identification bit for the shared data block corresponding to each processor to indicate whether the data block is readable and writable for other processors. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More