Implementation method of chip of PVLAN in stacked mode

An implementation method and chip technology, applied in the direction of data exchange, digital transmission system, electrical components, etc. through path configuration, to achieve the effect of reducing the use cost, flexible and efficient application, and reducing the number of devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

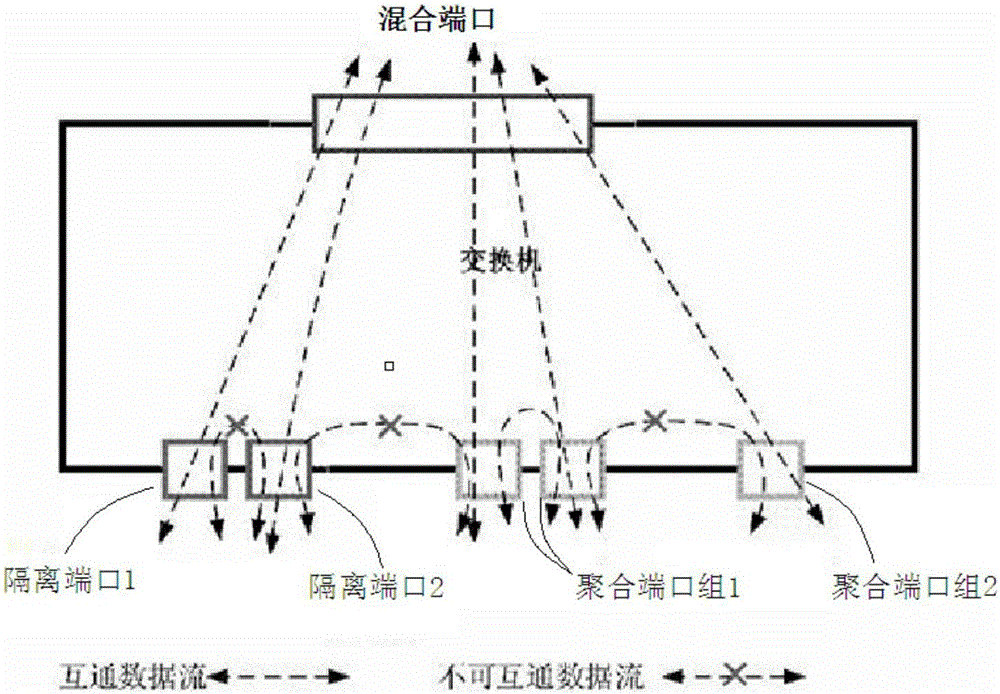

[0088] The difference between Embodiment 2 and Embodiment 1 is that the outbound port VLAN filtering rules are configured globally, that is, each chip participating in the stack has VLAN filtering rules in the outbound direction of the ports of all the chips participating in the stacking. In this way, the ingress chip can perform the VLAN filtering rule check in the outbound direction of the port to know whether to discard the packet. If it is discarded, the ingress chip will perform the discarding action instead of the destination and egress chip to perform discarding, which can reduce aggregation (stacking) Port bandwidth pressure.

[0089] The configuration of port VLAN allocation and VLAN filtering rules in this solution is the same as that in the above-mentioned embodiment 1, and the processing of the message is also carried out correspondingly according to the VLAN filtering rules. The specific configuration content is described above, and will not be repeated here. .

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More