Accurate, fast and low-input fpga delay estimation method

A delay estimation and fast technology, applied in computing, instrumentation, biological neural network model, etc., can solve problems such as neural network dependence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

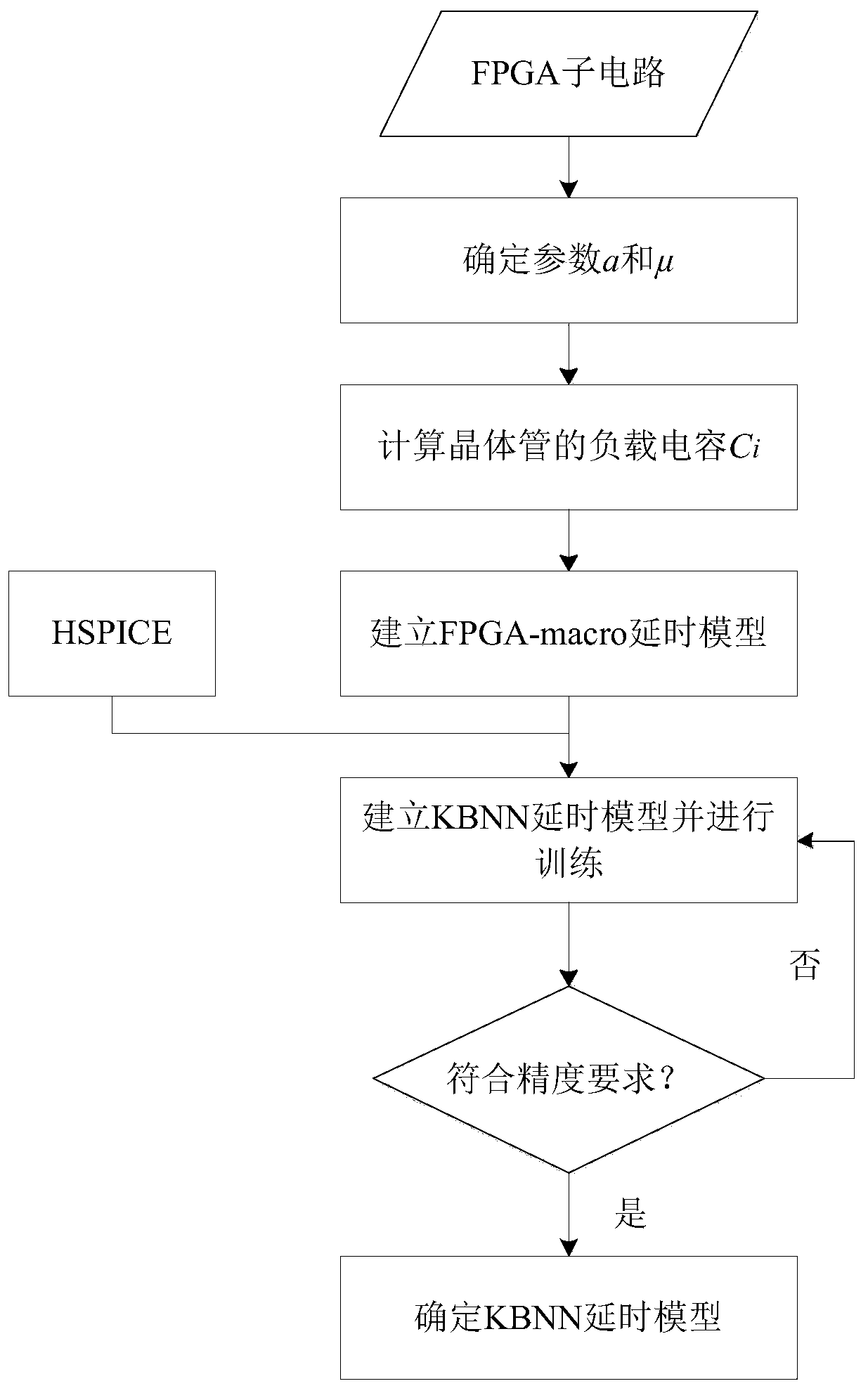

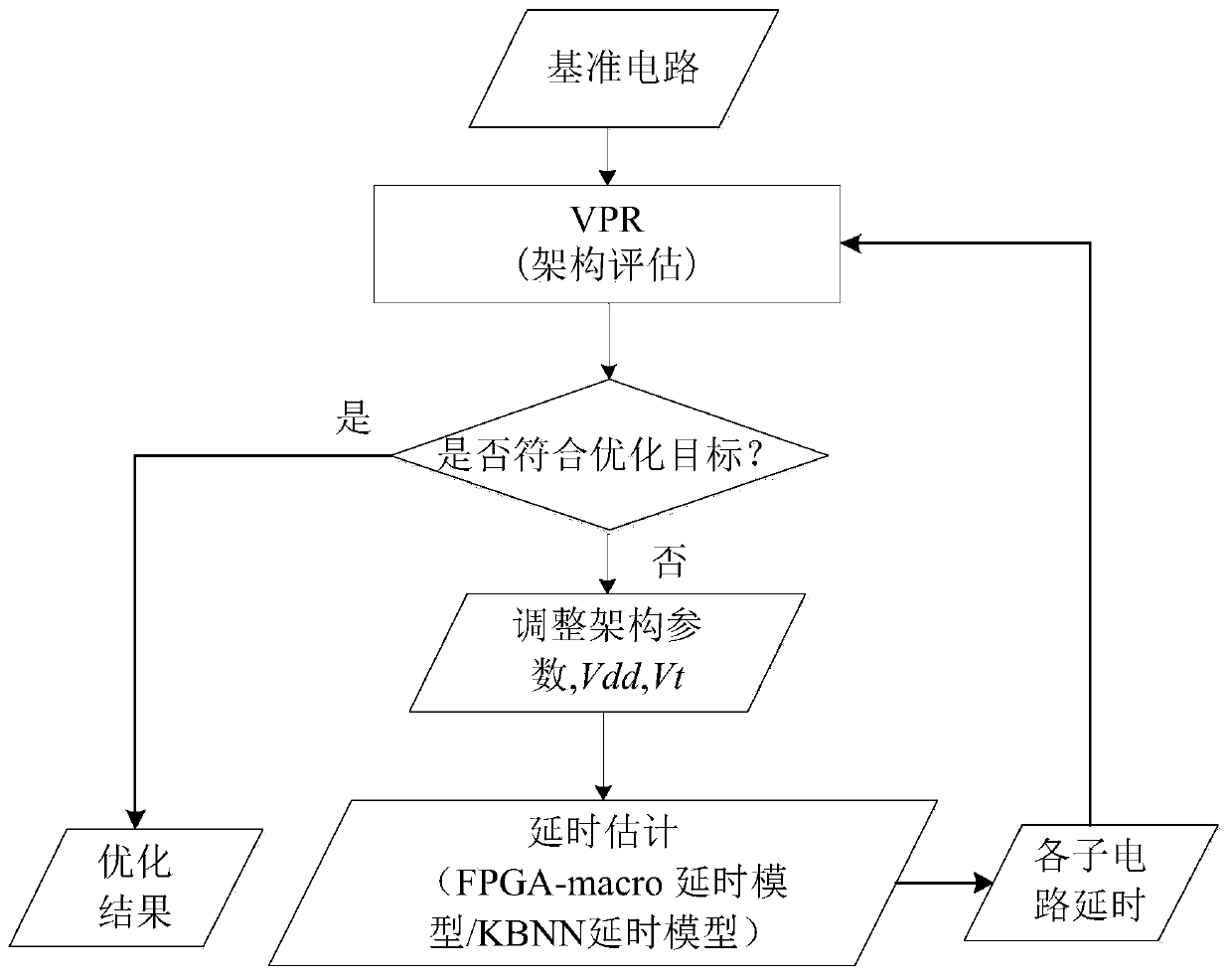

[0061] The invention provides an FPGA circuit delay estimation method based on a neural network that integrates architecture-level and transistor-level parameters, which can be combined with an architecture exploration process to speed up architecture exploration while ensuring accuracy. The specific technical solutions are as follows:

[0062] 1) Determine the fitting parameter ɑ and the effective mobility μ.

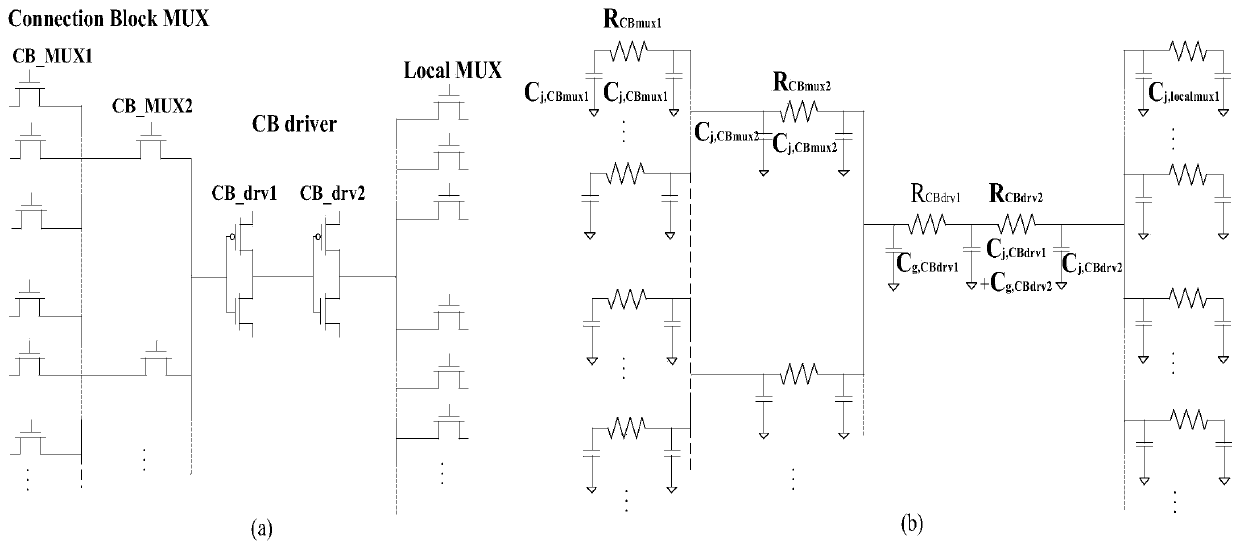

[0063] 2) Equivalent each sub-circuit in the FPGA to an RC model, and determine the load capacitance of each type of transistor in each sub-circuit based on the FPGA architecture parameters.

[0064] 3) According to the determined fitting parameters ɑ, effective mobility μ and load capacitance and other parameters, respectively establish a delay model for each sub-circuit in the FPGA, namely the FPGA-macro delay model.

[0065] 4) Collect training data, analyze and normalize it.

[0066] 5) Combine the FPGA-macro delay model with the neural network, establish a KBNN ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More