A bias current and power-on reset circuit for a shutdown chip

A technology of bias current and power-on reset, which is applied in the field of analog integrated circuits and circuits, can solve the problems of entering the normal working mode, the bias circuit and power-on reset circuit cannot work normally, and the chip cannot be powered on, so as to avoid downtime Logical confusion, improving reliability, and ensuring the effect of logical correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] The present invention will be further described below in conjunction with the embodiments shown in the accompanying drawings.

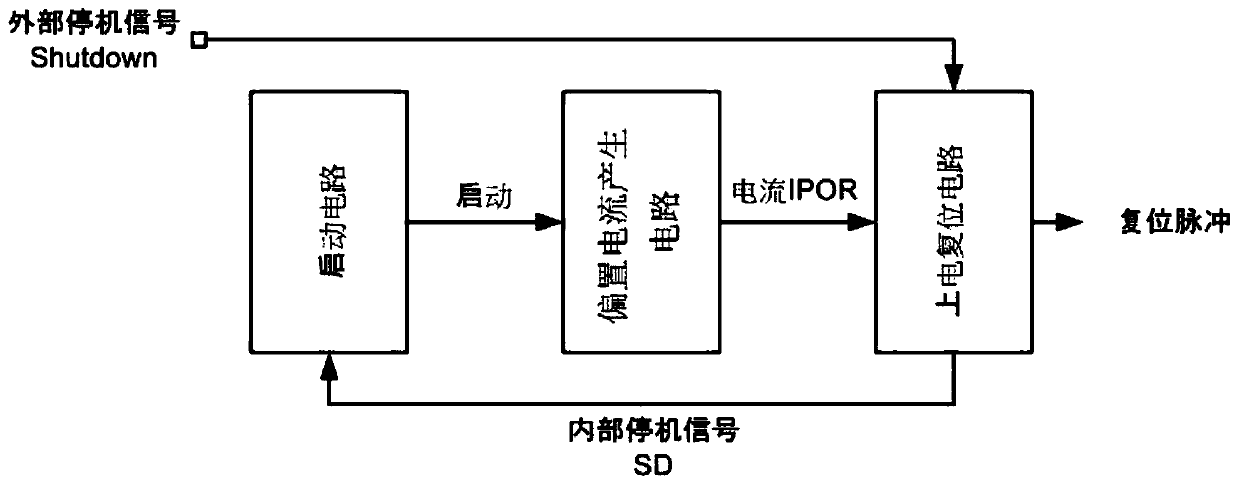

[0059] The present invention proposes a bias current and power-on reset circuit for a shutdown chip, figure 1 Shown is its structural block diagram.

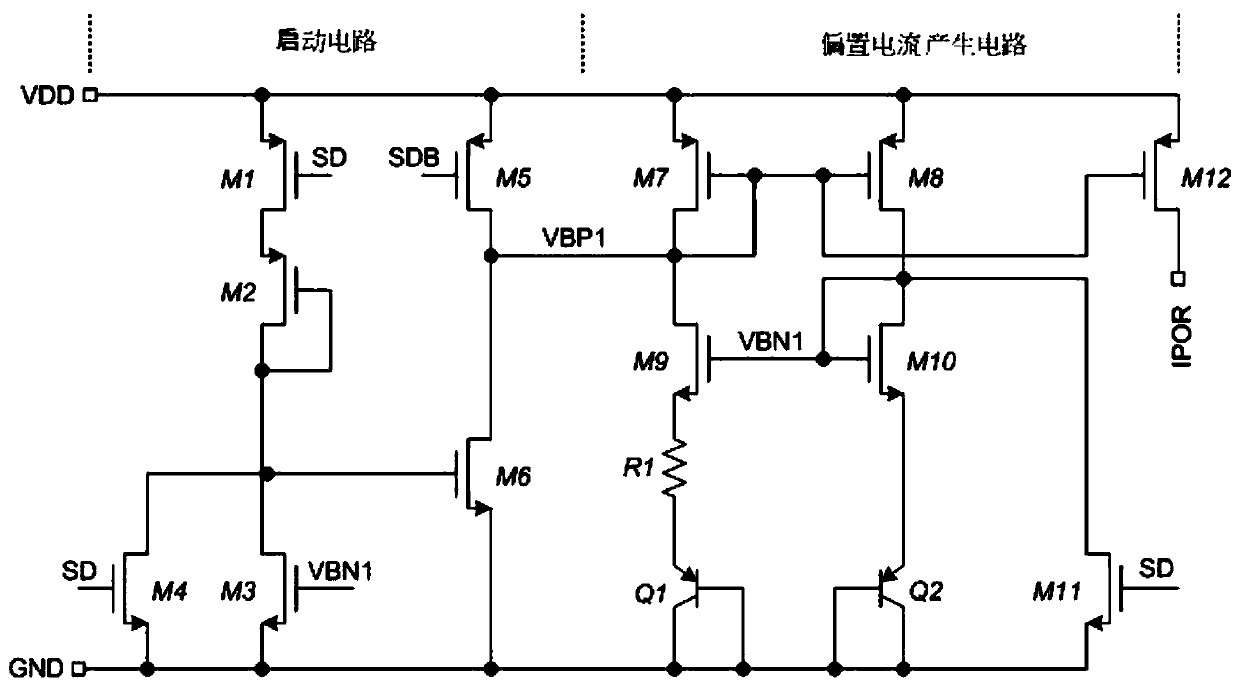

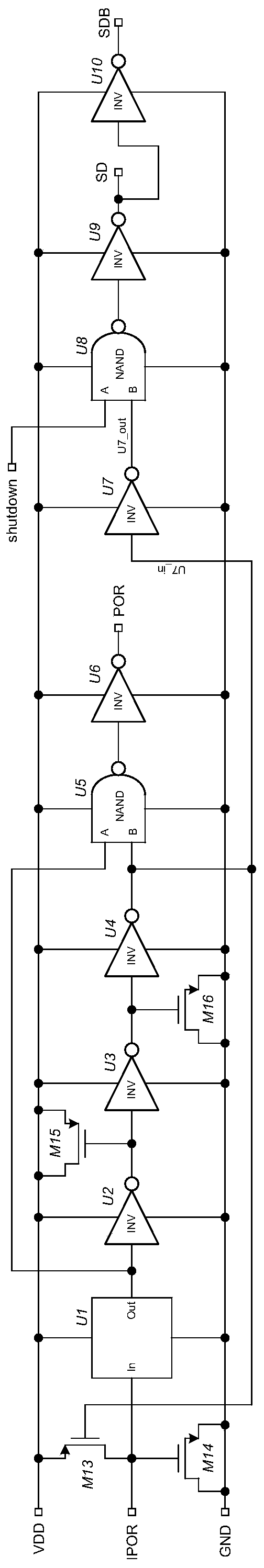

[0060] The bias current and power-on reset circuit of the shutdown chip includes a power-on reset circuit and a current bias circuit connected to each other, and the current bias circuit includes a start-up circuit and a bias current generation circuit connected to each other. Wherein: when the power-on reset circuit is powered on, the logic of the shutdown signal is guaranteed to be non-shutdown logic (0 in this embodiment), until the startup circuit charges the bias current generation circuit in the process until the shutdown chip gets rid of degeneracy bias point. The power-on reset circuit is also used to generate a power-on reset signal after power-on, and monitor the external shutdown sig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More