Cache performance evaluation method and device

An evaluation device and cache technology, applied in memory systems, instruments, electrical digital data processing, etc., can solve problems such as low accuracy and can not truly reflect the real performance of Cache, and achieve the effect of improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

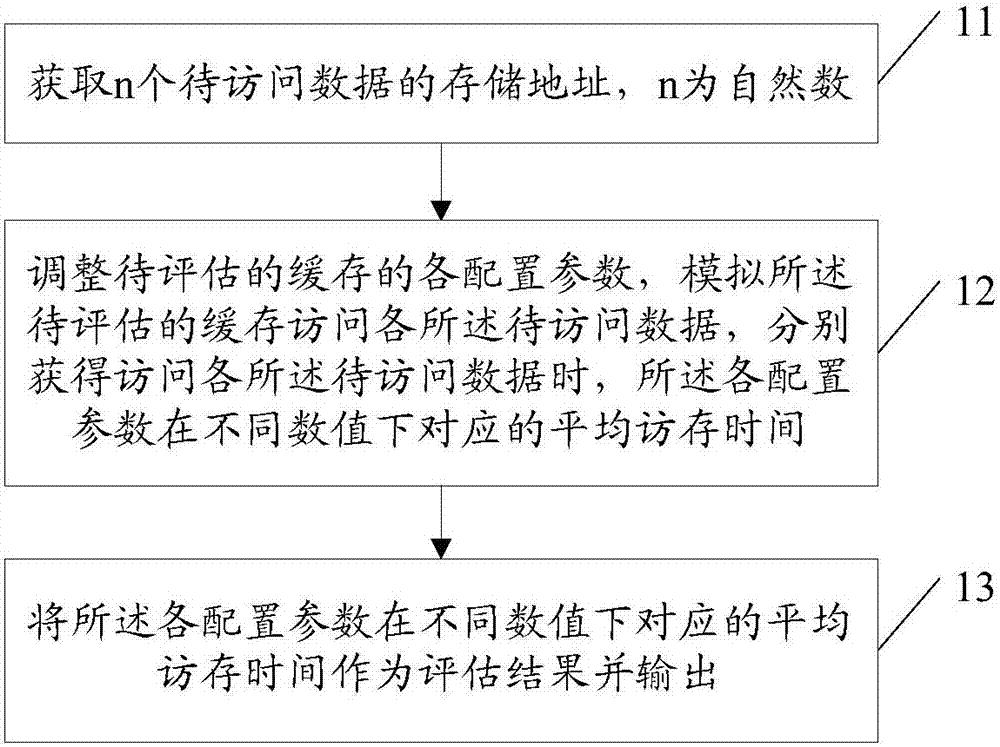

[0049] In practical applications, the application scenarios of embedded SOC are various, and the characteristics of various application scenarios are not the same. It is difficult for a specific structure of Cache to guarantee the versatility between different application scenarios. In addition, the design of embedded SOC not only needs to consider the performance of the system, but also the power consumption, area and cost of the system are also issues that designers need to consider. Therefore, in the Cache design of an embedded SOC, it is usually necessary to evaluate the impact of various structures and parameters on the final Cache acceleration effect under different application requirements.

[0050] However, when using the existing Cache performance evaluation method for Cache performance evaluation, only the Cache hit rate can be obtained according to the simulation process, and the Cache hit rate cannot reflect the real acceleration effect of the Cache, which ultimatel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More