A synchronous self-calibration method for multi-channel high-speed data reception

A high-speed data and data synchronization technology, applied in the field of signal processing, can solve the problems of complex debugging process, unfavorable product application of data acquisition system, and not widely used, and achieve the effect of ensuring accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

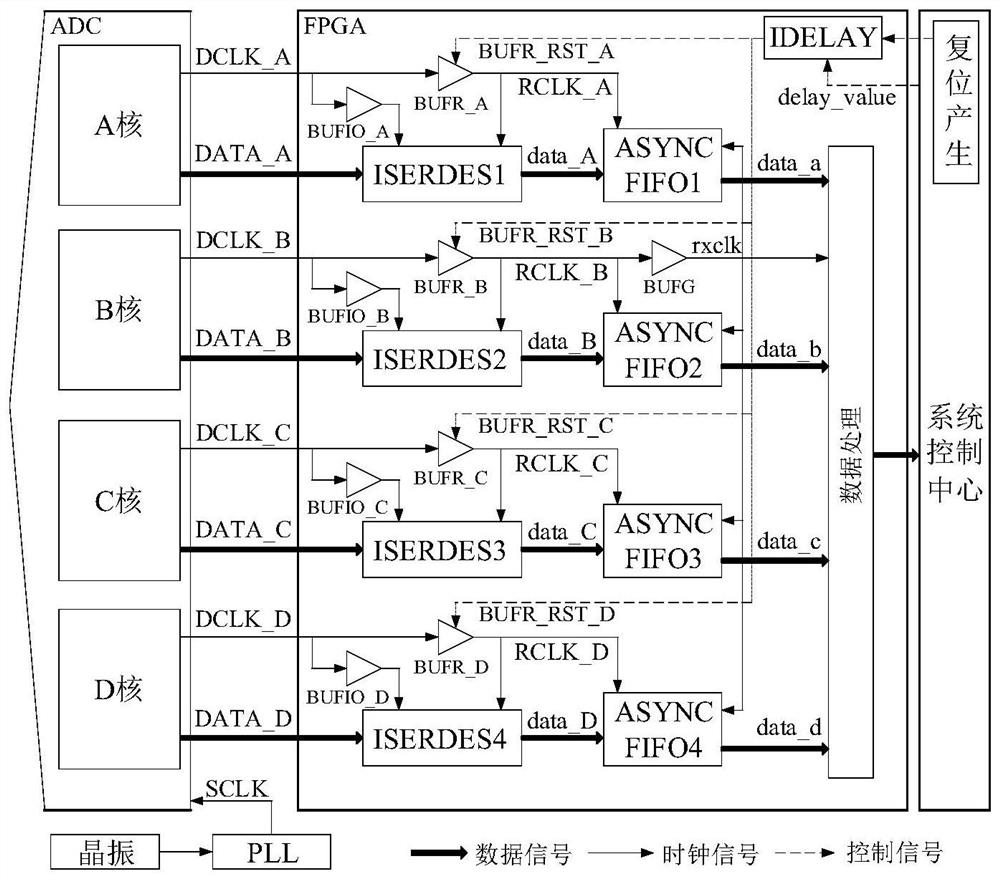

[0035] Figure 4 It is a functional block diagram of automatic correction of multi-channel high-speed data reception synchronization in the present invention.

[0036] In this example, if Figure 4 As shown, a kind of synchronous self-calibration method of multi-channel high-speed data reception of the present invention comprises the following steps:

[0037] S1. Configure the high-speed multi-core ADC chip into a test mode. In the test mode, each core of the ADC outputs a data synchronization clock signal with the same frequency and a sawtooth serial data signal that changes sequentially from 0-255, and then Input multiple data synchronous clock signals and sawtooth serial data signals to FPGA;

[0038] In this embodiment, taking EV8AQ165 as an example, the ADC chip is composed of four sub-cores with a sampling rate of 1.25GSPS, and outputs four 8-bit serial data streams DATA_A, DATA_B, DATA_C, DATA_D and four channels of data synchronization with the same frequency Clocks...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More