Memory structure

A memory and storage layer technology, applied in the semiconductor field, can solve problems such as leakage and affect memory performance, and achieve the effect of improving erasing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

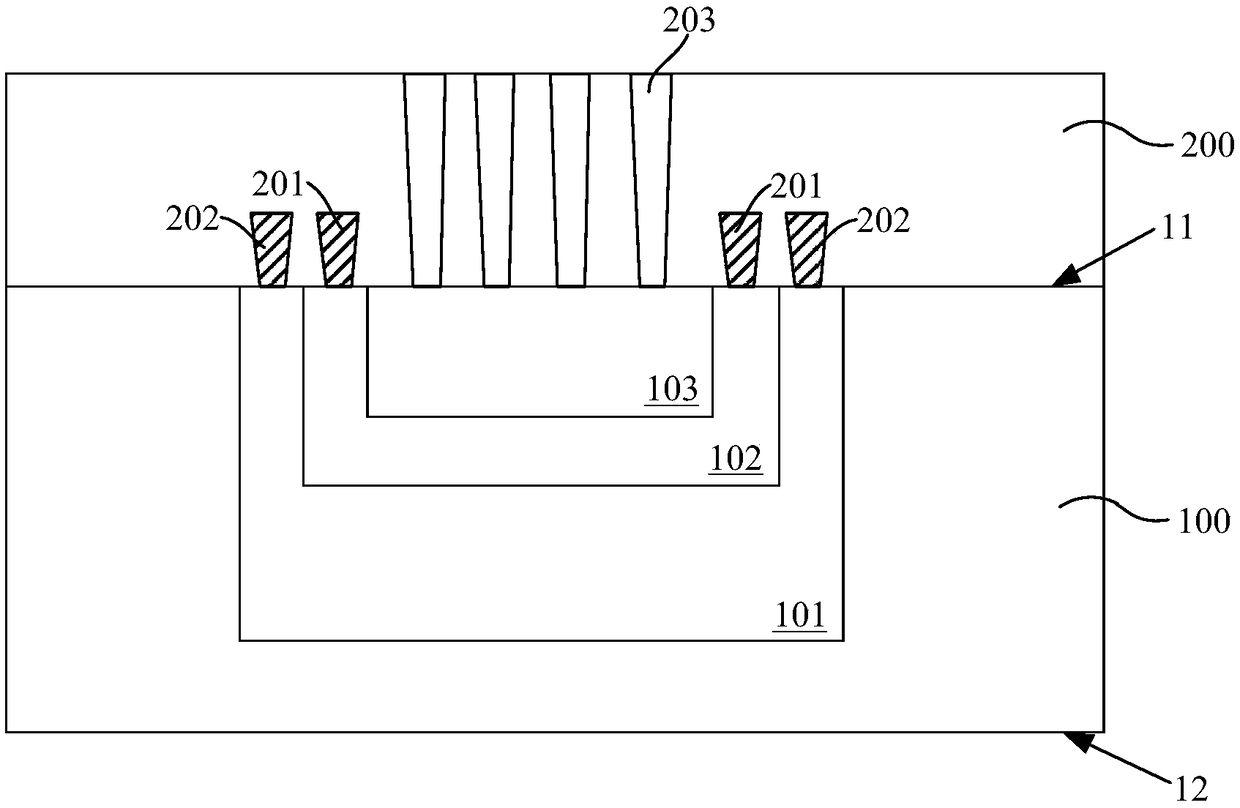

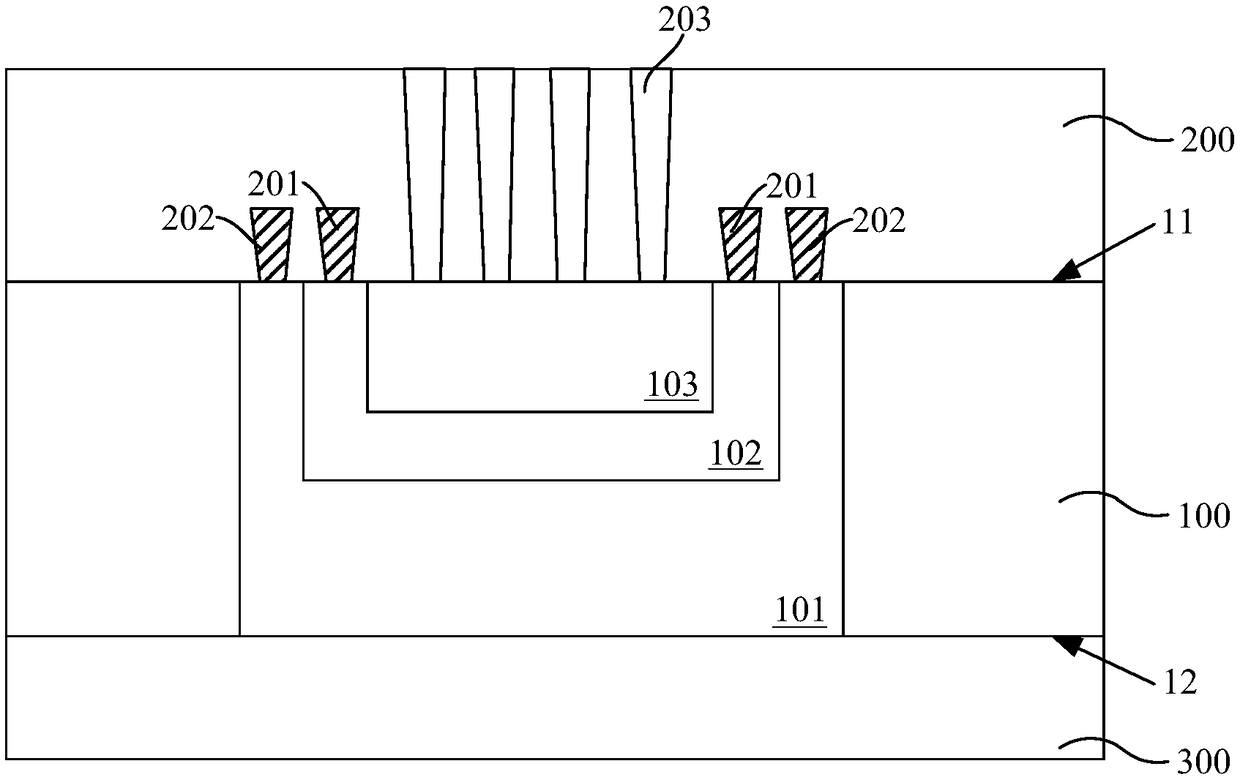

[0018] The specific implementation of the memory structure provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

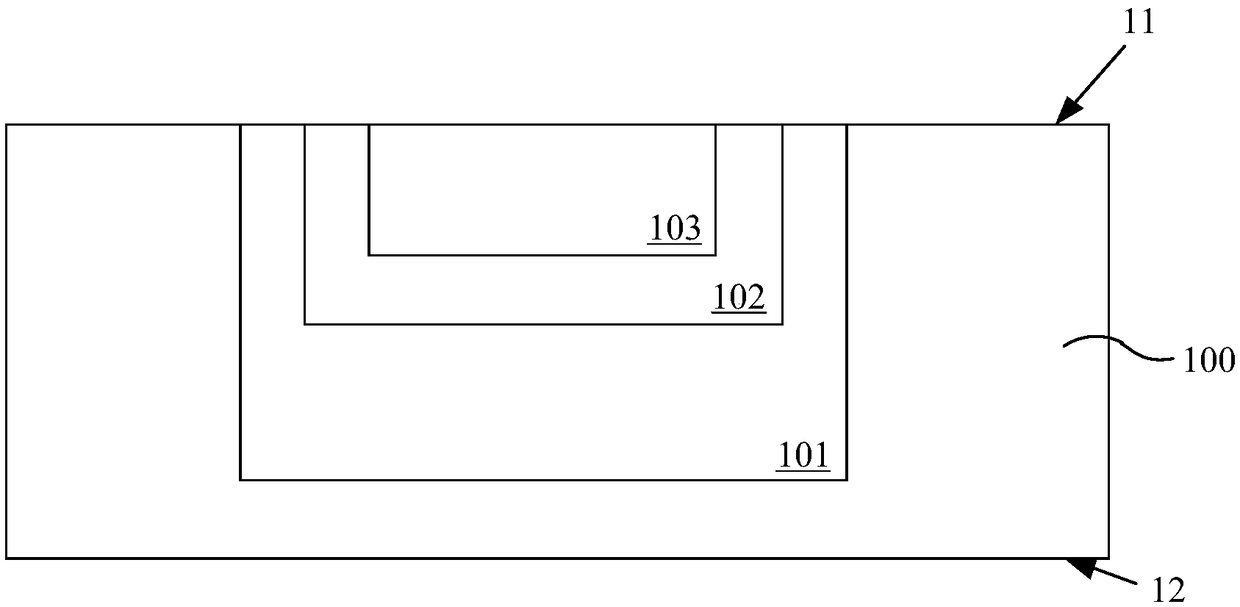

[0019] Please refer to Figure 1 to Figure 4 It is a structural schematic diagram of the formation process of the memory structure according to a specific embodiment of the present invention.

[0020] Please refer to figure 1 , providing a substrate layer 100, the substrate layer 100 has an opposite first surface 11 and a second surface 12; a conductive region is formed in the substrate layer 100, and the top of the conductive region faces the first surface of the substrate layer 100 surface 11 , the bottom of the conductive region faces the second surface 12 of the substrate layer 100 .

[0021] The substrate layer 100 is a semiconductor material layer, which may be a single crystal silicon wafer, a semiconductor epitaxial layer including a single crystal silicon wafer and the surface of the wafer, or...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More