Patents

Literature

194results about How to "Improve erase efficiency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

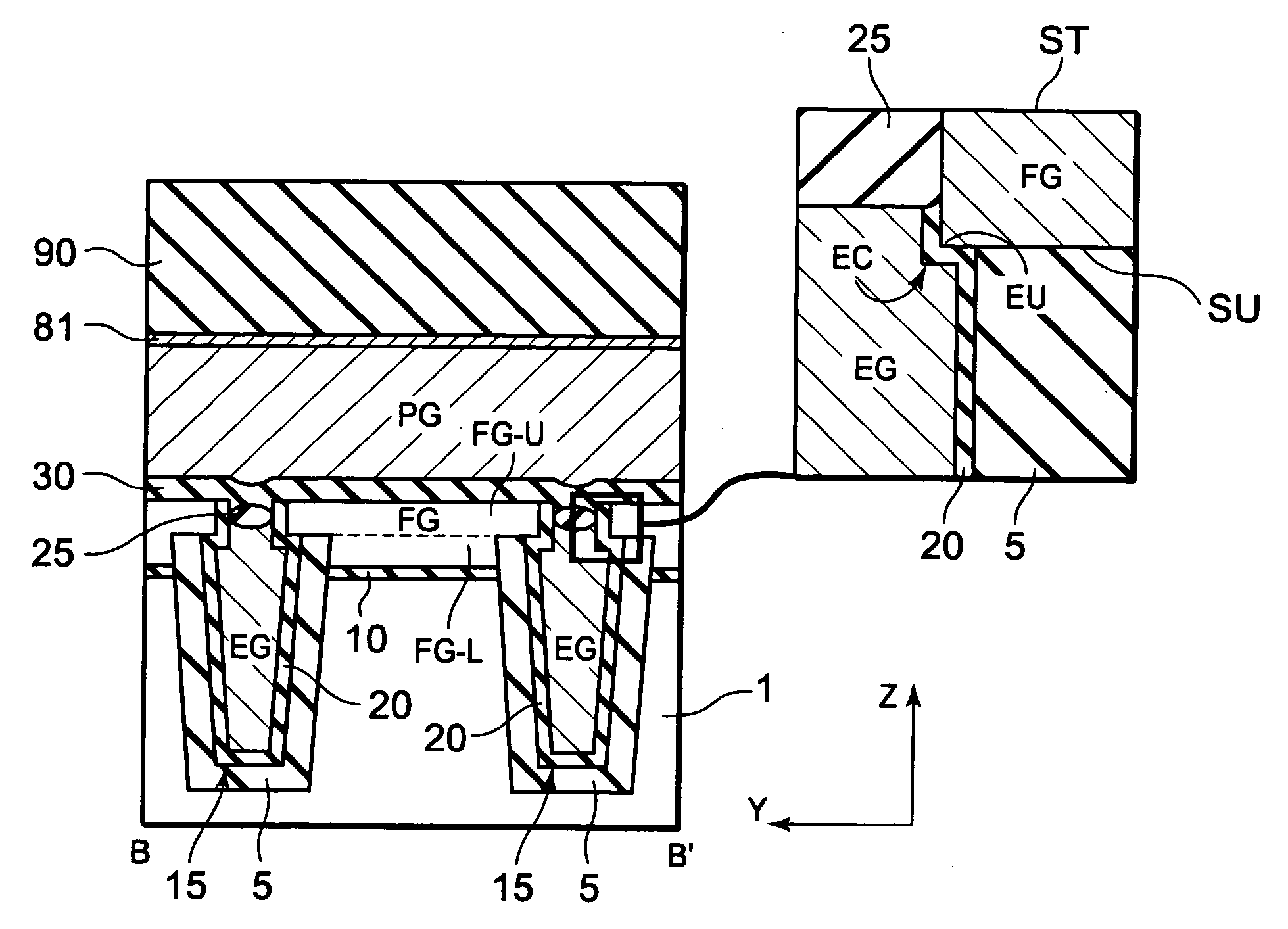

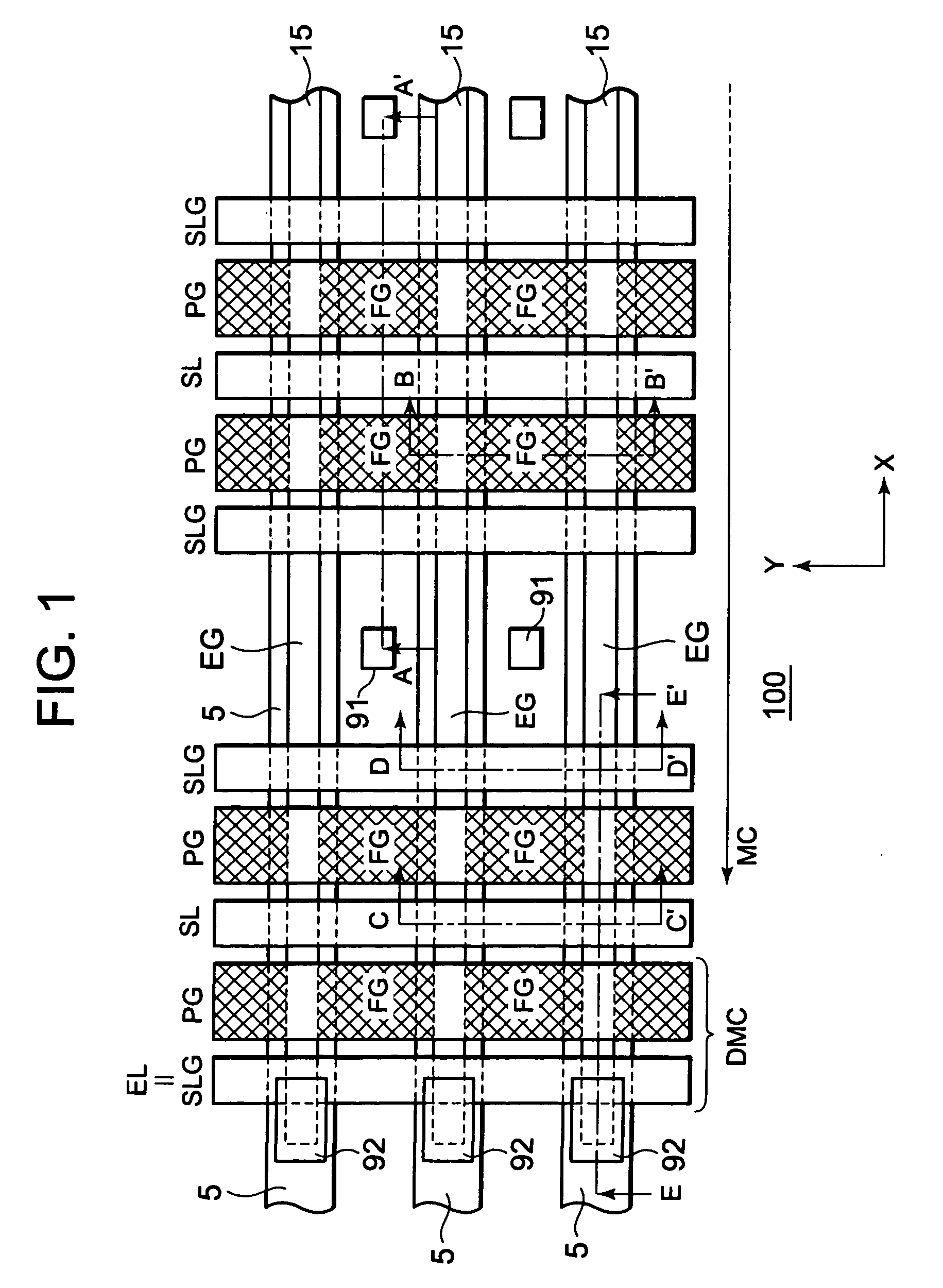

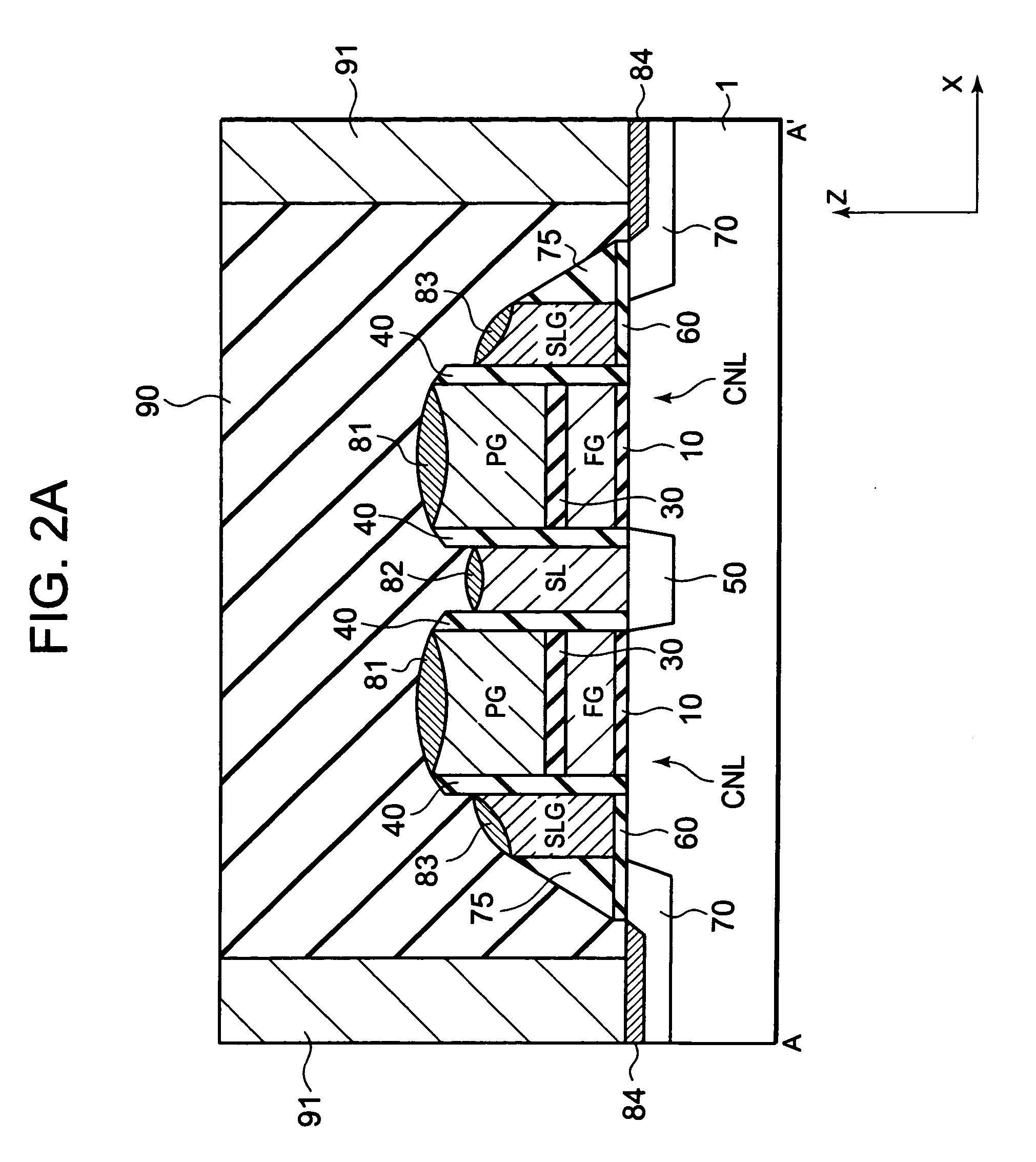

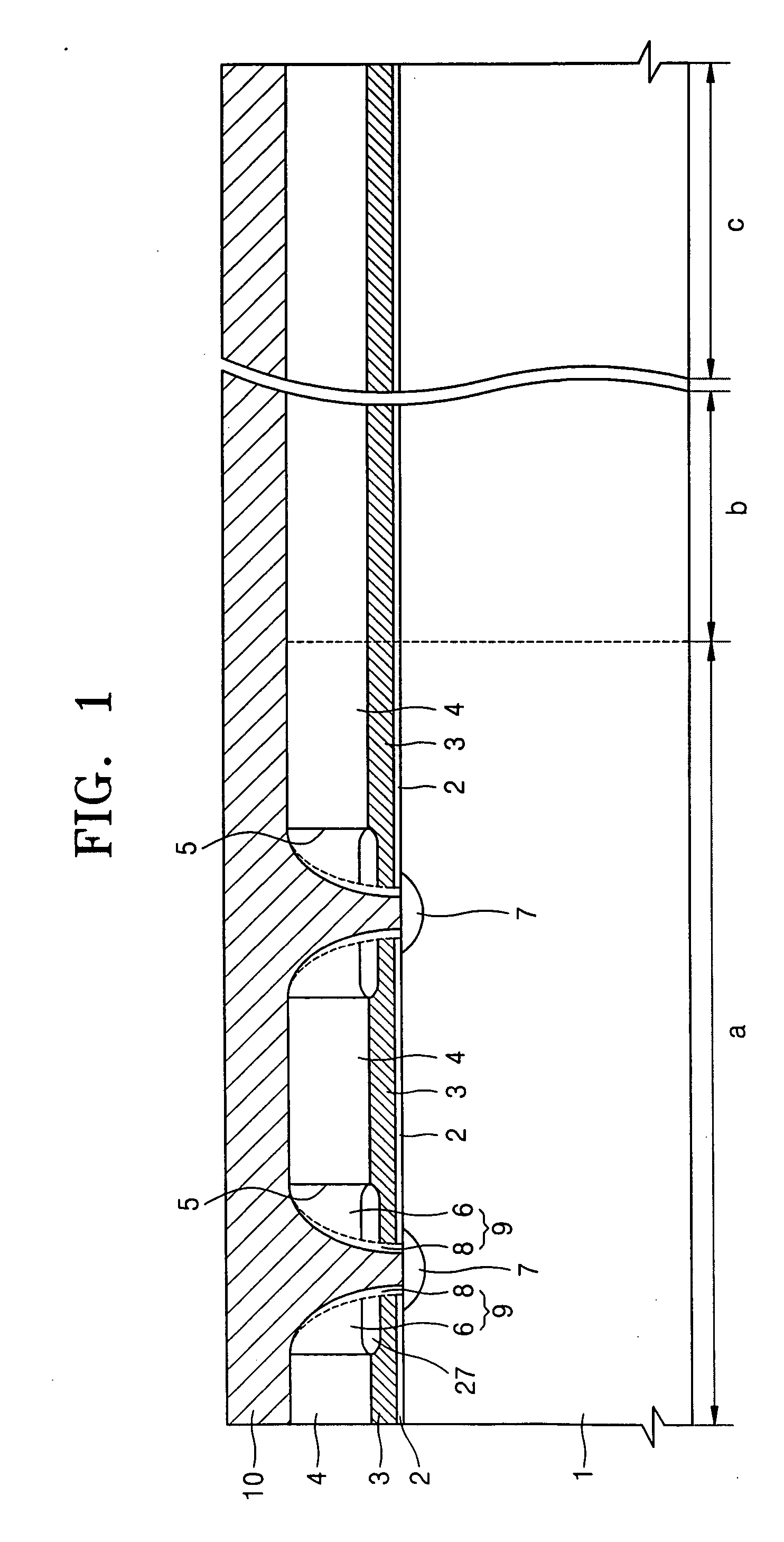

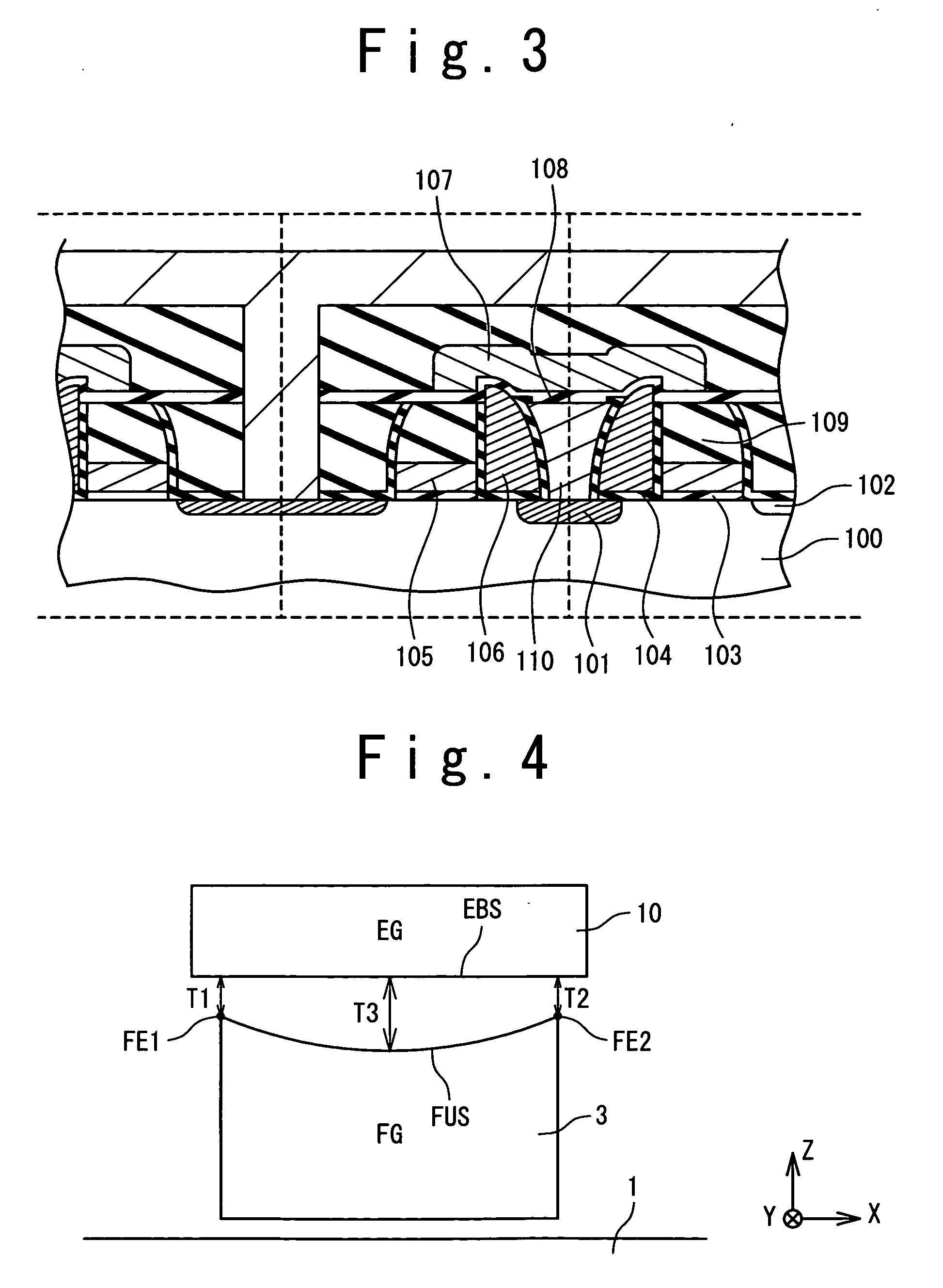

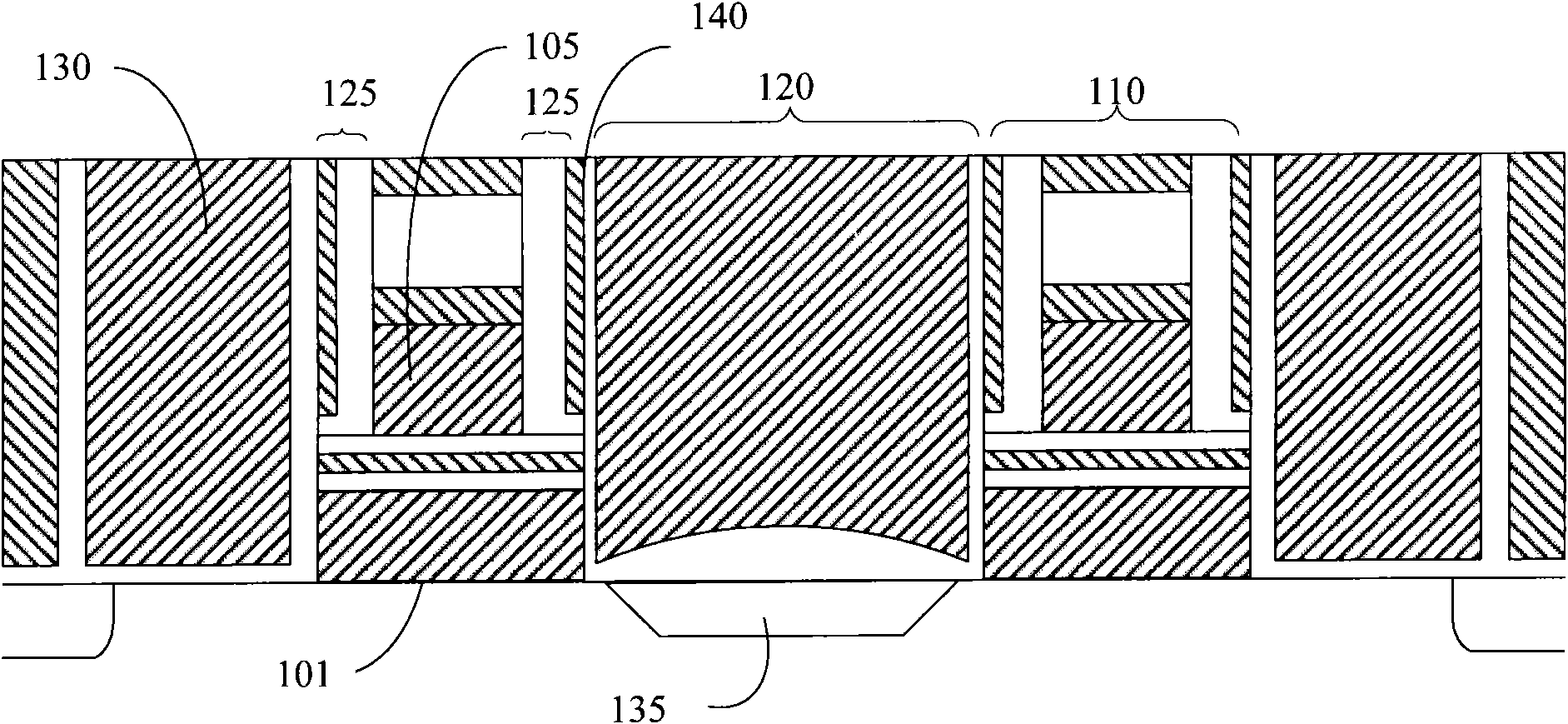

Nonvolatile semiconductor memory with erase gate and its manufacturing method

InactiveUS20090166708A1Improve erase efficiencySpeed up erasure operationSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor memory

A nonvolatile semiconductor memory device includes a semiconductor substrate, a select gate formed above the semiconductor substrate, a floating gate formed above the semiconductor substrate and an erase gate positioned lower than an upper surface of the floating gate, and opposite an edge of a lower surface of the floating gate.

Owner:RENESAS ELECTRONICS CORP

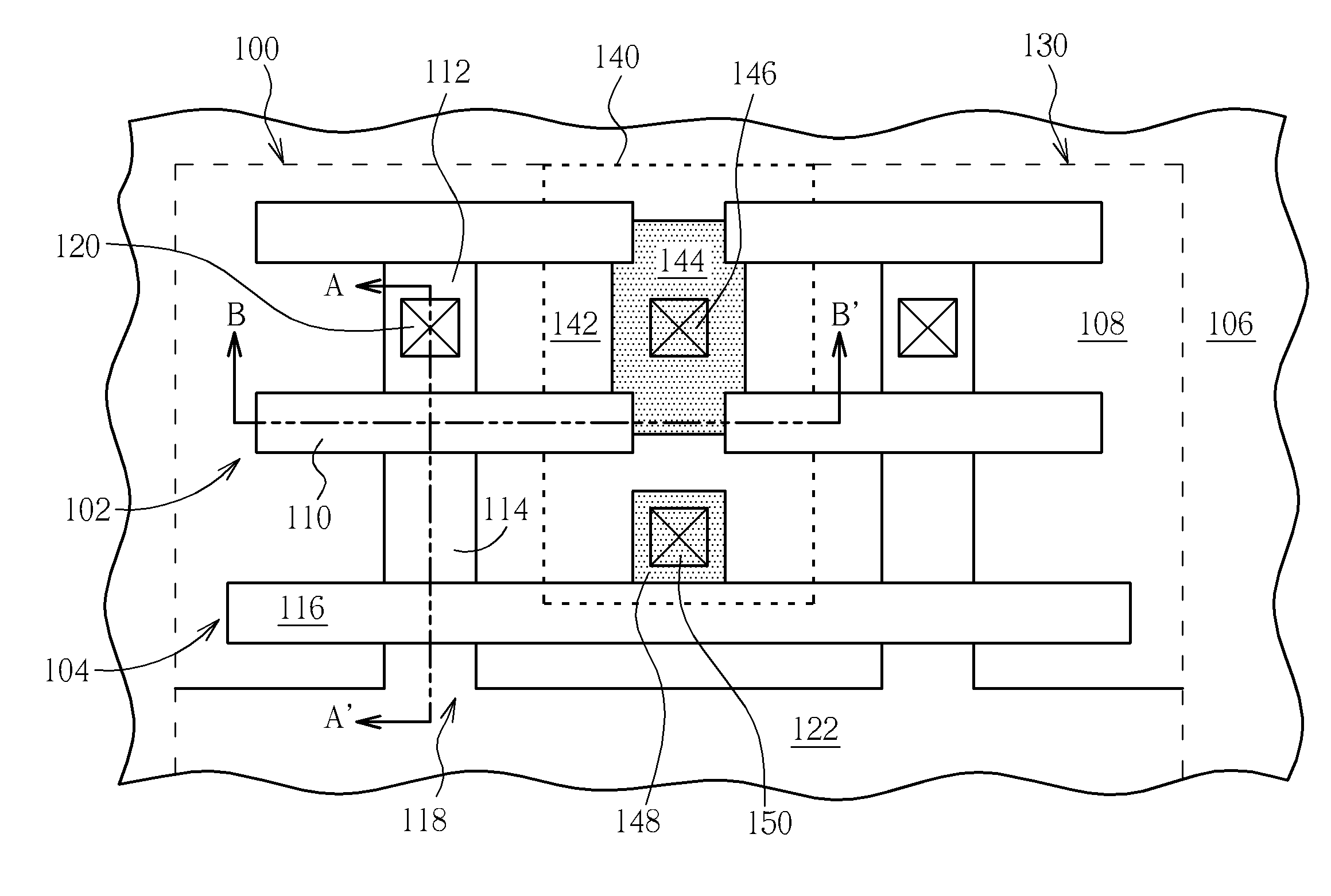

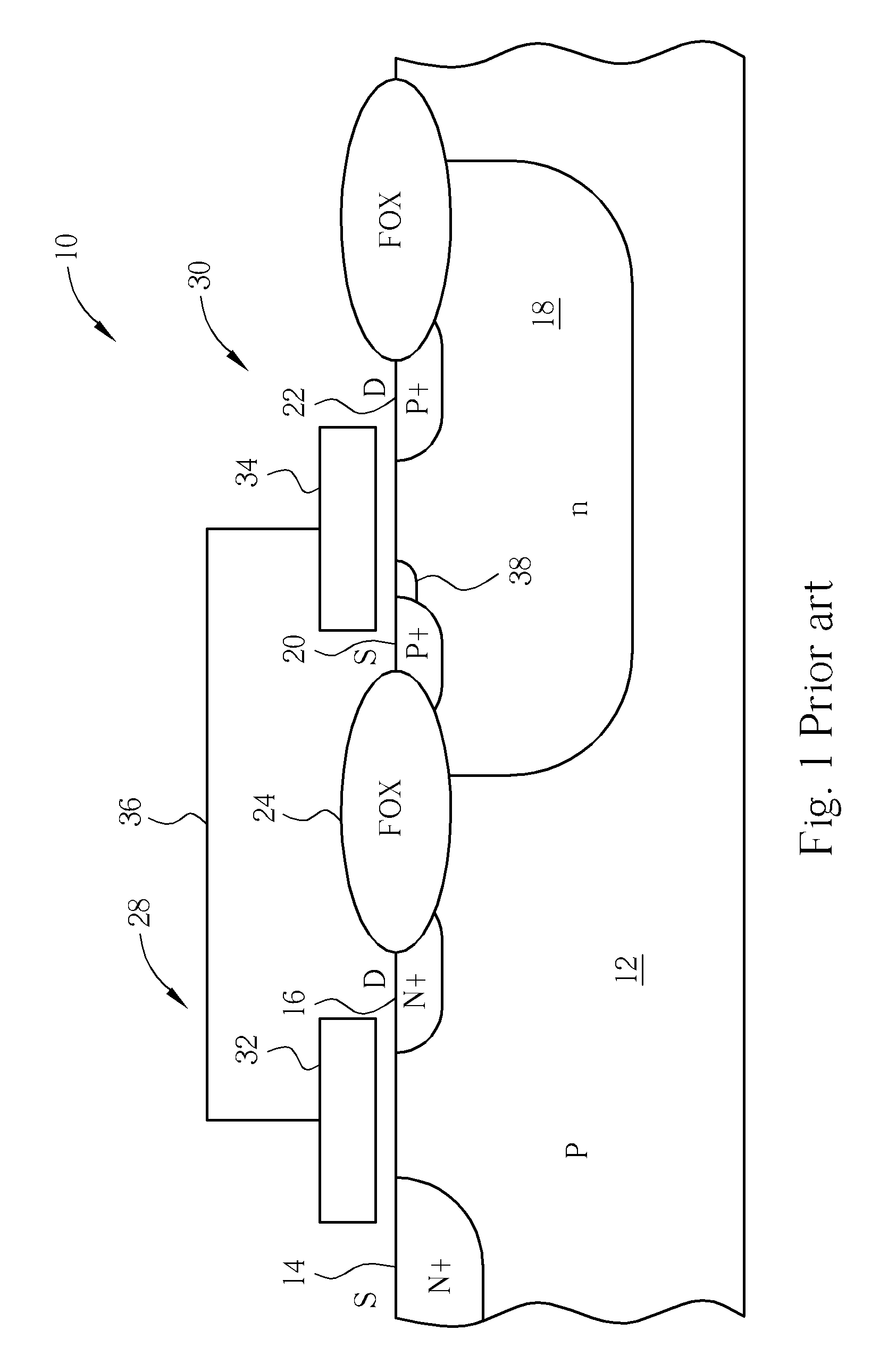

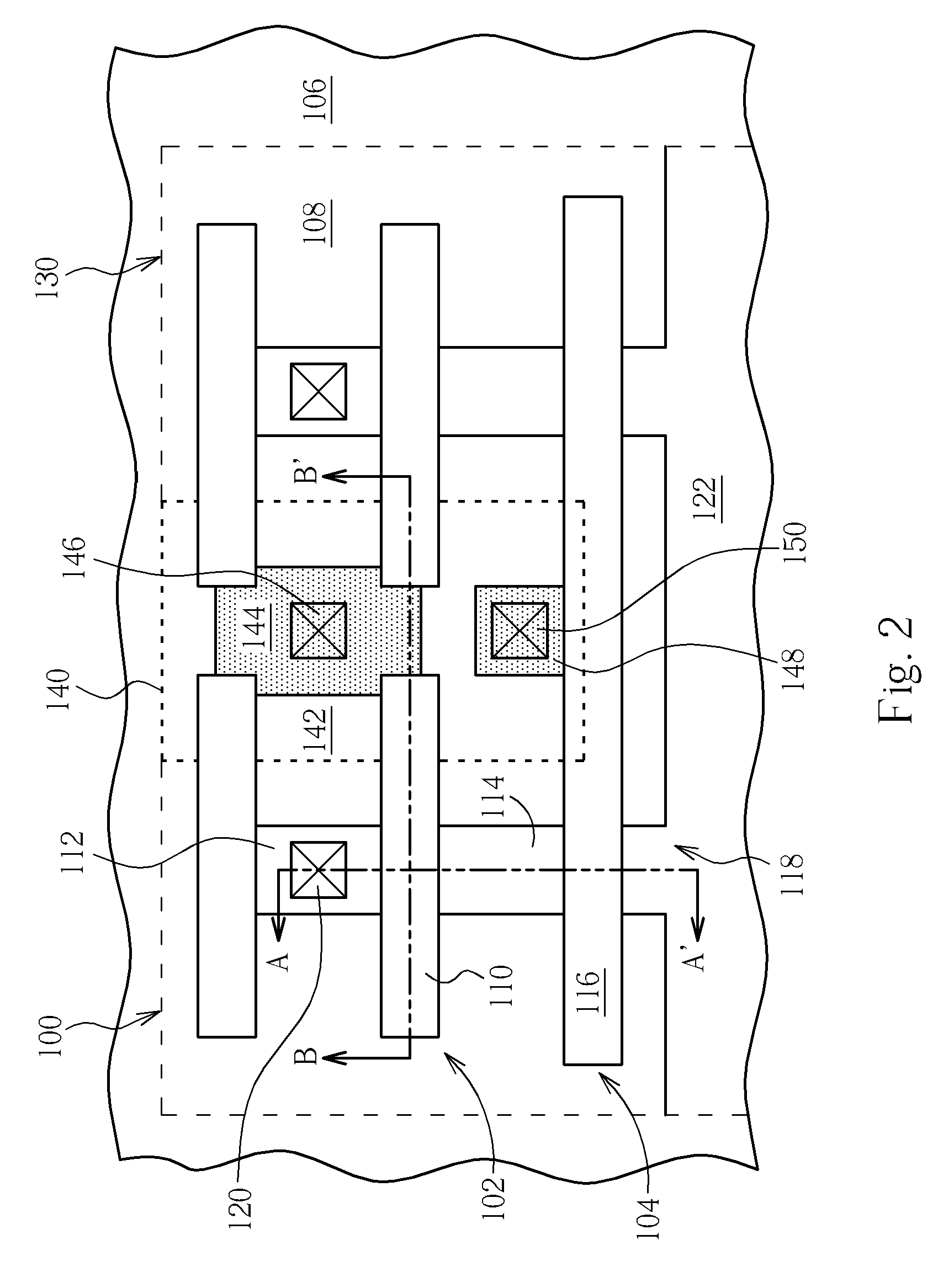

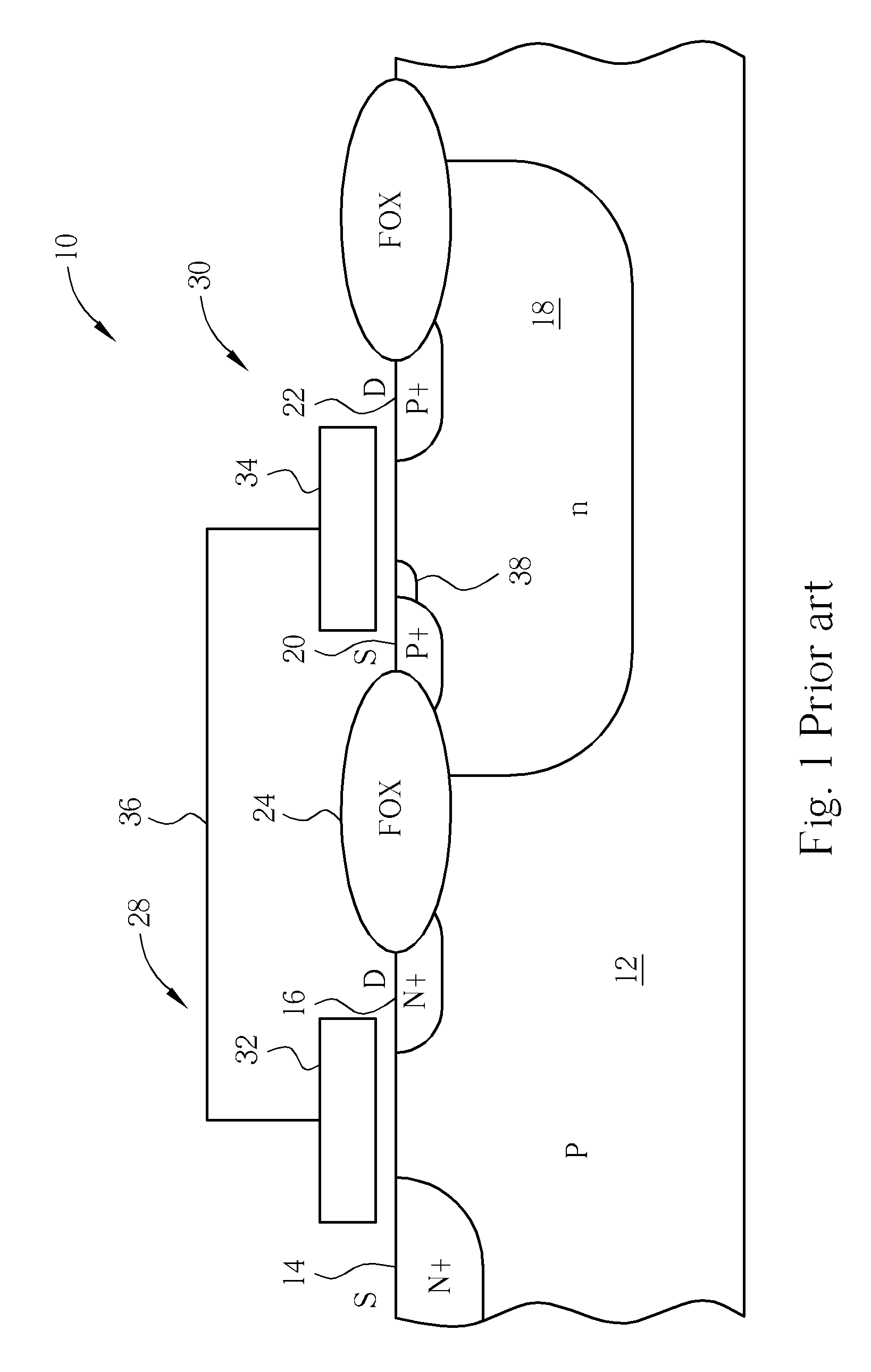

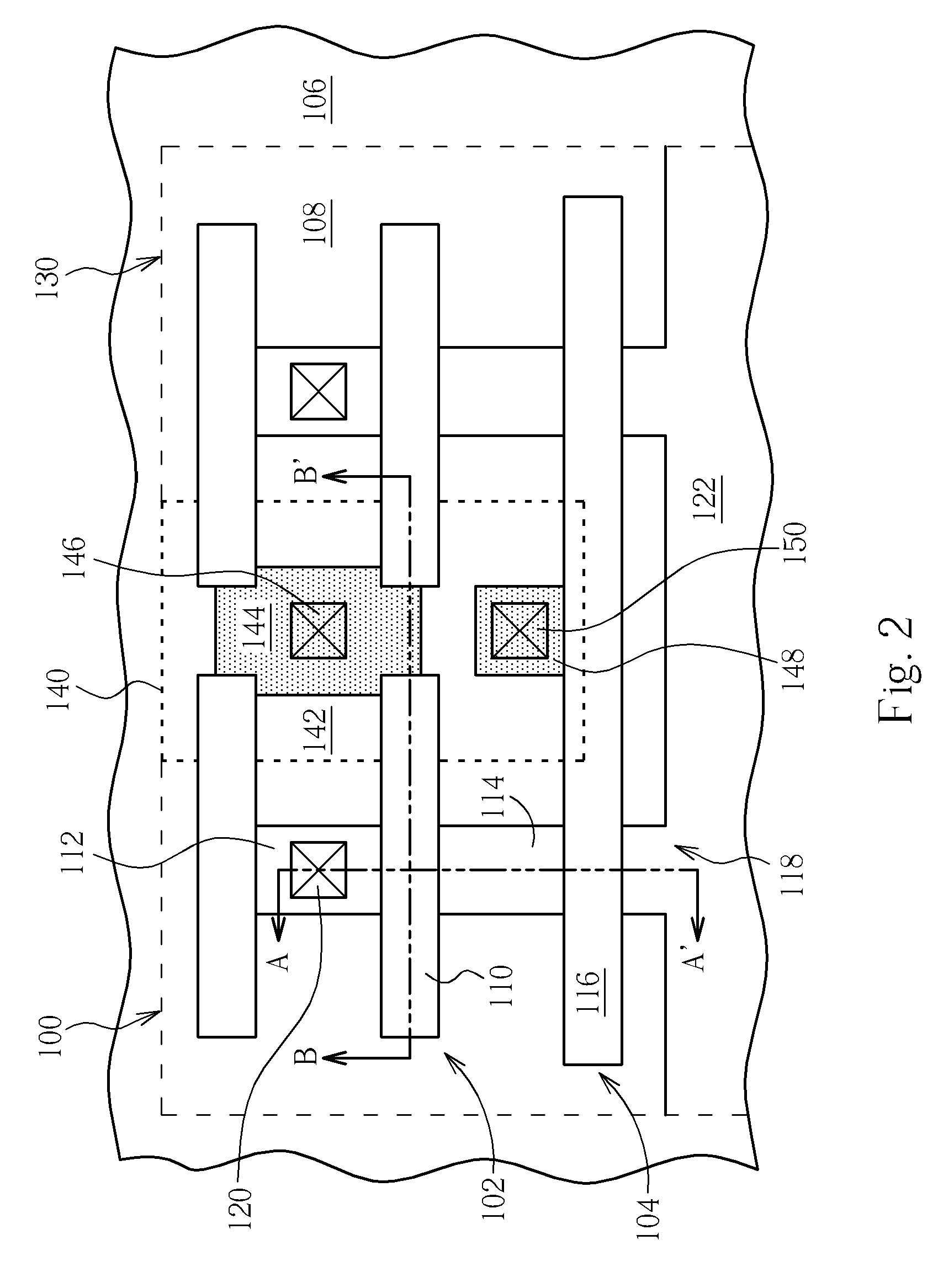

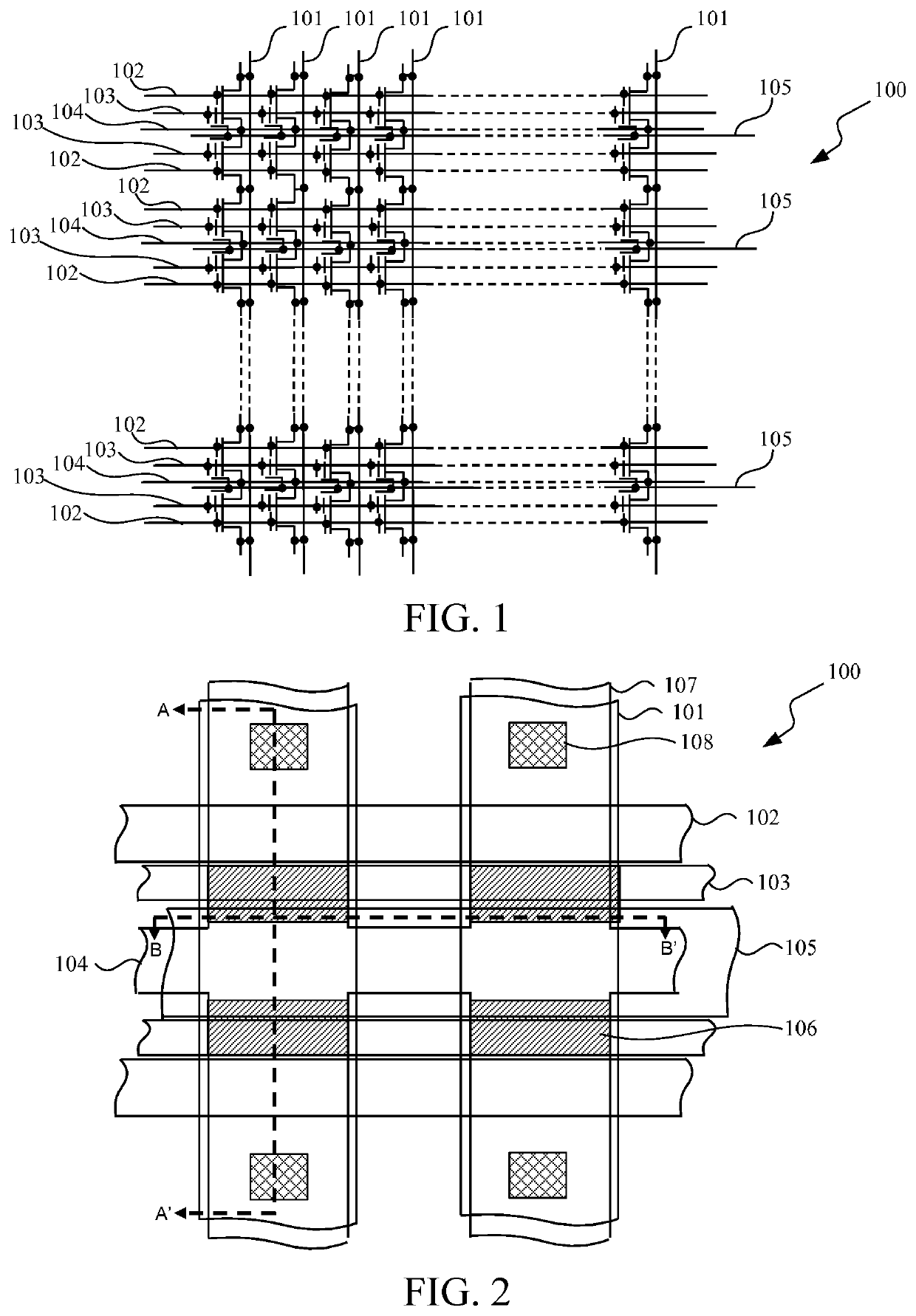

Single-poly eeprom

ActiveUS20060208306A1Improve efficiencyWider process windowTransistorSolid-state devicesInjection pointEngineering

The single-poly EEPROM includes a first PMOS transistor serially connected to a second PMOS transistor. The first and second PMOS transistors are both formed on an N-well of a P type substrate. The first PMOS transistor includes a floating gate, a first P+ doped drain region and a first P+ doped source region. The second PMOS transistor includes a gate and a second P+ doped source region. The first P+ doped drain region of the first PMOS transistor serves as a drain of the second PMOS transistor. A diode is located in the P type substrate including a P-well and a N+ doped region. The floating gate overlaps with the N-well and extends to the N+ doped region. The overlapped region of the P-well and the N+ doped region junction beneath the floating gate serves as an avalanche injection point in the vicinity of the first PMOS transistor.

Owner:UNITED MICROELECTRONICS CORP

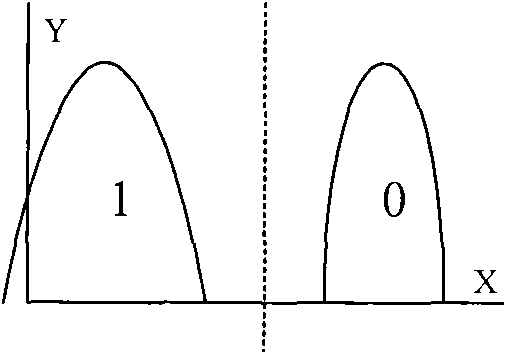

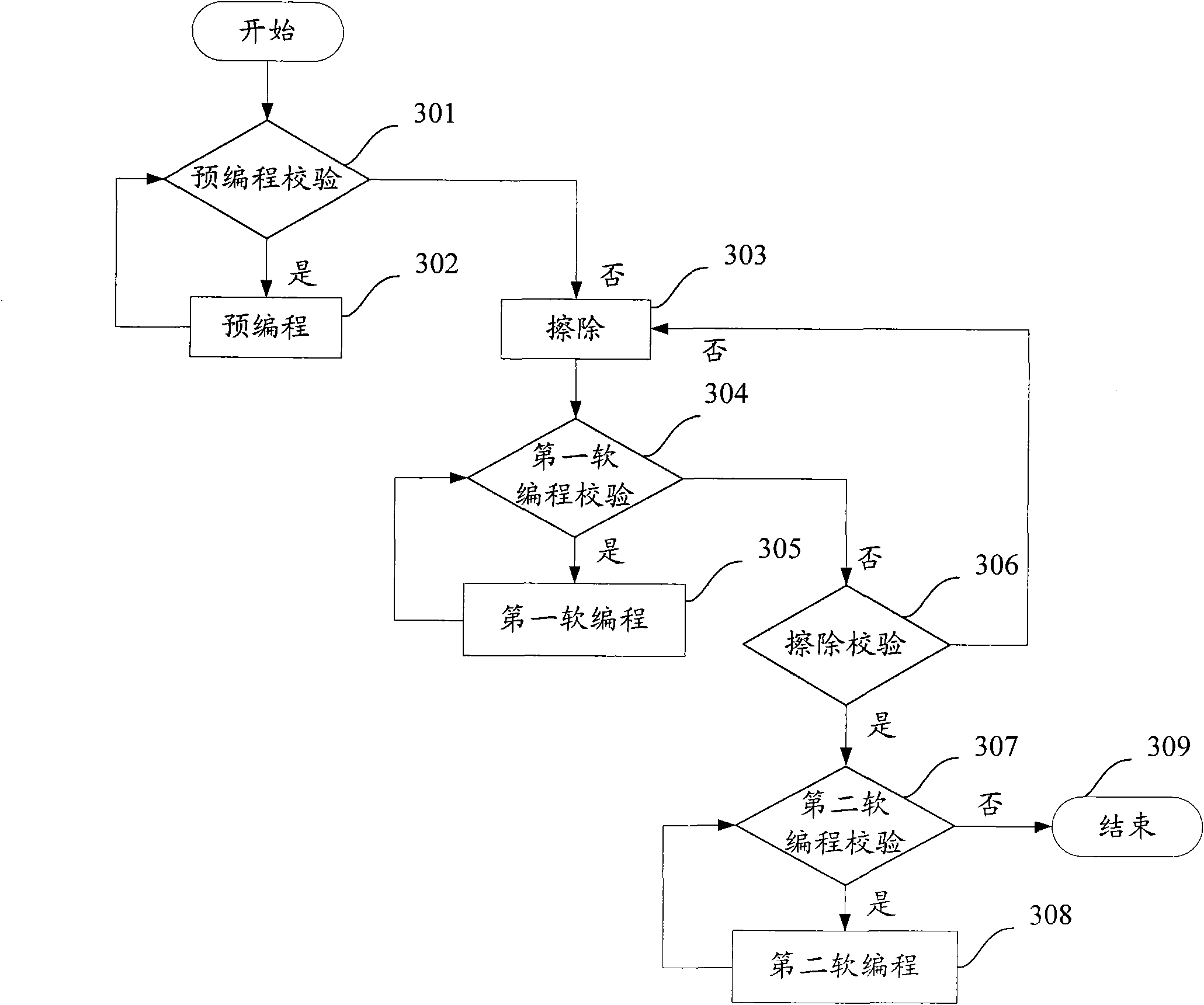

Method and device for erasing nonvolatile memory

ActiveCN101923899AImprove performanceImprove erase effectRead-only memoriesEmbedded systemThreshold voltage

The invention discloses a method and a device for erasing a nonvolatile memory. The method comprises the following steps of: after an erasing step is executed, triggering a first soft programming step to converge a distribution range of a threshold value voltage of an erased memory unit once the existence of the erased memory unit in a target erasing block is detected by a first soft programming verification step; and after the successful erasure of the target erasing block is verified by an erasing verification step, if the erased memory unit which again appears in the target erasing block is detected by a second soft programming verification step, triggering a second soft programming step to program all the erased memory units in the target erasing block into a normal erasing range so as to render all the threshold value voltages in the memory units in an erased state. The method and the device can more precisely control VT of a cell after erasing operation, so that the subsequent program operation is facilitated and the whole performance of the memory is improved.

Owner:GIGADEVICE SEMICON (BEIJING) INC

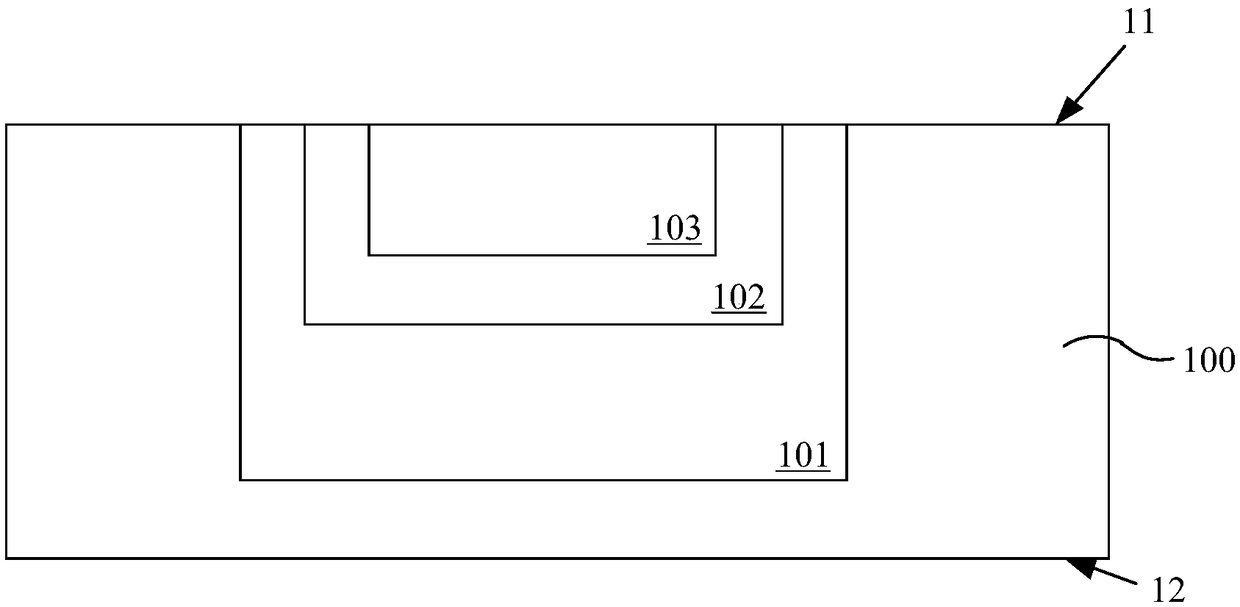

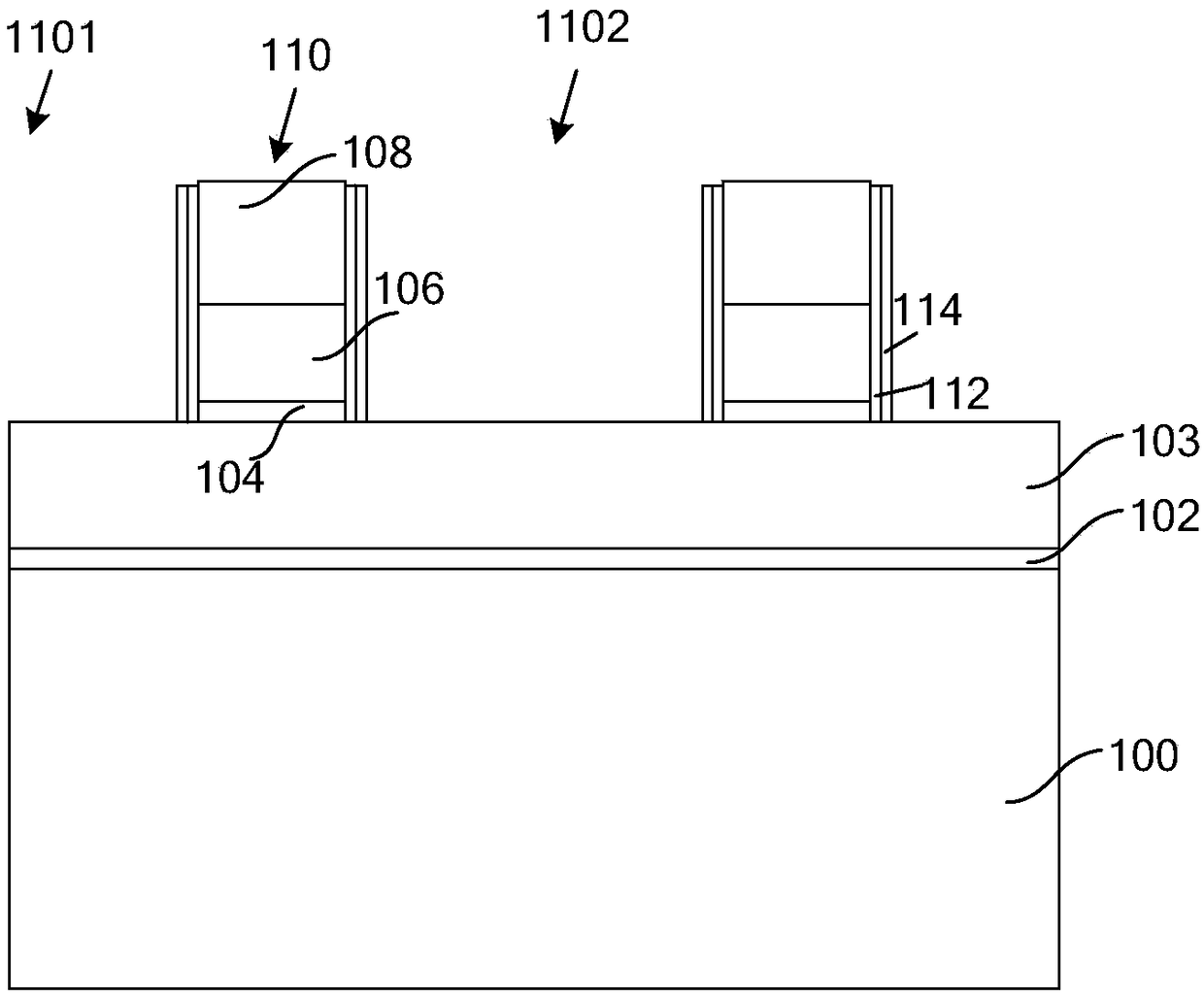

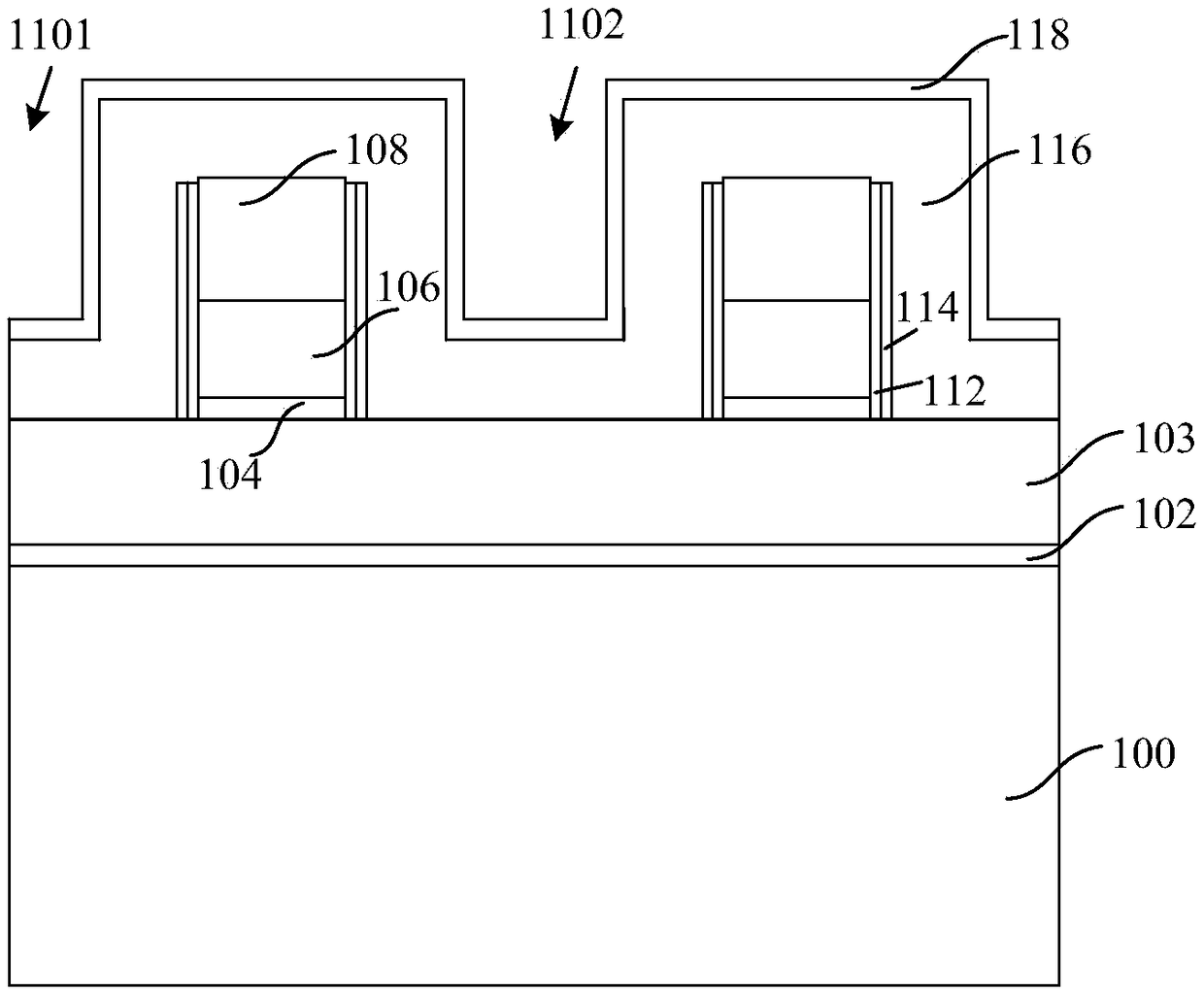

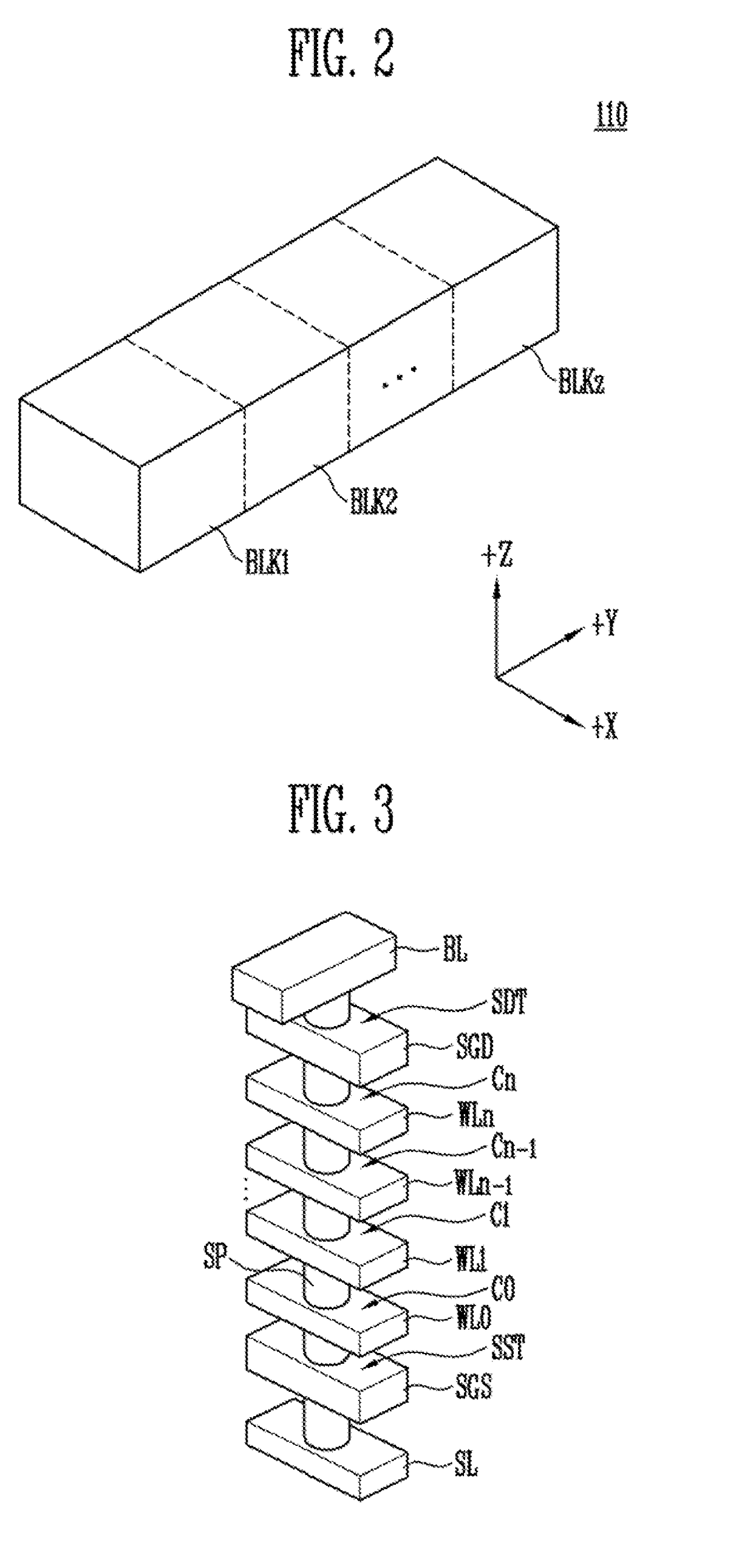

Memory structure

PendingCN109037224AImprove erase efficiencyPrevent leakageSolid-state devicesSemiconductor devicesEngineering

Owner:YANGTZE MEMORY TECH CO LTD

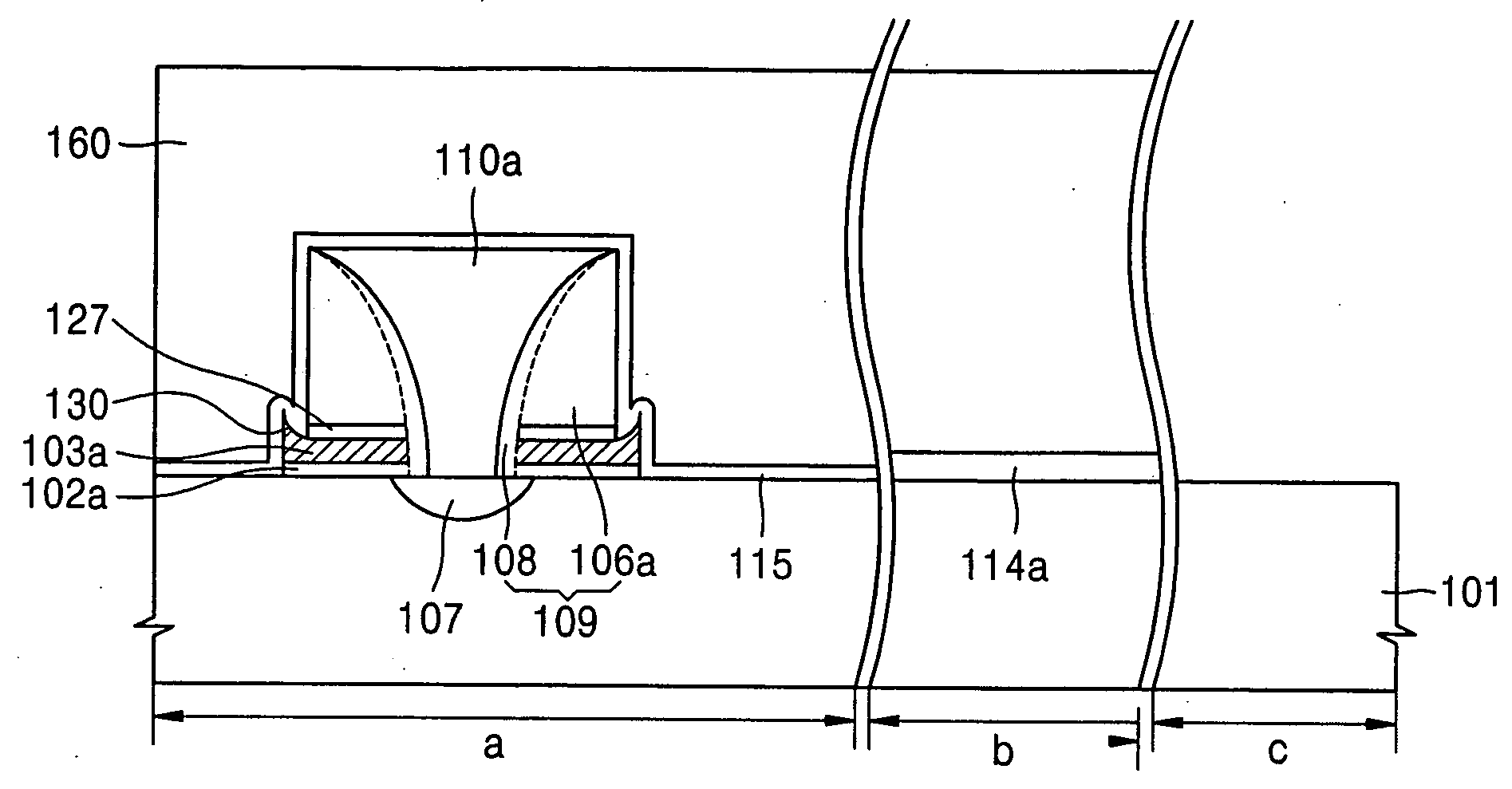

Method of manufacturing split-gate memory

ActiveUS20050112821A1Improve erase efficiencyImprove efficiencyTransistorSolid-state devicesLow voltageCell region

A method of manufacturing split-gate memory provides a control gate insulating film and the tunneling insulating film in a cell region, a high voltage gate insulating film in a high voltage region, and a low voltage gate insulating film in a low voltage region, all having different thickness. Additionally, a pre-cleaning process removes an outer sidewall portion of a spacer to form a tip portion of a floating gate that overlaps a control gate line formed proximate the floating gate.

Owner:SAMSUNG ELECTRONICS CO LTD

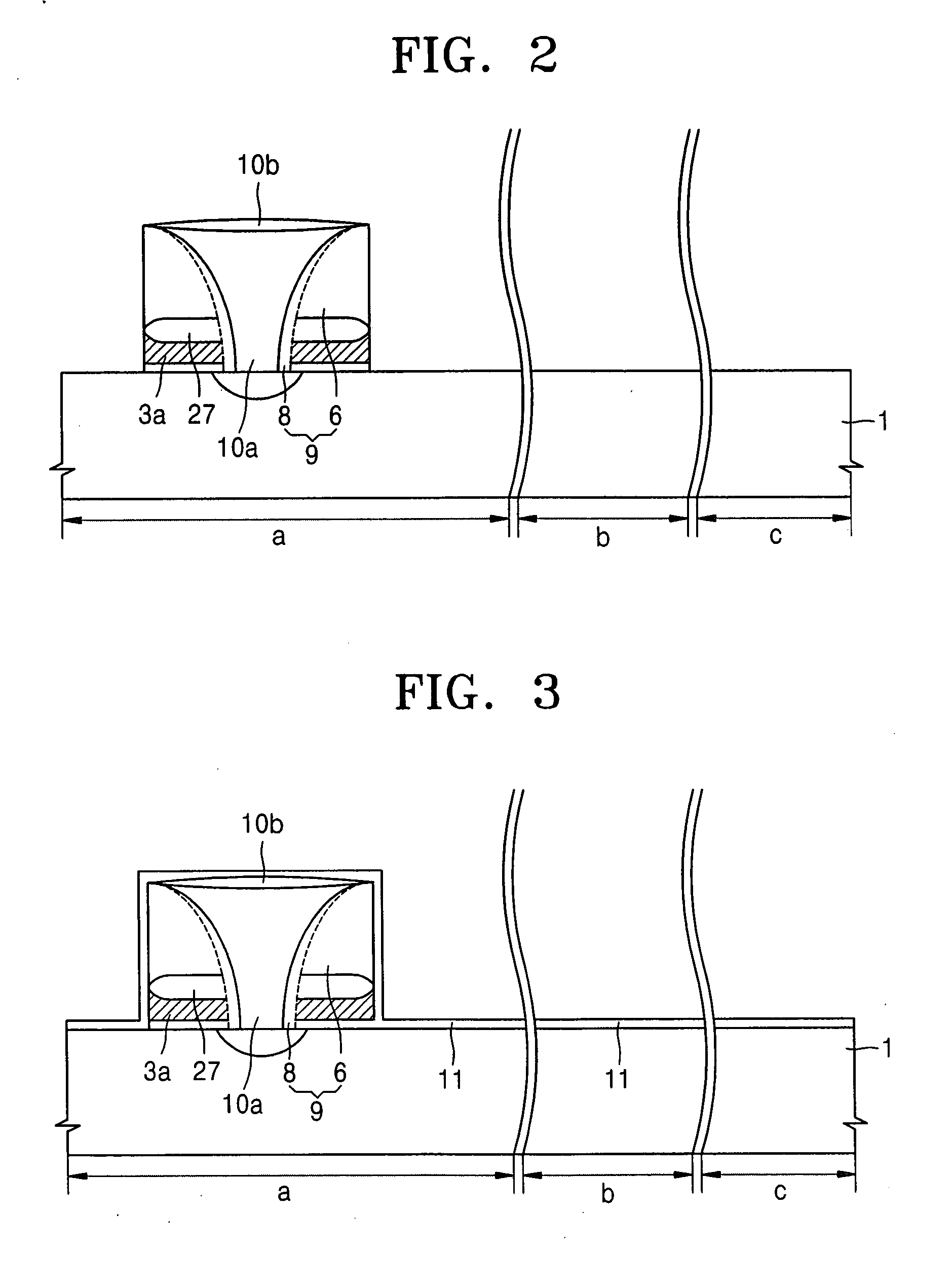

Nonvolatile semiconductor memory device and method of manufacturing the same

InactiveUS20090200600A1Couple capacitanceImprove erase efficiencyTransistorSolid-state devicesSemiconductor memorySemiconductor

A nonvolatile semiconductor memory device has: a semiconductor substrate; a control gate and a floating gate that are formed side by side on a gate insulating film on a channel region in the semiconductor substrate; and an erase gate facing an upper surface of the floating gate and totally located above the upper surface of the floating gate. The upper surface of the floating gate includes a first side and a second side that face each other. A bottom surface of the erase gate is closer to the first side and the second side than the upper surface between the first side and the second side.

Owner:RENESAS ELECTRONICS CORP

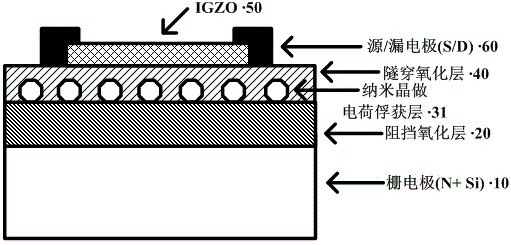

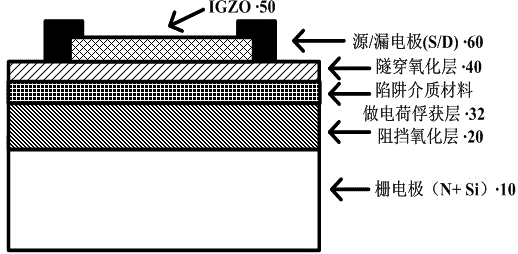

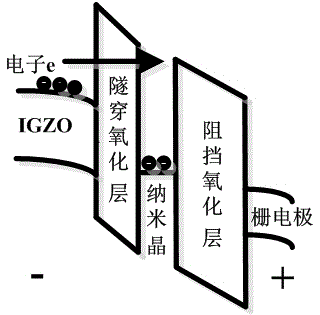

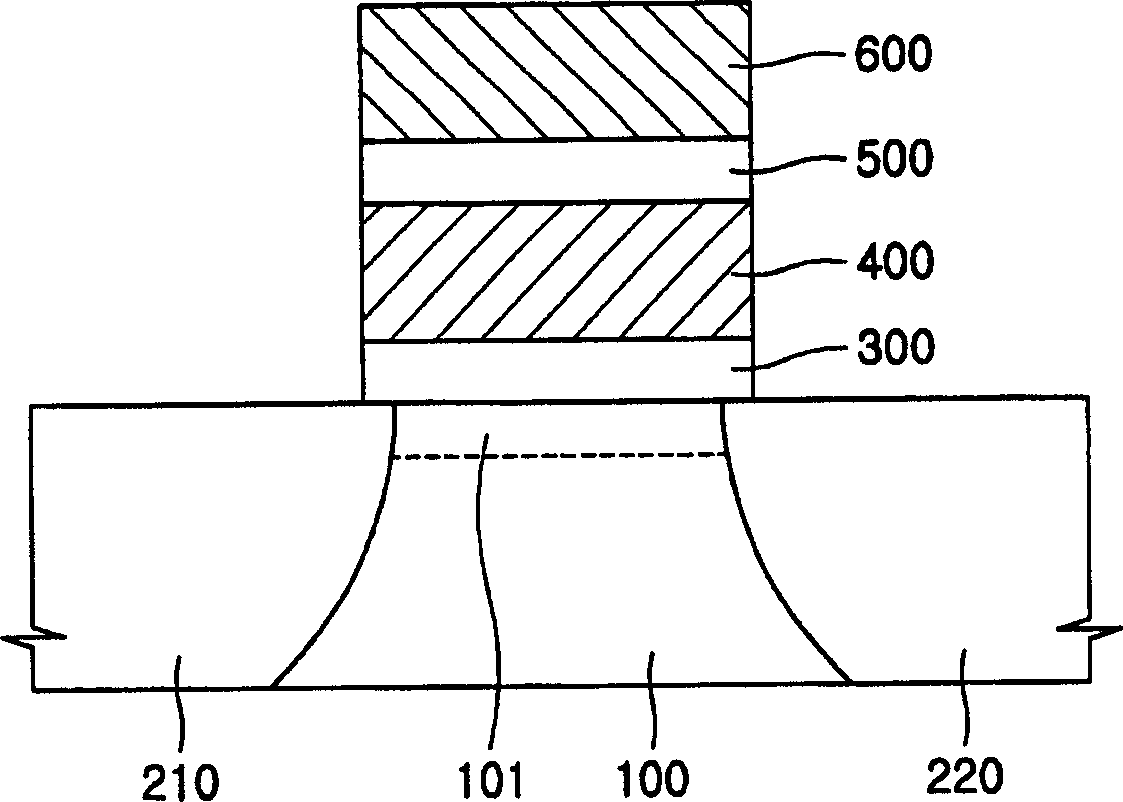

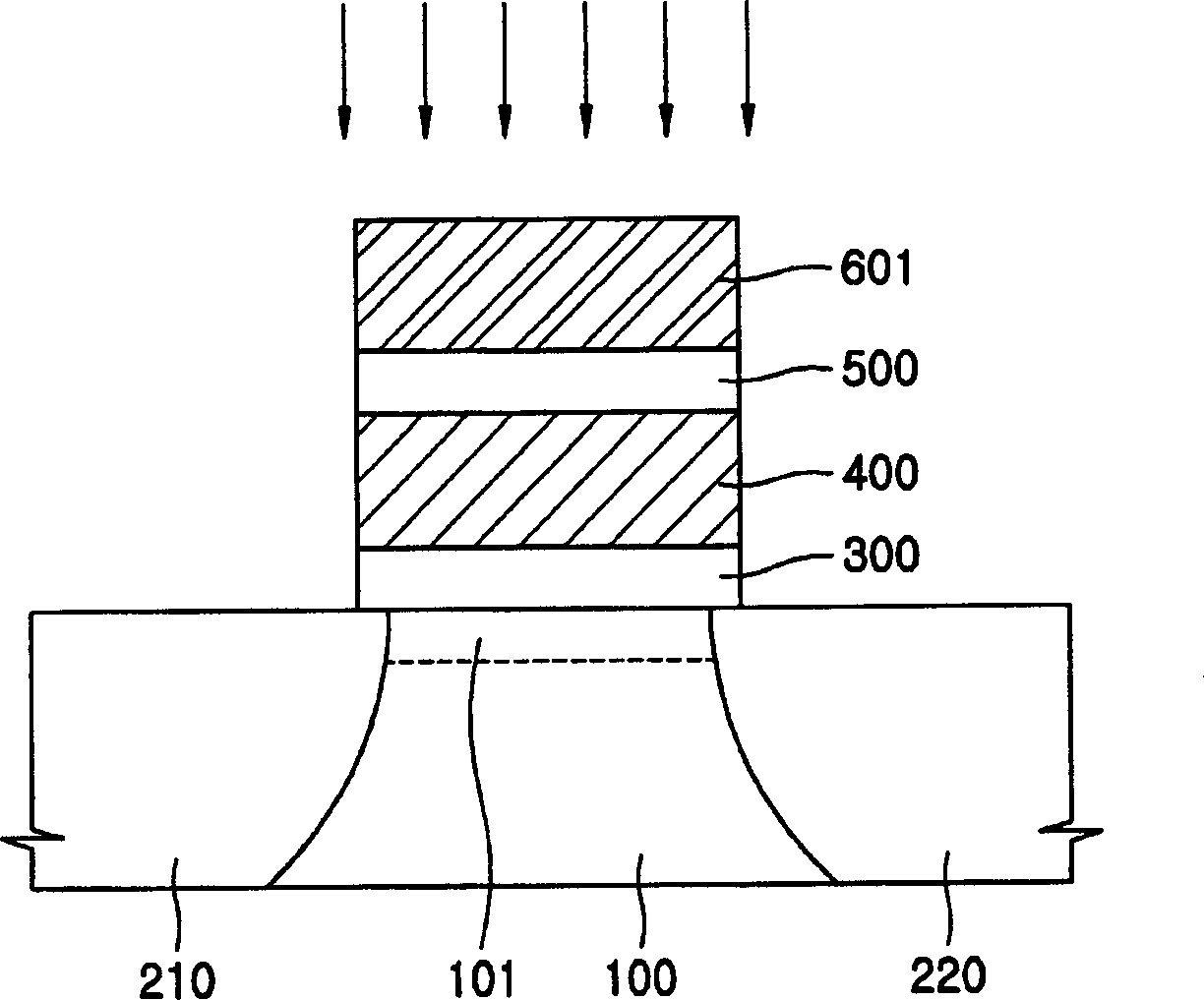

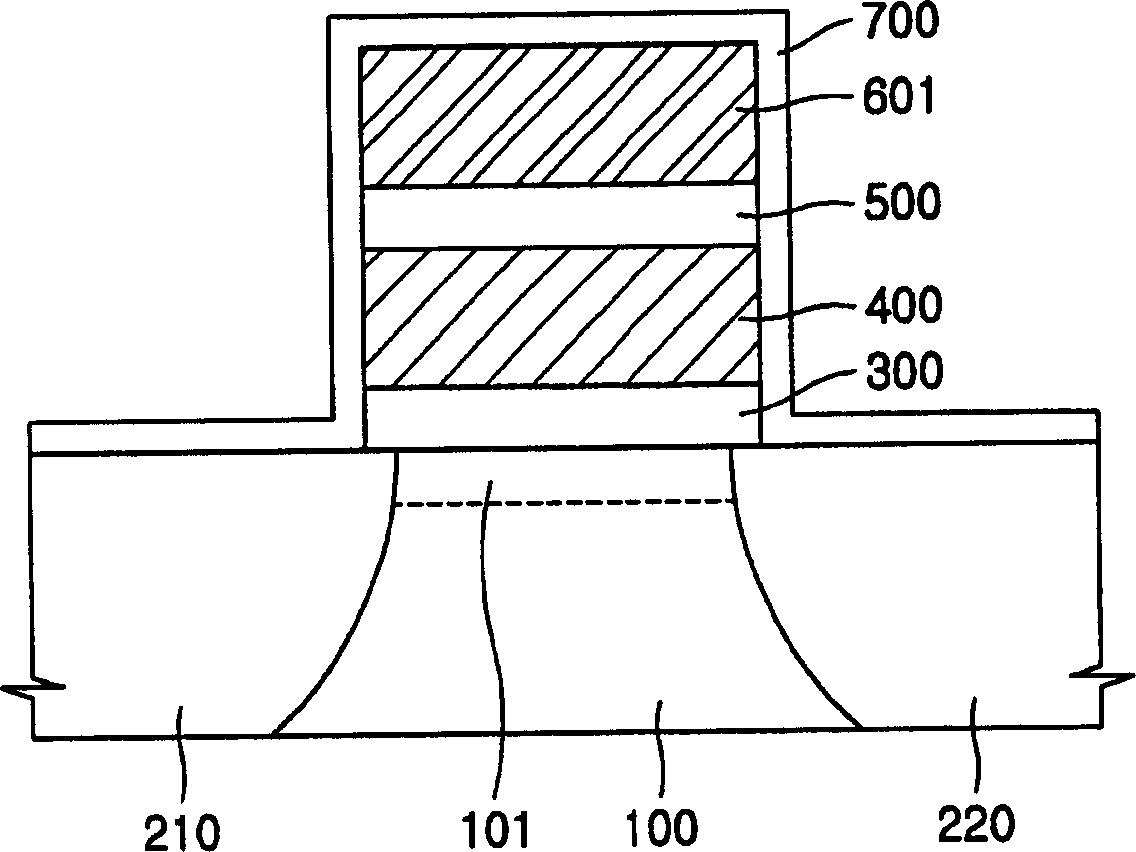

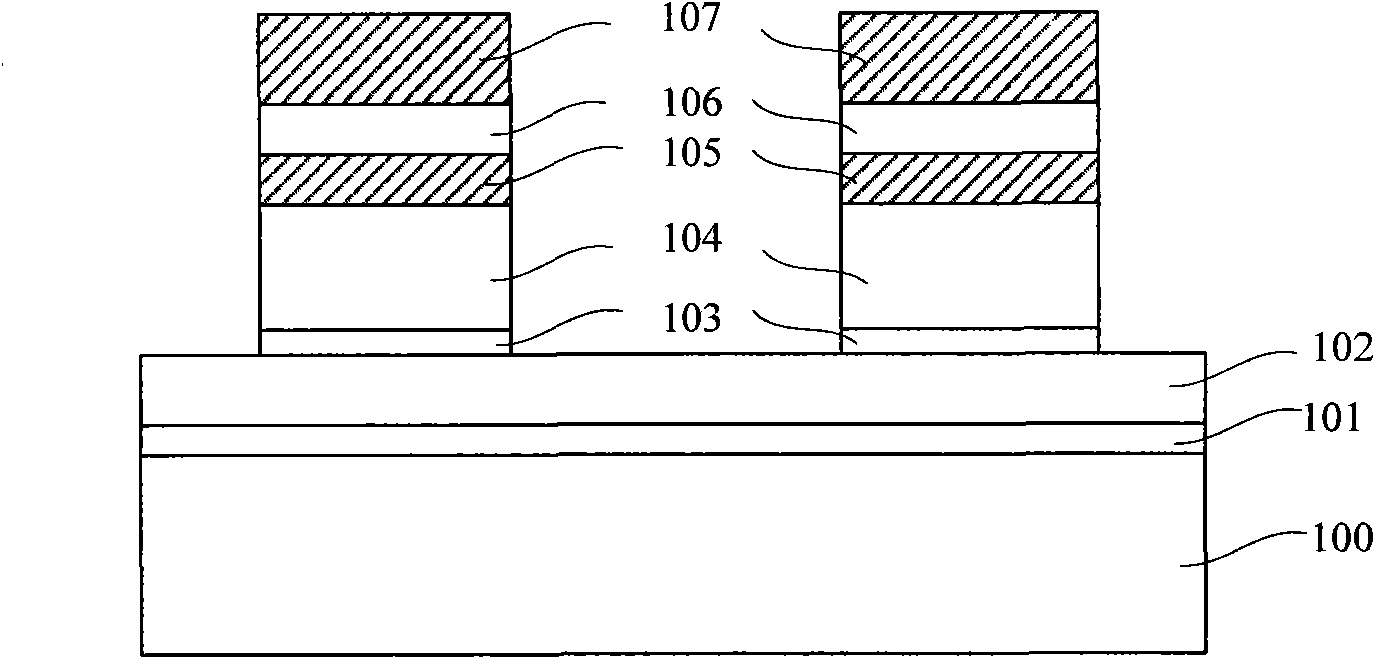

Electrical programming-ultraviolet light erasing memory device structure and preparation method thereof

InactiveCN103606564AImprove the possibility of applicationImprove erase efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingUltraviolet lights

The invention provides an electrical programming-ultraviolet light erasing memory device structure and a preparation method thereof. A heavily-doped N type monocrystalline silicon wafer is used as a substrate and an extraction electrode of a gate; an oxide insulator with relatively good compactness is used as a charge barrier layer of a memory; a thin-film material with many charge defects or nanocrystalline is used as a charge capture layer; an oxide insulator with relatively good compactness and a forbidden band being large in width as a tunneling layer of the memory; an IGZO film is used as an electroconductive channel of the memory, an active area is defined through photoetching and wet etching and the electroconductive channel is formed; processing of a source electrode and a drain electrode is completed through photoetching, metal deposition and stripping technology; in test, a positive pulse is applied to a gate electrode to realize programming operation of the device; and erasure of the device is realized by using ultraviolet light to irradiate the device without applying any bias voltage. The electrical programming-ultraviolet light erasing memory device structure solves the problem that an IGZO channel-based TFT memory cannot be erased; the erasure efficiency and the working speed of the device are improved; and the application space of the IGZO channel-based TFT memory is enlarged.

Owner:FUDAN UNIV

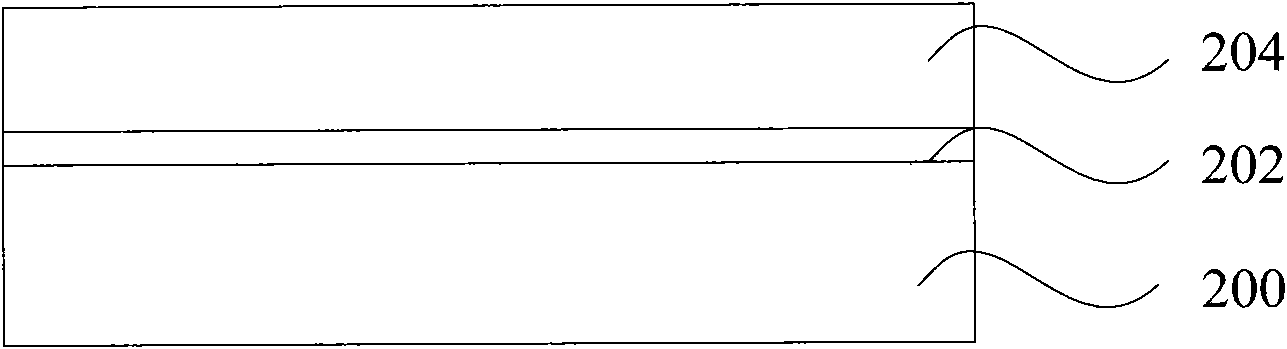

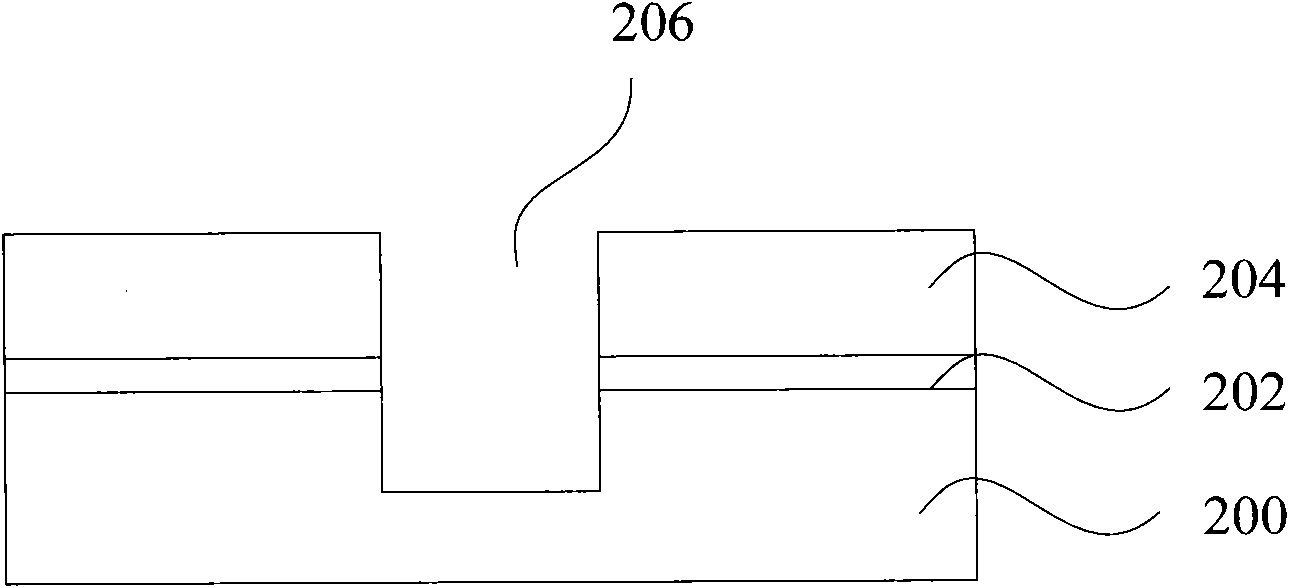

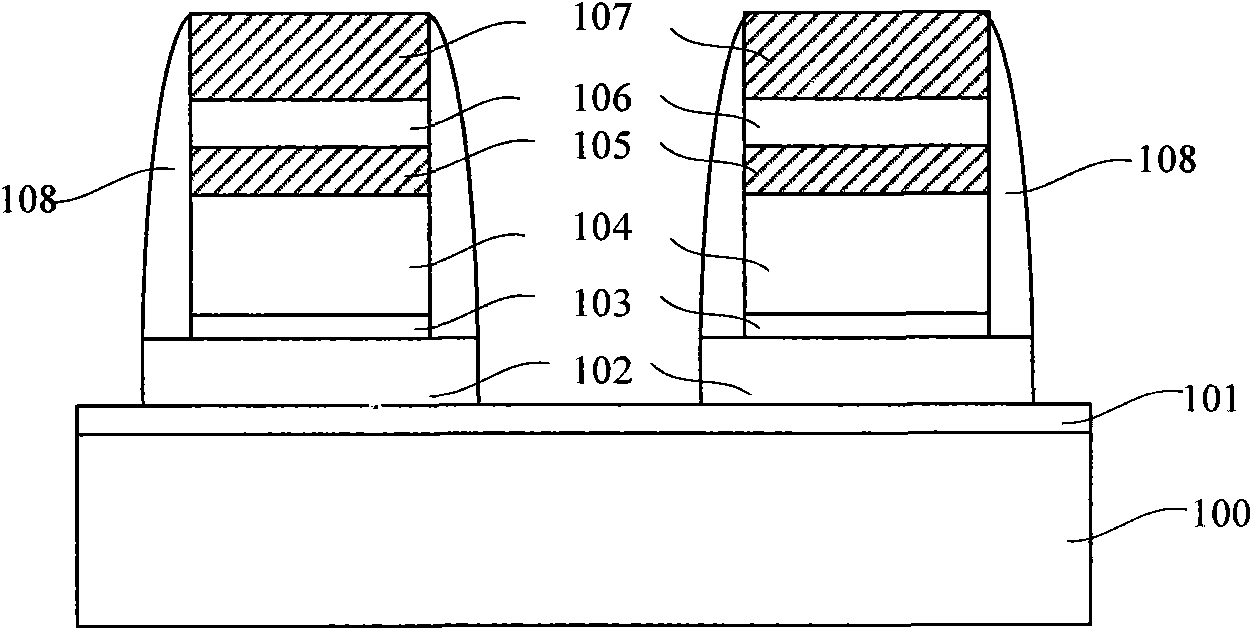

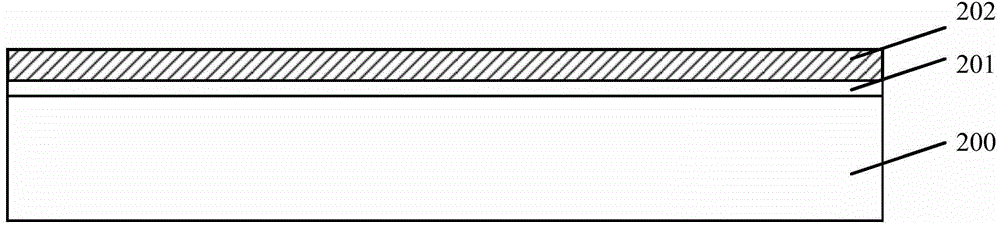

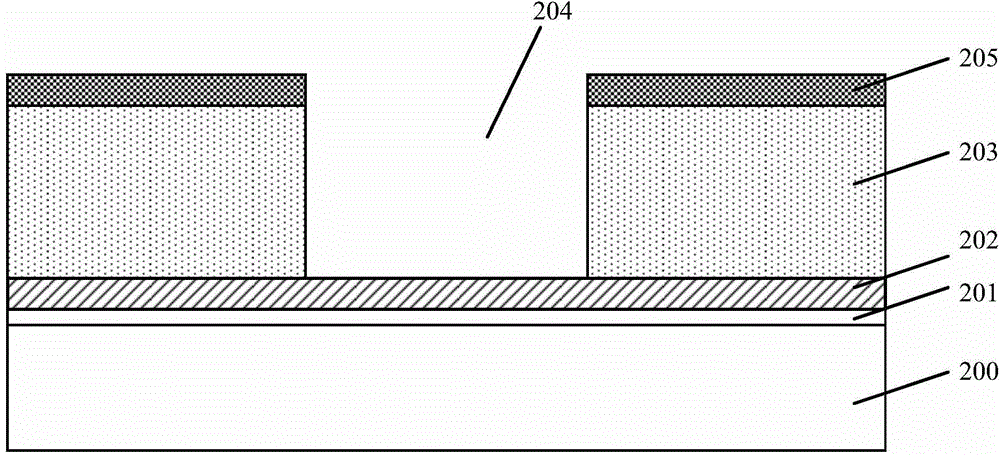

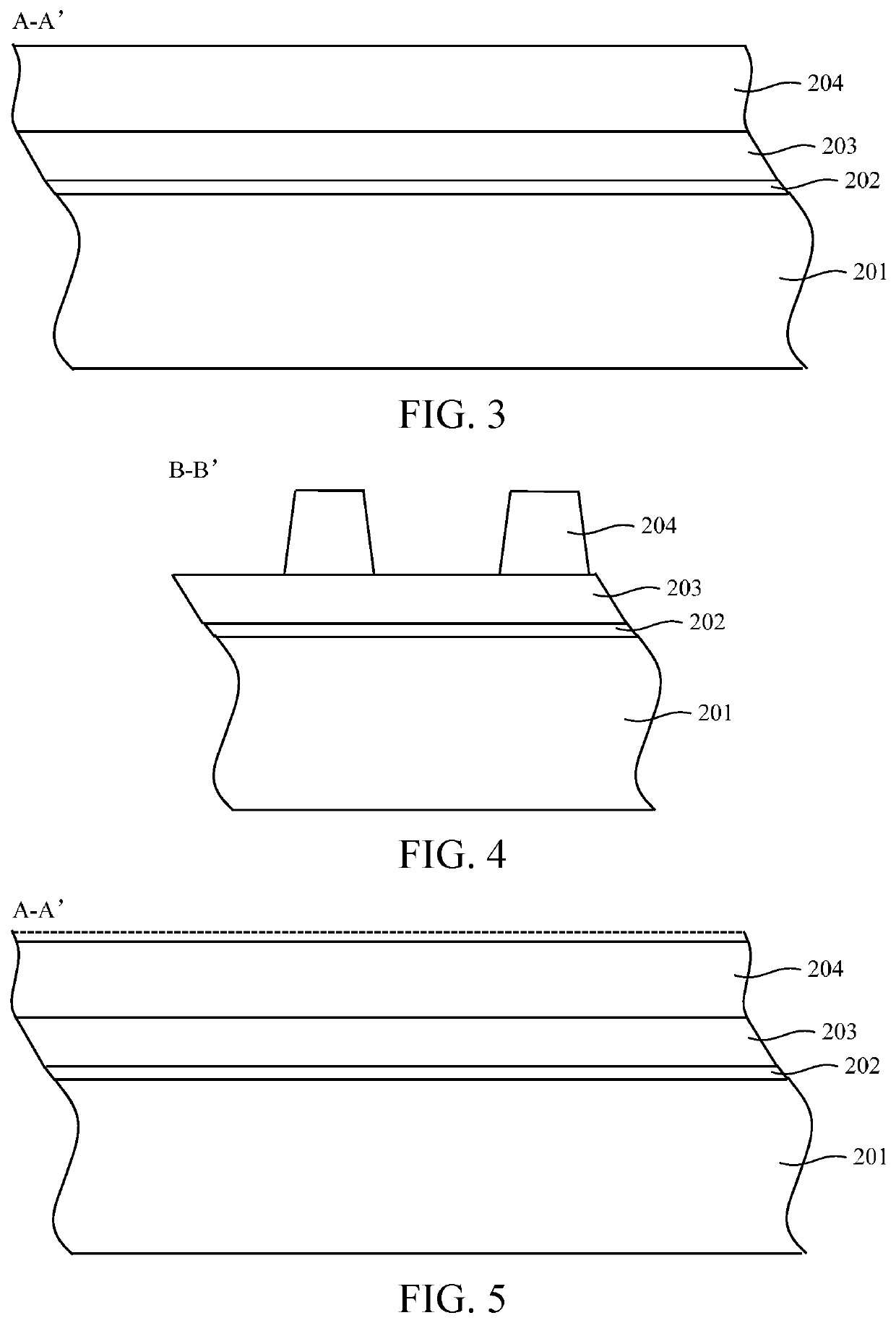

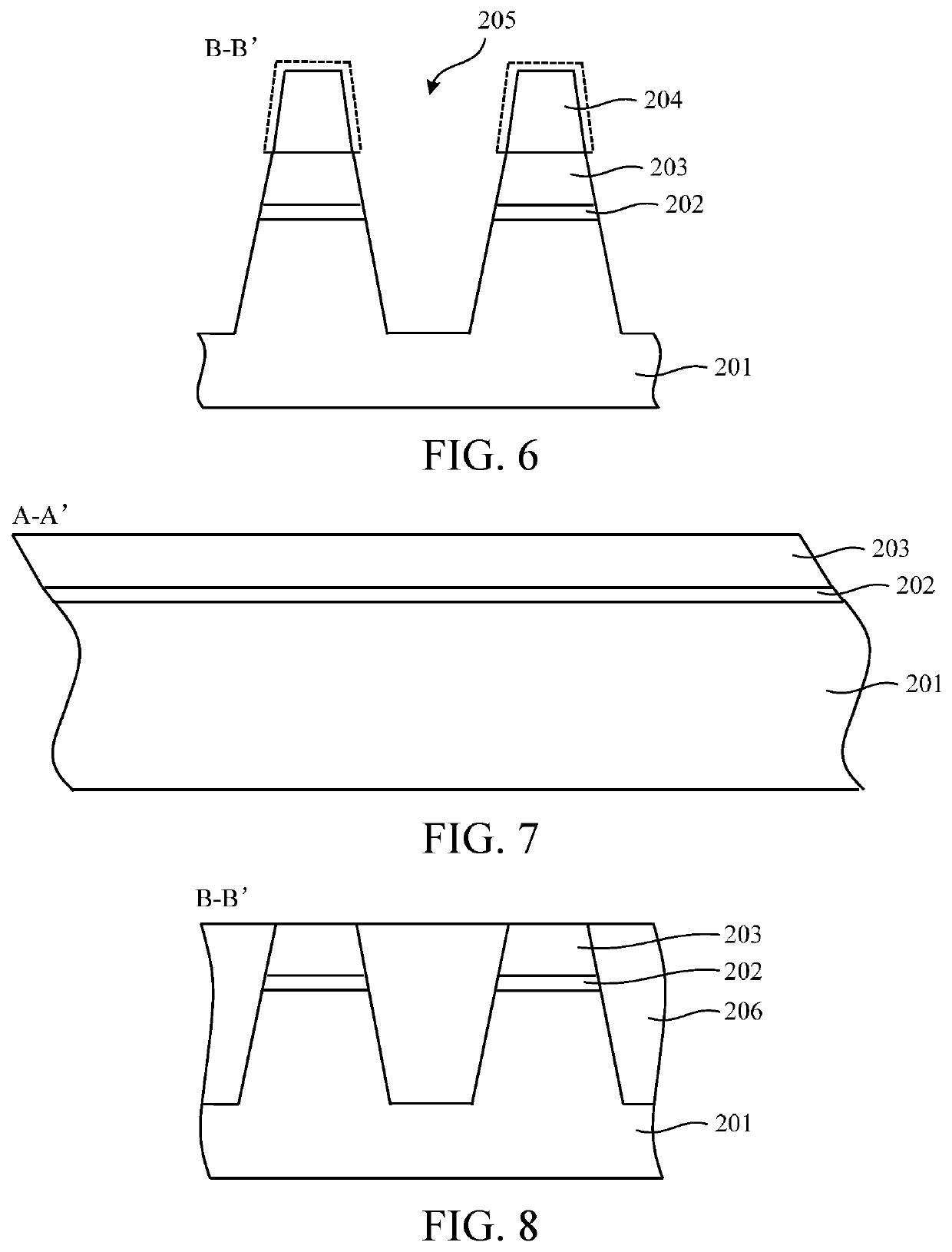

Formation method for split gate storage device

ActiveCN102044498AImprove thickness uniformityEnsure consistencySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsPolycrystalline silicon

The invention discloses a formation method for a split gate storage device, which is composed of a semiconductor substrate, wherein the semiconductor substrate is successively provided with a gate dielectric layer, a floating gate polycrystalline silicon layer and a hard mask layer. The formation method comprises the following steps: performing trench isolation etching on the hard mask layer, floating gate polycrystalline silicon layer, gate dielectric layer and part of the semiconductor substrate to form isolated trenches; filling dielectric in the isolated trenches; and removing the hard mask layer. By adopting the self-alignment shallow slot isolation method to form the floating gate polycrystalline silicon layer, the thickness uniformity of the floating gate polycrystalline silicon layer is improved and the consistency of the erasing performance of storage units can be ensured.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

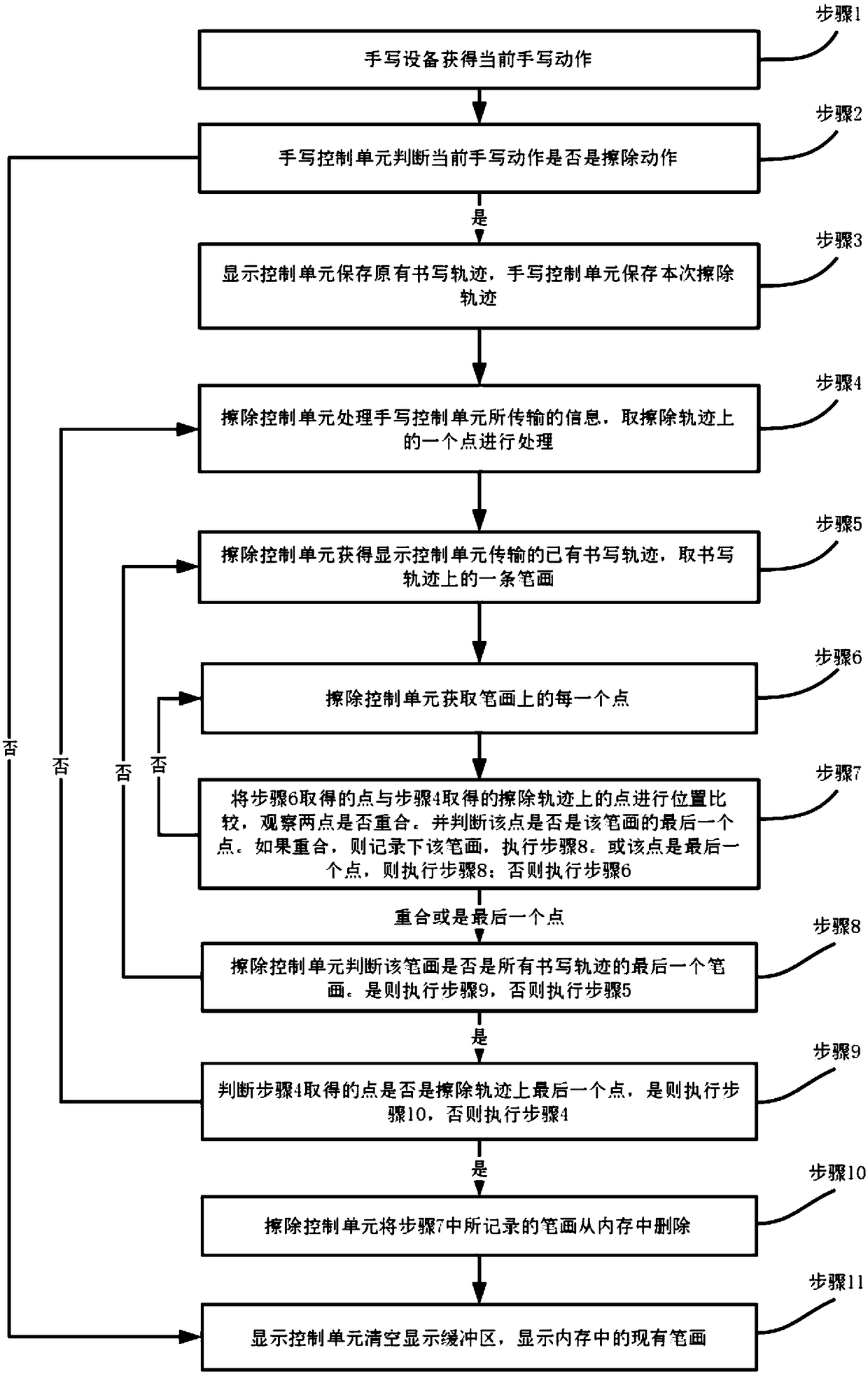

A method of deleting handwriting stroke information inputted by a user on a handwriting device

ActiveCN109445676ASatisfy erasure needsAchieve normal displayInput/output processes for data processingHandwritingInformation type

The invention discloses a method for deleting handwriting stroke information inputted by a user on a handwriting device, which relates to the field of information science and technology. The method comprises the following steps of after receiving the handwritten information input by the user, identifying the type of the information as erased information, comparing the existing information with thetrack information of the item, selecting the strokes to be erased and deleting the strokes, and displaying the modified handwriting information in real time by the display device. The invention has the following advantages that the handwriting device has a plurality of working modes, and the erasing method can automatically judge whether the current erasing action is an erasing action or not according to the input mode of the user; after reading and saving the erasing tracks, the handwriting passing through each track can be judged, so as to erase the corresponding strokes and satisfy the erasing requirements of some users; at the same time, the erasing effect of the strokes is displayed on the ink screen interface in real time, and the display speed is fast and the erasing efficiency ishigh.

Owner:宁波思骏科技有限公司

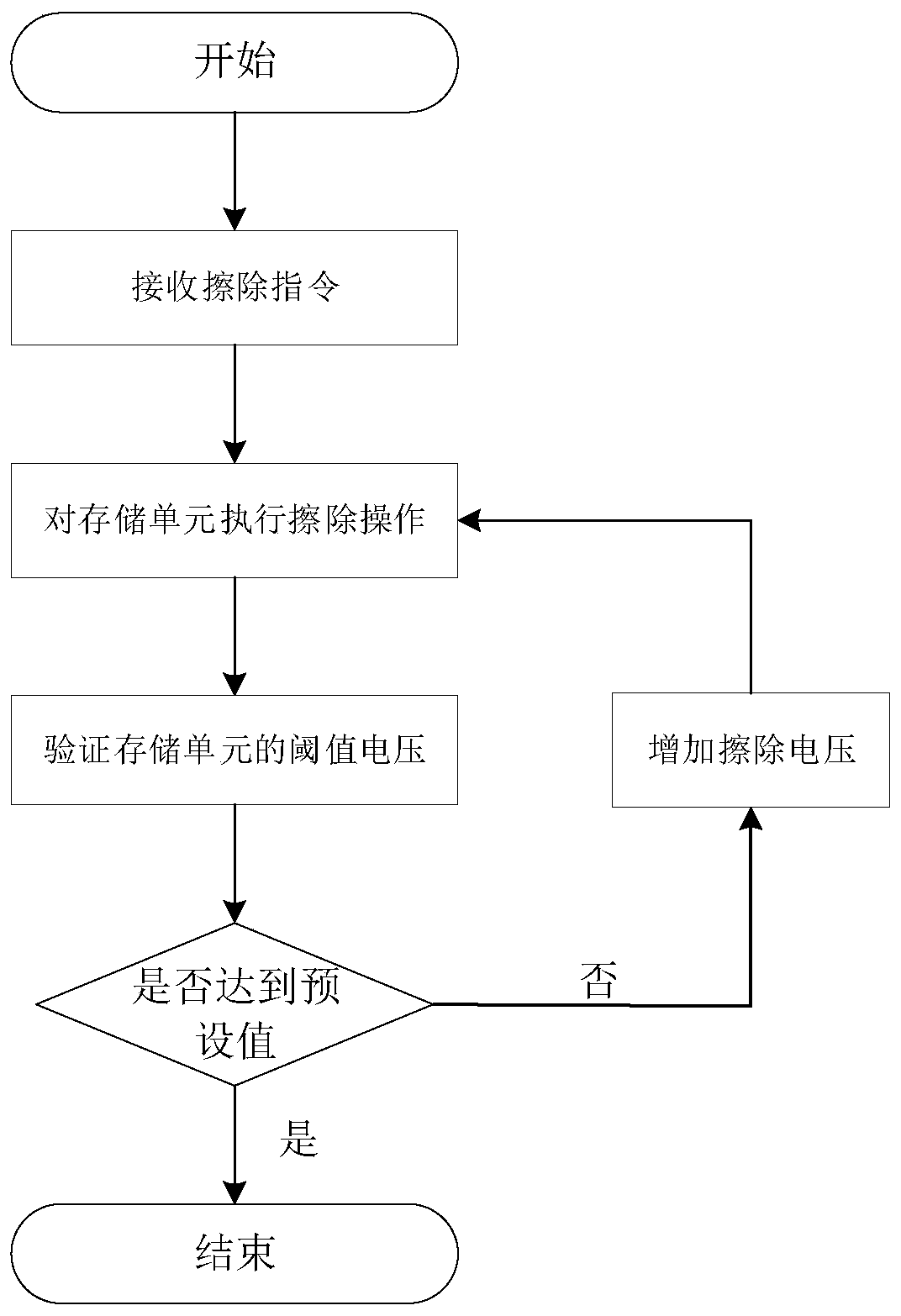

Erasing method and device for non-volatile memory

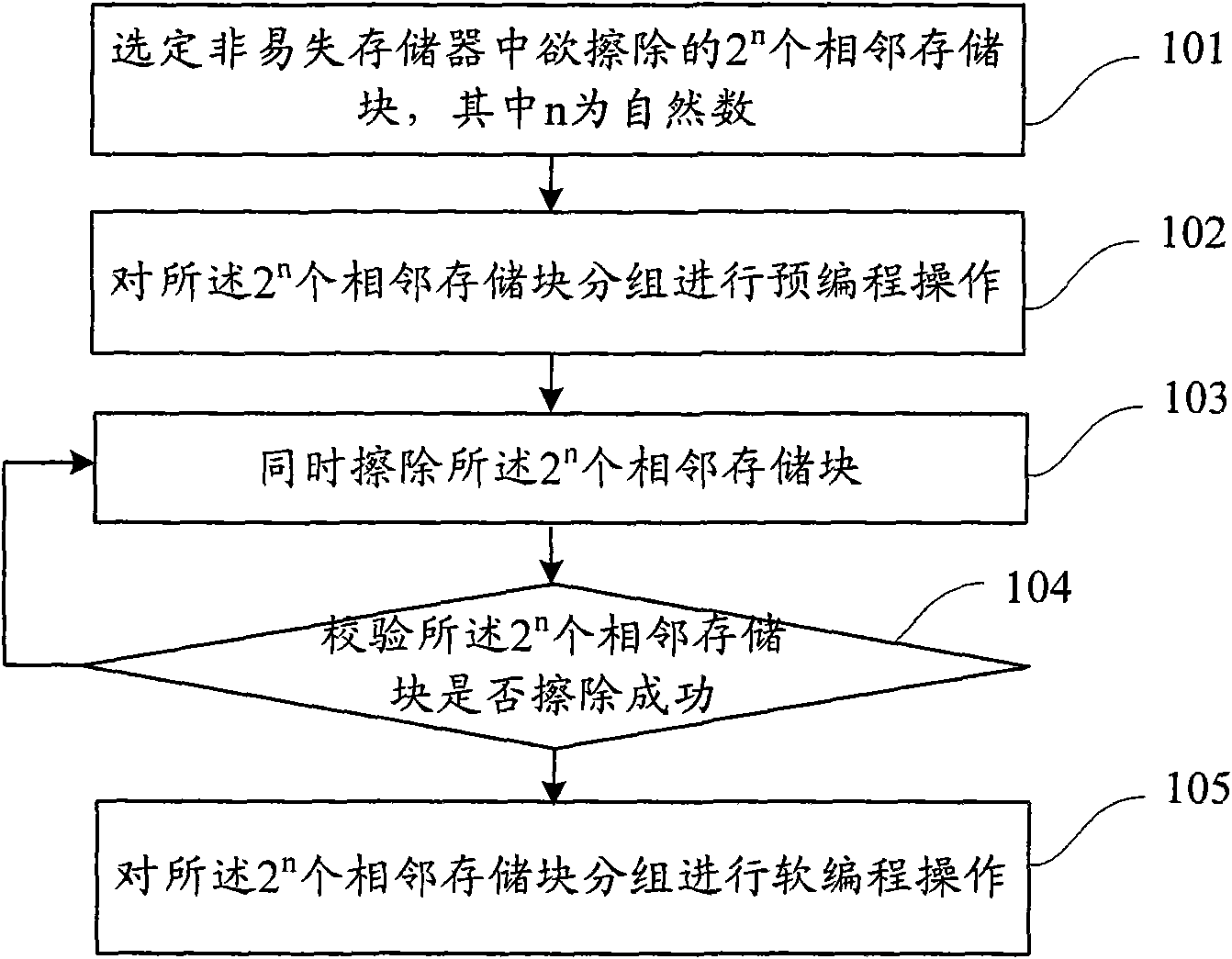

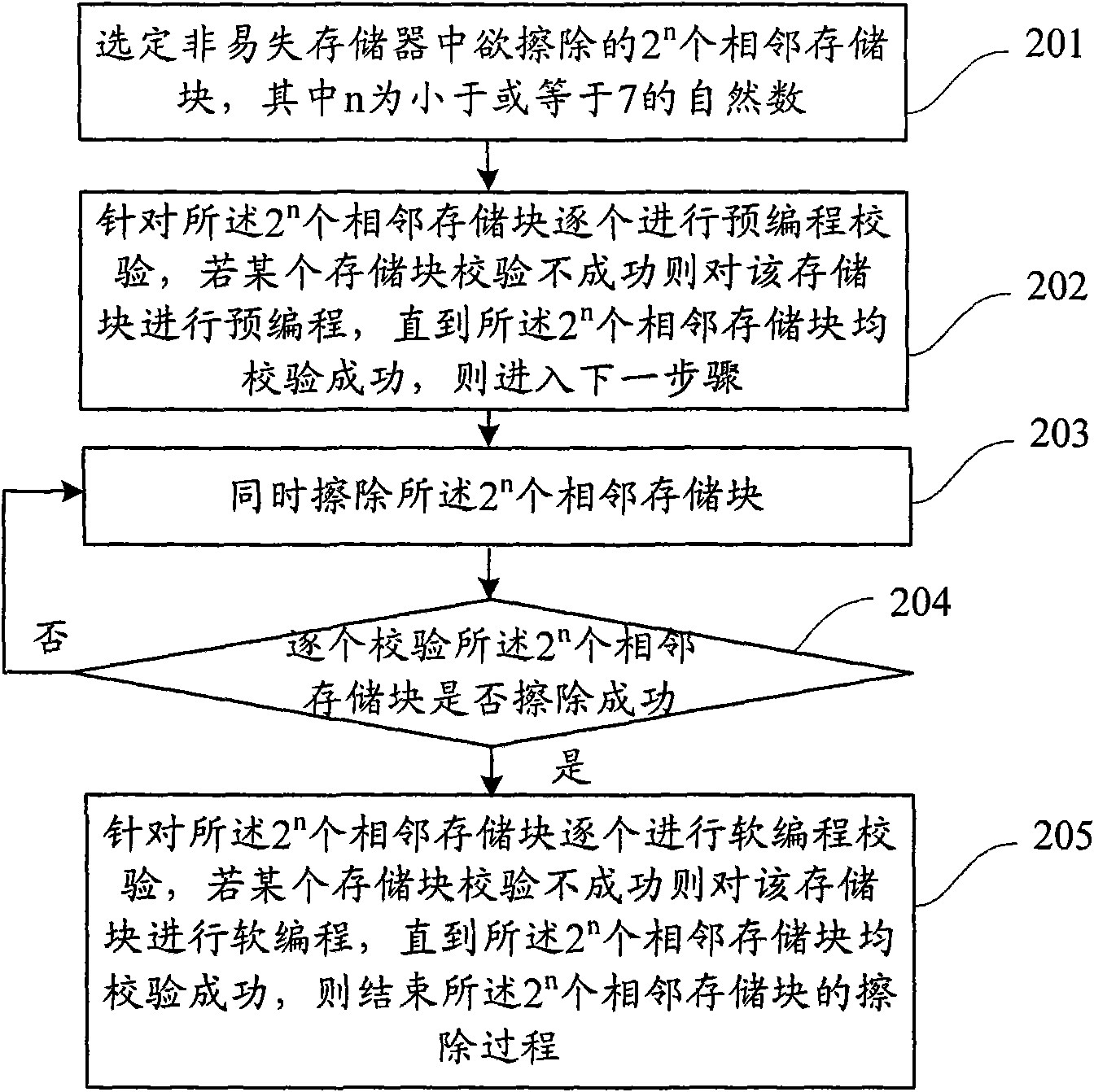

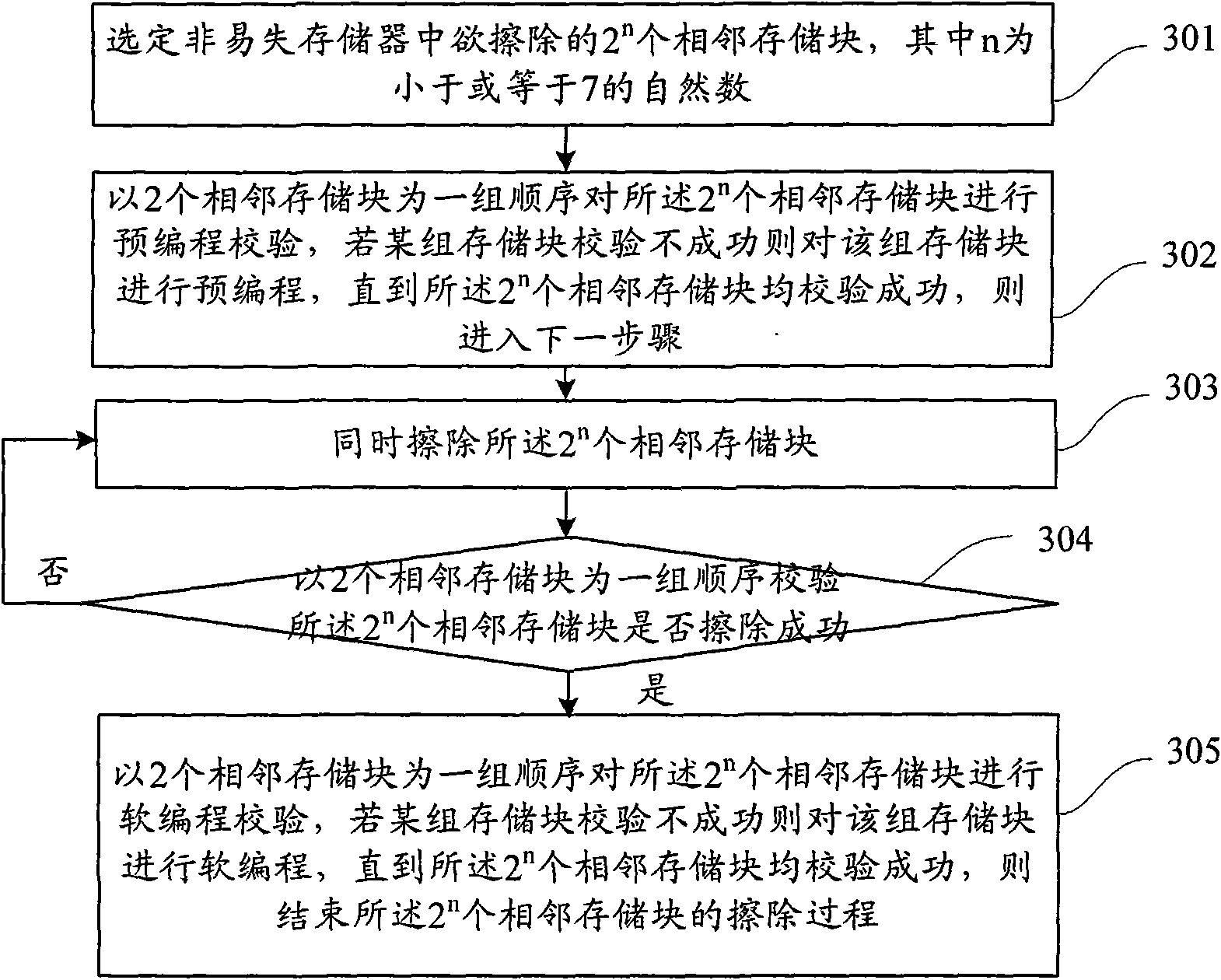

ActiveCN101923900AShorten the timeIncrease erasing speedRead-only memoriesNon-volatile memoryMemory block

The invention discloses an erasing method for a non-volatile memory. The method comprises the following steps of: selecting a target, namely, selecting 2n to-be-erased adjacent memory blocks in the non-volatile memory, wherein n is a natural number; performing pre-programming operation, namely, pre-programming the 2n adjacent memory blocks in groups; erasing, namely, simultaneously erasing the 2n adjacent memory blocks; checking the erasing, namely, checking whether the 2n adjacent memory blocks are successfully erased in groups, if so, performing soft programming operation, and otherwise, returning to the erasing step; and performing the soft programming operation, namely, performing the soft programming operation on the adjacent memory blocks in groups. The method can save erasing time and improve erasing speed and erasing efficiency.

Owner:GIGADEVICE SEMICON (BEIJING) INC

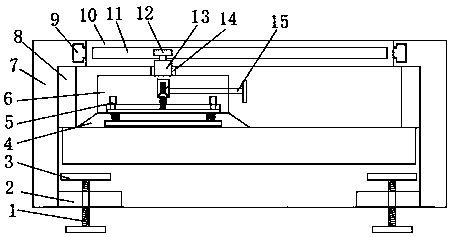

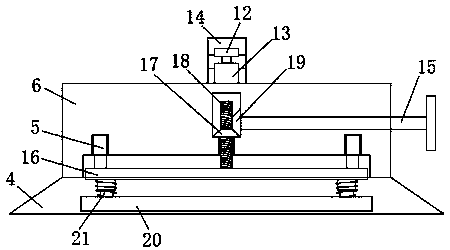

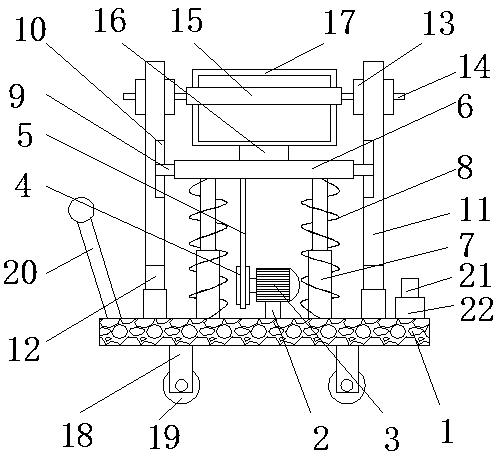

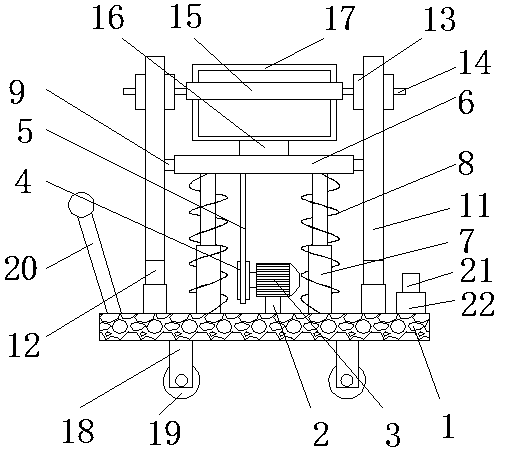

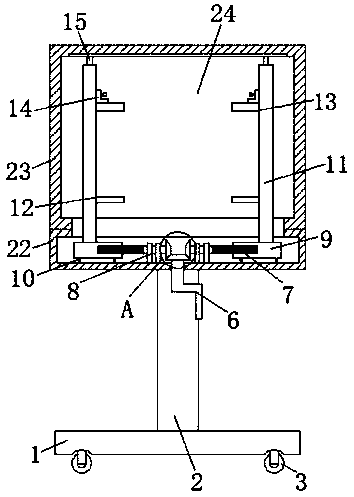

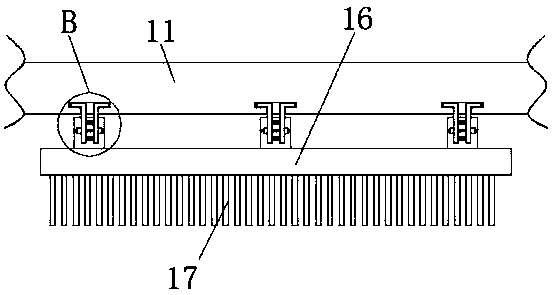

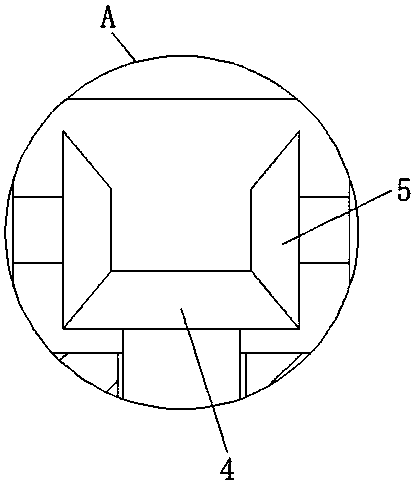

Dust removal equipment for solar cell panel

InactiveCN107774595AImprove erase efficiencySimple structurePhotovoltaicsCleaning using toolsEngineeringSolar cell

The invention discloses dust removal equipment for a solar cell panel. The dust removal equipment comprises a stander, wherein an opening is formed in the upper end of the stander in a penetration manner, first slide chutes are formed in the side walls opposite to the opening, a slide rod is arranged between the two slide chutes, and pulleys are rotatably connected to two ends of the slide rod andare connected into the two first chutes, respectively; a second slide chute is formed in the lower end of the slide rod, a cleaning device is arranged below the slide rod and comprise a cleaning head, a slide block is connected to the upper end of the cleaning head and is connected into the second slide chute in a sliding manner, a driving device is mounted at the upper end of the cleaning head,and a gear is fixedly connected to the tail end of an output shaft of the driving device; and a rack mutally meshed with the gear is arranged on the side wall of the slide rod, and a mounting slot isformed in the lower end of the cleaning head. The dust removal equipment is simple in structure, convenient to operate and high in dust removal efficiency and has a very good dust removal effect to the solar cell panel.

Owner:余金铭

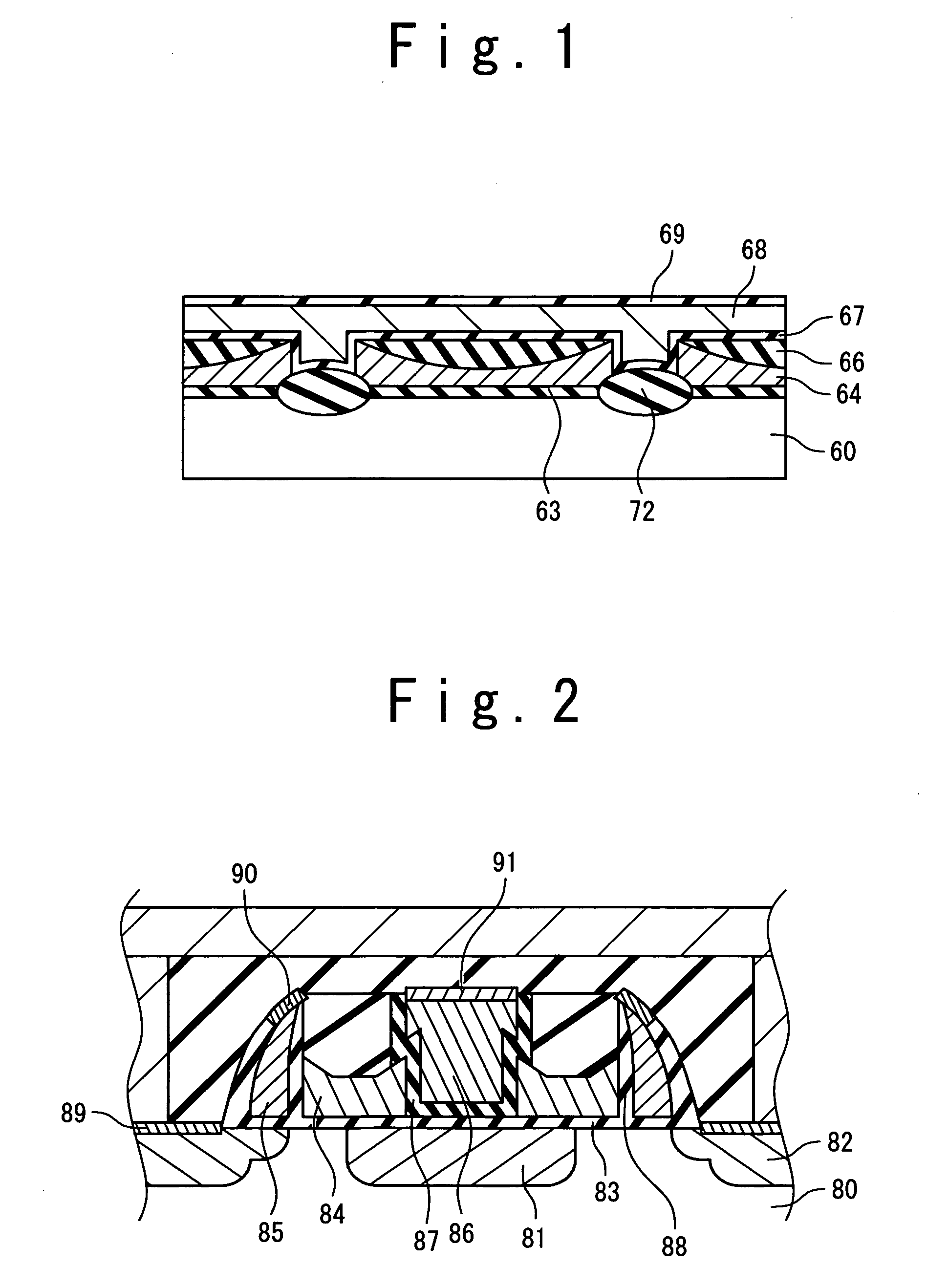

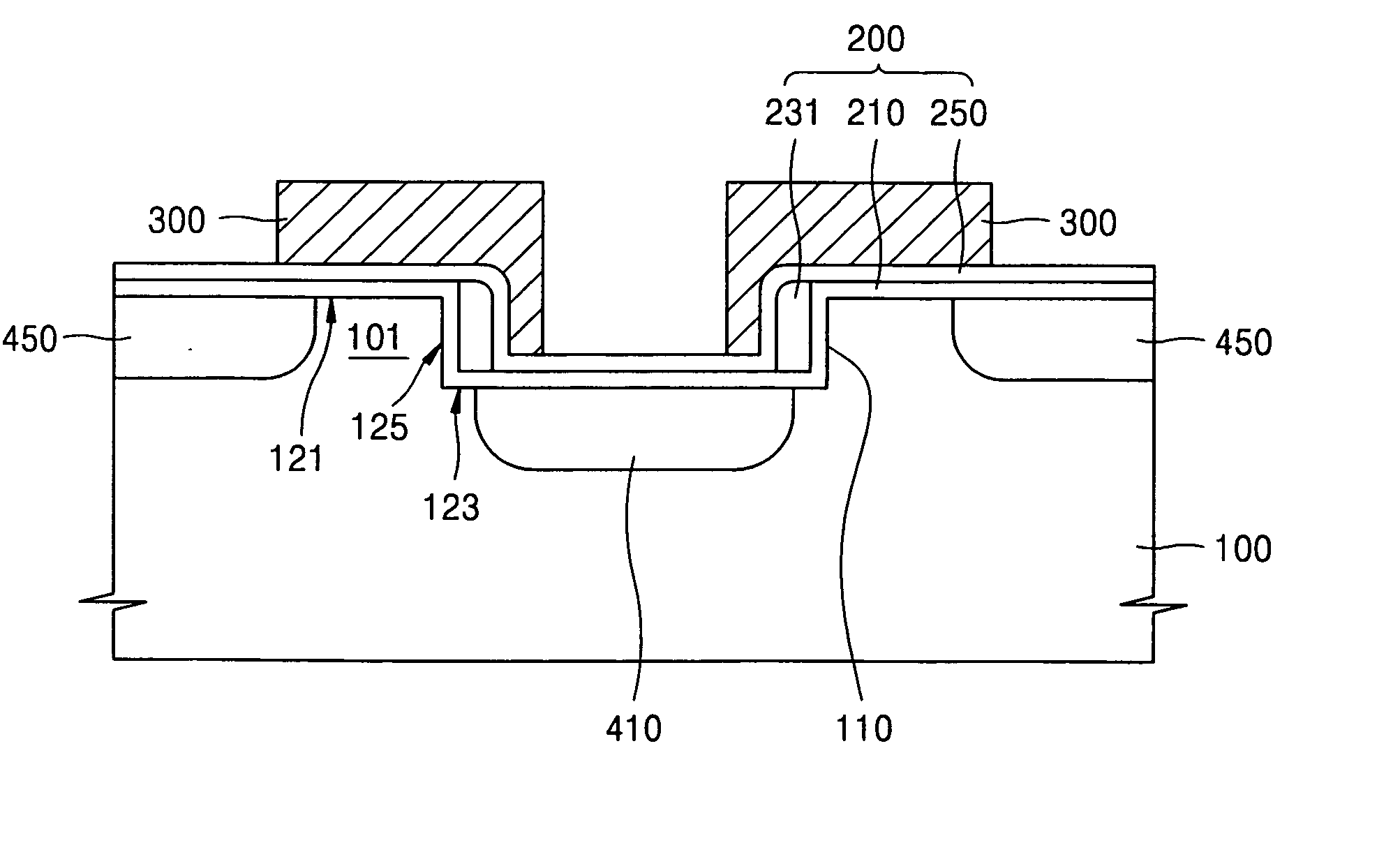

Sonos device and methods of manufacturing the same

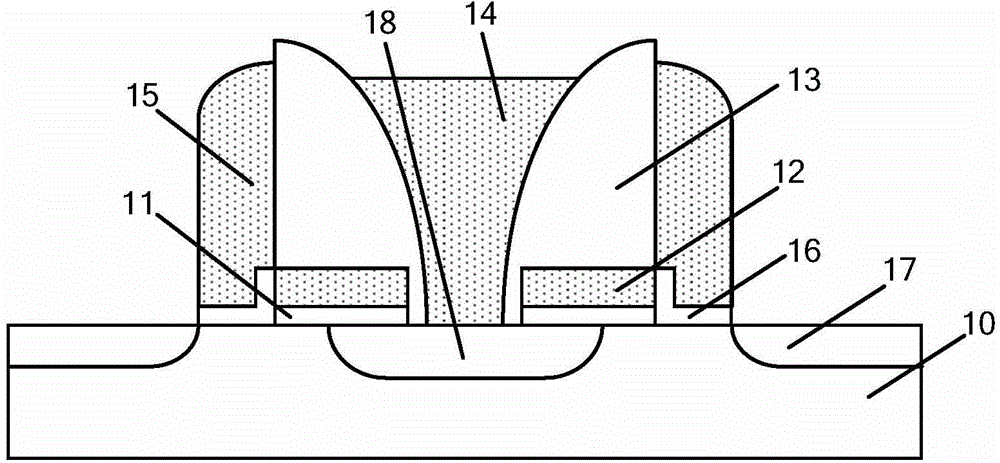

ActiveUS20050093058A1Improve erase efficiencyImprove programming efficiencyTransistorSolid-state devicesTrappingIsolation layer

Silicon-oxide-nitride-oxide-silicon (SONOS) devices and methods of manufacturing the same are provided. According to one aspect, a SONOS device includes a semiconductor substrate having a first surface, a second surface of lower elevation than the first surface, and a third surface perpendicular and between the first and second surfaces; a tunnel dielectric layer on the semiconductor substrate; a charge trapping layer in a form of a spacer on the tunnel dielectric layer on the third surface; a charge isolation layer on the tunnel dielectric layer, which covers the charge trapping layer; a gate that extends over a portion of the first surface, over a portion of the second surface, and is adjacent to a portion of the third surface of the semiconductor substrate on the charge isolation layer; a first impurity region formed below the first surface and near the gate; and a second impurity region formed below the second surface, opposite the first impurity region.

Owner:SAMSUNG ELECTRONICS CO LTD

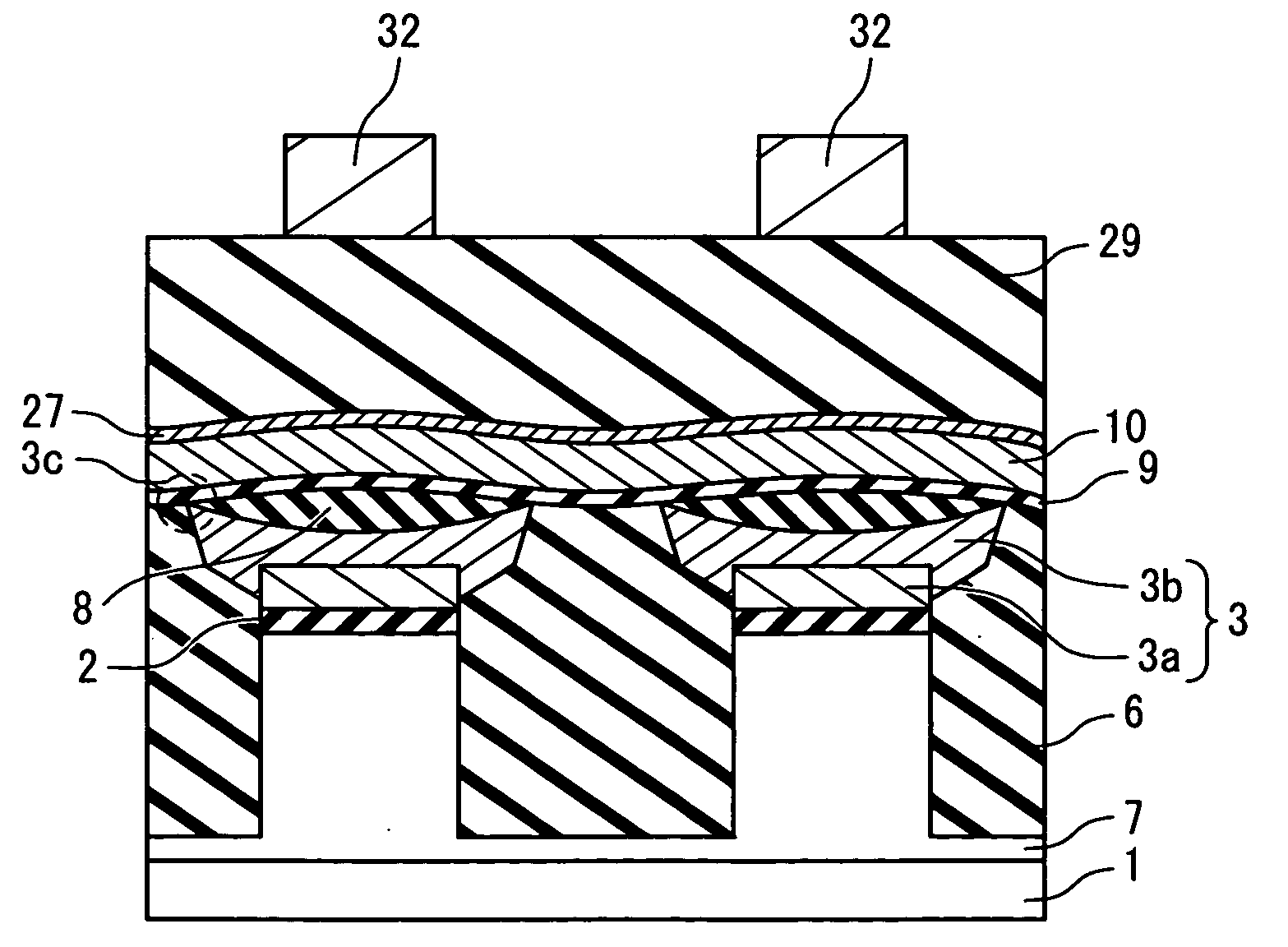

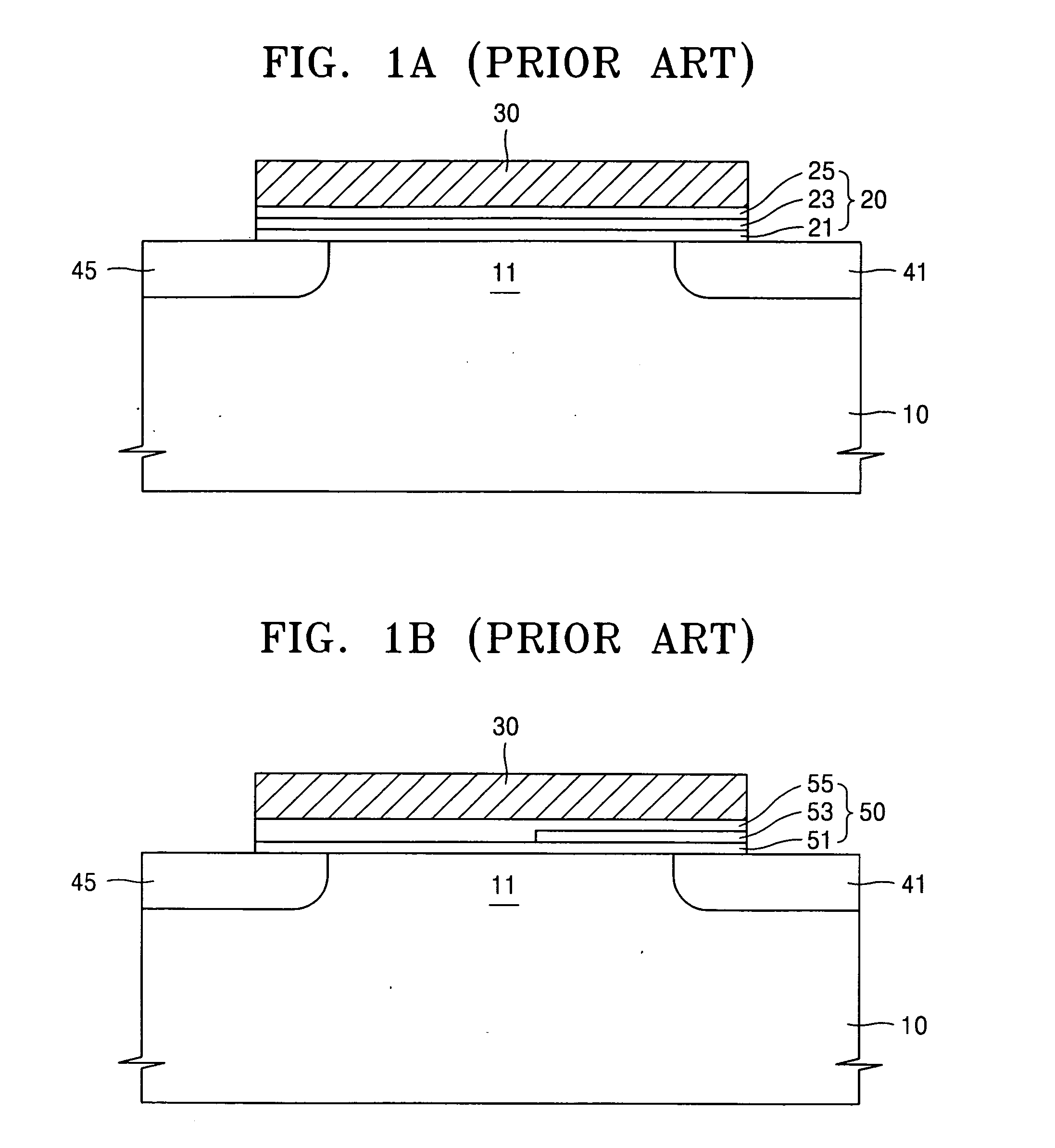

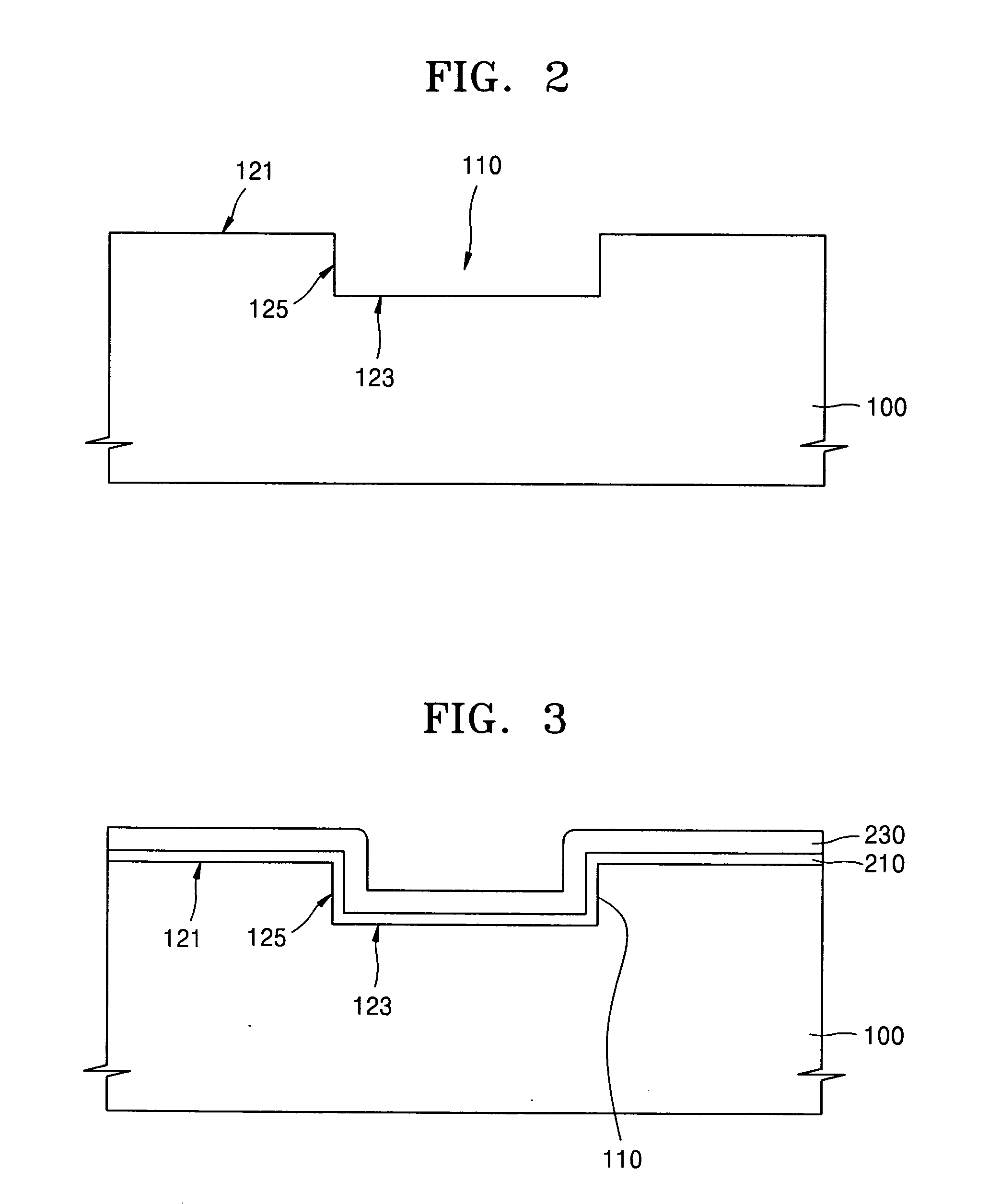

Non-volatile memory device having improved erase efficiency and method of manufacturing the same

InactiveCN1790640APrevent tunnelingImprove erase efficiencySolid-state devicesSemiconductor/solid-state device manufacturingTrappingWork function

The invention discloses a nonvolatile memory with improved erasing efficiency and a preparation method thereof. The method includes: forming a stacked structure of a tunnel dielectric layer, a charge trapping layer, a charge blocking layer, and a gate on a semiconductor substrate; and post-processing the gate using oxygen or CF4 plasma or ion implantation to increase the formation of The work function of the gate material. According to the present invention, since the work function of the metal layer forming the gate can also be increased, electron backtunneling during an erase operation can be suppressed.

Owner:SAMSUNG ELECTRONICS CO LTD

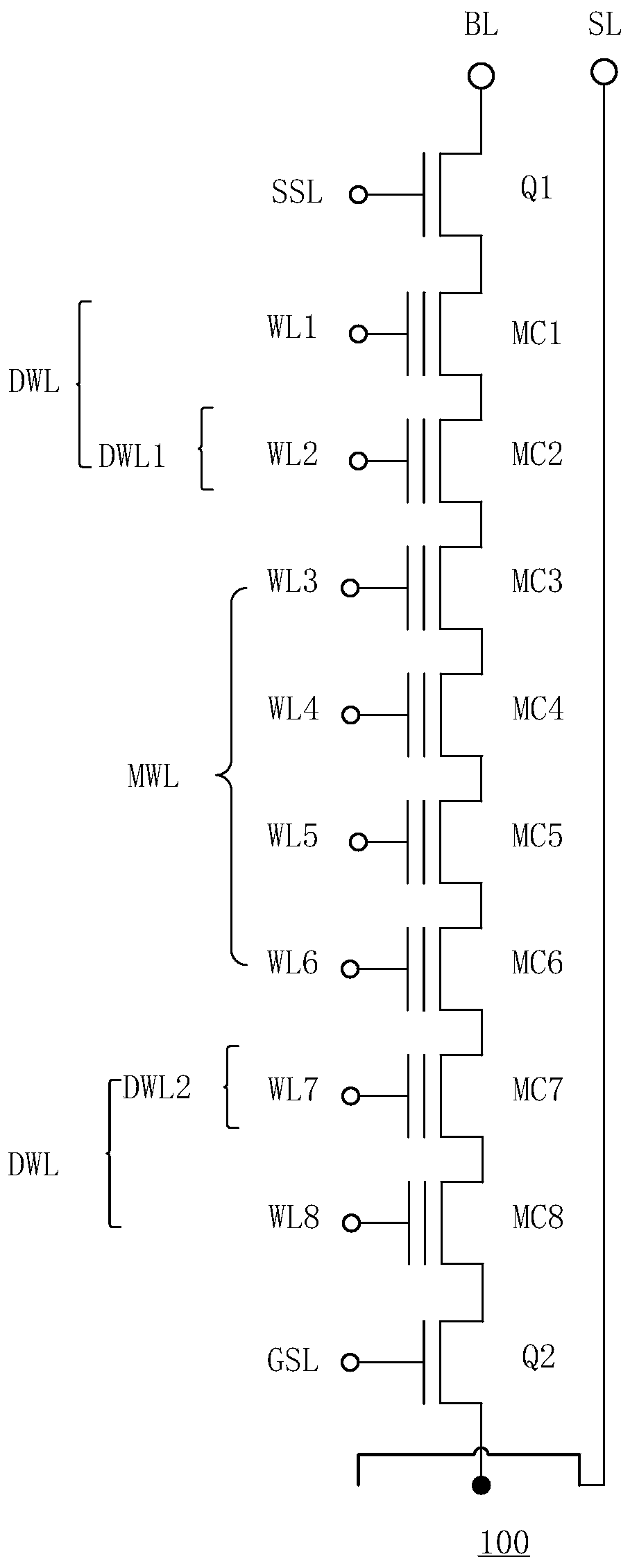

A 3D memory device and a data operation method thereof

ActiveCN109949835AImprove reliabilityImprove erase efficiencyRead-only memoriesComputer architectureData operations

The invention discloses a data operation method of a 3D storage device. The 3D memory device has a plurality of memory cell strings arranged in a direction perpendicular to a substrate, each memory cell string including a first select transistor, a first dummy memory cell, a plurality of main memory cells, a second dummy memory cell, and a second select transistor, including: receiving an erase instruction; executing an erase operation on the first pseudo storage unit, the plurality of main storage units and the second pseudo storage unit according to the erase instruction; verifying whether the plurality of main storage units are erased successfully or not after the erase operation is finished; when the plurality of main storage units are erased successfully, receiving a programming instruction; and executing programming operation on the first pseudo storage unit and the second pseudo storage unit according to the programming instruction. The pseudo storage unit and the storage unit are erased at the same time, and then the pseudo storage unit is programmed, so that the erasure efficiency of the edge storage unit is improved, the erasure frequency is reduced, and the reliability of the storage unit is improved.

Owner:YANGTZE MEMORY TECH CO LTD

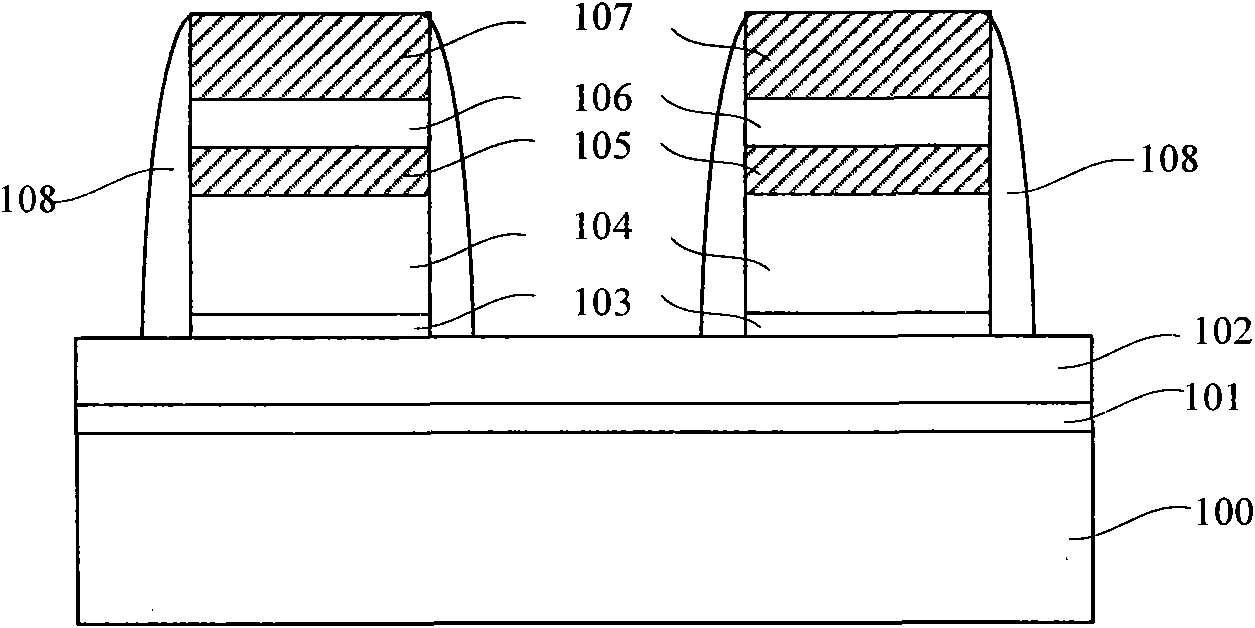

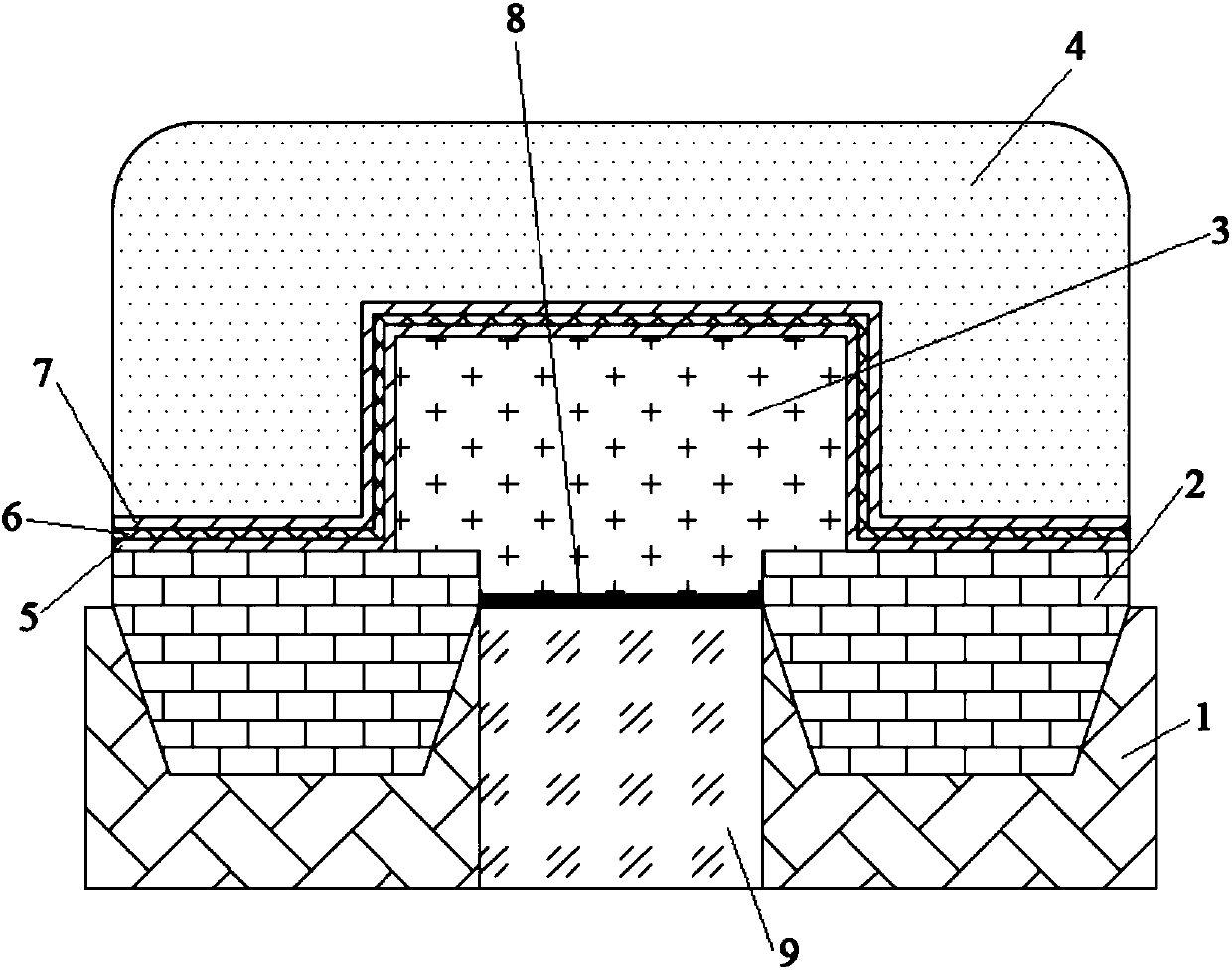

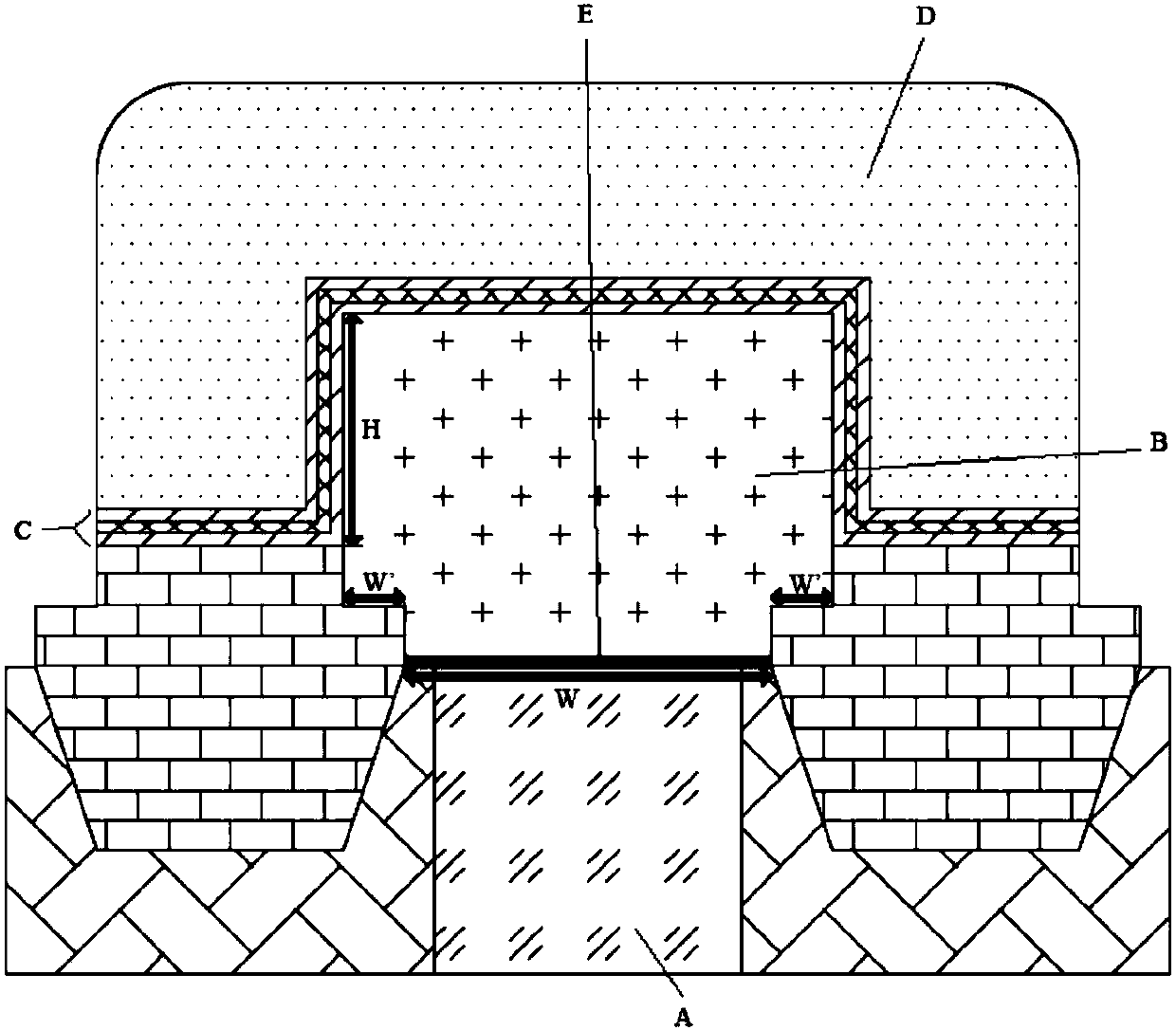

Method for improving efficiency of erasing floating gate

ActiveCN101882576AEnhanced electric fieldReduce the erase voltageSemiconductor/solid-state device manufacturingSilicon oxidePhotoresist

The invention discloses a method for improving the efficiency of erasing a floating gate, which comprises the following steps: sequentially forming a floating gate (FG) oxide layer, a FG polycrystalline silicon layer, an oxide layer-nitride layer-oxide layer (ONO) dielectric layer, a control gate (CG) polycrystalline silicon layer, a CG silicon nitride layer, a CG silicon oxide layer and a CG silicon nitride hard mask layer on a semiconductor substrate; coating photoresist on the CG silicon nitride hard mask layer, and patterning the photoresist; taking the patterned photoresist as a mask, and sequentially etching the CG silicon nitride hard mask layer, the CG silicon oxide layer, the CG silicon nitride layer, the CG polycrystalline silicon layer and the ONO dielectric layer to form two CGs; forming a CG side wall layer at two sides of each CG; forming a sacrificial layer at the outside of each CG side wall layer; taking the CG side wall layers, the sacrificial layer and the CG as masks, and etching the FG polycrystalline silicon layer to form FG; removing the sacrificial layer; and sequentially forming the oxide layer and depositing the polycrystalline silicon film outside the CG side wall layer and the FG, and finally forming the erasing gate EG by the polycrystalline silicon film. The method can effectively improve the efficiency of erasing the floating gate.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Nonvolatile memory cell and fabrication method thereof

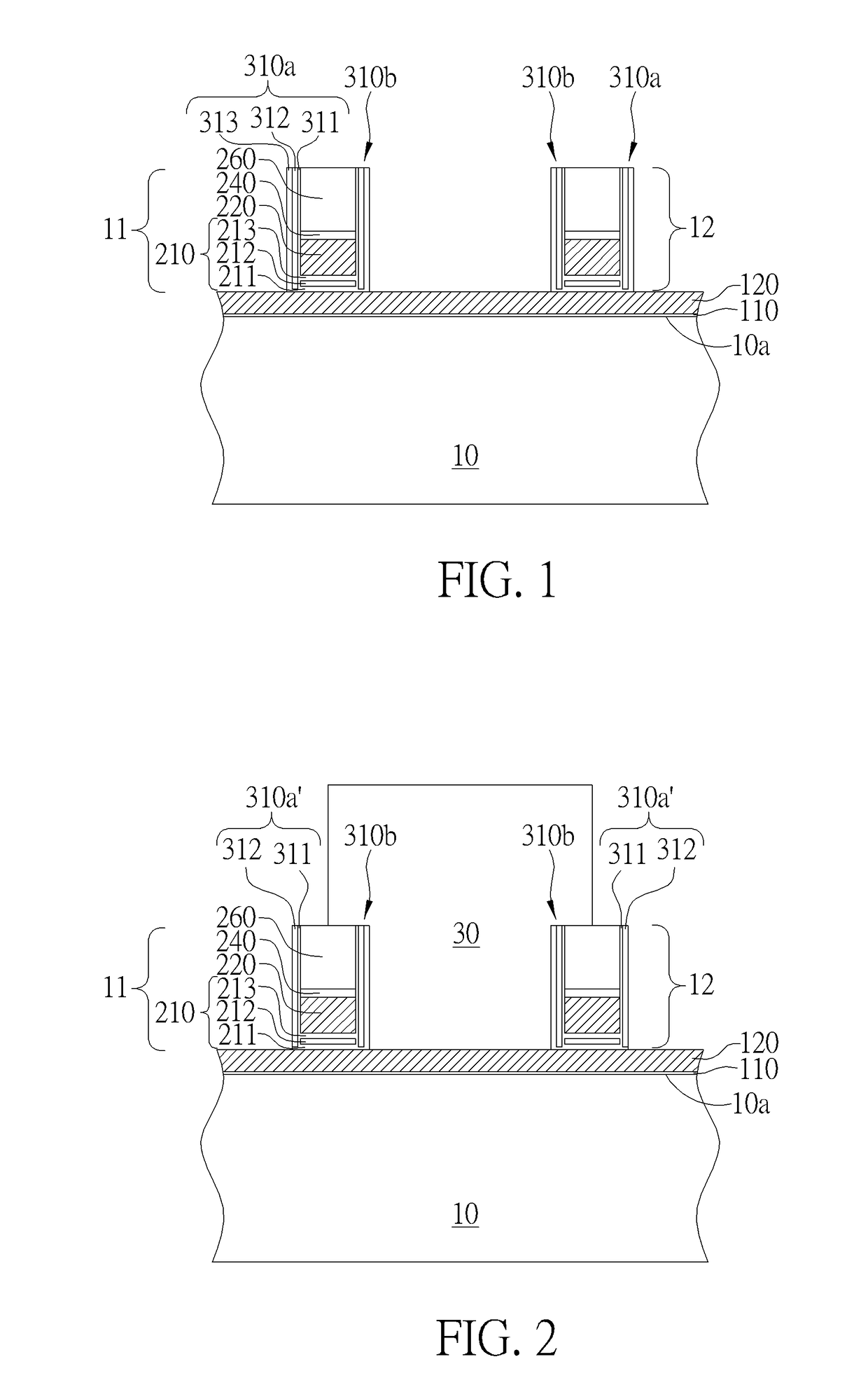

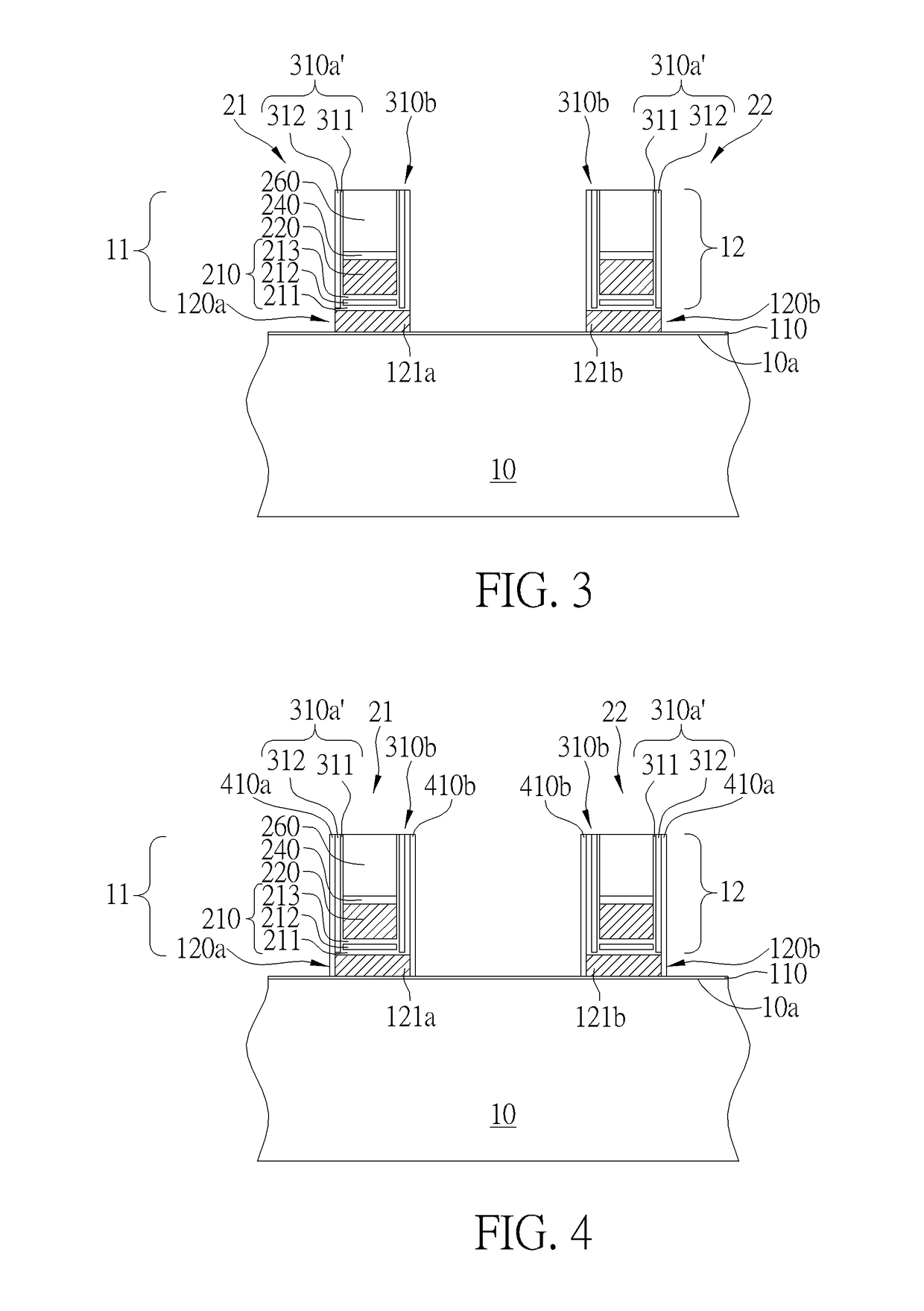

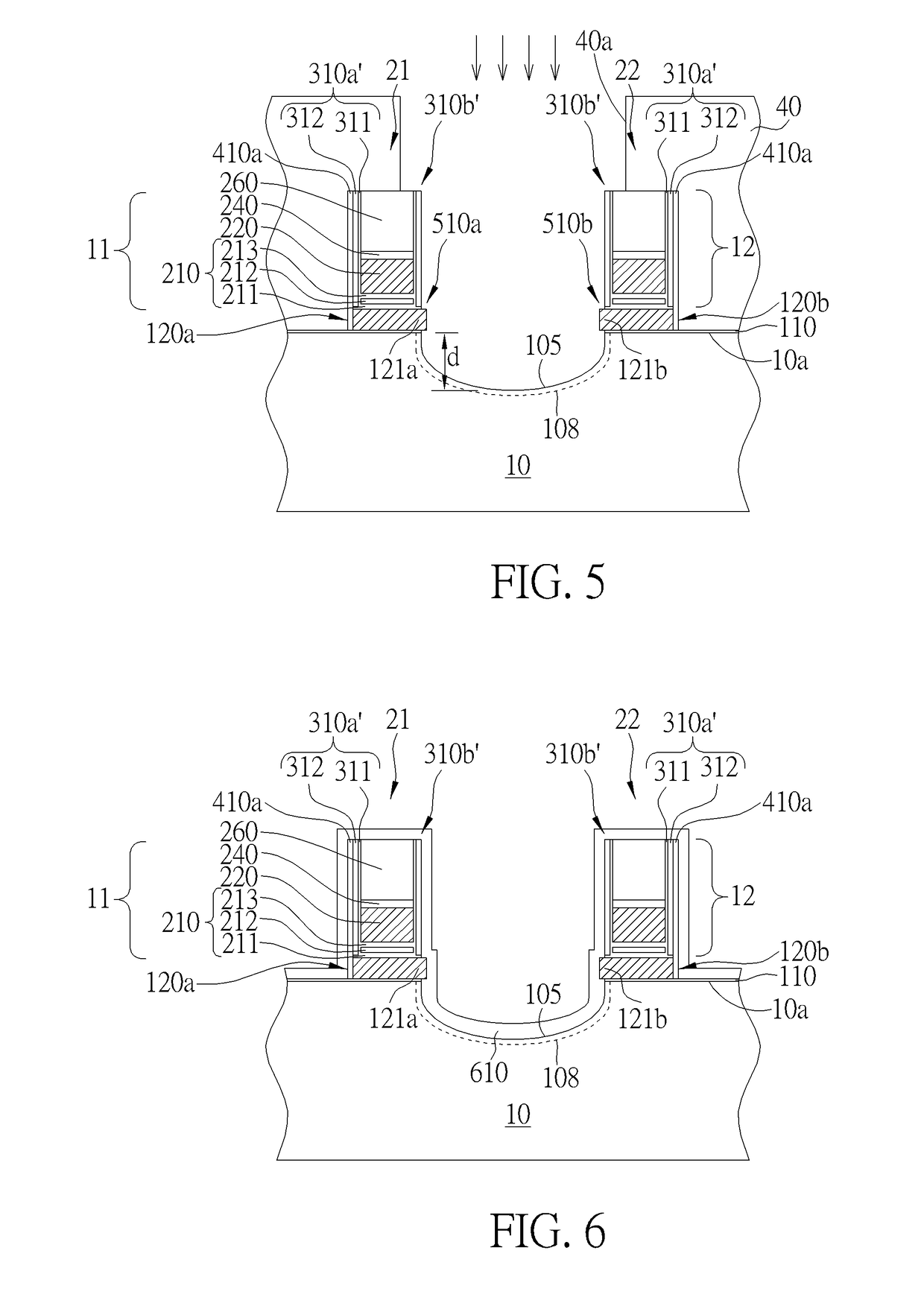

ActiveUS20180366478A1Improve erase efficiencyTransistorSolid-state devicesEngineeringNon-volatile memory

A nonvolatile memory cell includes a substrate having a drain region, a source region, and a channel region between the drain region and the source region. A floating gate and a select gate are disposed on the channel region. A control gate is disposed on the floating gate. An erase gate is disposed on the source region. The erase gate includes a lower end portion that extends into a major surface of the substrate.

Owner:UNITED MICROELECTRONICS CORP

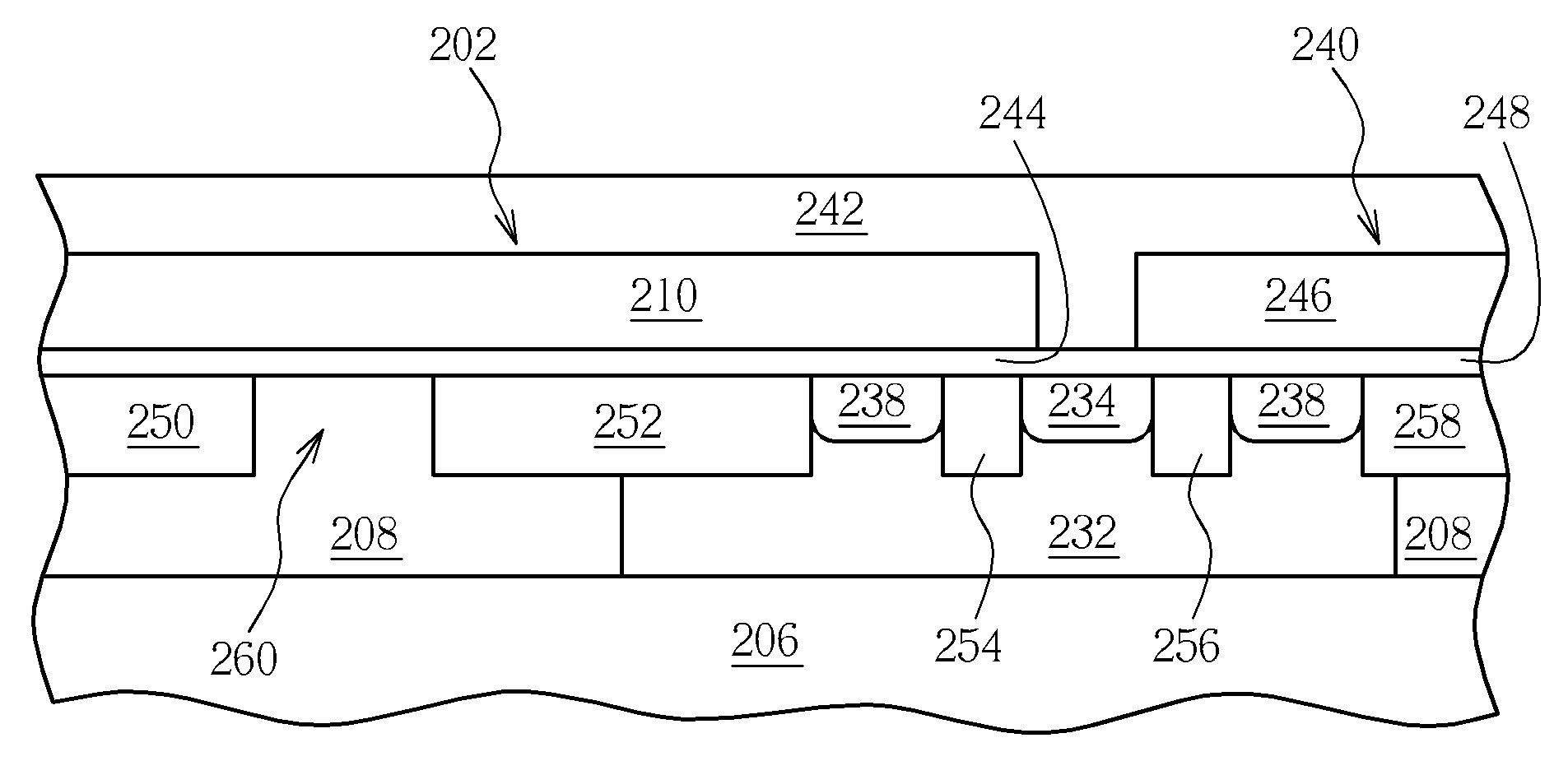

Flash memory unit and formation method thereof

ActiveCN104157616ASmall sizeReduce overlap areaTransistorSolid-state devicesDielectric layerComputer engineering

The invention discloses a flash memory unit and a formation method thereof. The flash memory unit comprises a substrate, a floating gate, a source line doping area, a second dielectric layer, a control gate, a first side wall, a third dielectric layer, word lines and a bit line doping area, wherein the surface of the substrate is provided with a first dielectric layer, the floating gate is located on the surface of the first dielectric layer, a second opening is formed inside the floating gate, the source line doping area is located at the position, at the bottom of the second opening, inside the substrate, the second dielectric layer is located on the surface of the floating gate and arranged on the surface of the position, at the bottom of the second opening, of the substrate, the control gate is located on the surface of the second dielectric layer, the first side wall is located on the surface of the side wall of the control gate, the third dielectric layer is located on the surface of the side wall of the floating gate, the word lines are located on the two sides of the first side wall, the two sides of the control gate, the two sides of the floating gate and the two sides of the third dielectric layer, and the bit line doping area is located inside the position, on the two sides of the first side wall, the two sides of the control gate, the two sides of the floating gate and the two sides of the word lines, of the substrate. The size of the formed flash memory unit is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

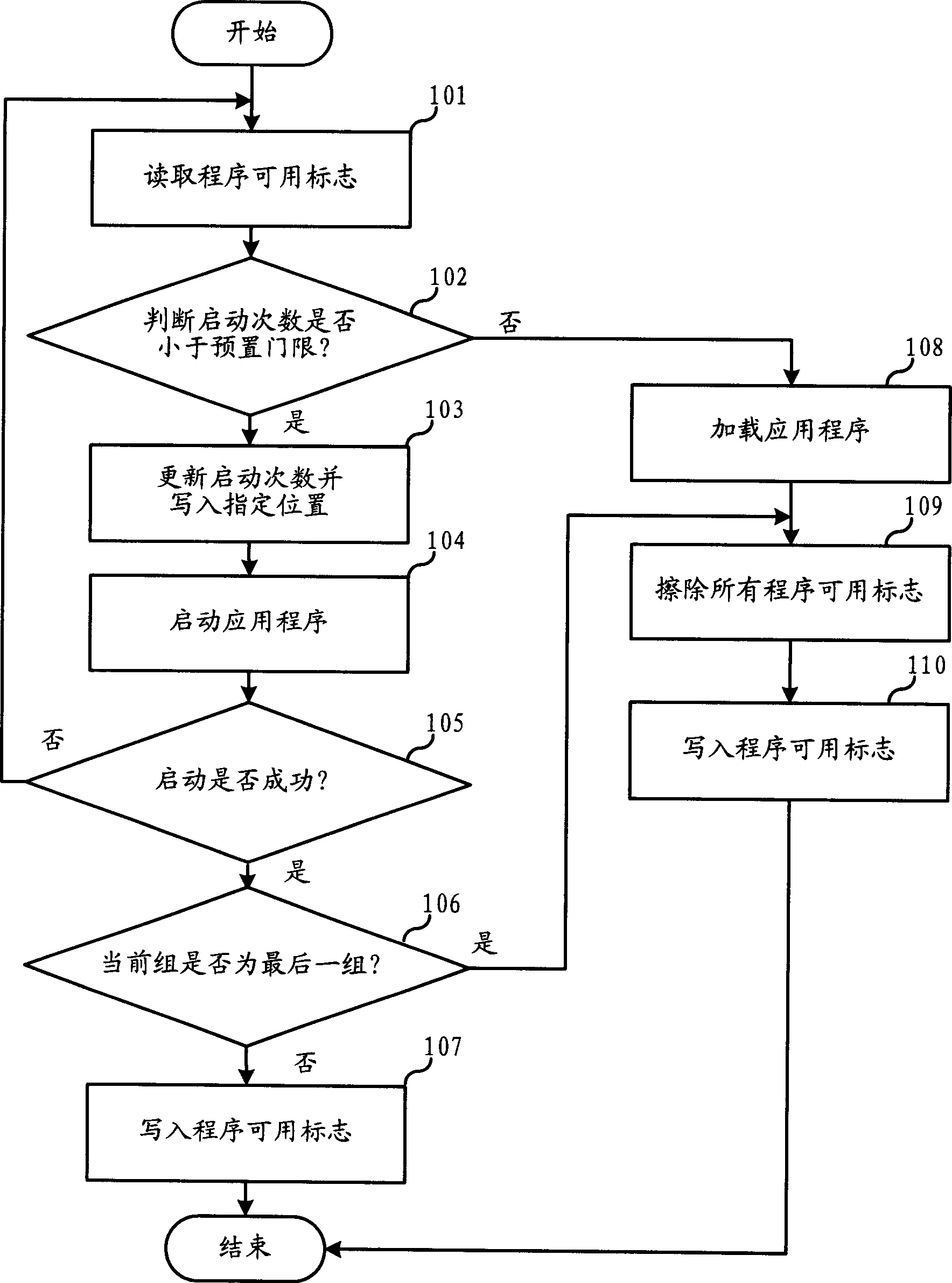

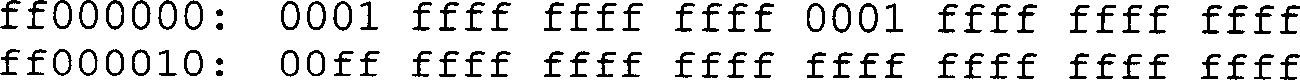

Starting method of device

InactiveCN1858703AFast startupImprove securityProgram loading/initiatingStart up timeArray data structure

This invention relates to an electronic device containing control programs and discloses a starting up method for the device, which designs multiple tuples and fetches the program available marks written when starting up last time from the last written position, if the start up times exceed the threshold, then the programs are loaded again, otherwise the program available mark containing the counting information of this time is written in the next un-written position in the tuples, if the start up is successful, then the successful program available mark is written in the first position of the next tuple, if the preset sets are full or the program is re-loaded, then the written ones are erased.

Owner:HUAWEI TECH CO LTD

Flash memory unit structure with high coupling ratio and preparation method thereof

InactiveCN107946370AImprove the coupling rateReduce capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceCoupling ratio

The present invention relates to a flash memory unit structure with a high coupling ratio and a preparation method thereof. The flash memory unit structure comprises: a semiconductor substrate, wherein the semiconductor substrate comprises two shallow trench isolations and an active area, and the active area is located in the semiconductor substrate between the two shallow trench isolations; a tunneling oxide layer; a floating gate; a dielectric layer; and a control gate, wherein the dimensions of the top portions of the two shallow trench isolations are equal to the dimension of the top portion of the active area, and the dimension of the tunneling oxide layer is equal to the dimension of the top portion of the active area. A silicon nitride reduction resistance amount prior to depositionof the shallow trench isolations is increased to increase the dimensions of the top portions of the shallow trench isolations; and moreover, in the subsequent technology process, the top portions ofthe shallow trench isolations can be consumed, the dimensions of the top portions of the shallow trench isolations after consumption are equal to the actual dimension of the top portion of the activearea to allow the width of the bottom portion of the floating gate to be equal to the dimension of the top portion of the active layer when a subsequent floating gate process is performed so as to reduce the capacitance of the floating gate to the substrate and increase the coupling ratio of a flash unit.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

LED display screen with dust removal function

InactiveCN109903683AWith dust removal functionSlide up and down smoothlyCleaning using toolsIdentification meansSurface displayLED display

The invention discloses an LED display screen with the dust removal function. The LED display screen comprises a base, the upper surface of the base is fixedly connected with the bottom of a first support rod, the top of the first support rod is fixedly connected with the lower surface of the body of a motor, the output shaft of the motor is fixedly connected with a take-up reel, the outer surfaceof the take-up reel is fixedly connected with the lower surface of a movable plate, two telescopic rods are arranged on the upper surface of the base, and tops of the telescopic rods are fixedly connected with the lower surface of the movable plate. The LED display screen has the advantages that the operation of a control panel makes the motor to rotate reversely when dust cloth moves to the lower surface of an LED display screen body, dust on the surface of the LED surface display screen is erased through the dust cloth lapped with the LED display screen body, the dust on the surface of theLED display screen body is mechanically erased by reciprocating actions, labor is saved, and the erasing efficiency is improved.

Owner:西安谷德电子科技有限公司

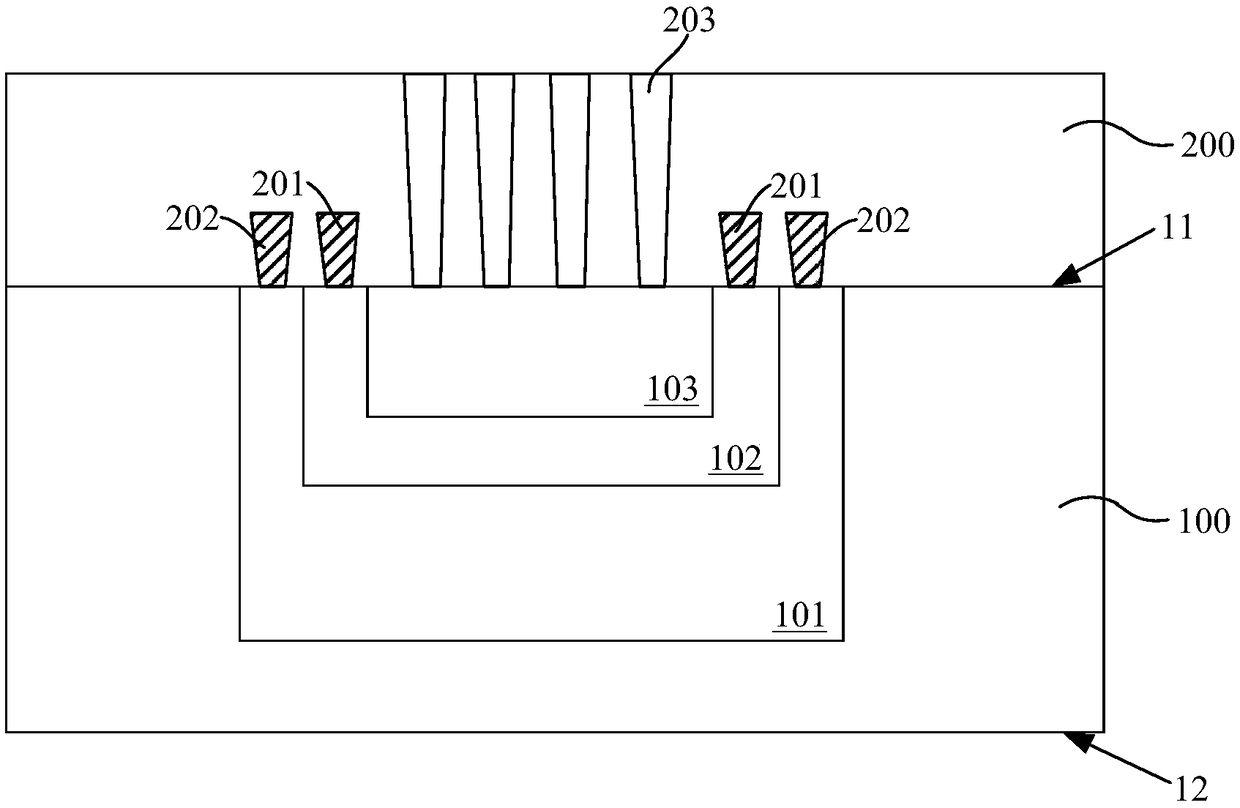

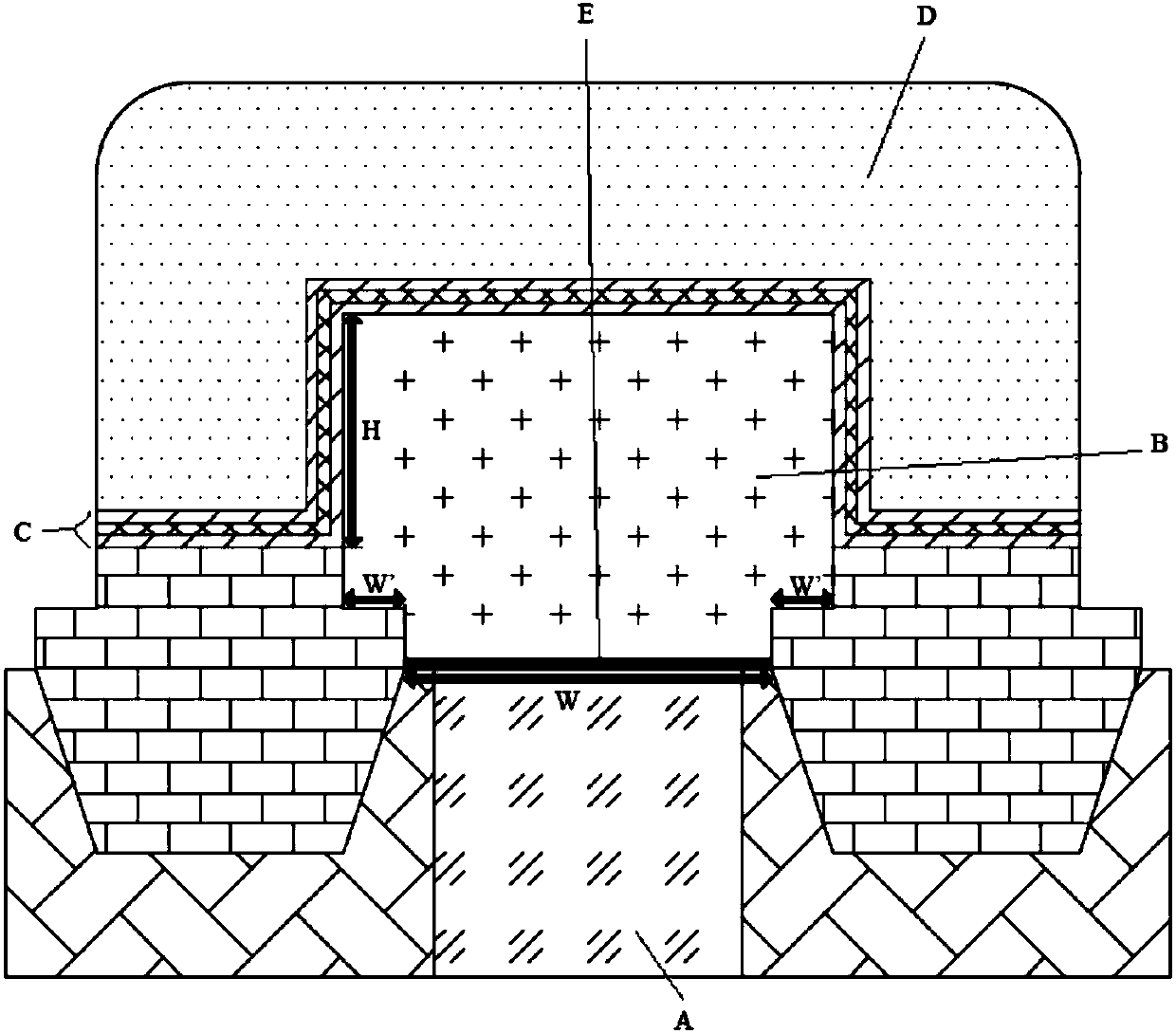

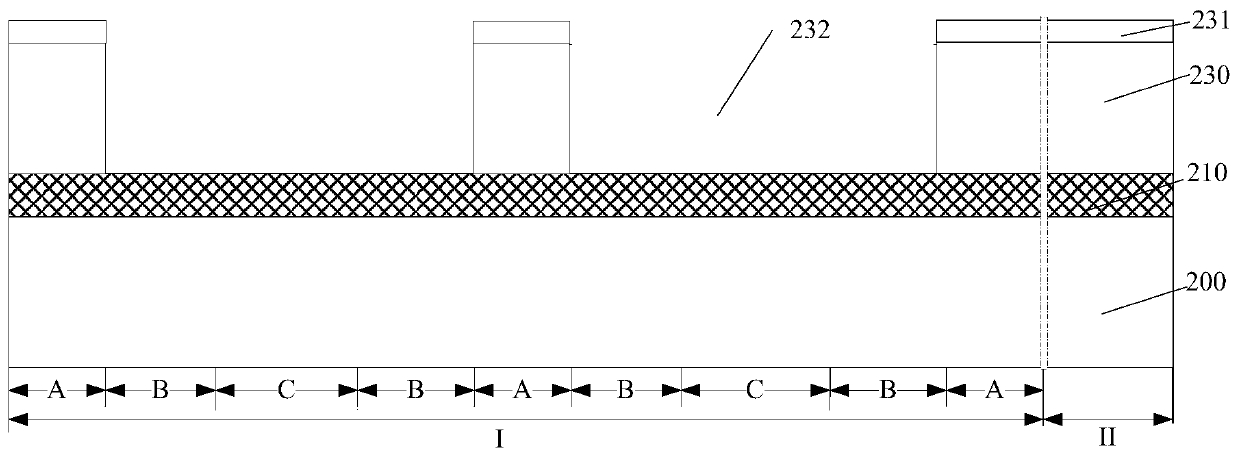

Memory and formation method thereof

ActiveCN109712981ASimple processReduced process flowSolid-state devicesSemiconductor devicesBit lineDielectric layer

A memory and a formation method thereof are disclosed. The method includes the following steps: a substrate is provided, the substrate includes erasure regions, floating gate regions and word line bitline regions, wherein the floating gate regions are located on both sides of the erasure regions, and the word line bit line regions are located on both sides of the erasure regions and the floatinggate regions; a floating grid electrode structure membrane and a dielectric layer located on the floating grid electrode structure membrane are formed on the substrate, and a first opening exposing the floating grid electrode structure membrane of the floating gate regions and the word line bit line regions are disposed in the dielectric layer; a first side wall is formed on the side wall of the first opening; a control grid electrode membrane is formed on the bottom of the first opening; a second side wall is formed on the side wall of the first side wall; the control grid electrode membraneand the floating grid electrode structure membrane exposed by the first side wall, the second side wall, and the dielectric layer are removed to form a floating gate structure layer, a control grid electrode layer and a second opening; the dielectric layer and the floating gate structure layer on the erasure regions are removed to form a third opening and a floating grid electrode structure; and an erasure grid electrode structure is formed in the third opening. The method enables the production efficiency of the memory to be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

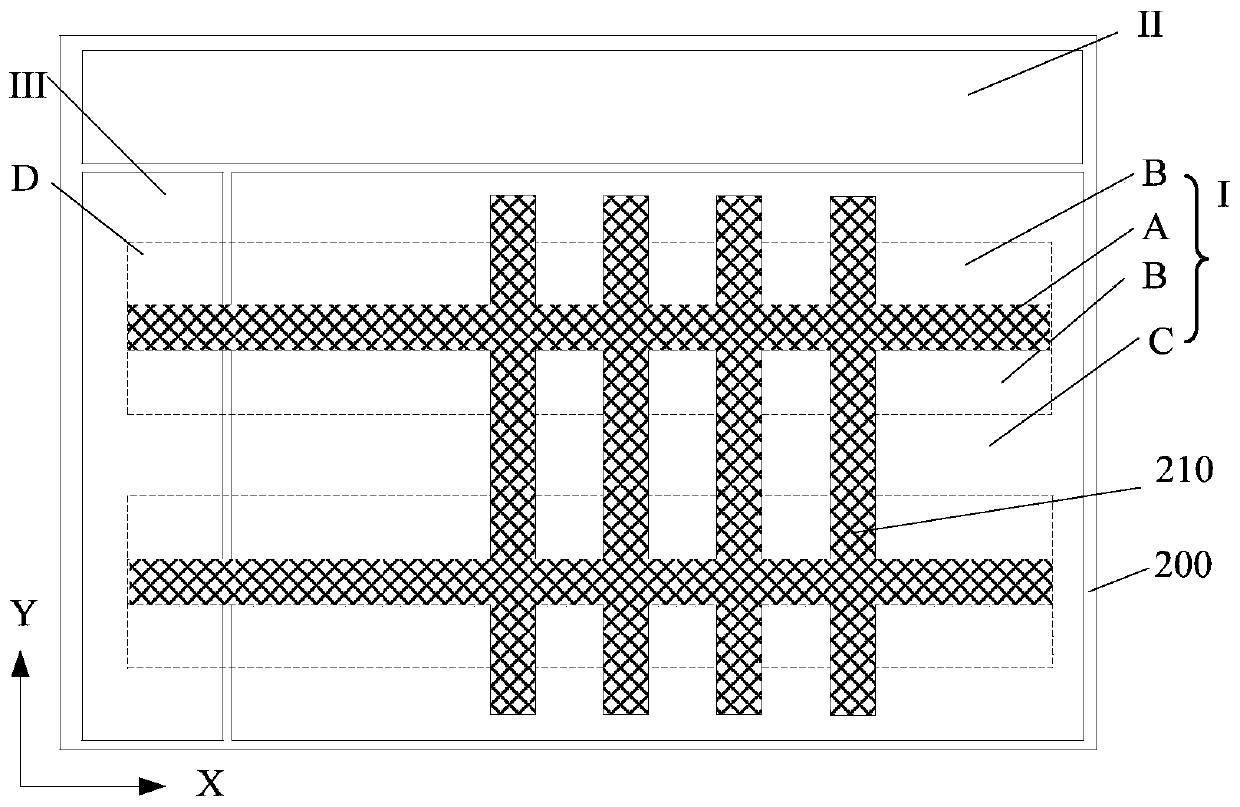

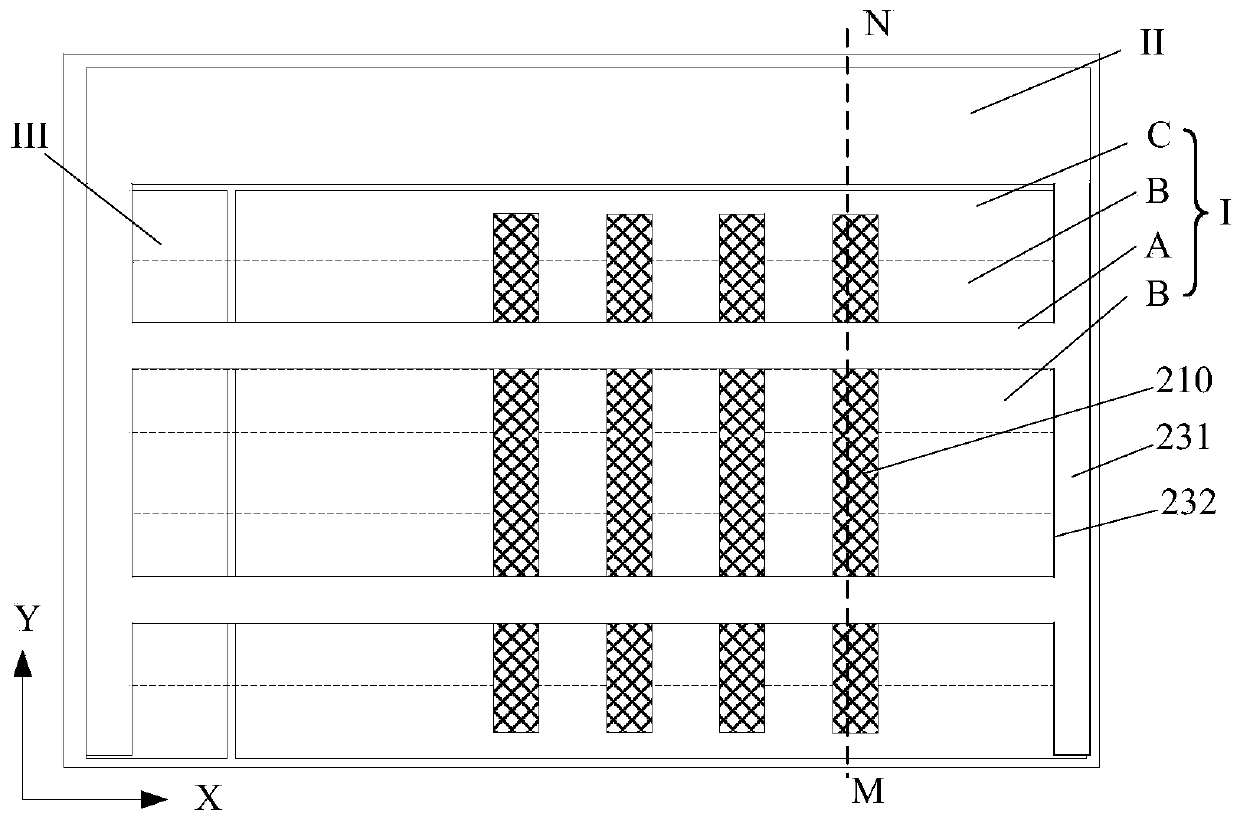

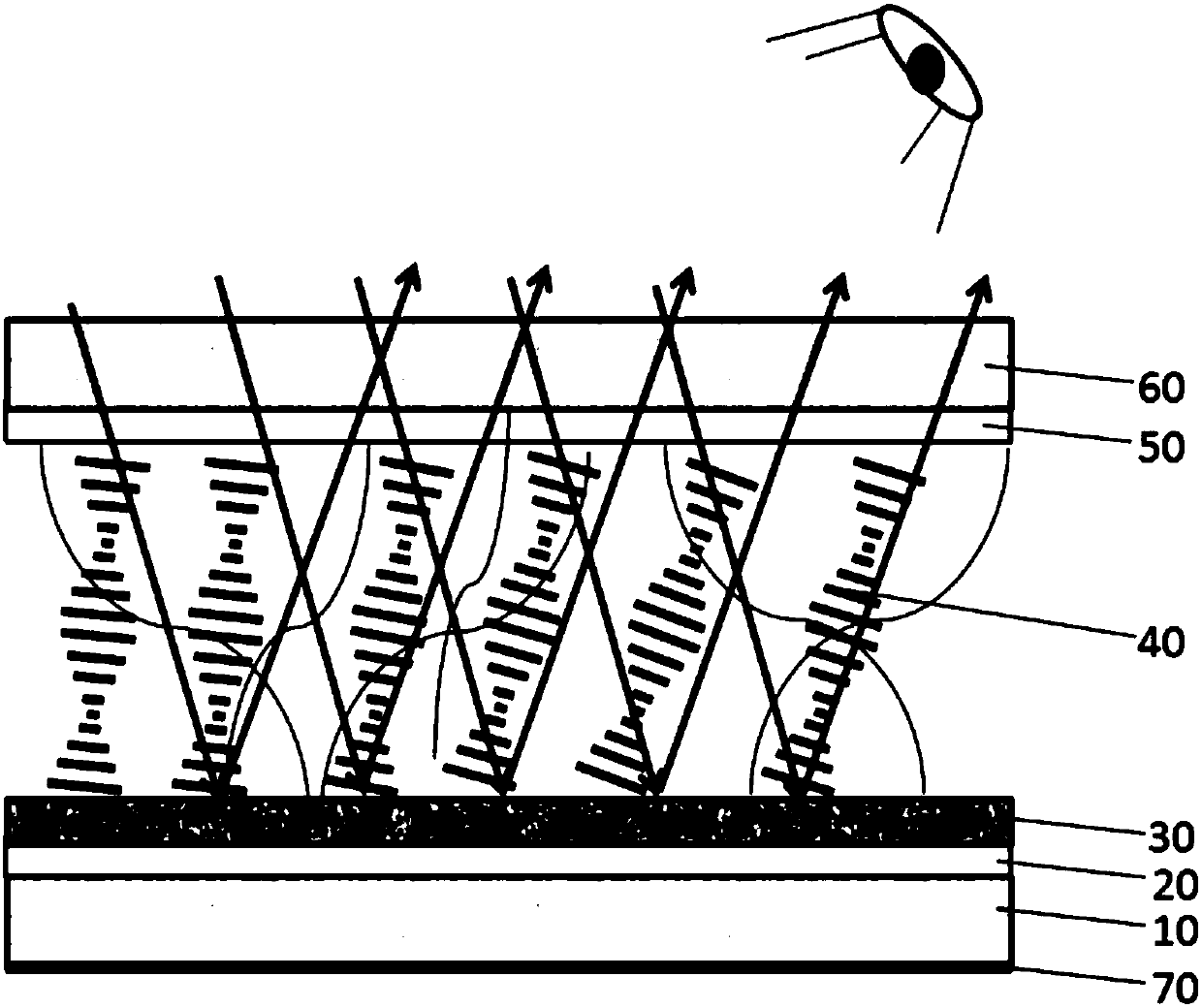

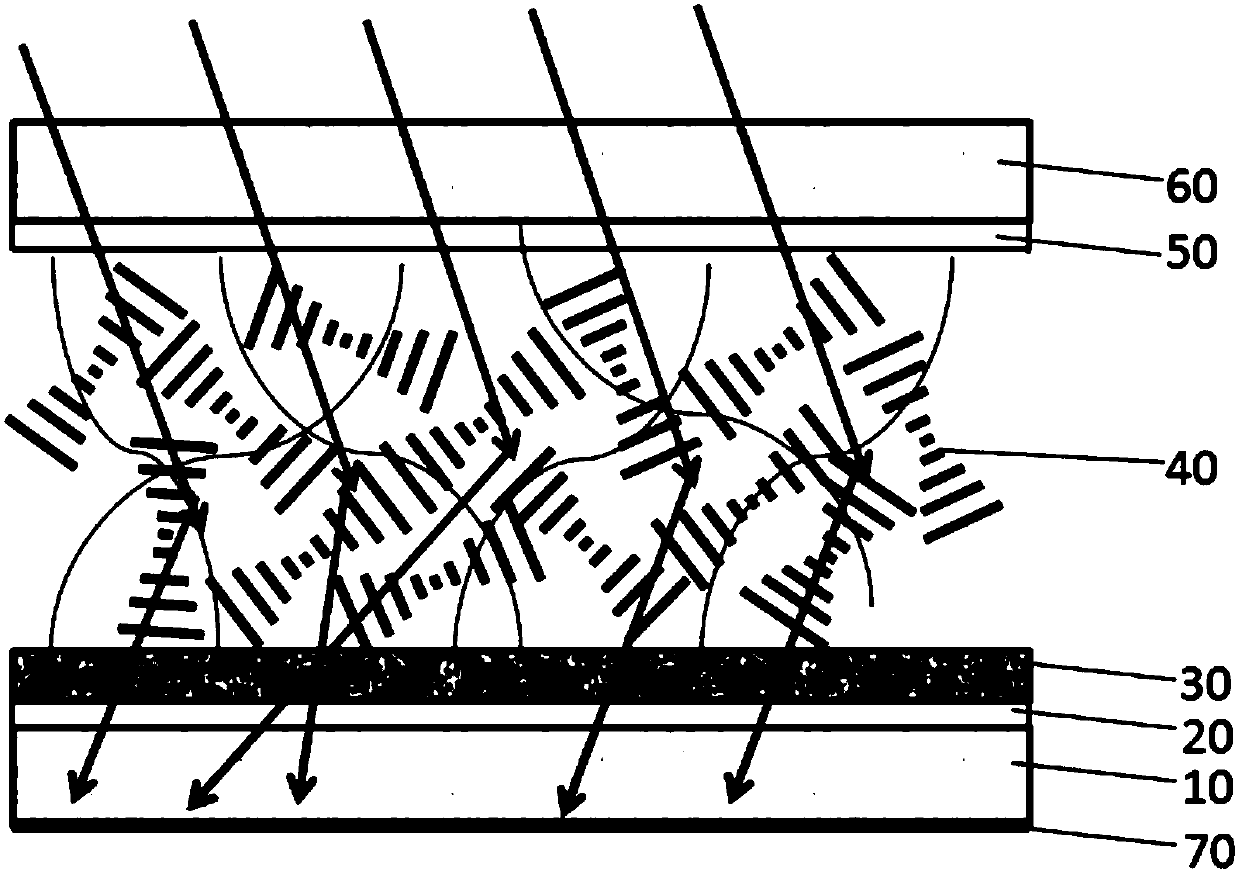

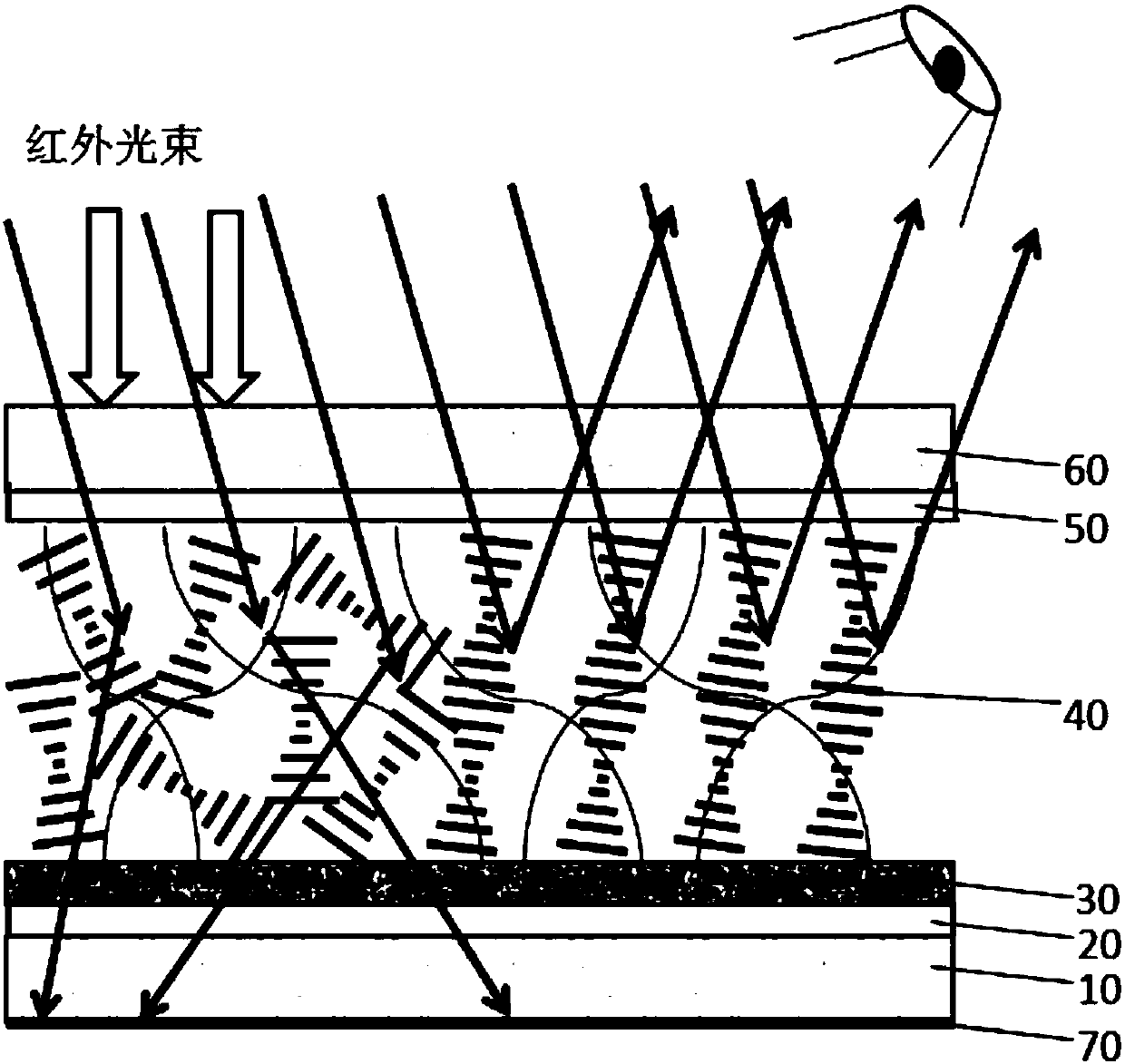

Partial erasing liquid-crystal handwriting board device and forming method thereof

ActiveCN109932834AFast implementation of partial erasurePartial Erase ImplementationNon-linear opticsInput/output processes for data processingInfraredBasic dimension

The invention discloses a partial erasing liquid-crystal handwriting board device and a forming method thereof. The partial erasing liquid-crystal handwriting board device comprises a liquid-crystal handwriting board and an erasing pen. The liquid-crystal handwriting board includes a substrate, a first conductive layer, an infrared absorbing material layer, a liquid crystal layer, a second conductive layer, and a flexible transparent substrate. The first conductive layer and the infrared absorbing material layer are arranged on the substrate in a basic dimension consistence manner. The first conductive layer and the second conductive layer are transparent conductive layers; the second conductive layer is formed on the flexible transparent substrate; and the substrate and the flexible transparent substrate jointly clamp the liquid crystal layer to form a liquid crystal box of the liquid-crystal handwriting board. The erasing pen includes an infrared emitting light source and a control switch. According to the partial erasing liquid-crystal handwriting board device, the partial erasing is realized by means of non-contact photothermal conversion; the erasing efficiency is high; the device is convenient to use; and energy-saving and low-cost effects are realized.

Owner:JIANGSU JICUI INTELLIGENT LCD TECH CO LTD

Method for manufacturing split gate flash by reducing writing interference

ActiveCN102376652AReduce doping concentrationReduce concentration differenceSemiconductor/solid-state device manufacturingIon beamEngineering

The invention discloses a method for manufacturing a split gate flash by reducing writing interference. After a control gate, a floating gate, an erasing gate and a word line are formed on a semiconductor substrate, lightly-doped ions are implanted; and the iron implantation comprises a vertically lightly doping step and a pocket ion implantation step, wherein in the pocket ion implantation step, an ion beam is injected into the semiconductor substrate below the word line at an inclined angle. By the method for manufacturing the split gate flash, an ion implantation step which is used for defining threshold value voltage of a flash unit in the prior art is eliminated; after a step of forming the word line, the pocket ion implantation step is added to reduce the doping concentration of a substrate area below a clearance between the word line and the floating gate, so that the difference of the doping concentration of the substrate area below the clearance between the word line and the floating gate and the doping concentration between the concentrations of channels below the floating gate is reduced; therefore, a writing unit which is not ought to have a writing change is prevented from having the writing change, and the writing interference is effectively avoided.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Method for manufacturing flash memory device

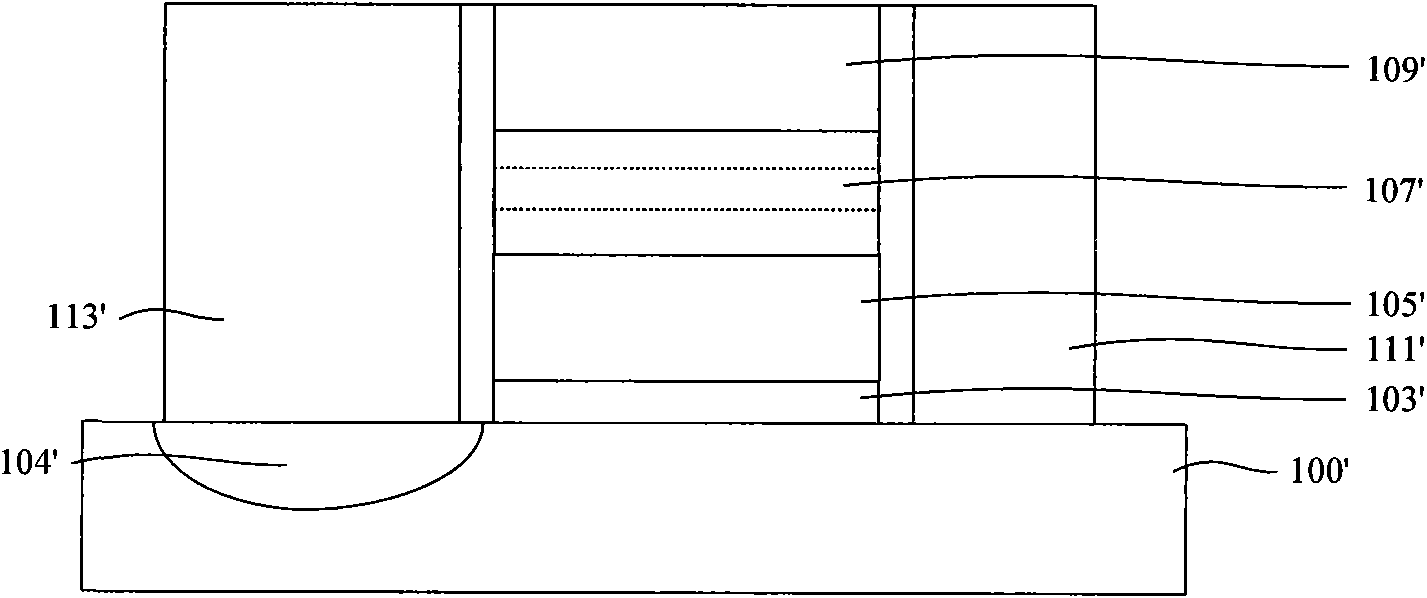

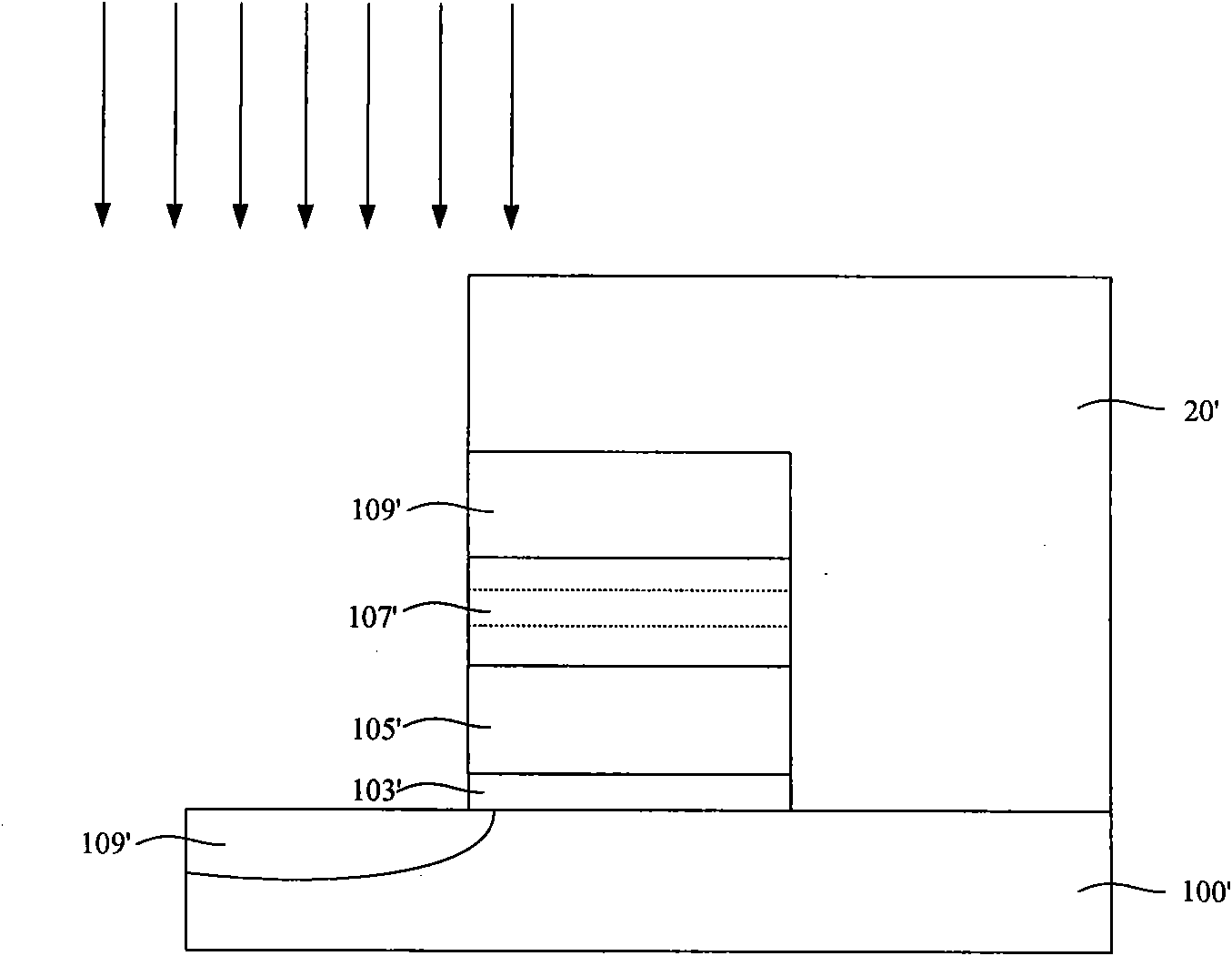

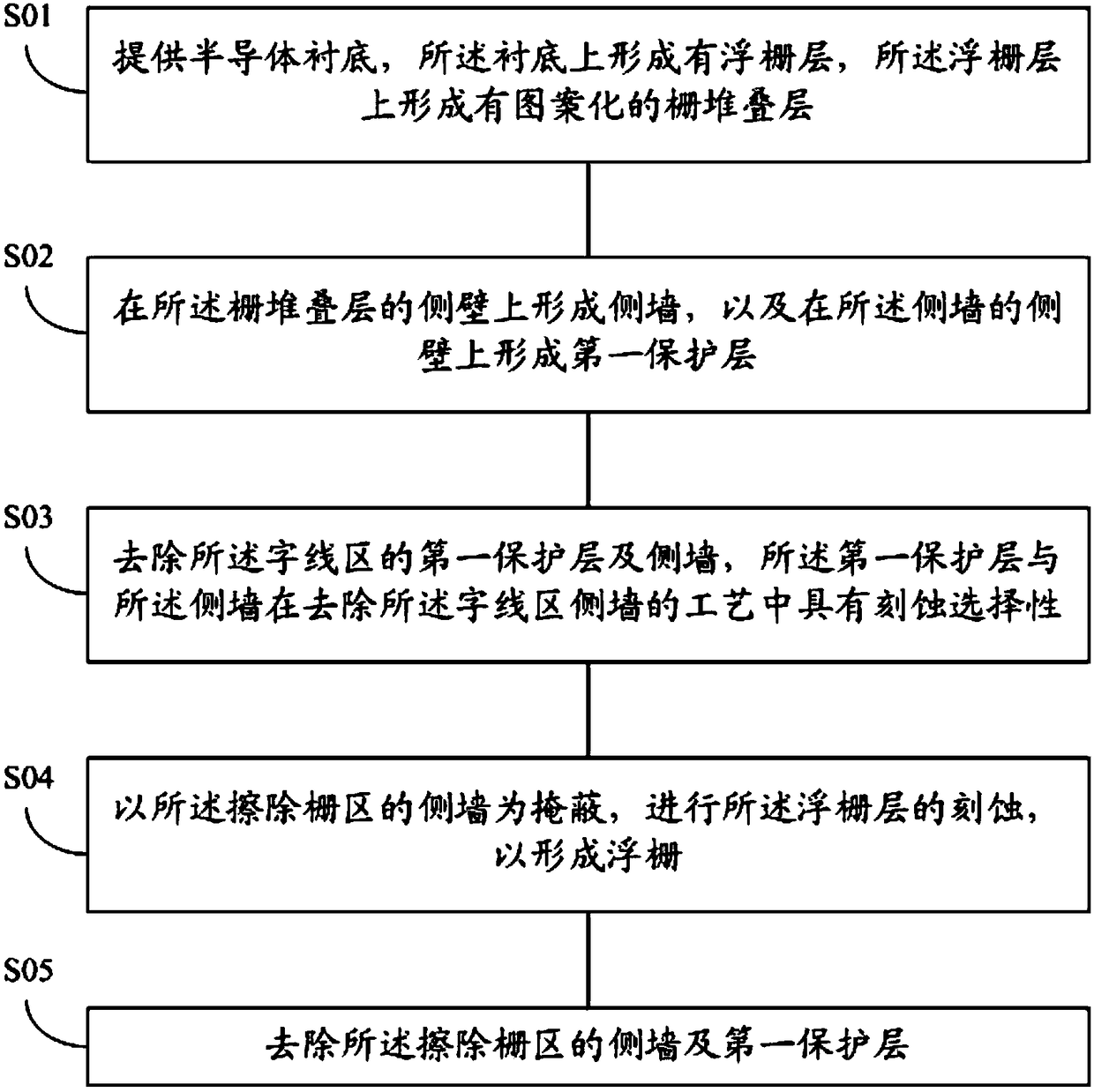

ActiveCN109378314AImprove erase efficiencyImprove performanceSolid-state devicesSemiconductor devicesEngineeringGate stack

The invention provides a method for manufacturing a flash memory device. When a sidewall of a gate stack layer is formed, a first protective layer is formed on a side wall of the sidewall; and the protective layer and the sidewall are etching-selective in a process of removing the sidewall in a word line region; in this way, when the sidewall in the word line region is removed, the protective layer can protect the sidewall of an erase gate region from being removed, and the sidewall of the erase gate region is a mask when a floating gate is formed. The protective layer can reduce or avoid damage to the mask forming the floating gate, thereby improving the uniformity of the formed floating gate, improving the erasing efficiency of the flash memory device and improving the performance of theflash memory device.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

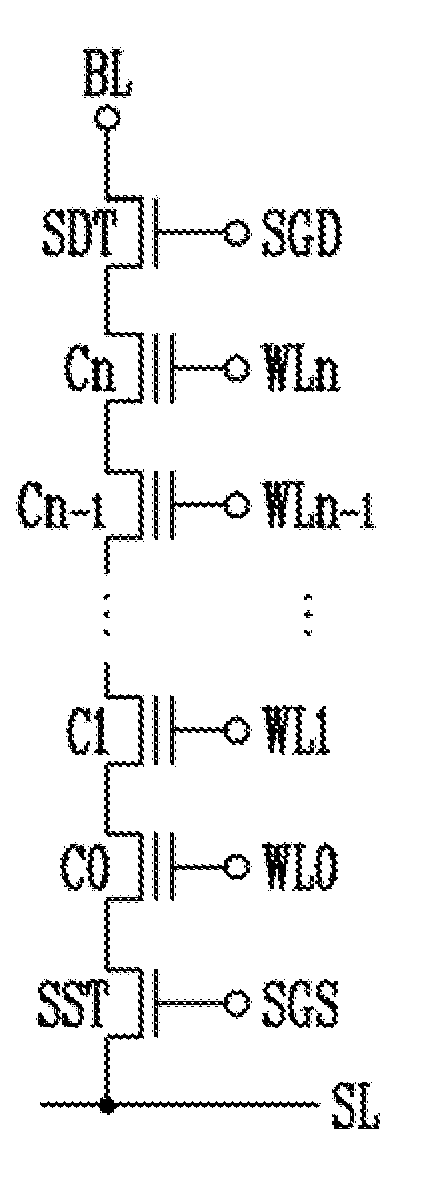

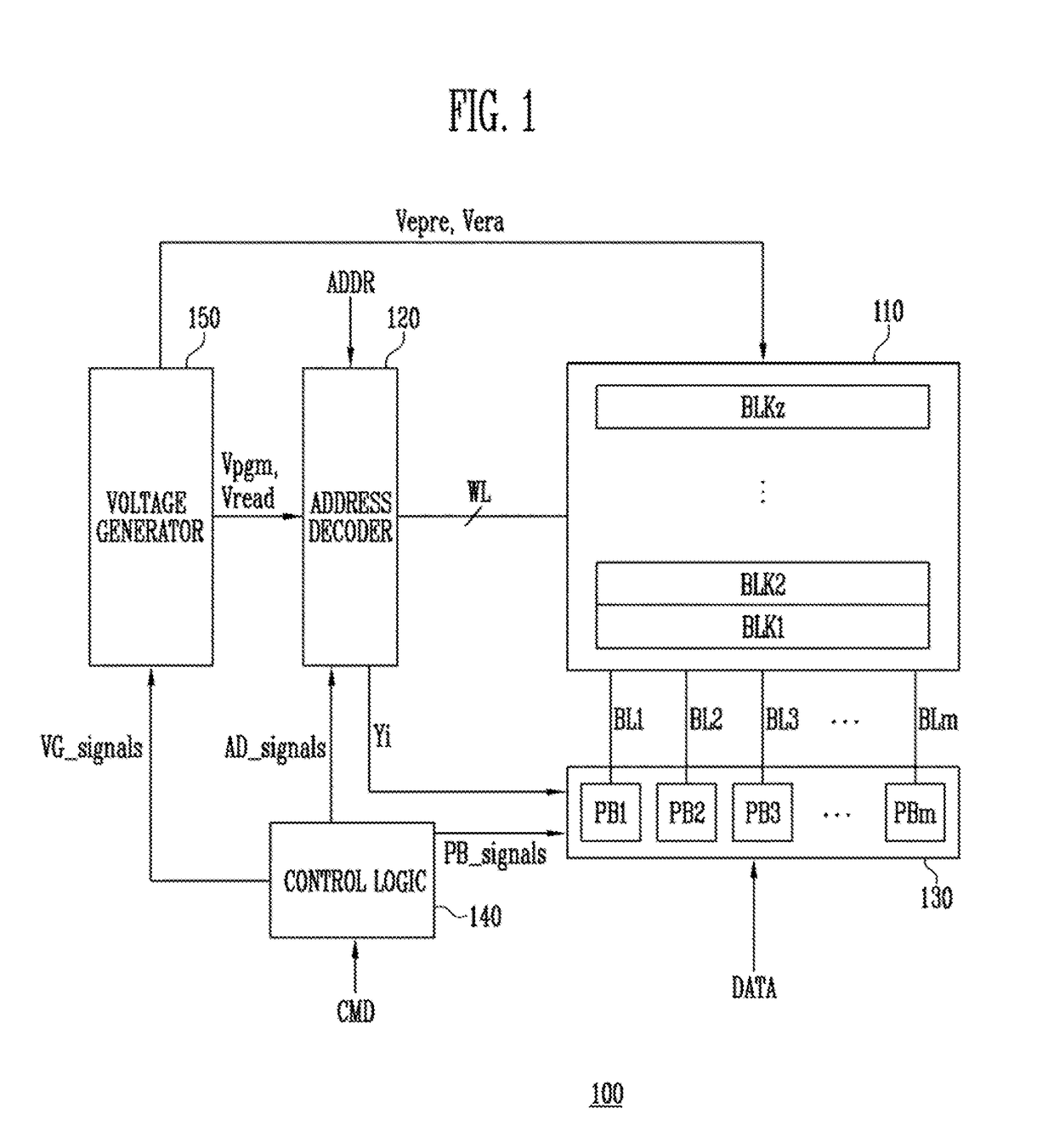

Semiconductor memory device and operating method thereof

A semiconductor memory device includes a memory cell array including a plurality of memory blocks, a voltage generator suitable for applying an erase voltage to a source line of at least one memory block selected from among the plurality of memory blocks during an erase operation, a read and write circuit suitable for applying an initial setting voltage, to bit lines of at least one memory block during the erase operation, and a control logic suitable for controlling the voltage generator and the read and write circuit to apply the initial setting voltage to the bit lines before applying the erase voltage to the source line.

Owner:SK HYNIX INC

Single-poly EEPROM

Owner:UNITED MICROELECTRONICS CORP

Teaching board

InactiveCN108257456AQuick eraseImprove erase efficiencyBoard cleaning devicesTeaching apparatusDrive shaftSlide plate

The invention discloses a teaching board which comprises a base. A support column is fixedly connected with the upper side of the base, a teaching board body is fixedly connected with a side of the support column, a mounting frame is fixedly connected with the side, which is far away from the support column, of the teaching board body, a mounting cover is fixedly connected with the lower side of the mounting frame, a first bevel gear is rotationally connected with the inner bottom of the mounting cover by a first transmission shaft, the lower end of the first transmission shaft penetrates thebottom of the mounting cover and is connected with a crank, and slide plates are connected with two sides of the first bevel gear by adjusting mechanisms. The teaching board has the advantages that the two slide plates can be driven by the adjusting mechanisms to move towards opposite directions, mounting plates can be driven to move under the movement actions of the slide plates, brushes can be driven to move under the movement actions of the mounting plates, accordingly, board writing on the teaching board body can be quickly erased under the movement actions of the brushes, and the erasingefficiency of the teaching board body can be improved without influence on the teaching progress of teachers or influence on learning of students.

Owner:JIANGSU MARITIME INST

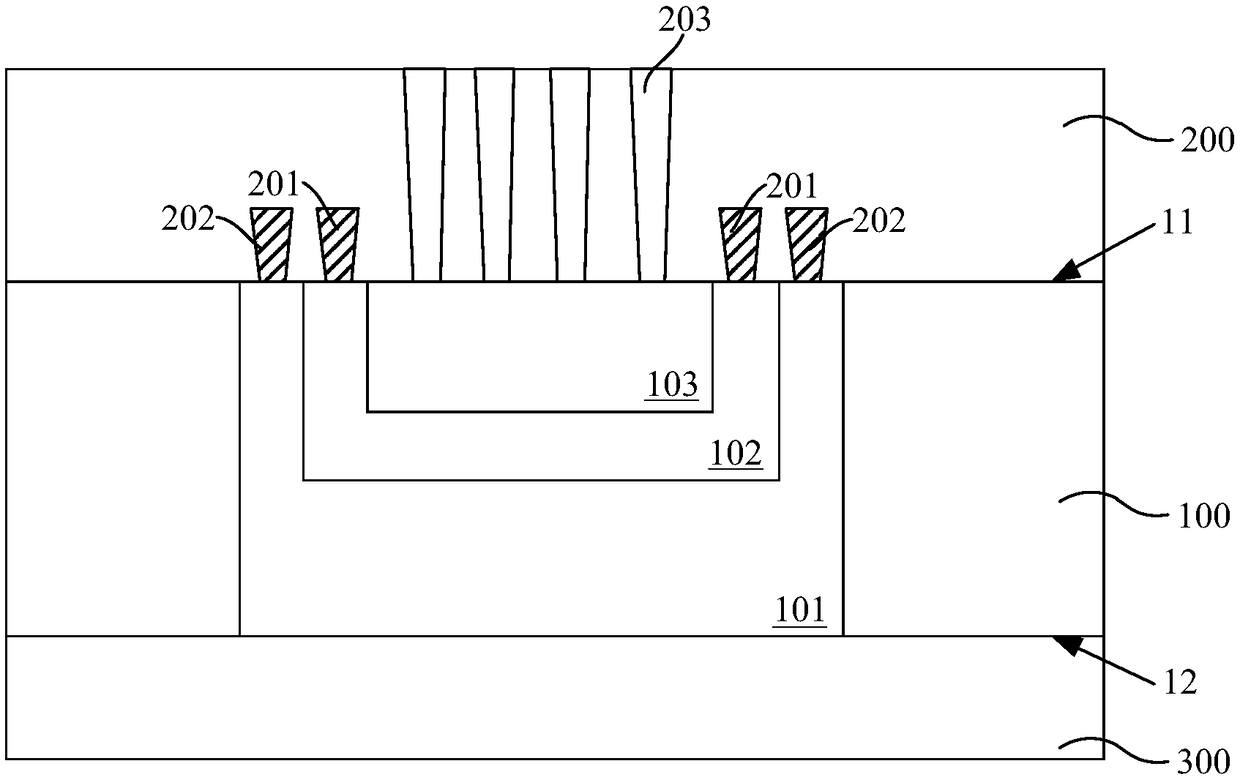

Non-volatile memory and manufacturing method for the same

ActiveUS20200152784A1Enhanced tunneling effectImprove erase efficiencyTransistorSemiconductor/solid-state device manufacturingEngineering physicsDielectric layer

The present invention provides a non-volatile memory and a manufacturing method for the same. In the non-volatile memory, a floating gate structure has a first sharp portion and a second sharp portion, and a corner formed by a side surface of the floating gate structure and a part of a top surface of the floating gate structure is not covered by a control gate structure. The corner is connected between the first sharp portion and one end of the second sharp portion. A tunneling dielectric layer of an erasing gate structure covers the first sharp portion, the second sharp portion, and a tip part of the corner.

Owner:NEXCHIP SEMICON CO LTD

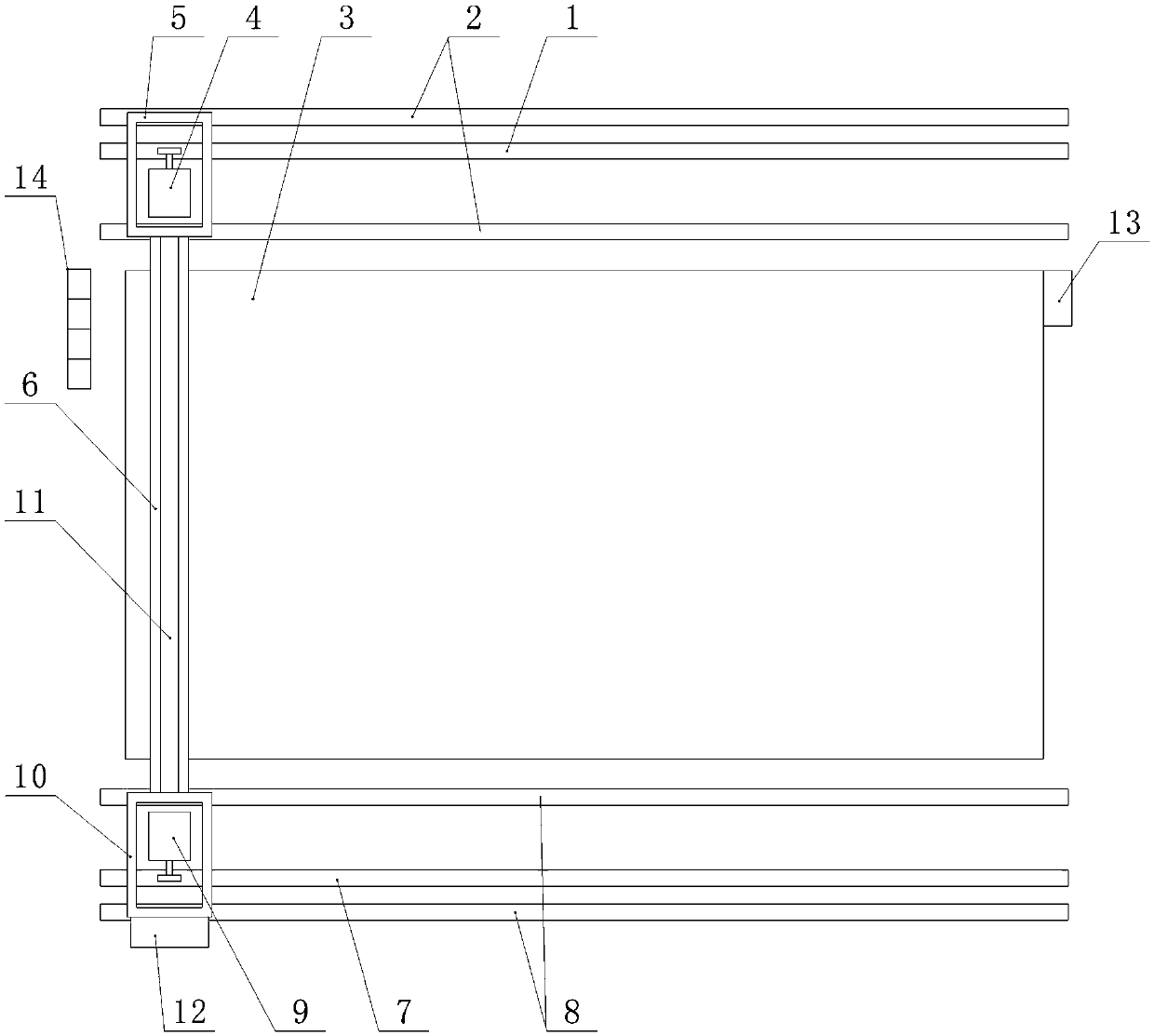

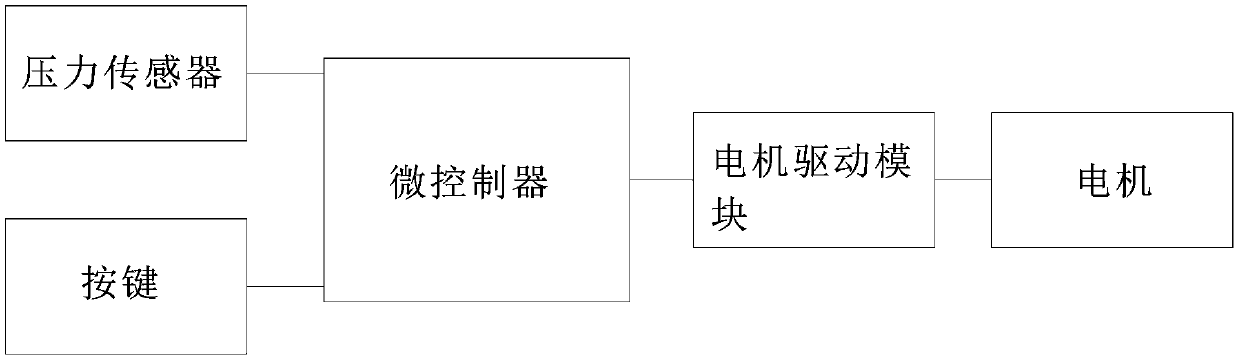

Intelligent blackboard eraser

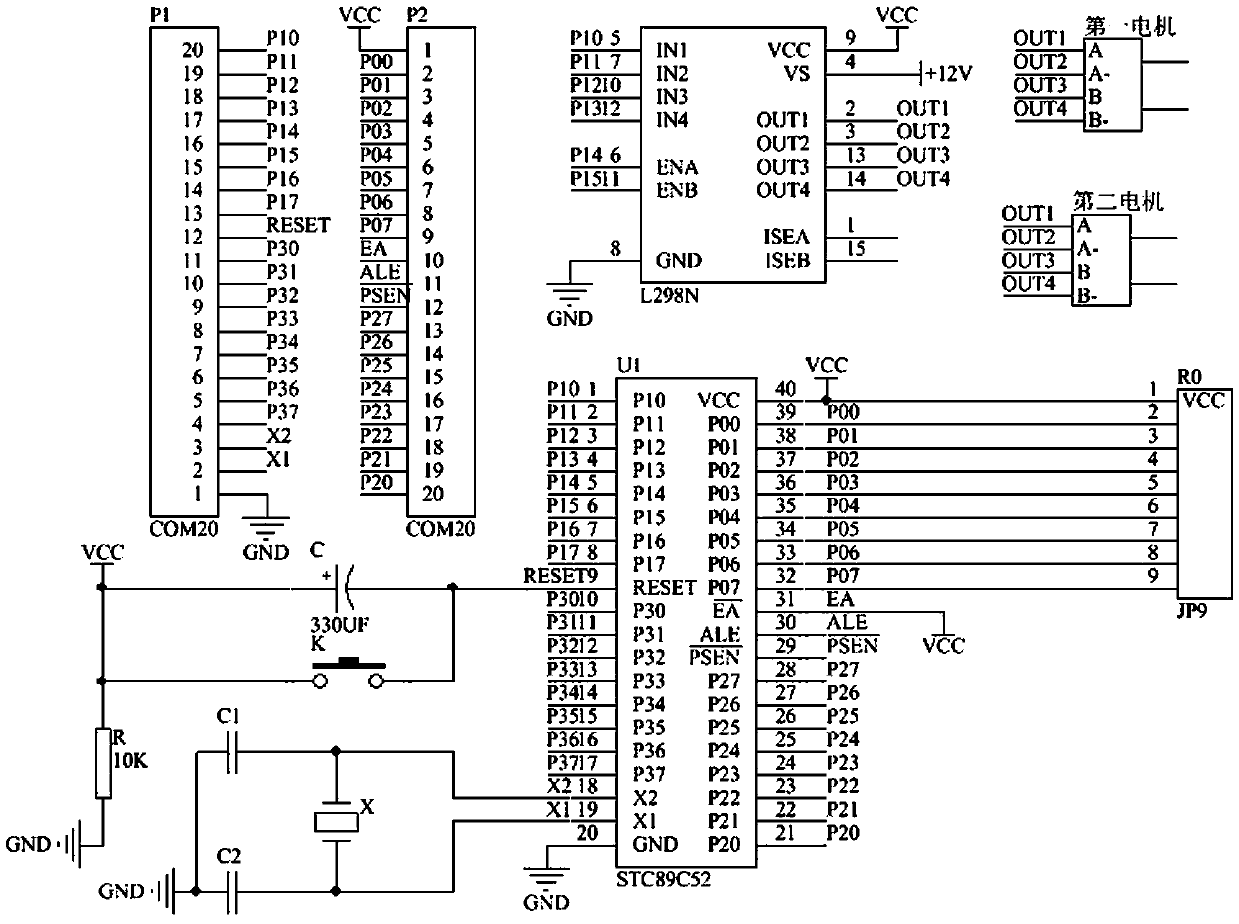

The invention discloses an intelligent blackboard eraser. The intelligent blackboard eraser comprises a first chain-chain wheel group, first guide rail-pulley groups, a first motor, a first motor frame and an eraser, wherein a chain in the first chain-chain wheel group and a guide rail in each first guide rail-pulley group are arranged at an upper edge of a blackboard body; the first motor is arranged in the first motor frame, a pulley in each first guide rail-pulley group is installed on the first motor frame, and a chain wheel in the first chain-chain wheel group is installed on a rotary shaft of the first motor; and the eraser is connected with the first motor frame, and brushes of the eraser are bonded with a blackboard surface of the blackboard body. The intelligent blackboard eraser further comprises a control circuit, wherein the control circuit comprises a microcontroller, and a pressure sensor, keys and a motor drive module which are connected with the microcontroller, wherein the motor drive module is connected with the motor. The blackboard eraser is simple in structure, low in cost, convenient to use, economic and safe, high in reliability, high in erasing effect, capable of reducing dust flying, time-saving and labour-saving, high in erasing efficiency, and capable of reducing dust harm to teachers and students.

Owner:BAISE UNIV

An erasing method of a flash memory device and a flash memory device

InactiveCN109256166AExtended service lifeReduce in quantityRead-only memoriesMaster controllerSmall data

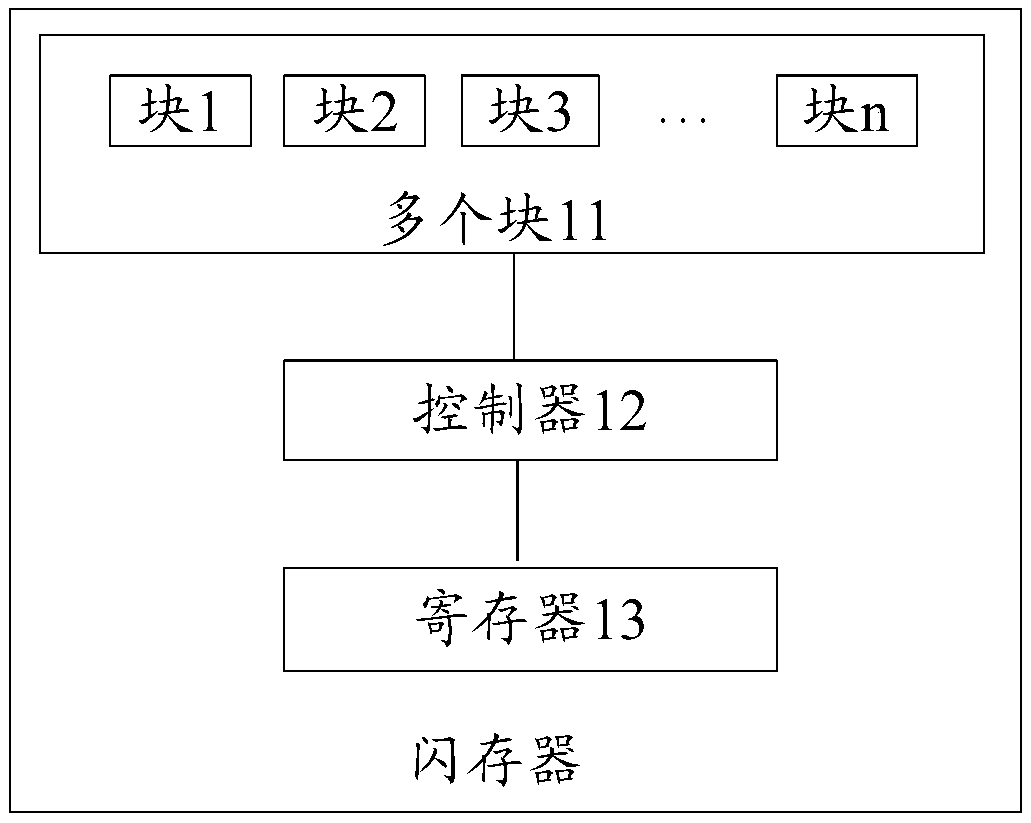

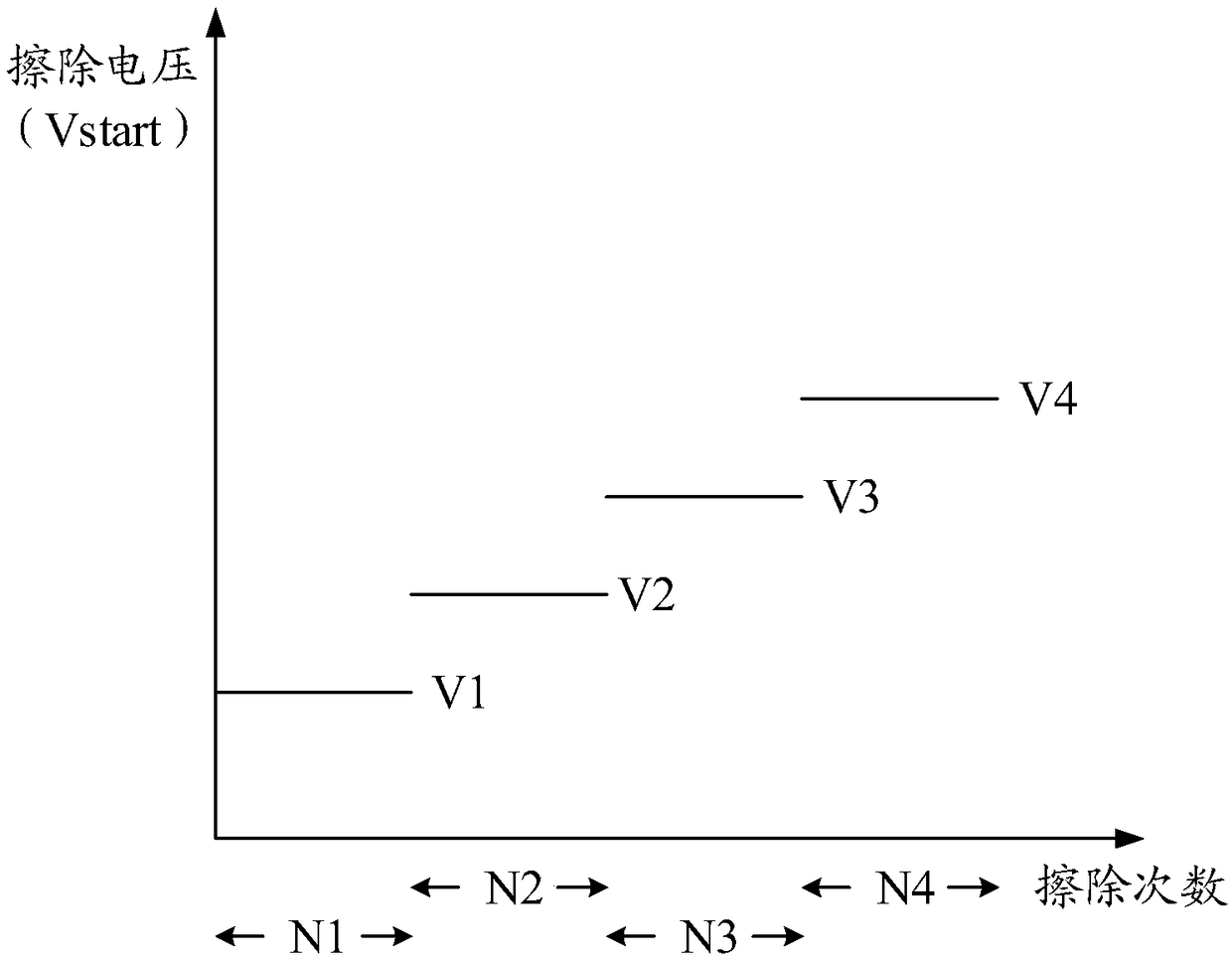

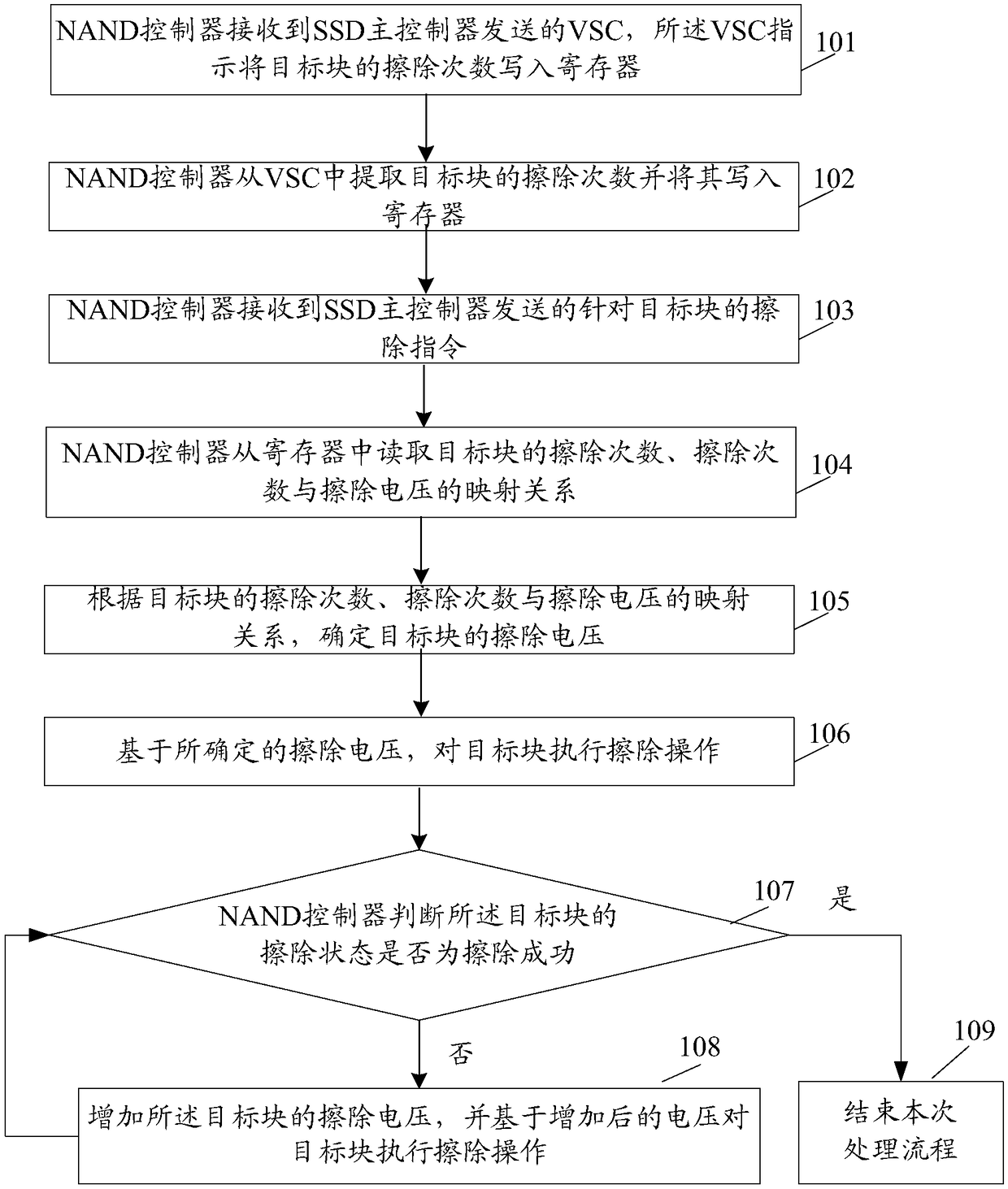

The invention discloses an erasing method of a flash memory device and a flash memory device. The flash memory device comprises a plurality of blocks, each of which is composed of a plurality of memory cells, wherein the memory cells are the smallest data storage units of the flash memory device; a controller, configured to receive a write instruction carrying an erase parameter from an external main controller, and write the erase parameter into a register, and to receive an erase instruction for a target block from an external master controller and obtain an erase parameter of the target block, determine an erase voltage corresponding to the target block based on an erase parameter of the target block, and perform an erase operation on the target block based on the determined erase voltage; and a register which is used for storing the erase parameter.

Owner:YANGTZE MEMORY TECH CO LTD