Patents

Literature

51results about How to "Reduce the erase voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

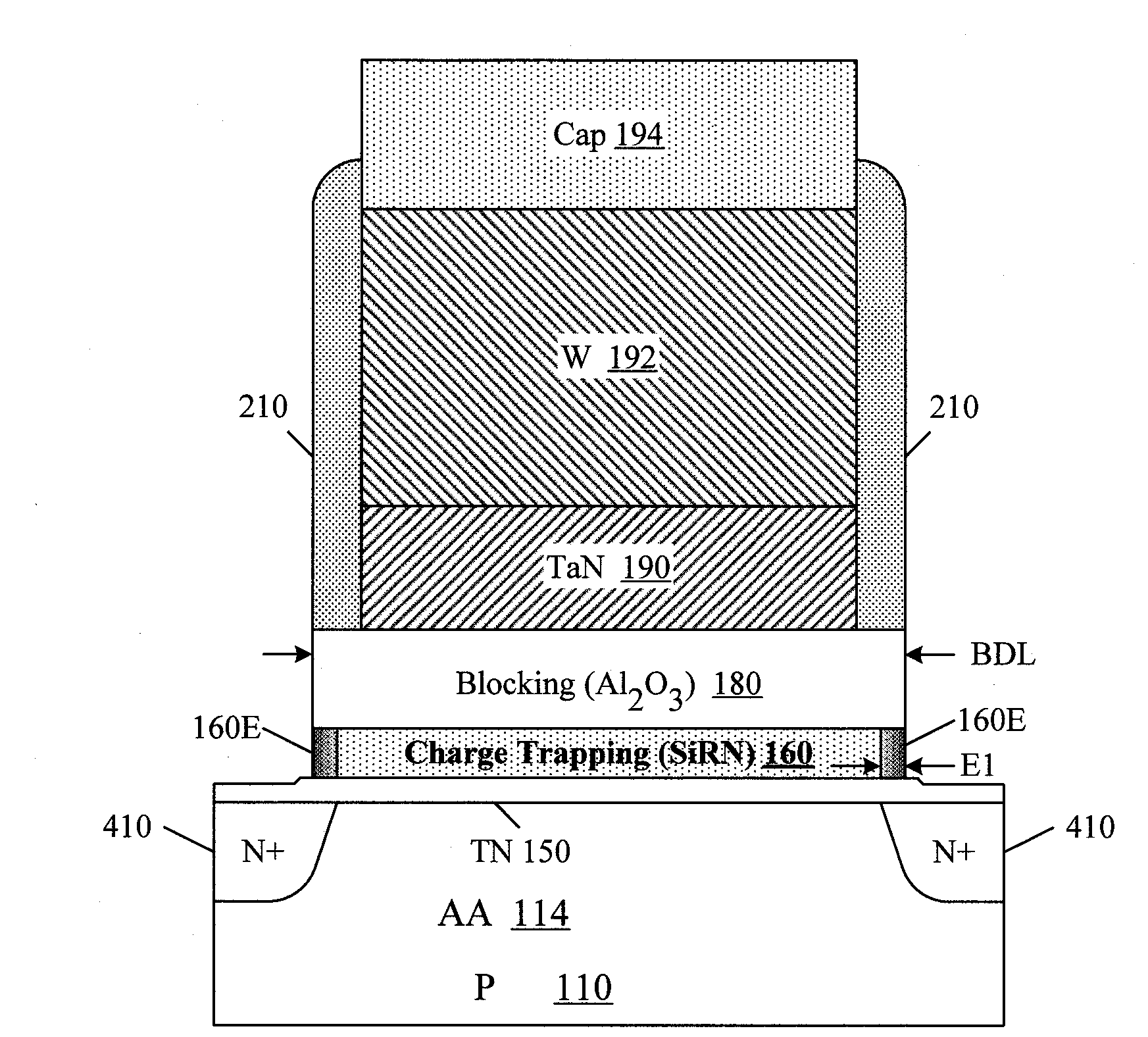

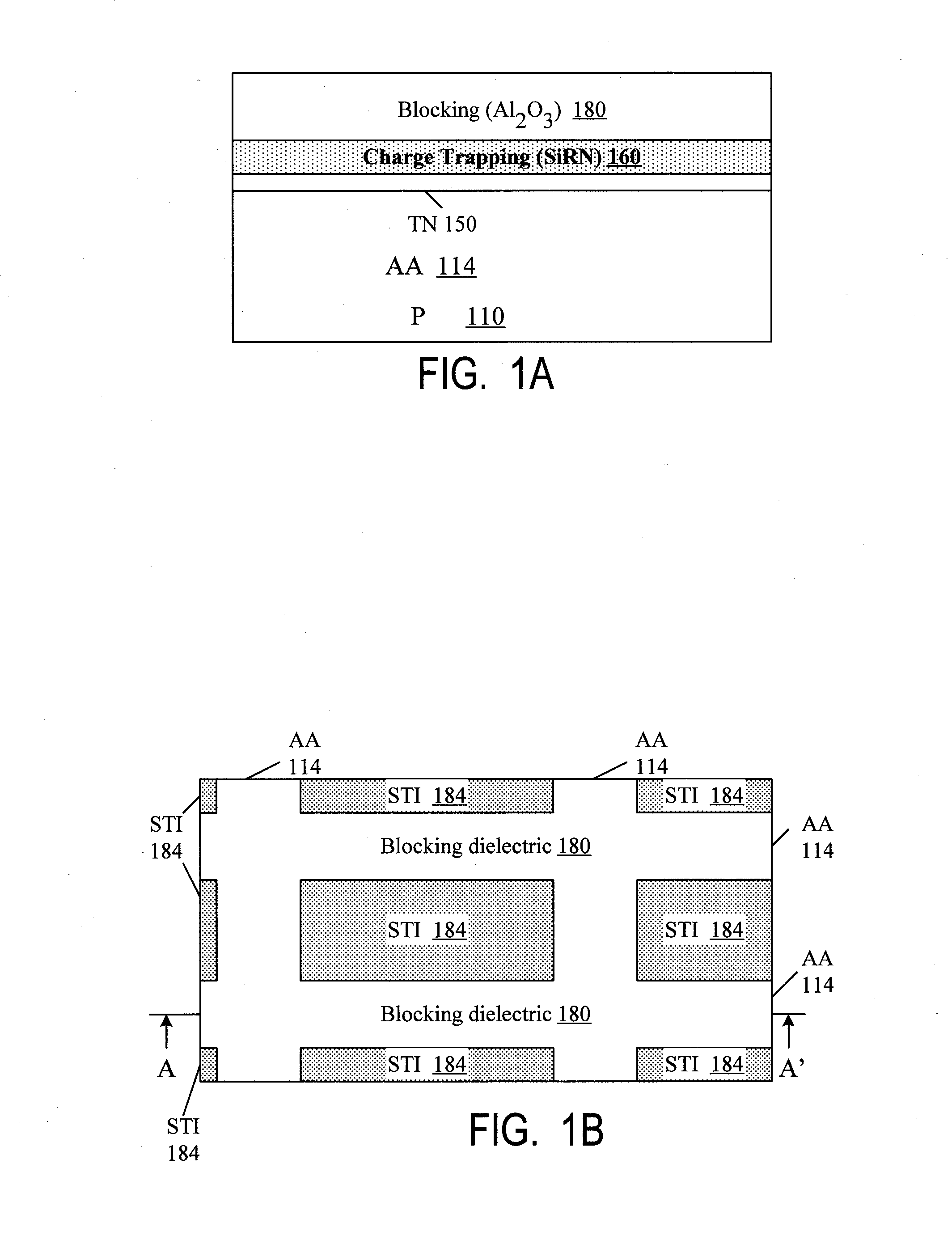

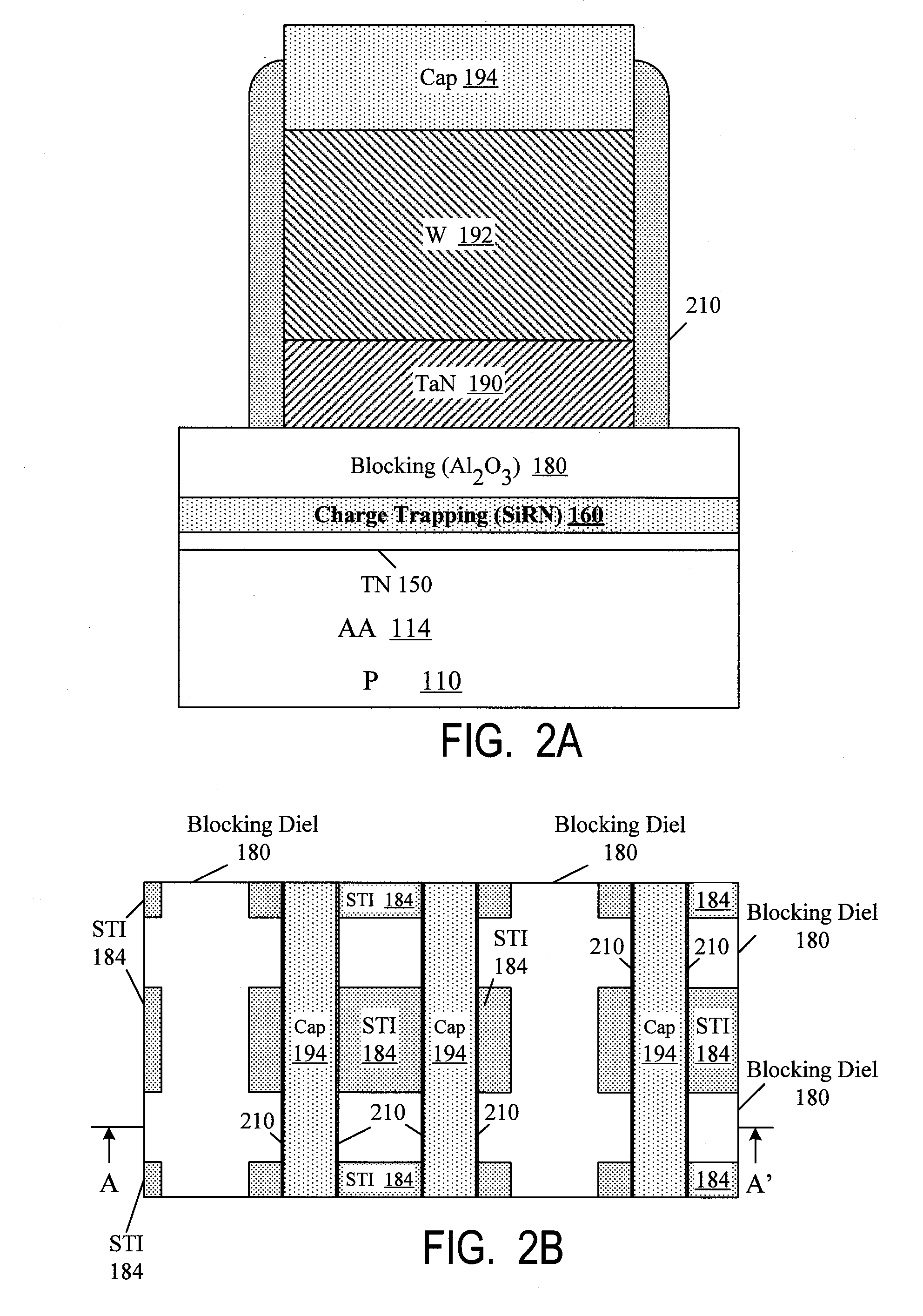

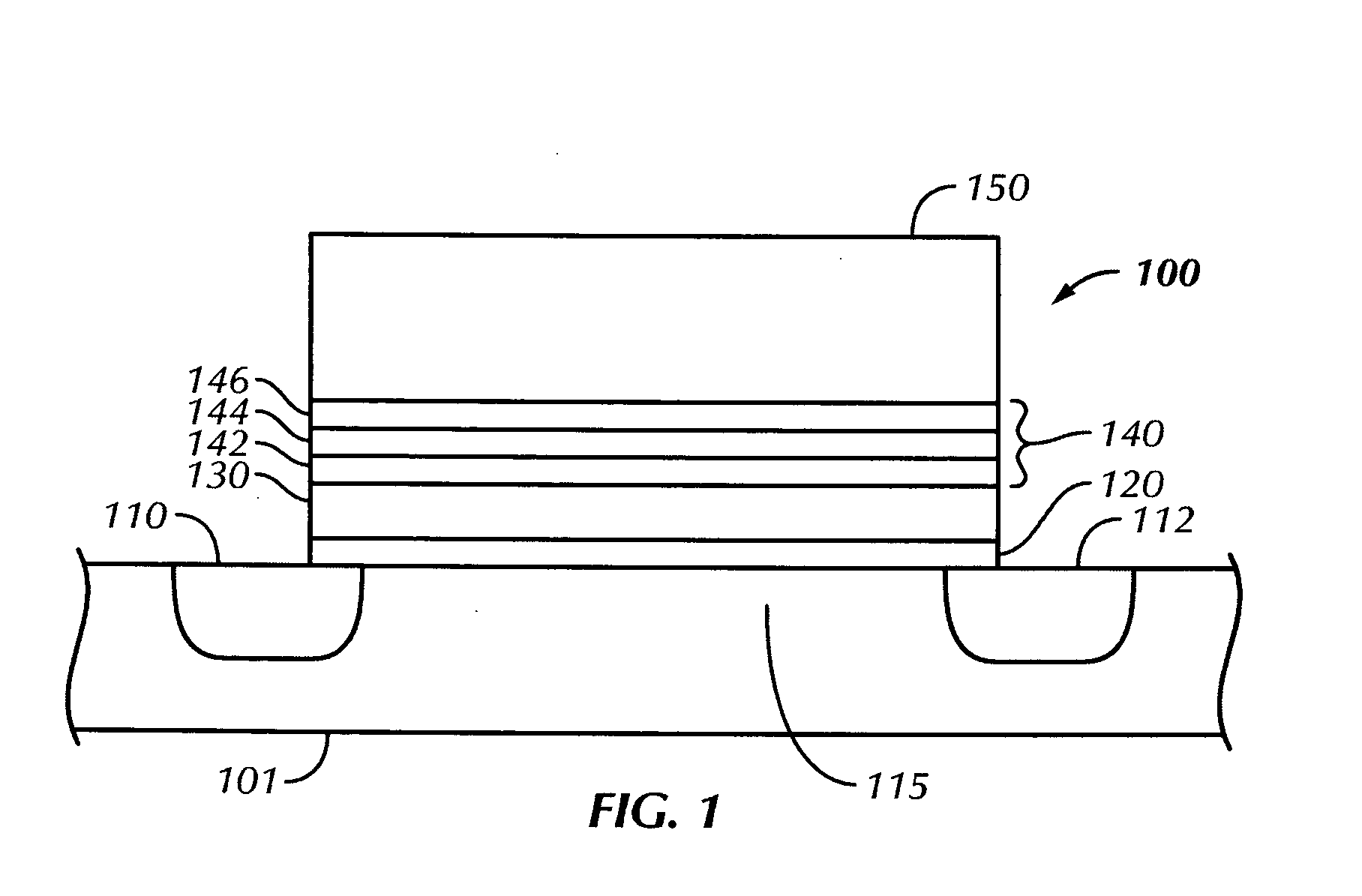

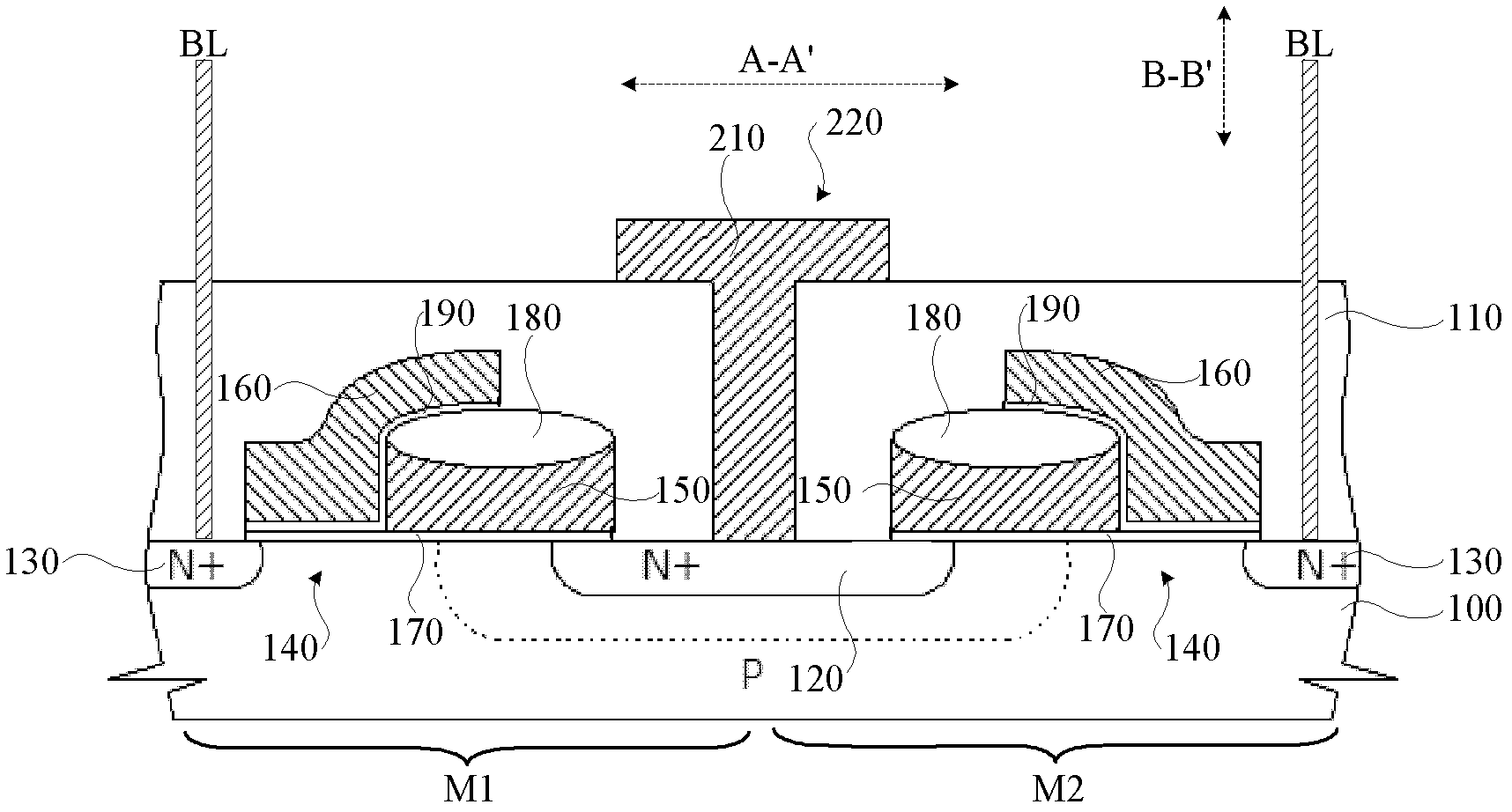

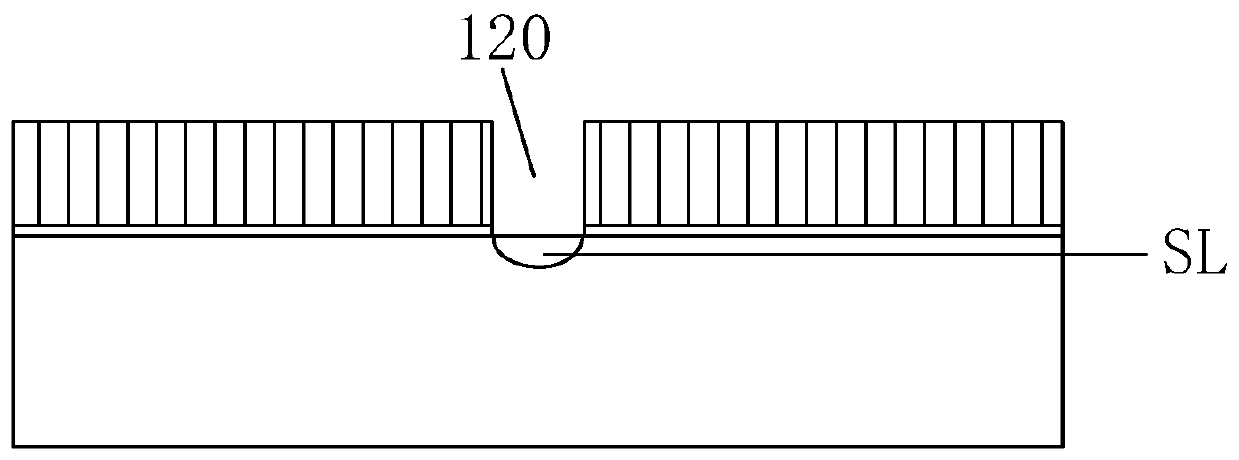

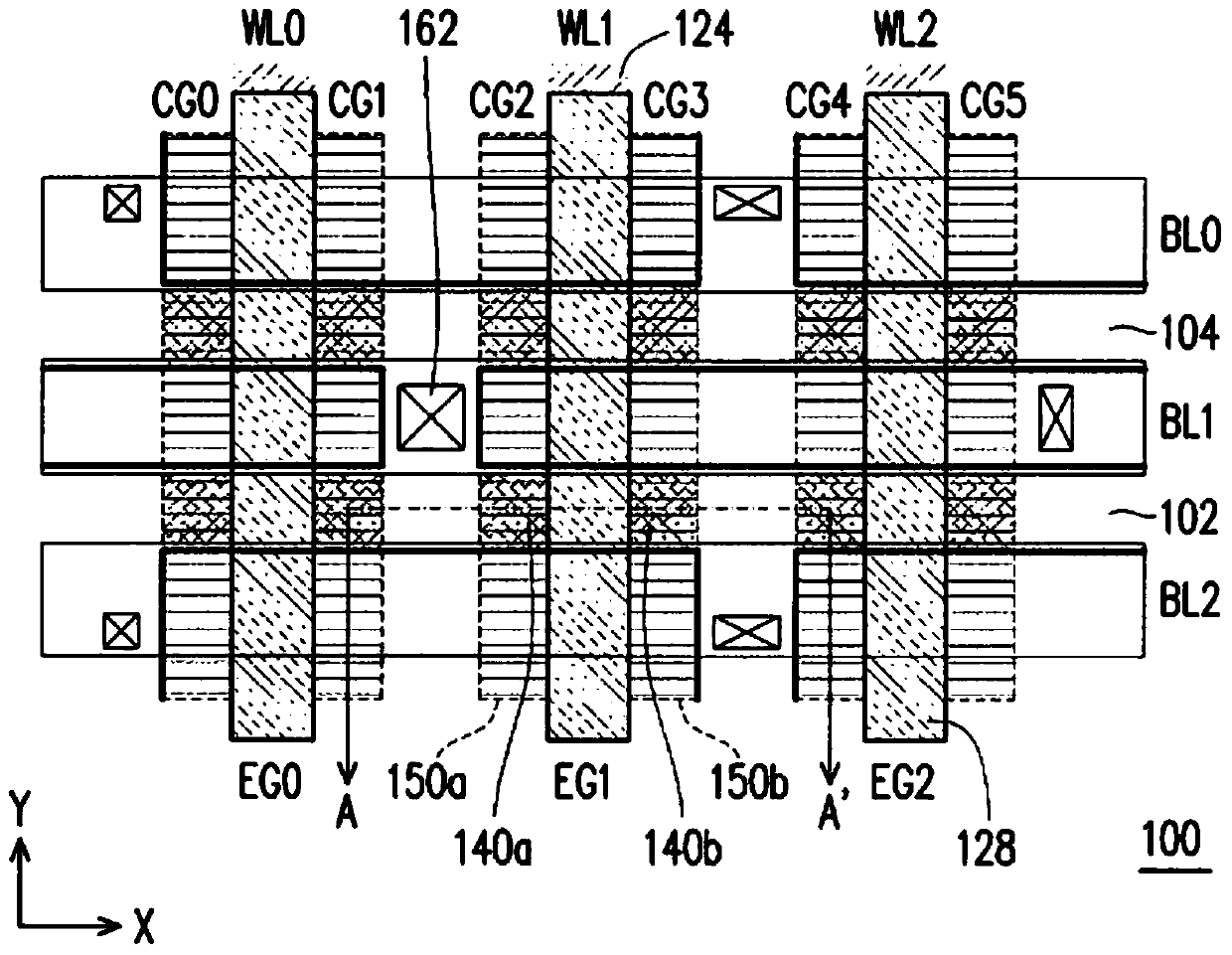

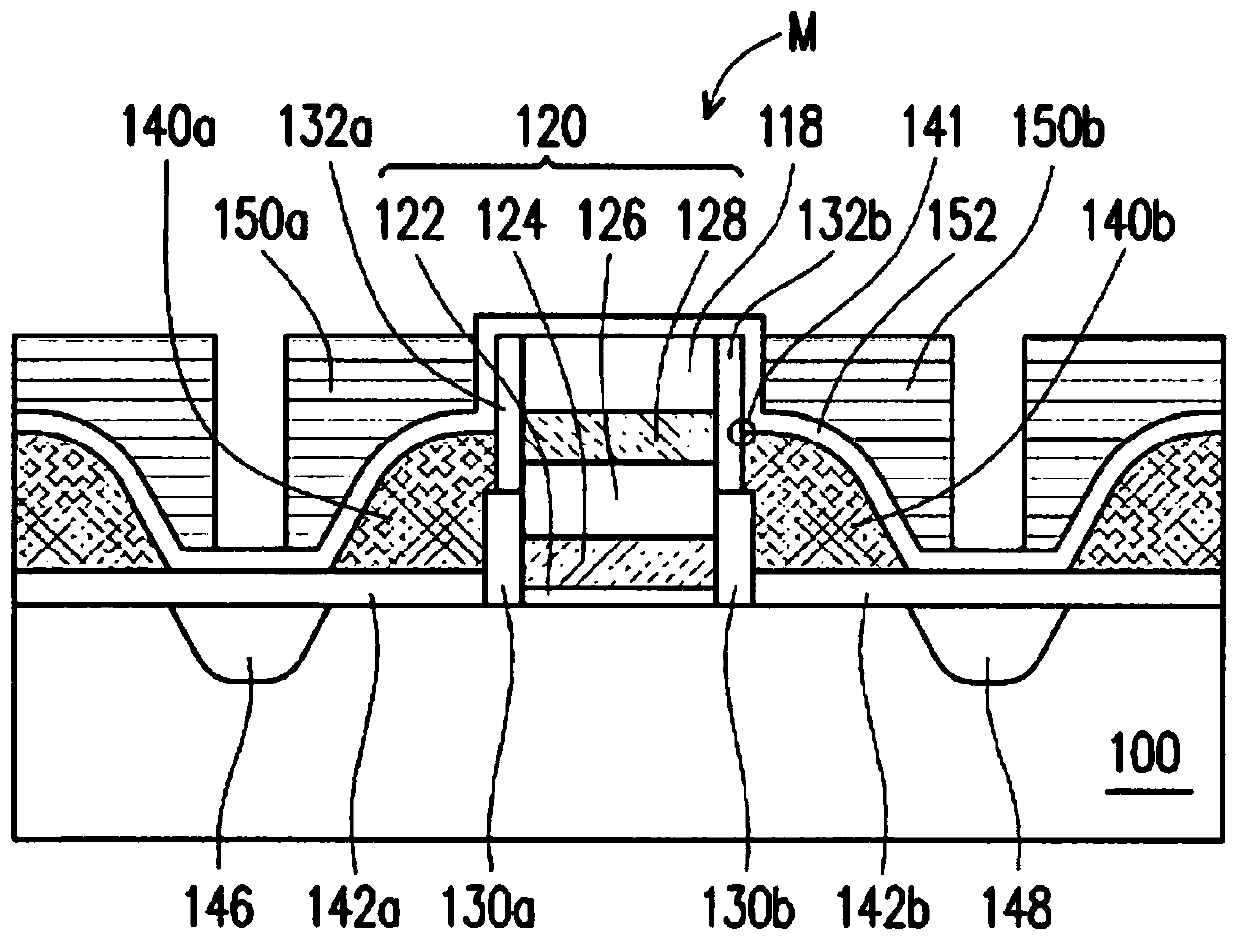

Nonvolatile memories with charge trapping dielectric modified at the edges

InactiveUS20100059808A1Reduce charge densityTotal current dropTransistorSolid-state devicesDielectricTrapping

A nonvolatile memory cell has charge trapping dielectric (160) which has been modified (i.e. oxidized) adjacent to edges of blocking dielectric (180). The modification reduces the charge-trapping density adjacent to the edges of the blocking dielectric, and hence reduces the leakage current at the edges. Other features are also provided.

Owner:PROMOS TECH PTE LTD

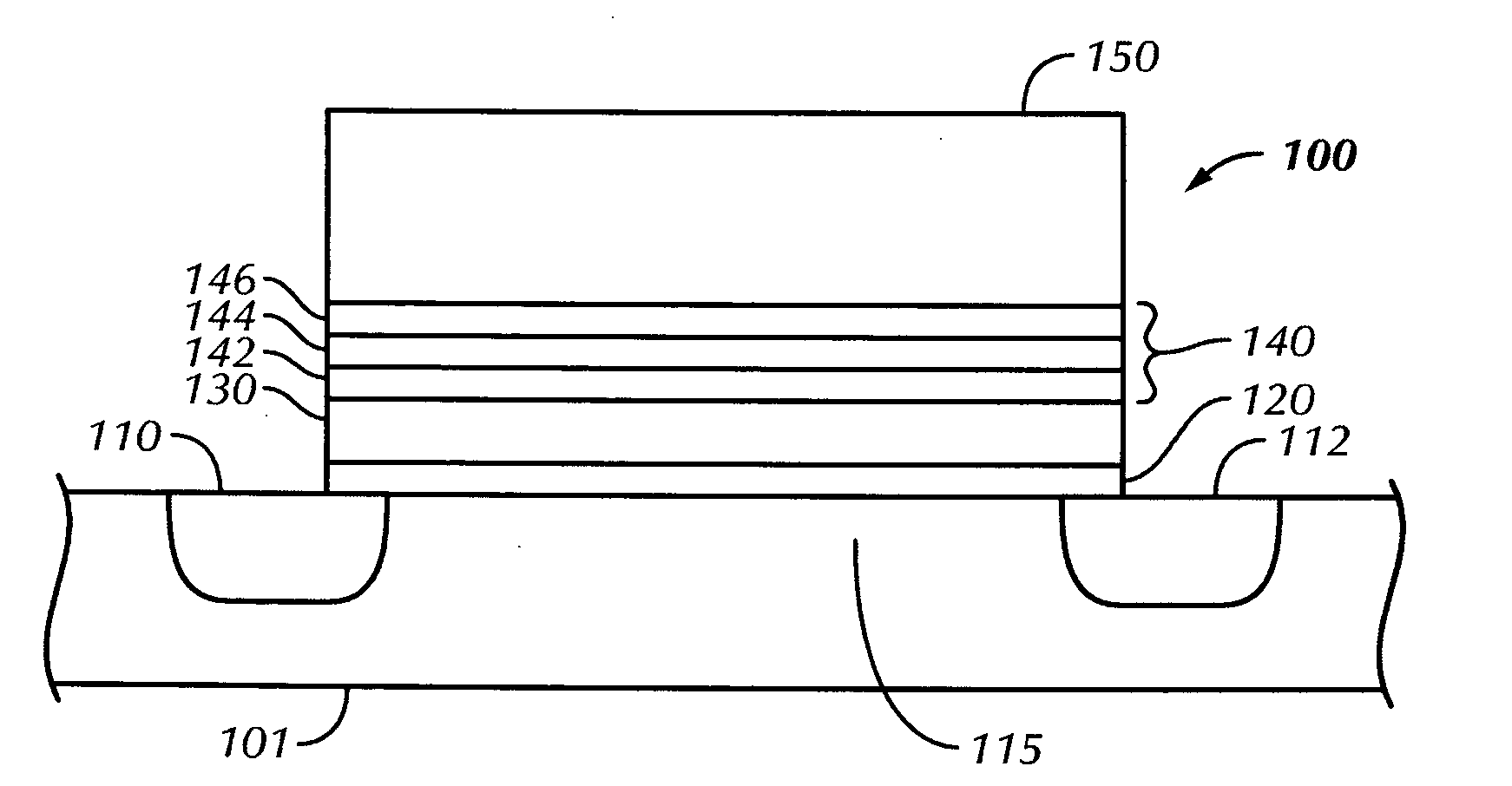

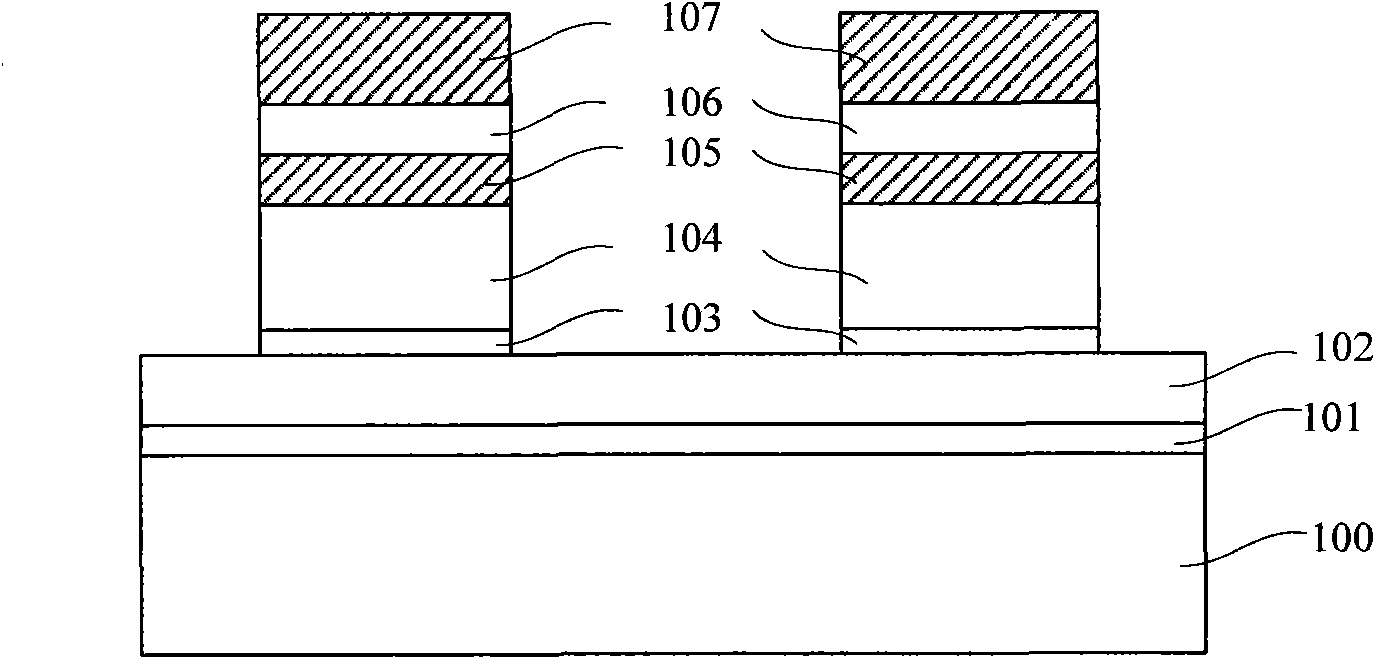

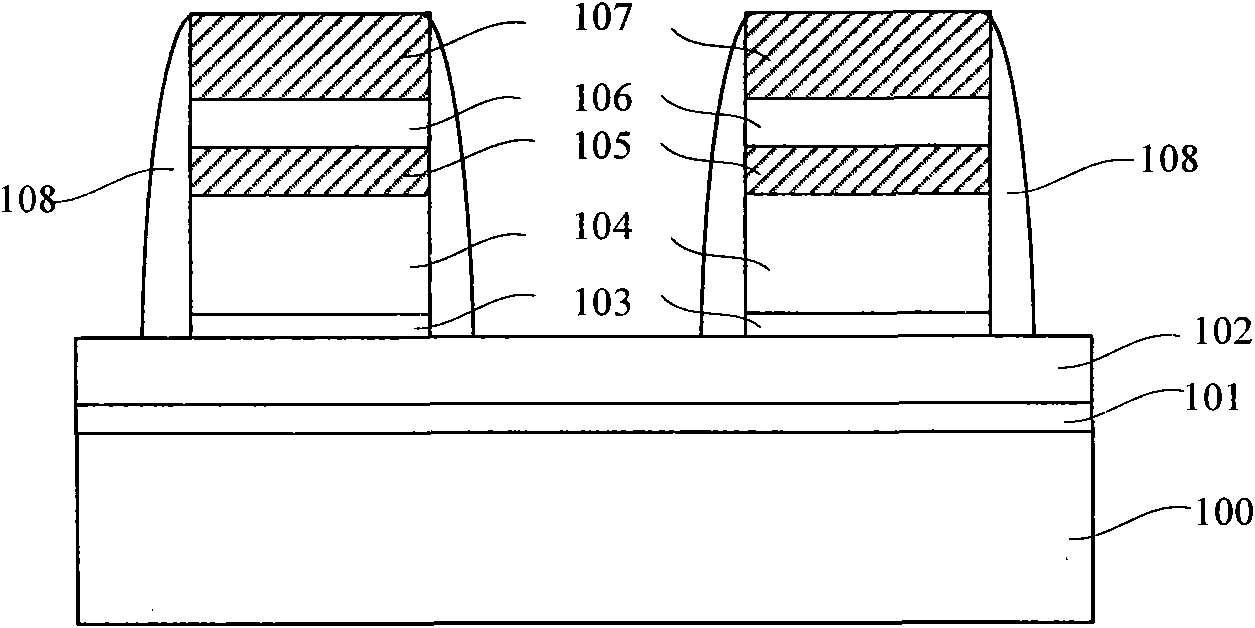

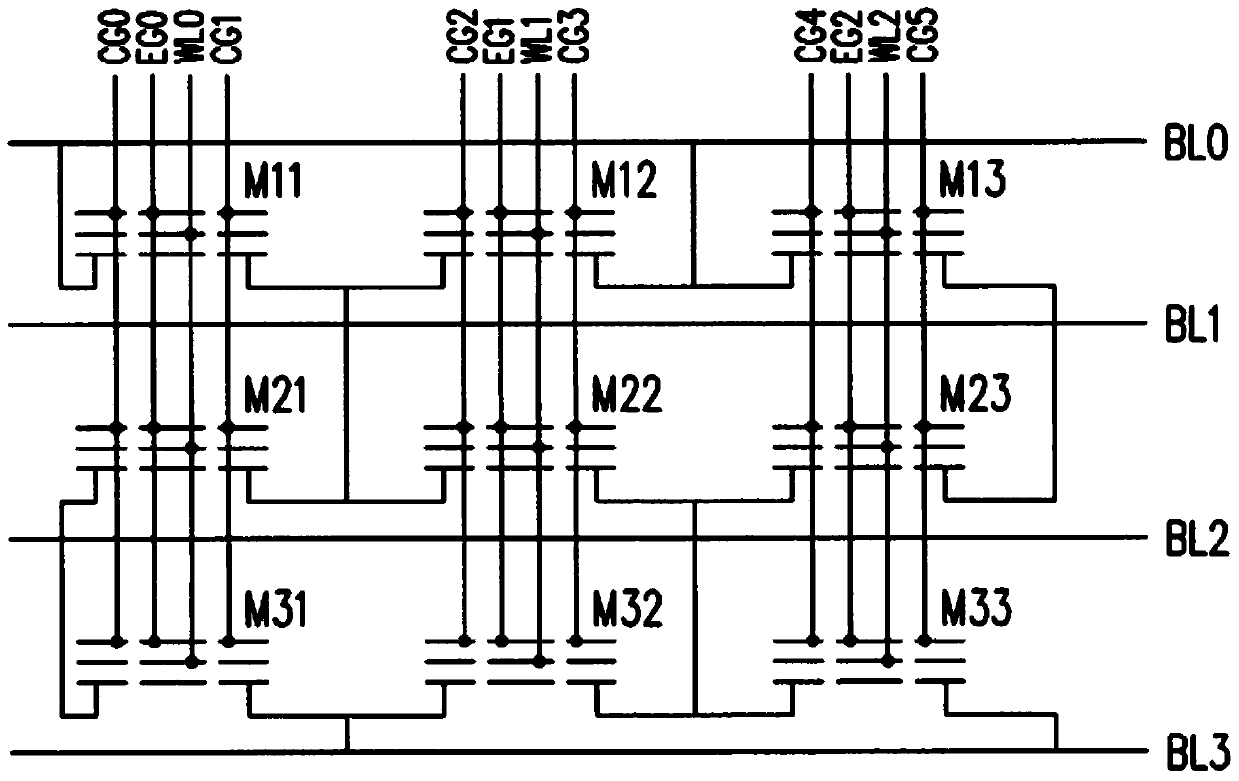

Non-volatile memory cells having a polysilicon-containing, multi-layer insulating structure, memory arrays including the same and methods of operating the same

ActiveUS20080099826A1Facilitates positive voltage erase operationReduce semiconductor layer/oxide interface damageTransistorRead-only memoriesPolycrystalline siliconSemiconductor

Memory cells including a semiconductor layer having at least two source / drain regions disposed below a surface of the semiconductor layer and separated by a channel region; a lower insulating layer disposed above the channel region; a charge storage layer disposed above the lower insulating layer; an upper insulating multi-layer structure disposed above the charge storage layer, wherein the upper insulating multi-layer structure comprises a polysilicon material layer interposed between a first dielectric layer and a second dielectric layer; and a gate disposed above the upper insulating multi-layer structure are described along with arrays thereof and methods of operation.

Owner:MACRONIX INT CO LTD

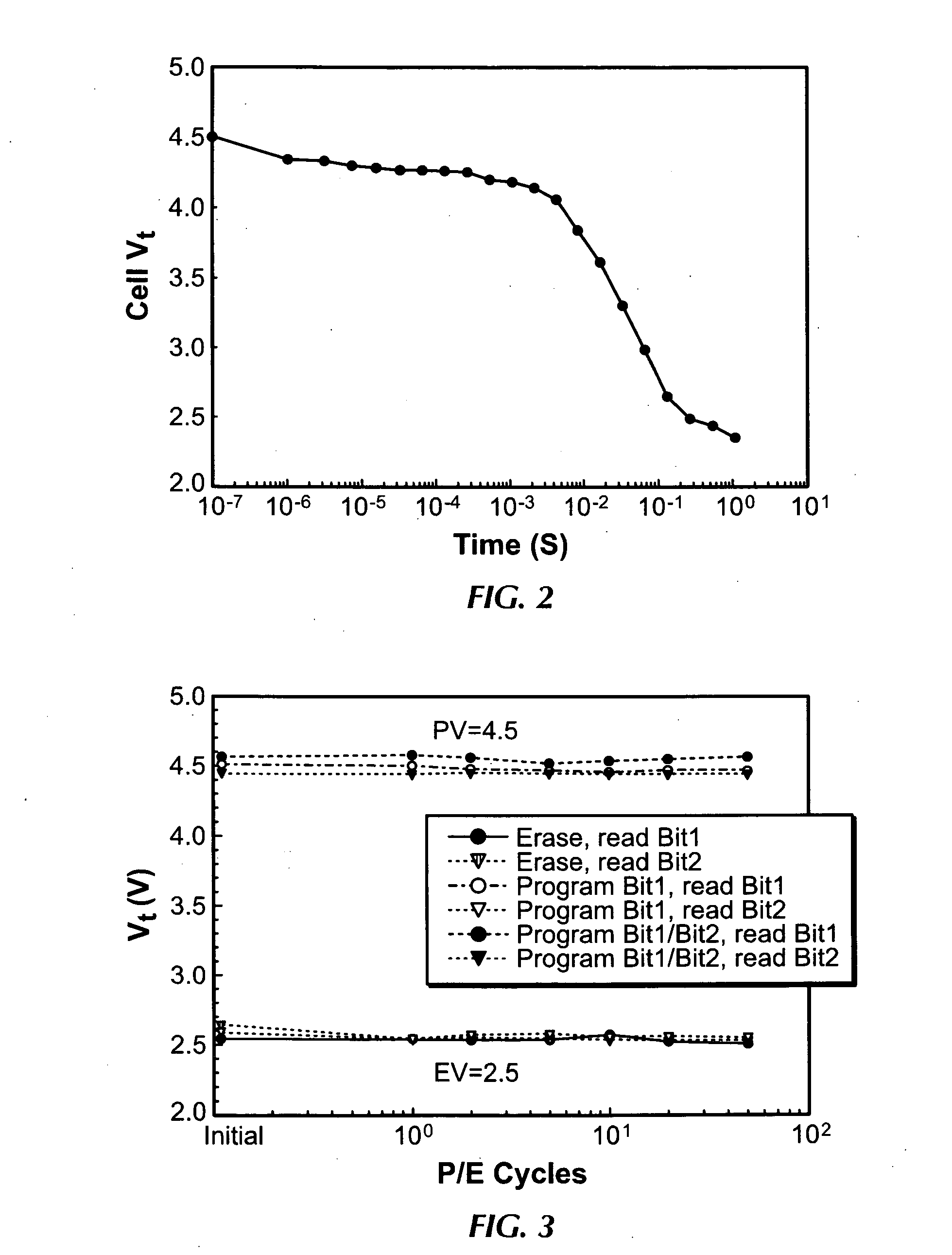

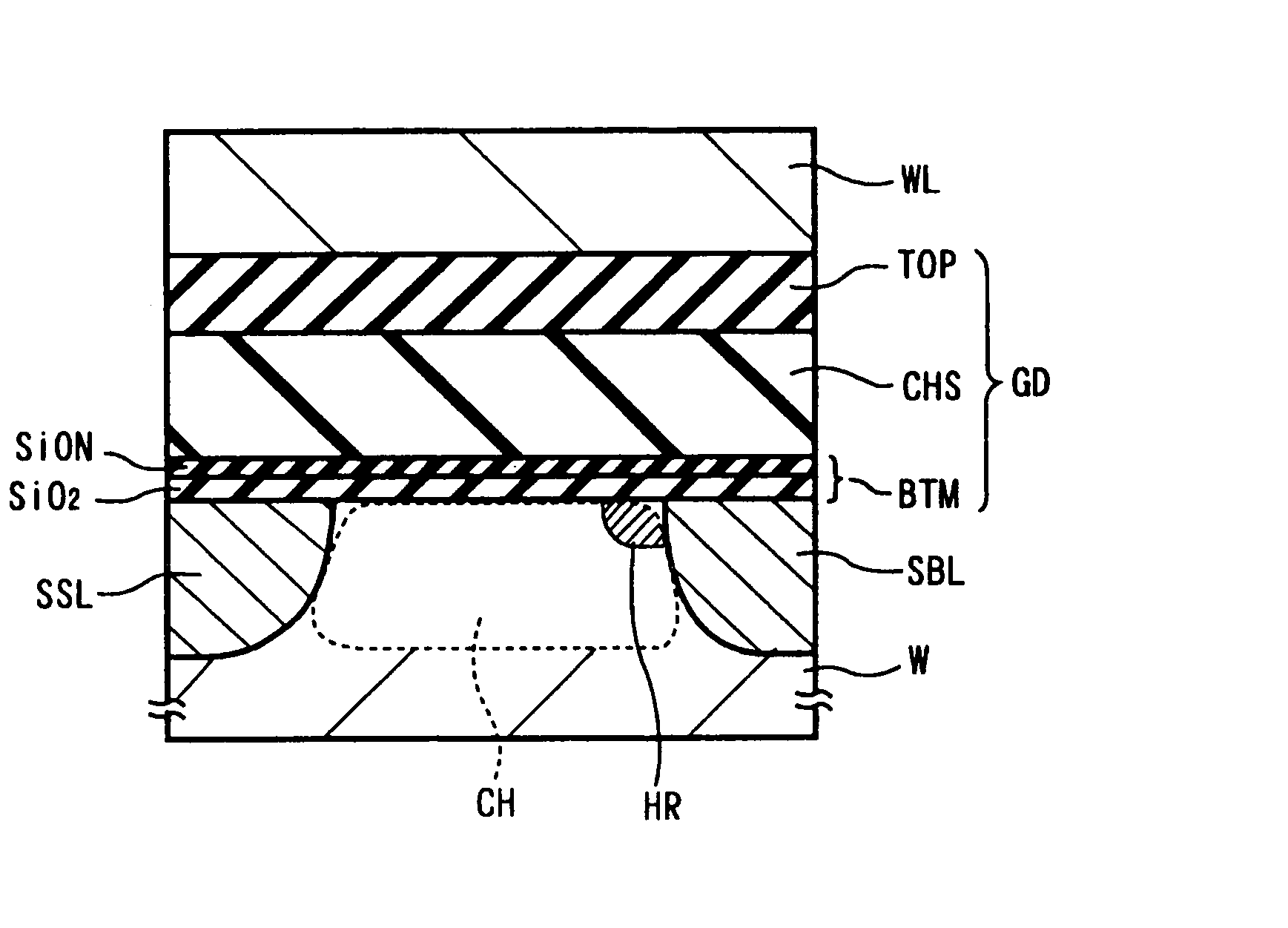

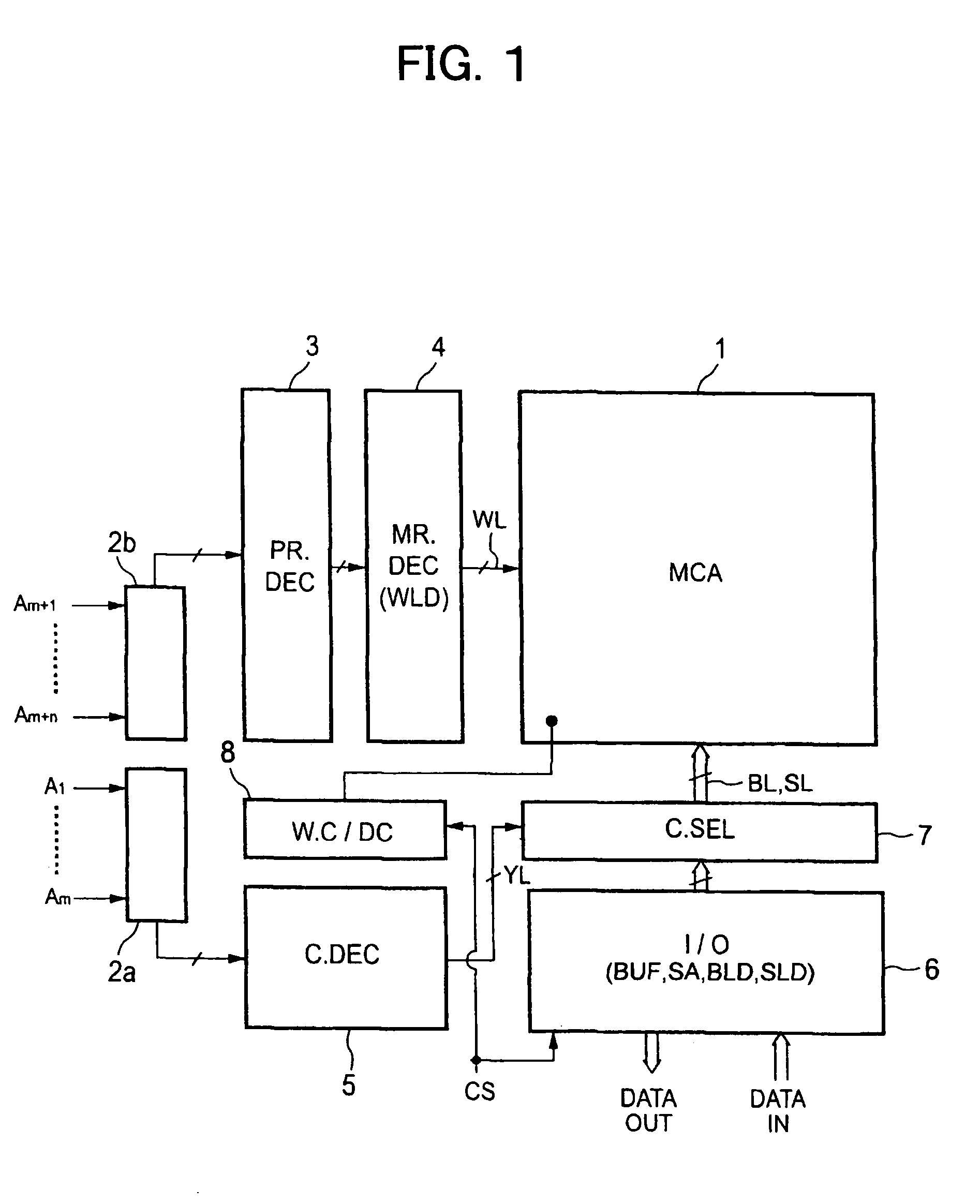

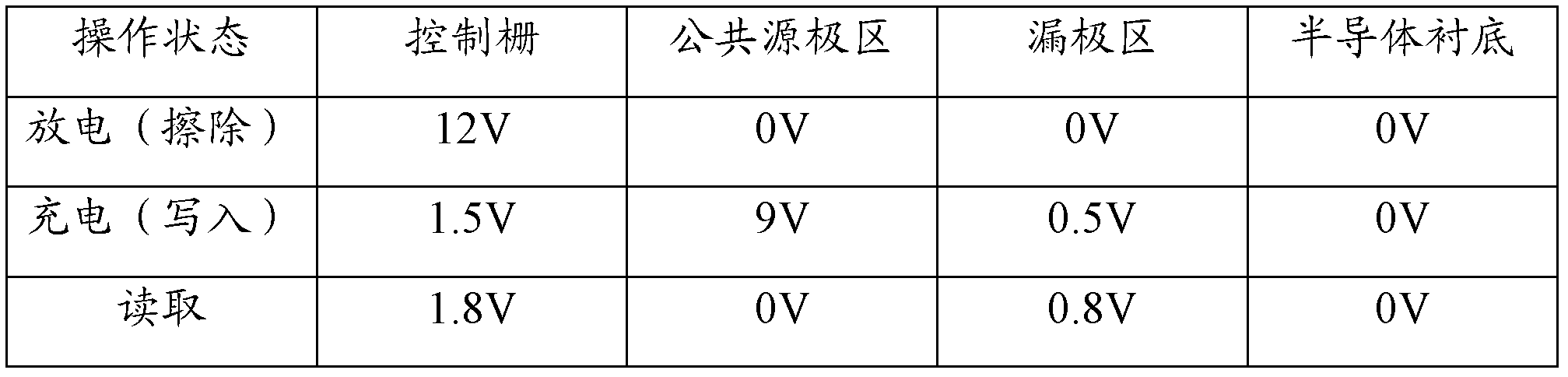

Apparatus and method for high sensitivity read operation

InactiveUS7075143B2Low operationHigh reading sensitivityTransistorSolid-state devicesEngineeringControllability

A nonvolatile semiconductor memory device enabling a high sensitivity read operation by a low voltage, provided with a gate insulating film comprised of a bottom insulating film, a charge storing film, and a top insulating film successively stacked from the bottom, the bottom insulating film including a silicon oxynitride film directly under the charge storing film, and reading a bit of data stored at a local portion of a sub-source line side of a memory transistor and a bit of data stored at a local portion of a sub-bit line side independently by the reverse read method, whereby the incubation time is suppressed by the presence of silicon oxynitride, the controllability of the thickness of the charge storing film is improved, and the threshold voltage in an erase state is decreased, and a method of high sensitivity reading whereby a lower voltage and improved operational reliability are achieved.

Owner:SONY CORP

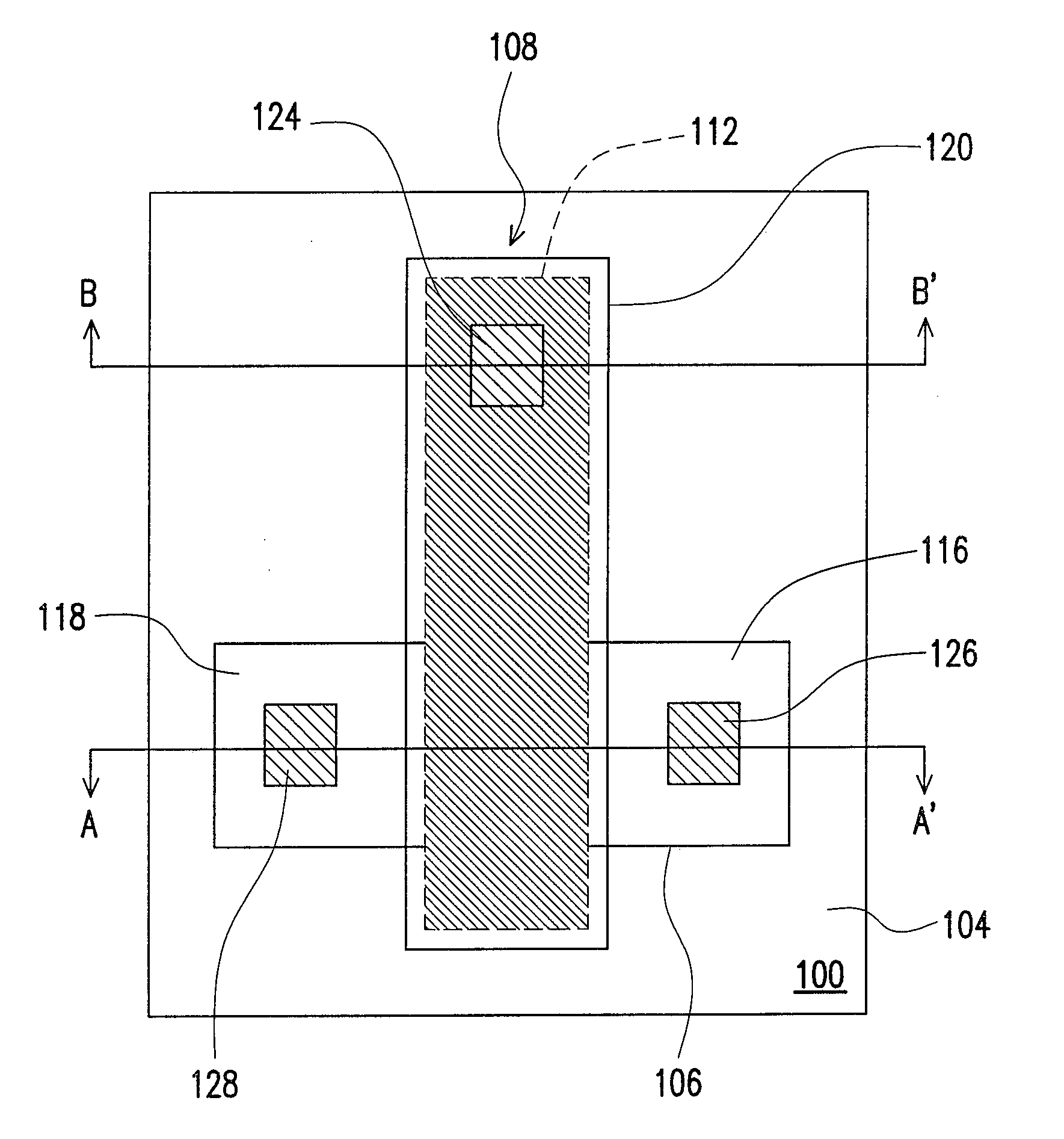

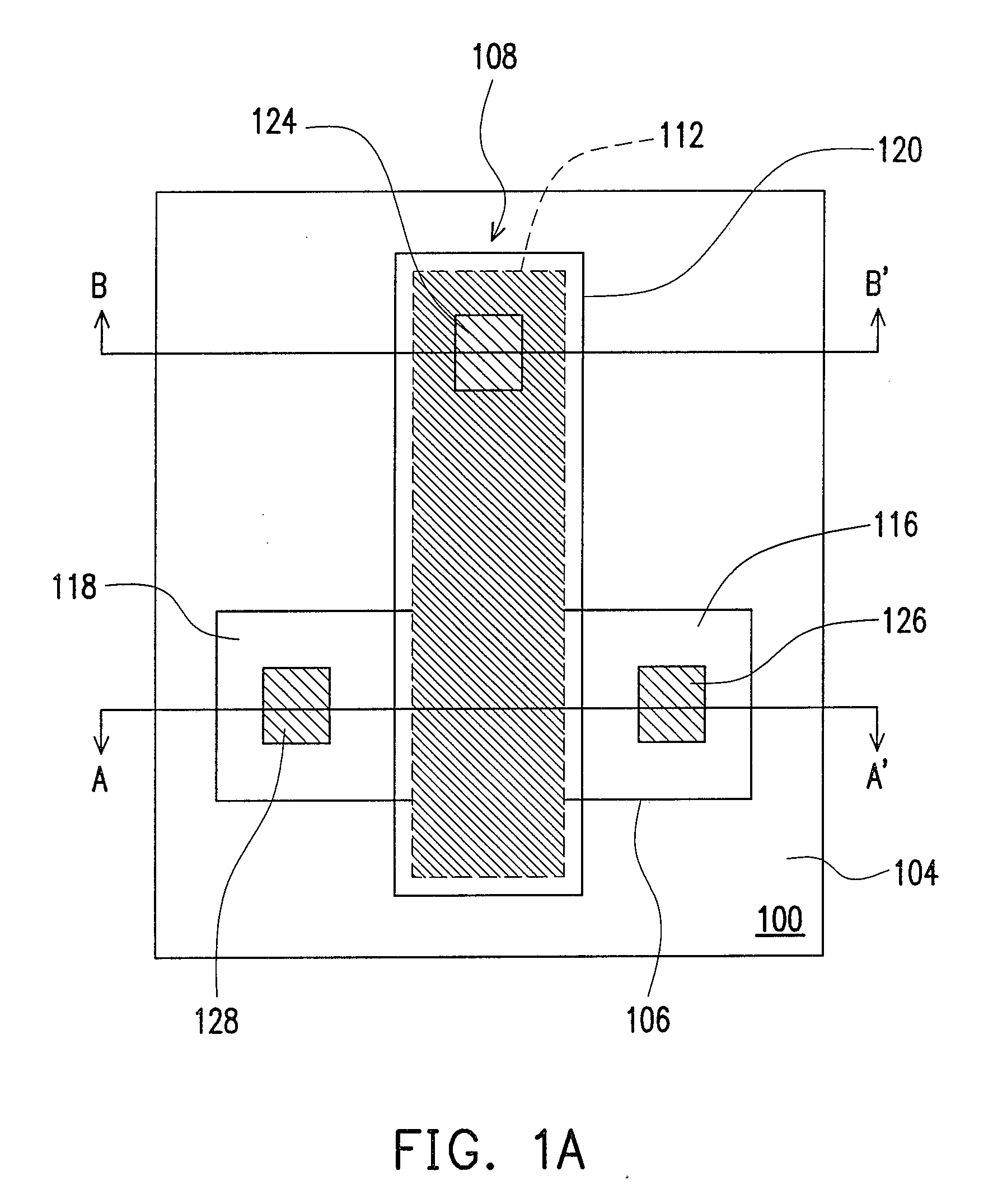

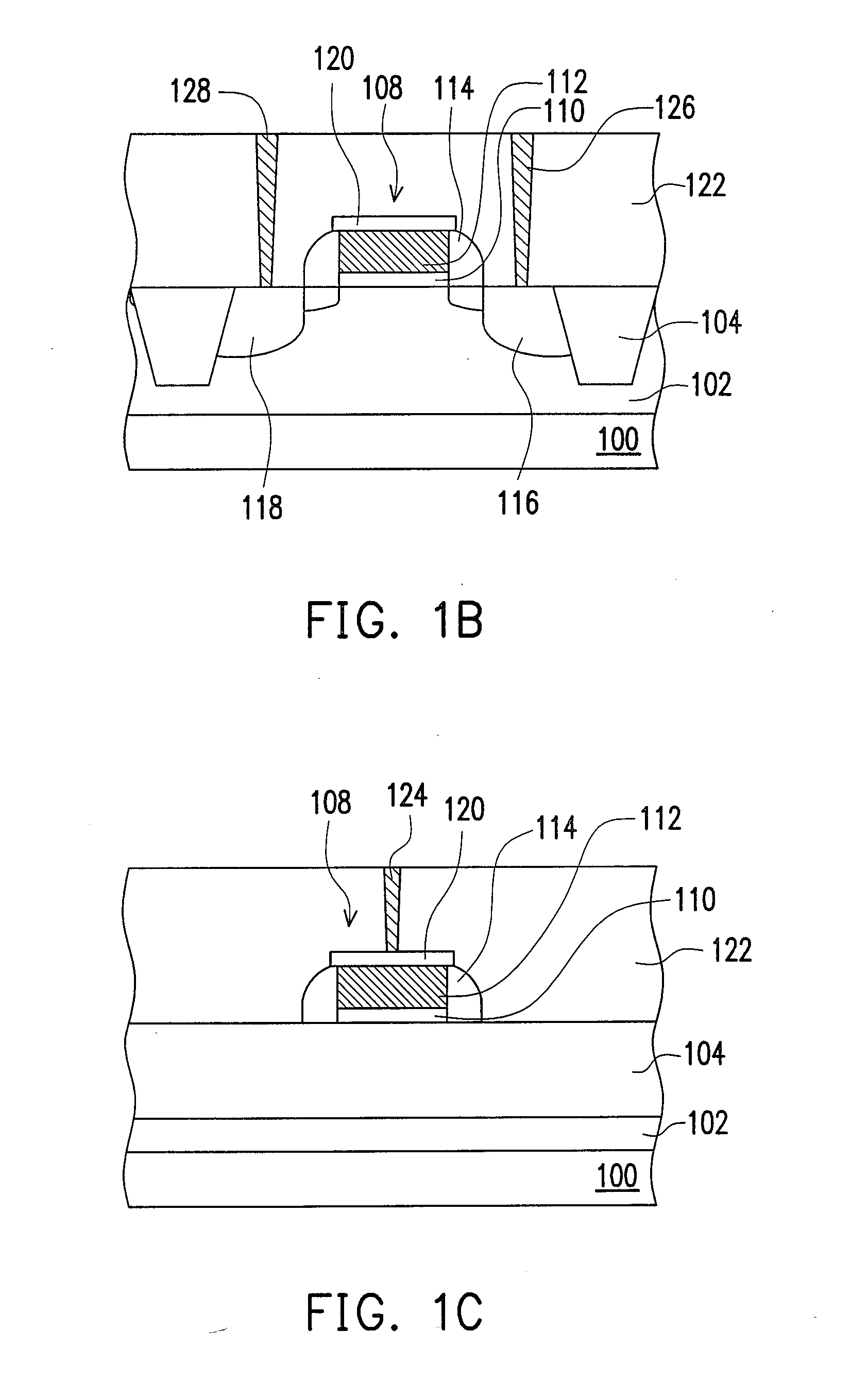

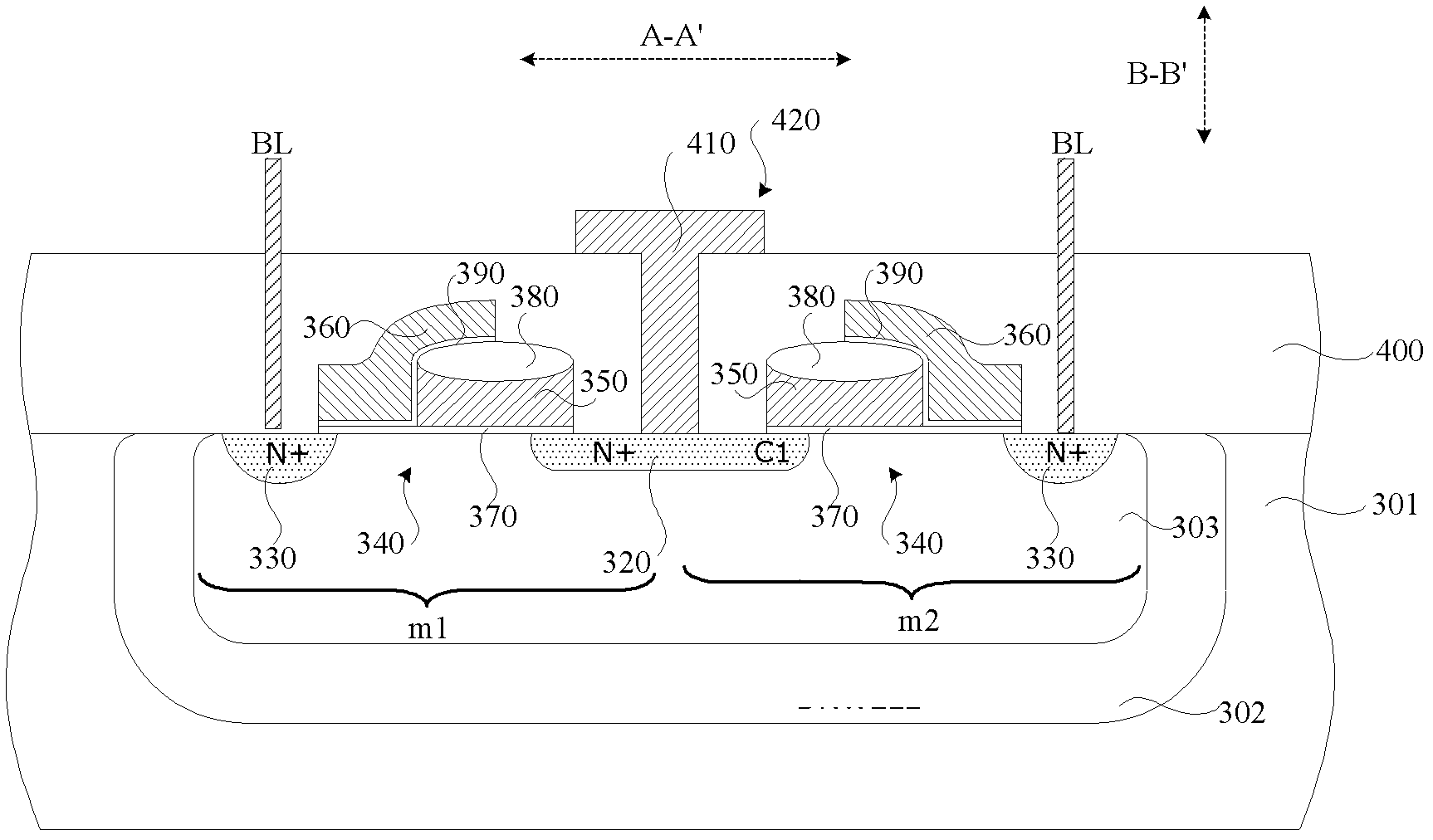

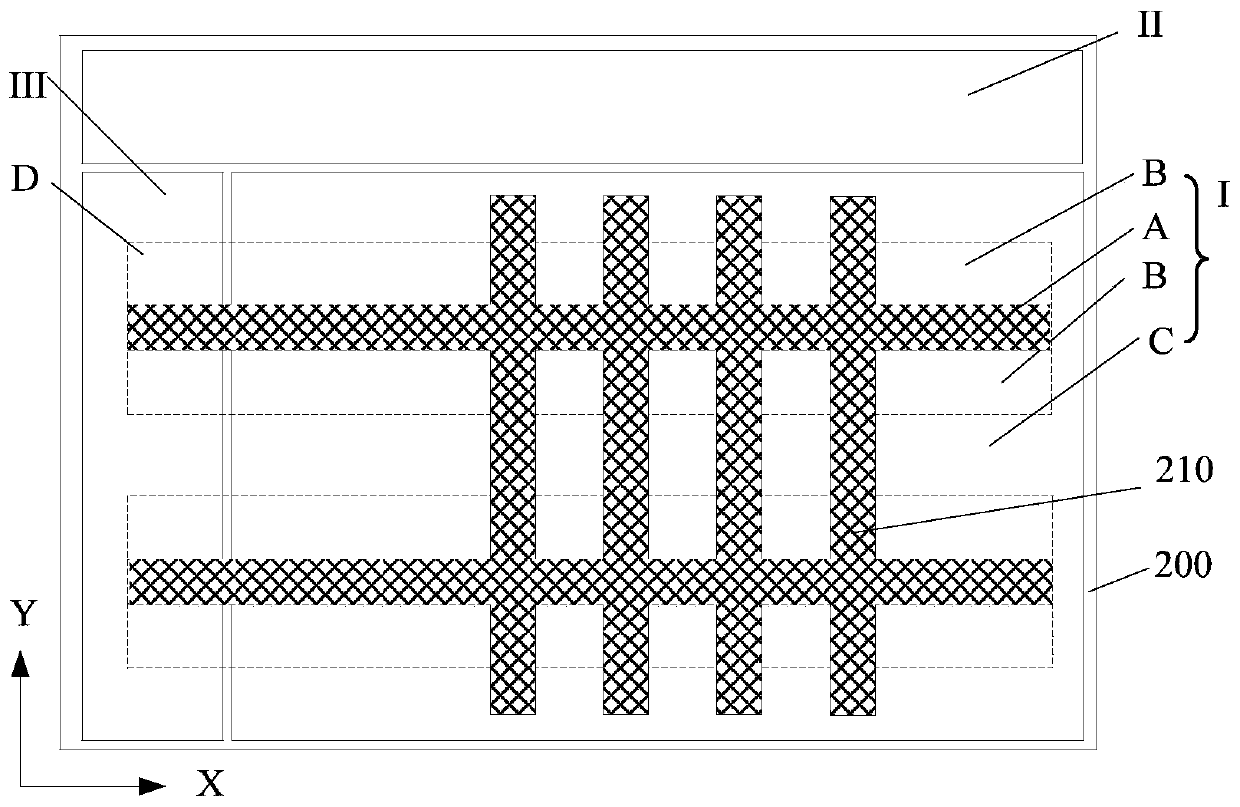

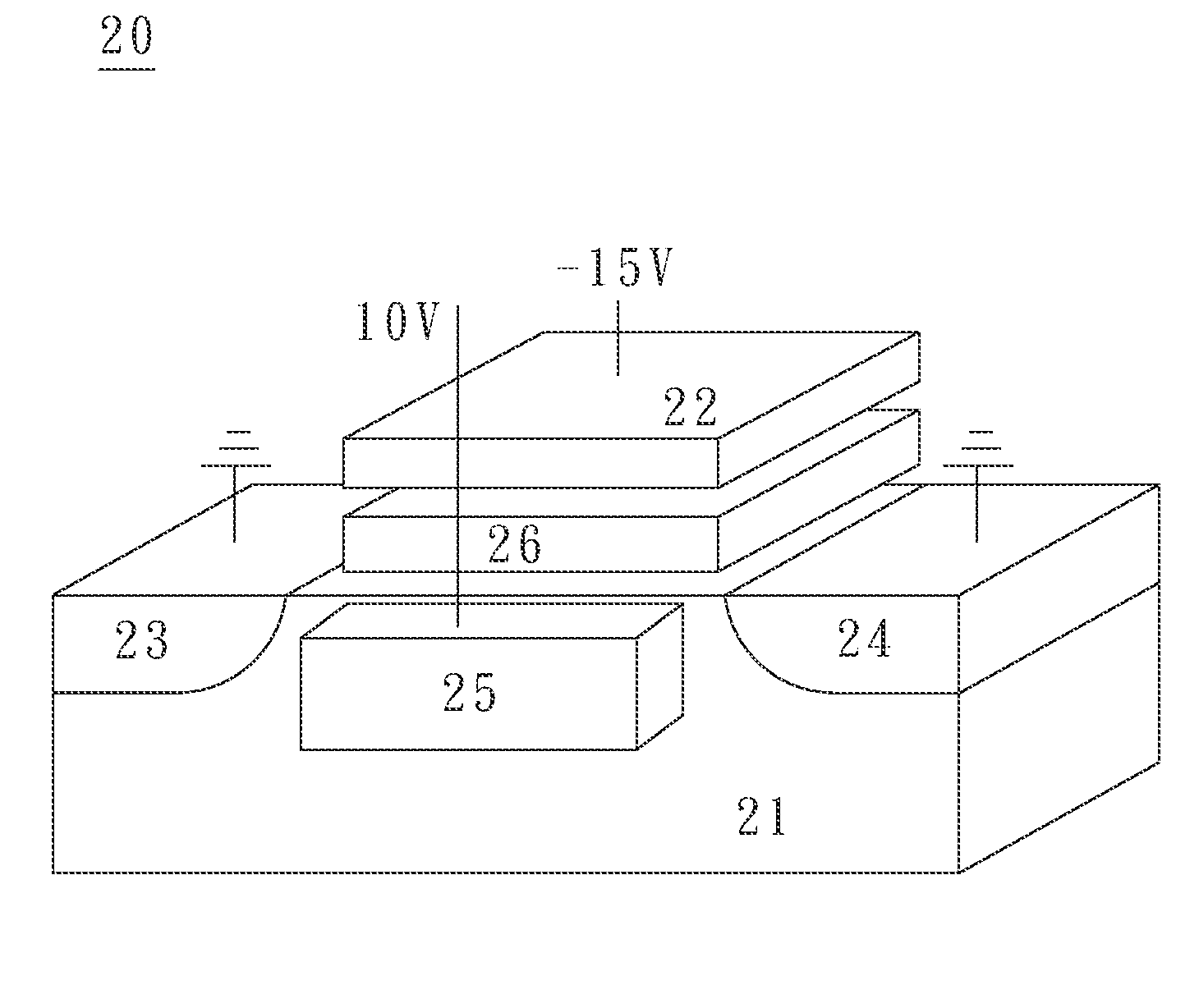

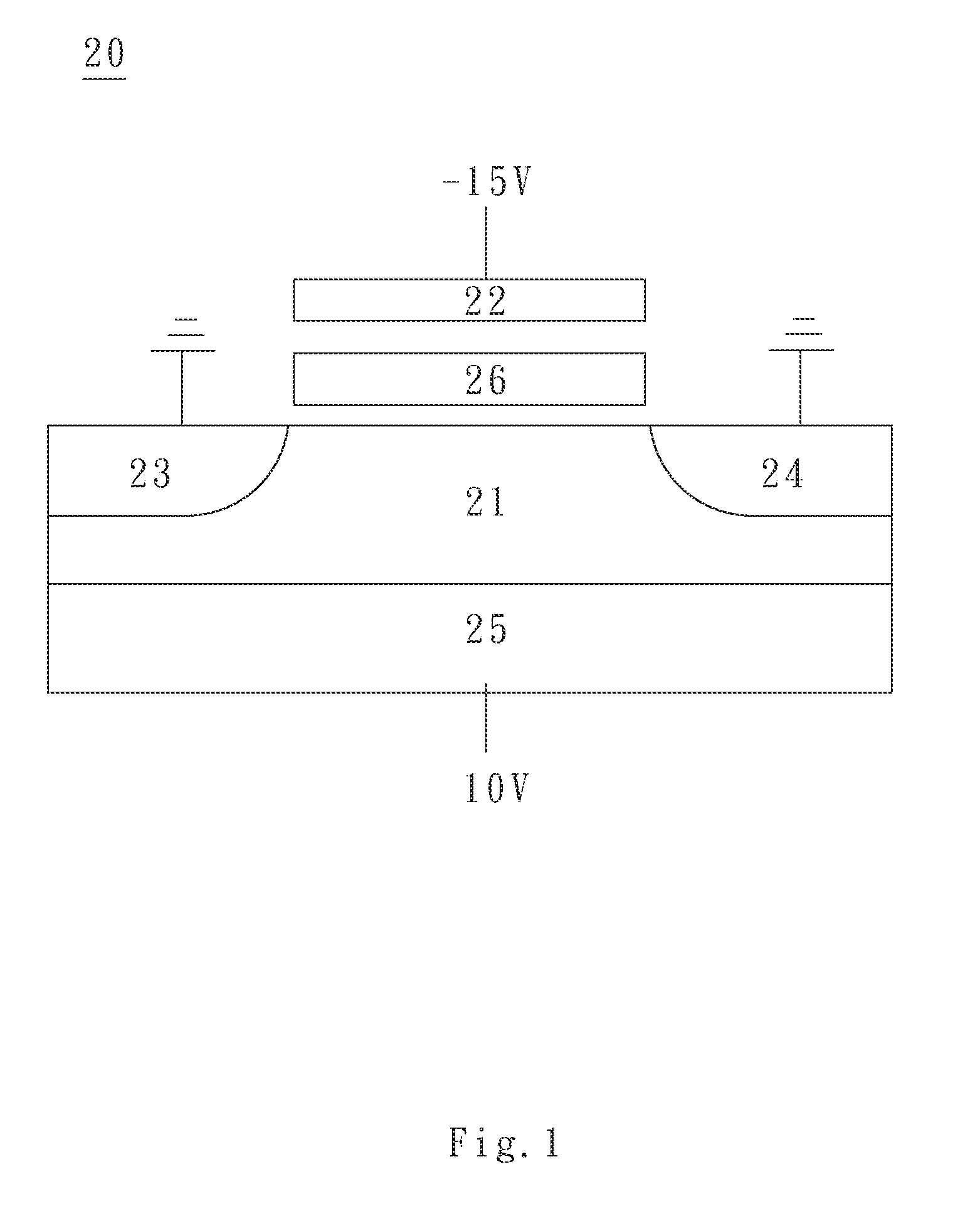

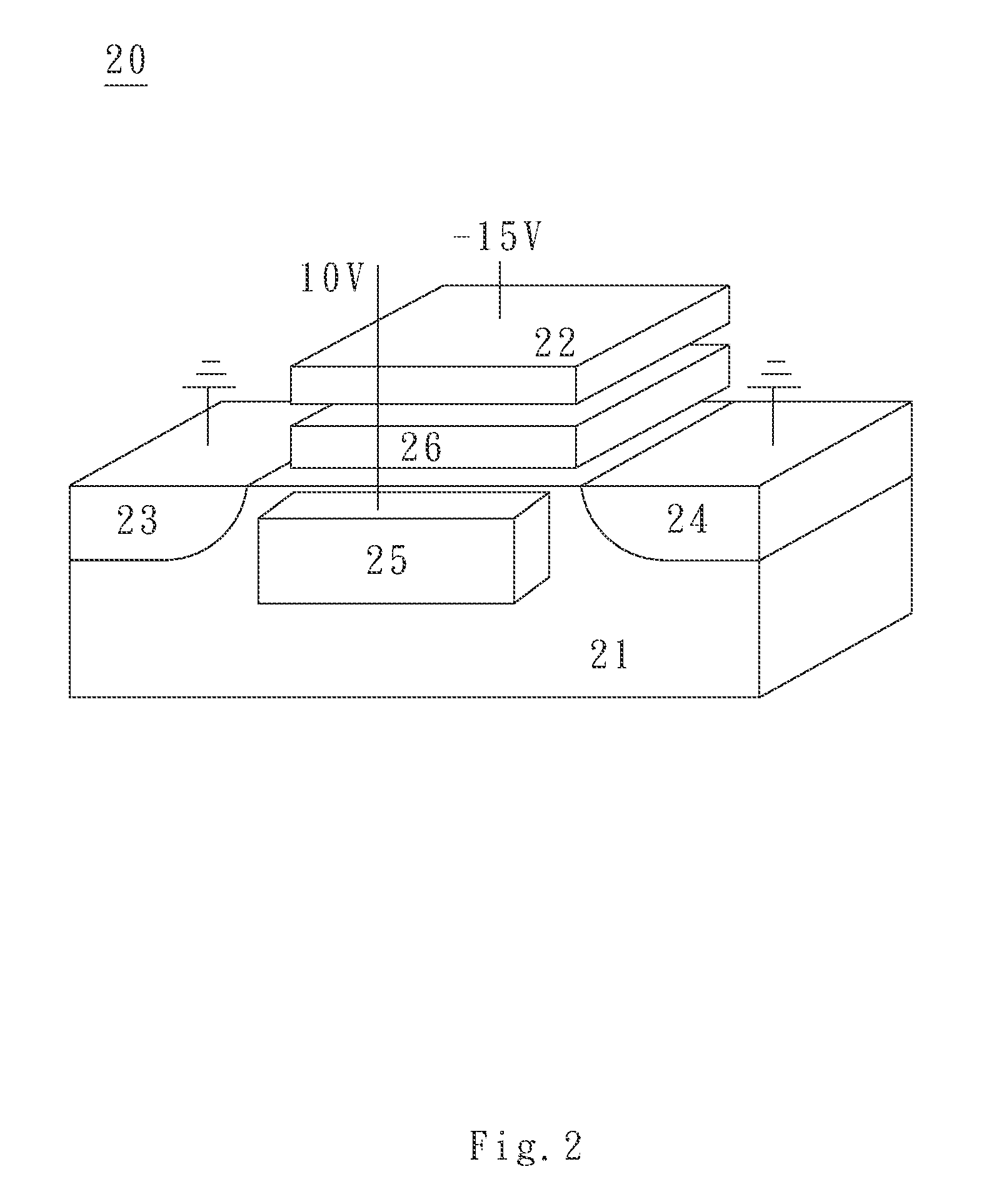

Non-volatile memory and fabricating method thereof

InactiveUS20080017917A1Increase integrationImprove reliabilityTransistorSolid-state devicesEngineeringNon-volatile memory

Owner:EMEMORY TECH INC

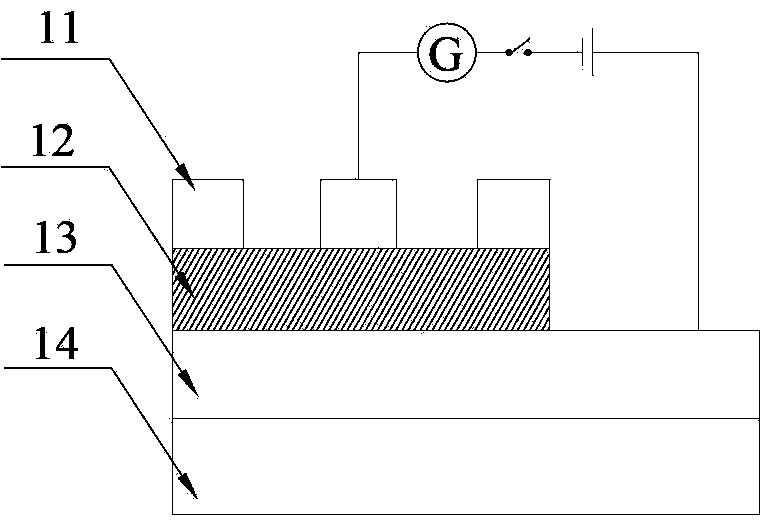

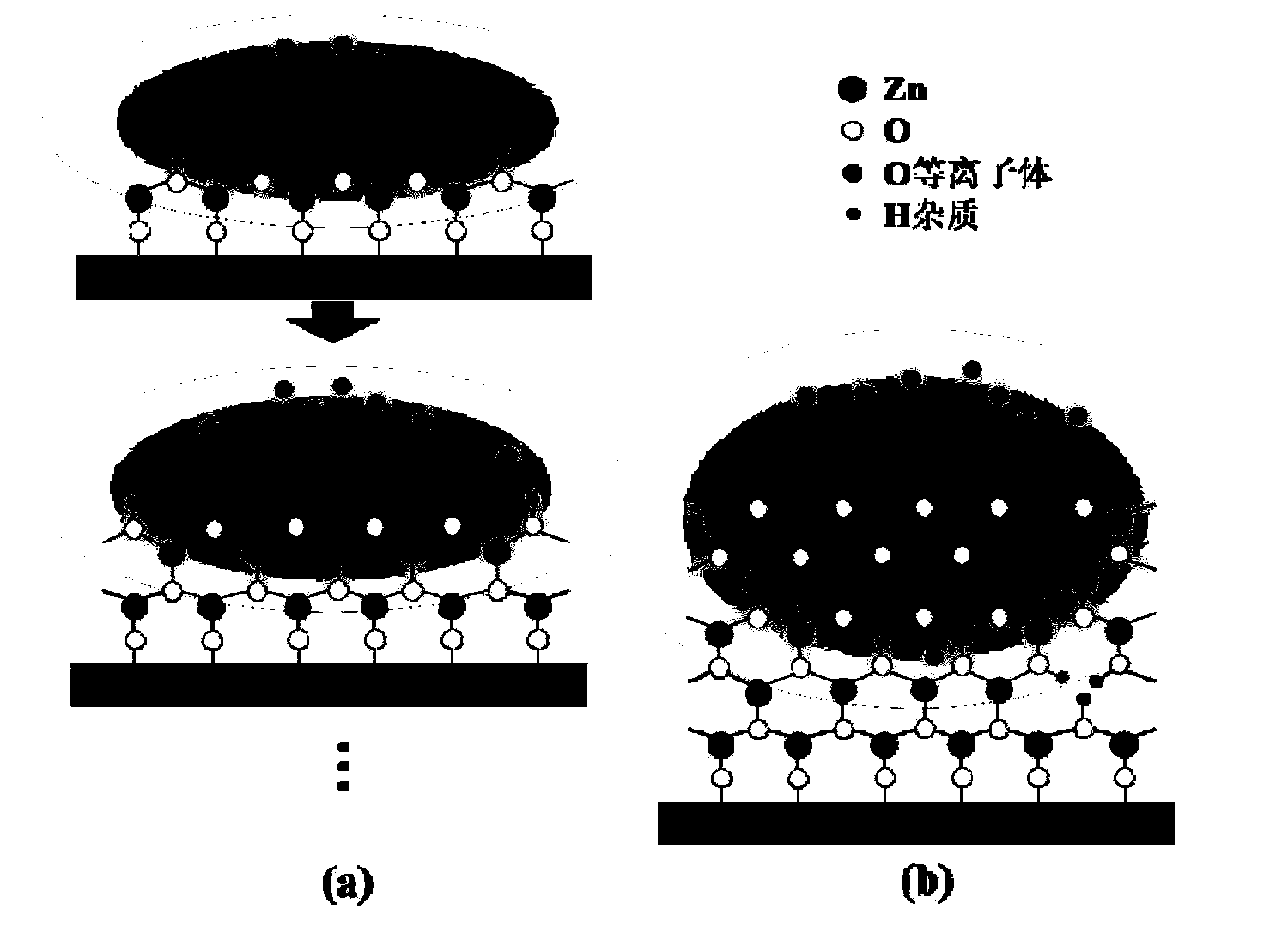

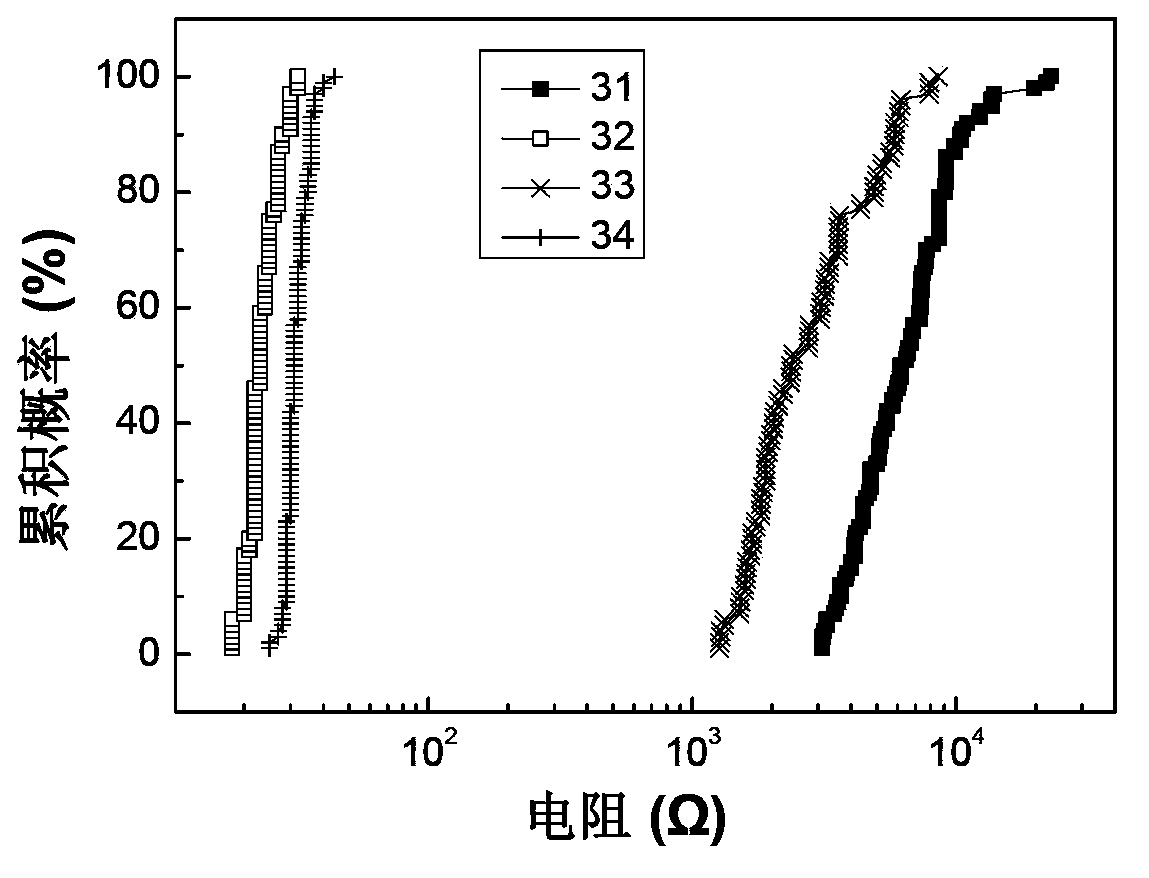

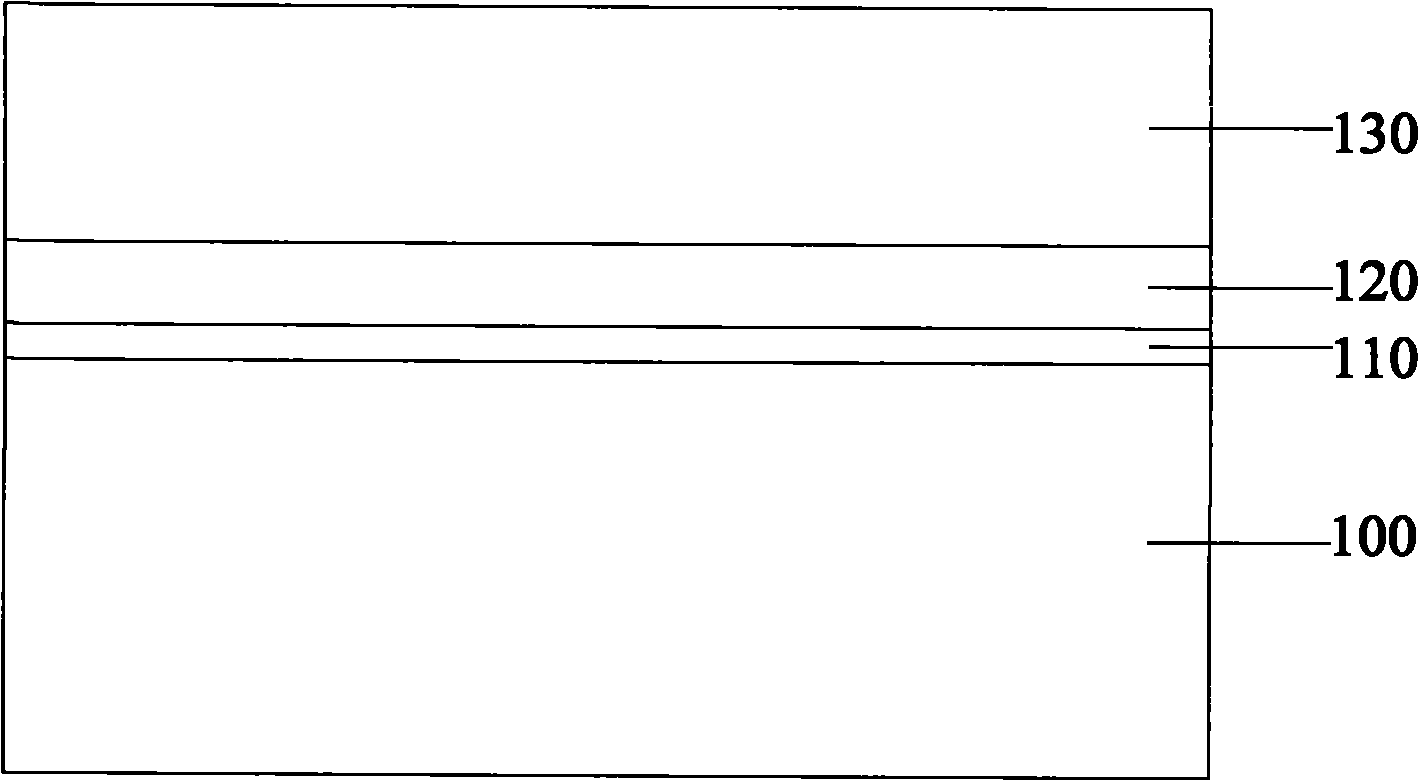

Preparation method for resistive random access memory

ActiveCN103441214AEfficient removalHigh on/off ratioElectrical apparatusElectrical resistance and conductanceStatic random-access memory

The invention discloses a preparation method for a resistive random access memory. The resistive random access memory comprises a bottom electrode, a resistance change dielectric layer material and a top electrode which are assembled in sequence. Preparation of the resistance change dielectric layer material includes the following steps that firstly, a first precursor, first inert gas, a second precursor and second inert gas are fed into a reactor in order, and a monolayer metallic oxide film is deposited on the bottom electrode through a cycle of hot atomic layer deposition; secondly, a plasma enhancement process is carried out on the film; finally, the steps are carried out circularly and alternately. In the preparation process of a resistance change dielectric layer, a brand new in-situ plasma enhancement hot atomic layer deposition technology is brought in, so the surface appearance and defects of the metallic oxide film can be adjusted on a large scale; the resistive random access memory obtained through the preparation method can achieve precision control over device resistance switching characteristics to enable the device switch ratio and erase / write voltage to be adjusted, and has excellent resistance change stability.

Owner:ZHEJIANG UNIV

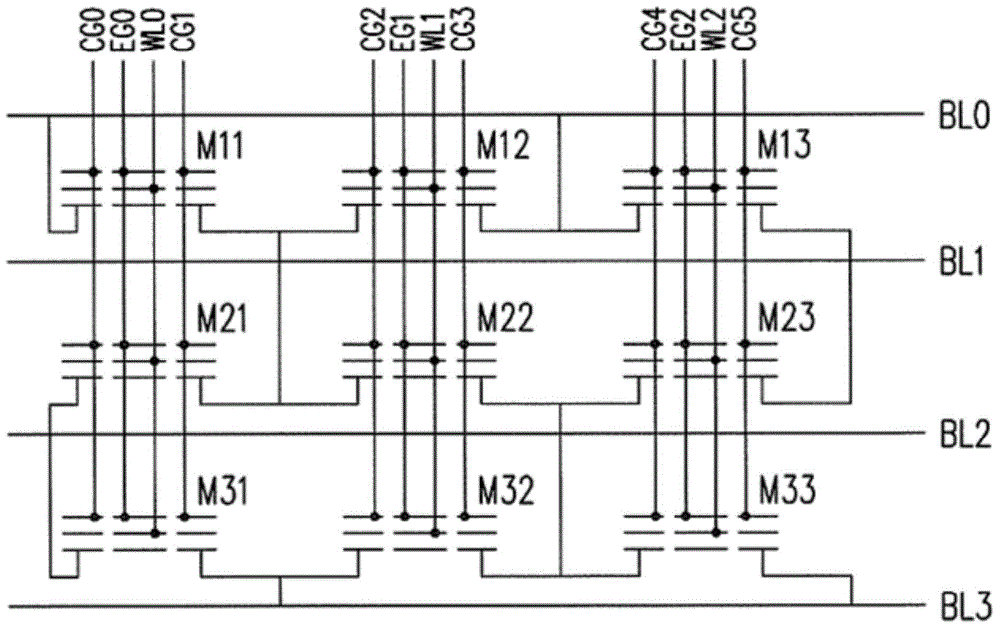

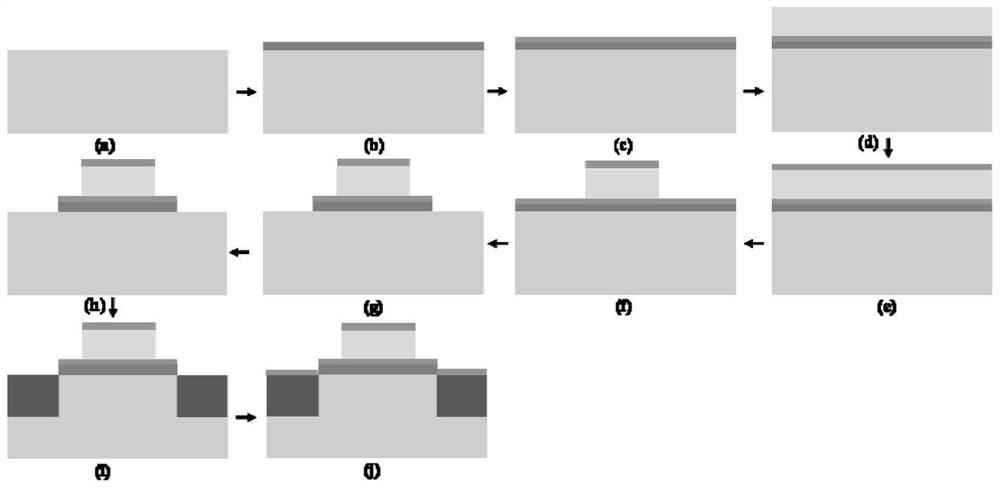

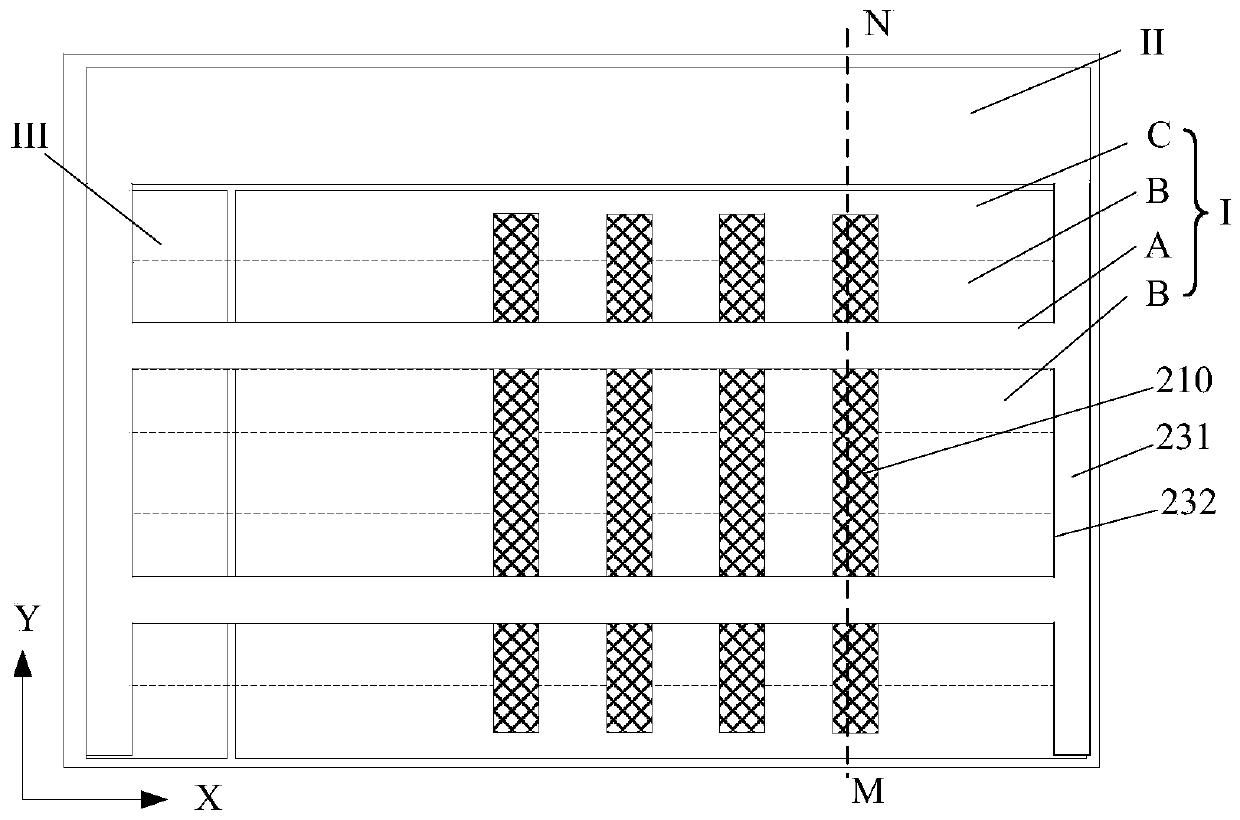

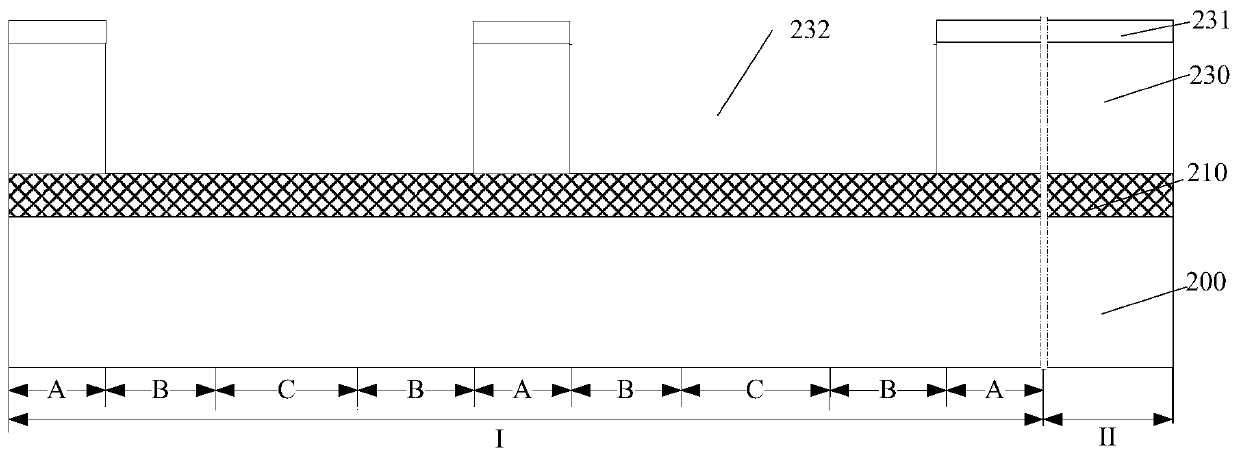

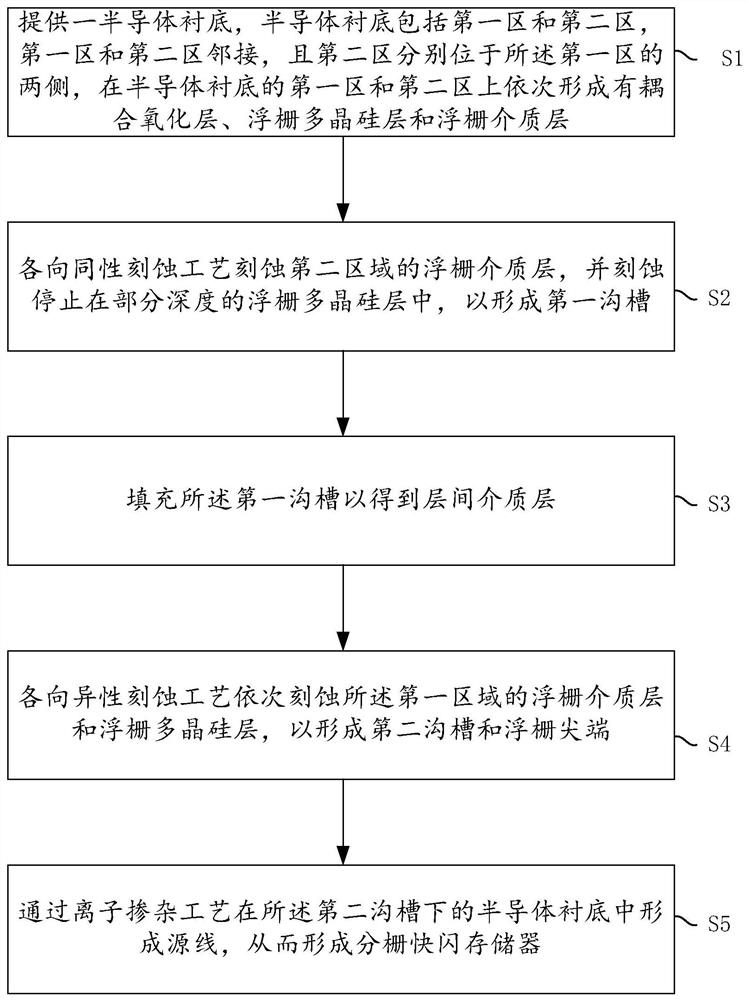

Manufacturing method of split-gate type flash memory of shared word line

ActiveCN101777521AThe electrical isolation performance remains unchangedReduce areaSemiconductor/solid-state device manufacturingBit lineComputer science

The invention provides manufacturing method of a split-gate type flash memory of a shared word line. The split-gate type flash memory of the obtained shared word line enables two memory bit units to share one word line, realizes the read, programming and the erasure of the memory bit units by applying different working voltages to the word line, two control gates and a source drain area, can effectively reduce the area of a small chip under the condition of keeping the electric isolation of the chip unchanged due to a shared bit line structure and also prevent the problem of erasure and is beneficial to strengthening a tunnelling electric field when a device is erased due to a self-aligned structure formed by a floating gate positioned on a top end and the work line, thereby effectively reducing the erasure voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

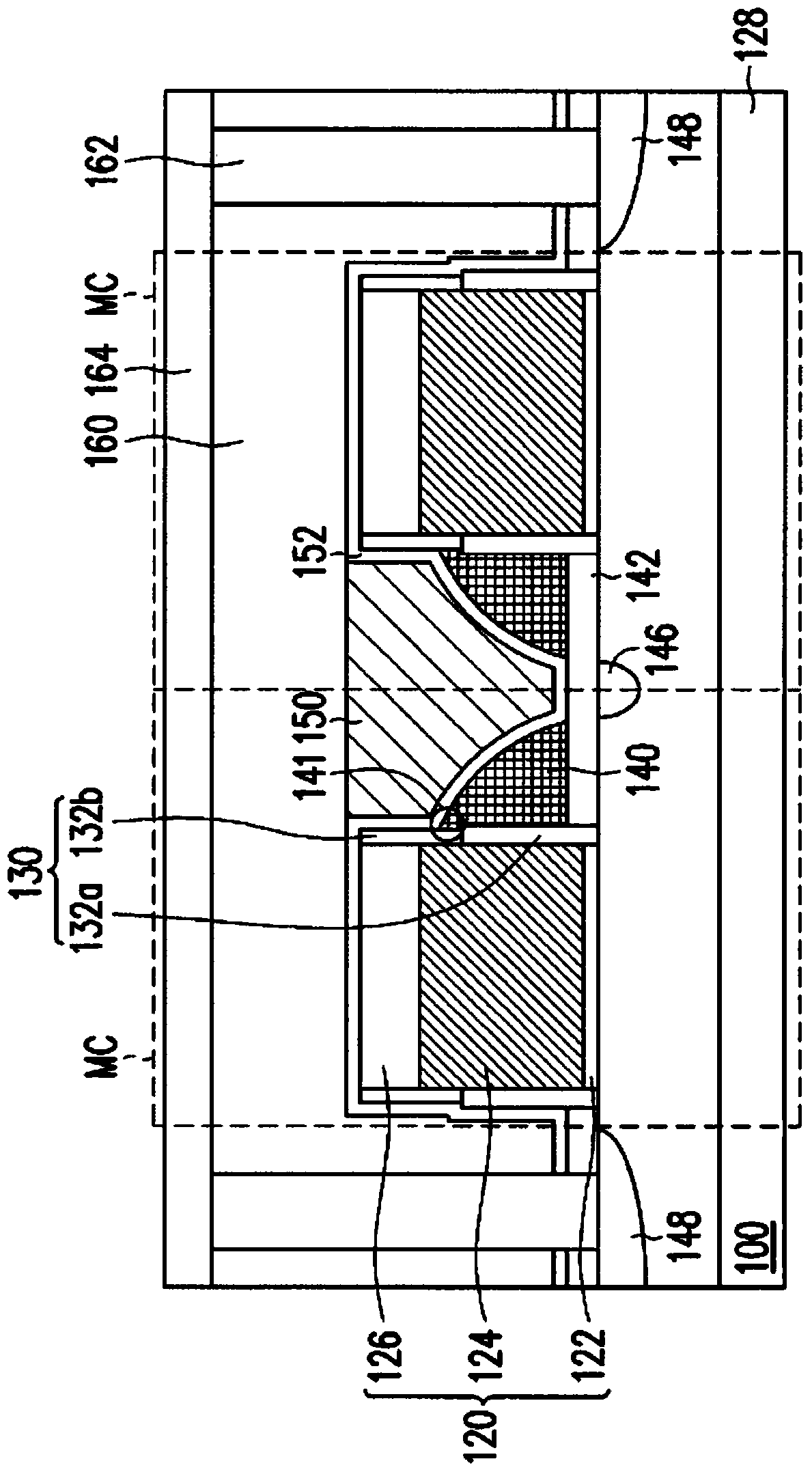

Nonvolatile memory

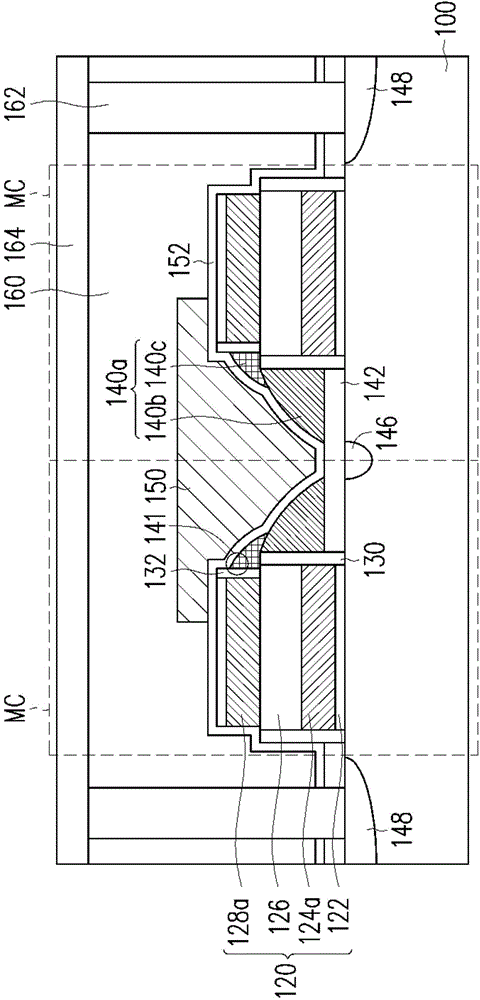

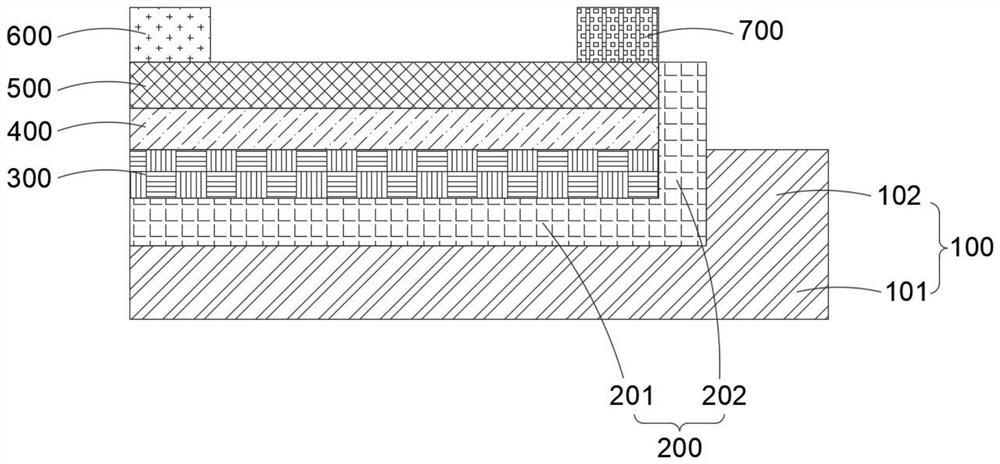

ActiveCN106206588APromote accumulationThe overall thickness is thinSolid-state devicesSemiconductor devicesGate dielectricInsulation layer

The invention provides a nonvolatile memory. The nonvolatile memory is provided with a storage unit, wherein the storage unit is provided with a stack structure, a first floating gate, a second floating gate, erase gate dielectric layers, auxiliary gate dielectric layers, a first doping region, a second doping region, a first control gate and a second gate, wherein the stack structure comprises a gate dielectric layer, an auxiliary gate, an insulation layer and an erase gate which are sequentially arranged, the first floating gate and the second floating gate are respectively arranged on side walls of two sides of the stack structure, the erase gate dielectric layers are arranged between the erase gate and the first floating grid and between the erase gate and the second floating grid, the auxiliary gate dielectric layers are arranged between the auxiliary gate and the first floating gate and between the auxiliary gate and the second floating gate, the first doping region and the second doping region are respectively arranged at two sides of the stack structure, the first floating gate and the second floating gate, and the first control gate and the second gate are respectively arranged on the first floating gate and the second floating gate. By the nonvolatile memory, low-voltage operation can be performed, and the reliability of a semiconductor component is further improved.

Owner:IOTMEMORY TECH +1

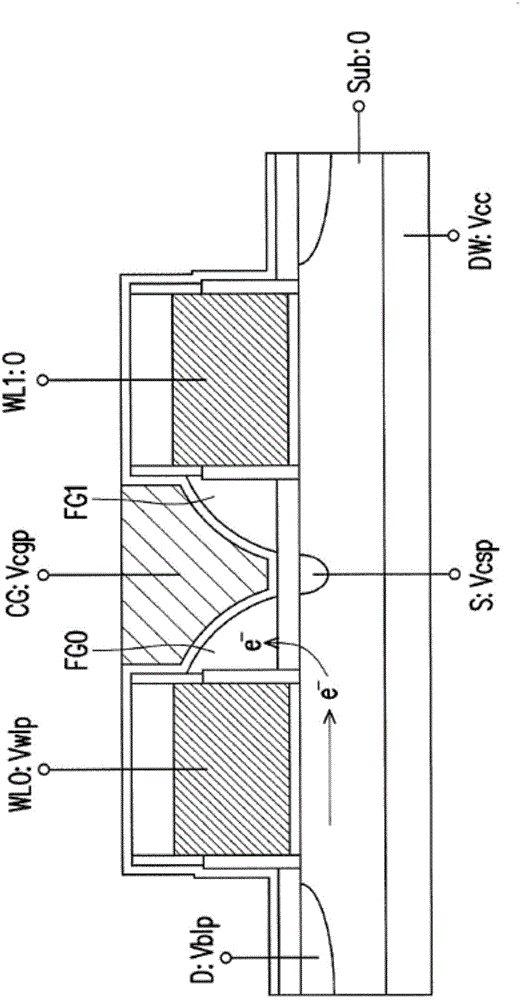

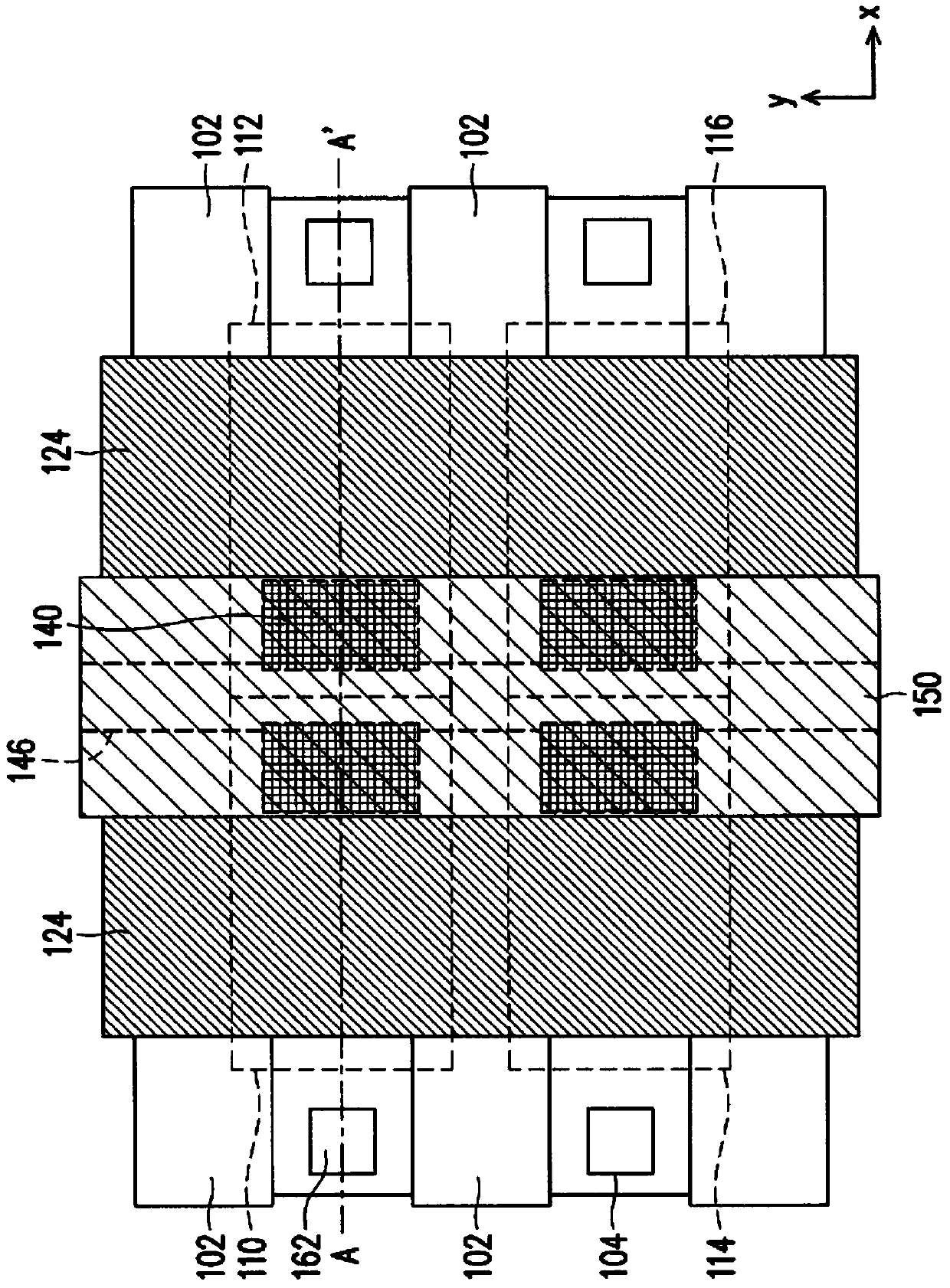

Splitting grid memory cell and operation method thereof

ActiveCN102437161ASmall sizeReduce the erase voltageSolid-state devicesRead-only memoriesDiffusionSemiconductor

A splitting grid memory cell and an operation method thereof are disclosed. The memory cell comprises: a semiconductor substrate, a floating grid, a control grid and a selection grid, wherein a first doped region, a second doped region and a third doped region are successively formed on the semiconductor substrate; a first diffusion region and a second diffusion region are formed in the third doped region; the floating grid is formed on the semiconductor substrate between the first diffusion region and the second diffusion region; a first side of the floating grid is overlapped with parts of the first diffusion region; the control grid is formed on the semiconductor substrate between a second side of the floating grid and the second diffusion region; an insulating oxide layer is formed between the control grid and the second side of the floating grid; the selection grid is formed on the semiconductor substrate in the first diffusion region; a doped type of the first doped region is the same with the doped type of the third doped region and is opposite to the doped type of the second doped region. By using the memory cell and the method of the invention, a size of the memory cell can be effectively reduced; a quality of the memory cell can be improved and manufacturing costs can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

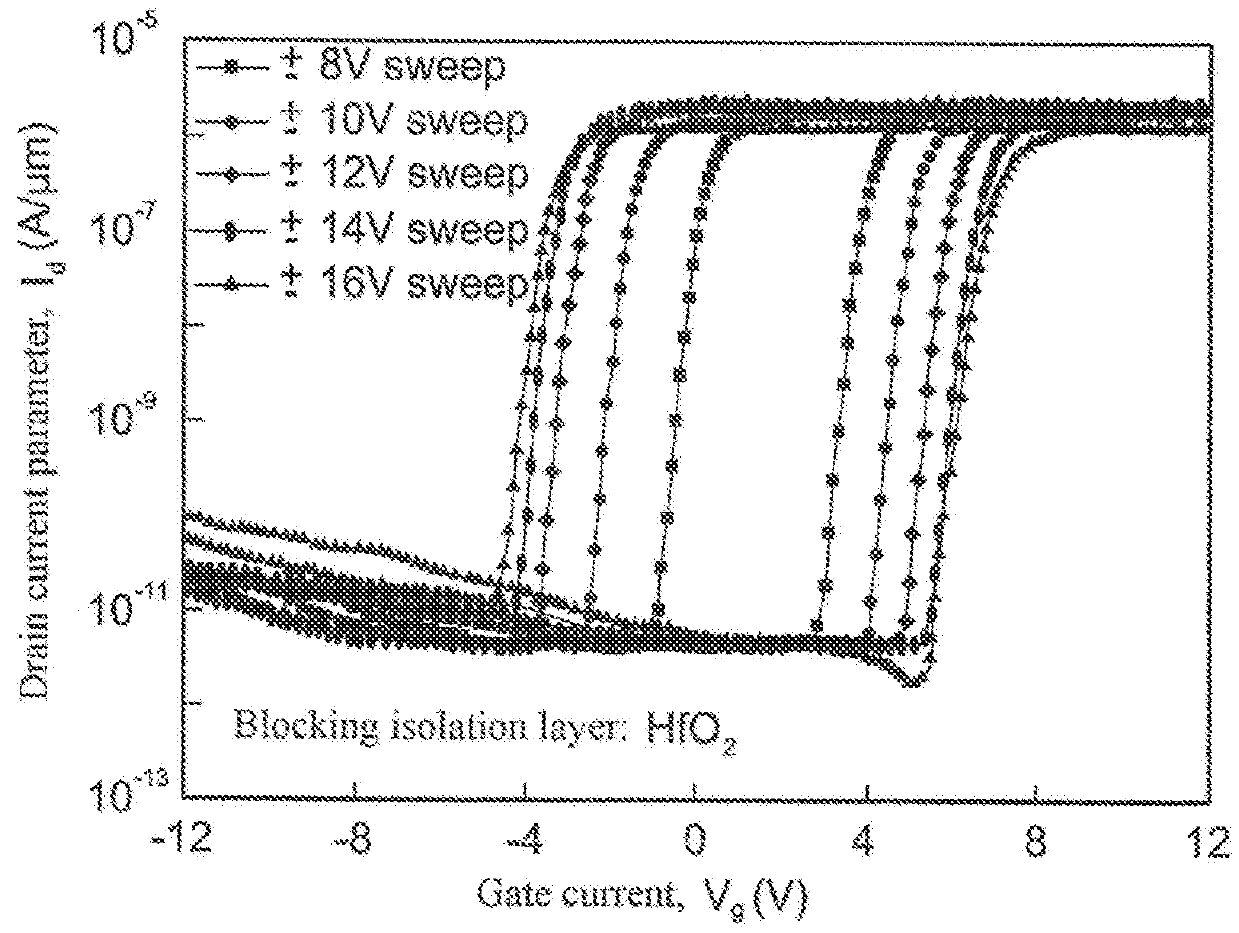

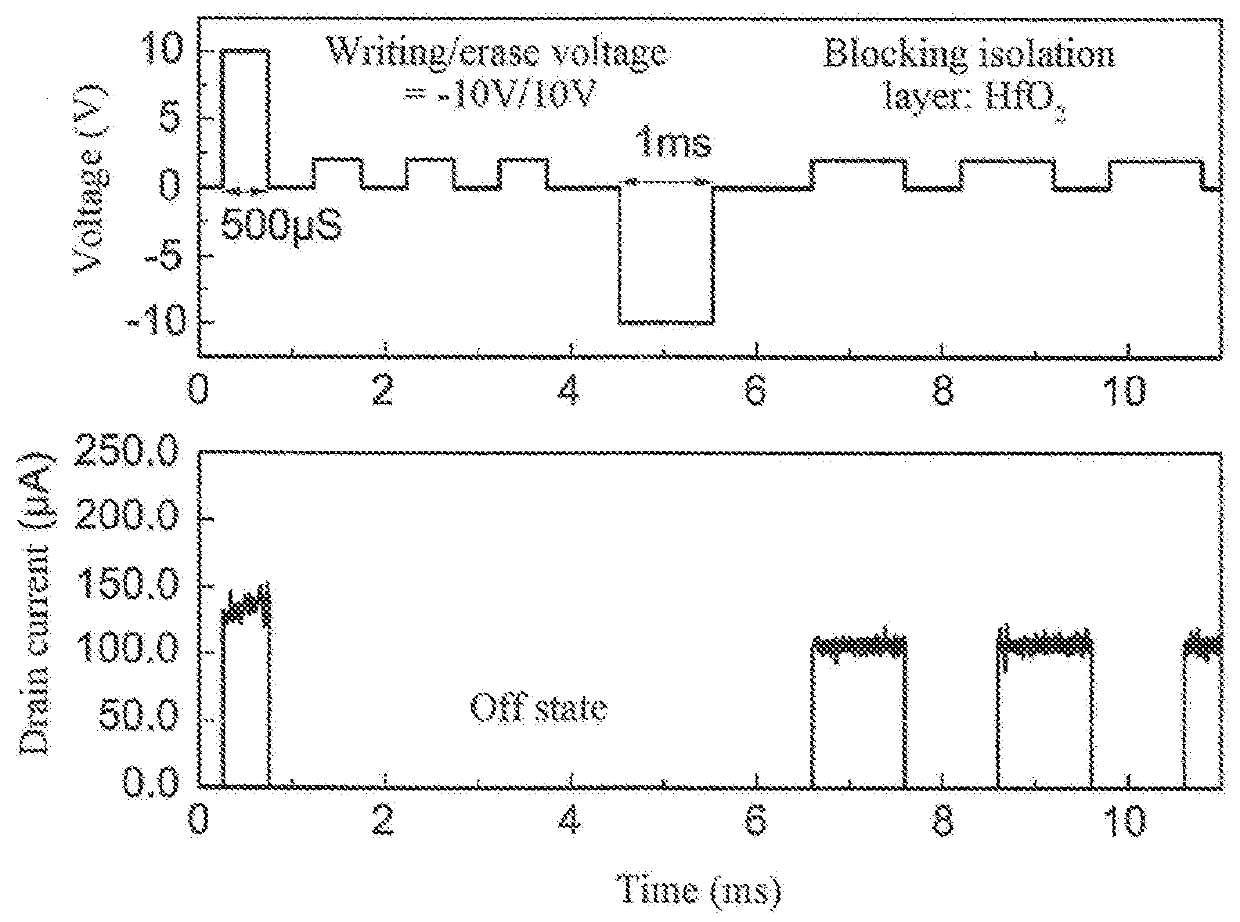

Flash memory structure and method of manufacturing the same

ActiveUS20180182769A1Reduce writingReduce the erase voltageSolid-state devicesRead-only memoriesCapacitanceSemiconductor materials

A flash memory structure and a method of making the same are provided. The flash memory structure comprises a substrate, a source, a drain, a tunnel isolation layer, a ferroelectric-charge-trapping layer, at least one blocking isolation layer and at least one gate. The substrate is made of a semiconductive material. The source is formed on the substrate. The drain is formed on the substrate and spaced apart from the source. The tunnel isolation layer is formed on the substrate. The ferroelectric-charge-trapping layer is formed on the tunnel isolation layer and contains a charge-trapping layer and a ferroelectric negative-capacitance effect layer. The at least one blocking isolation layer is formed on the ferroelectric-charge-trapping layer. The at least one gate is formed on the blocking isolation layer. The ferroelectric negative-capacitance effect layer is made of a material with the ferroelectric negative-capacitance effect.

Owner:NATIONAL TAIWAN NORMAL UNIVERSITY

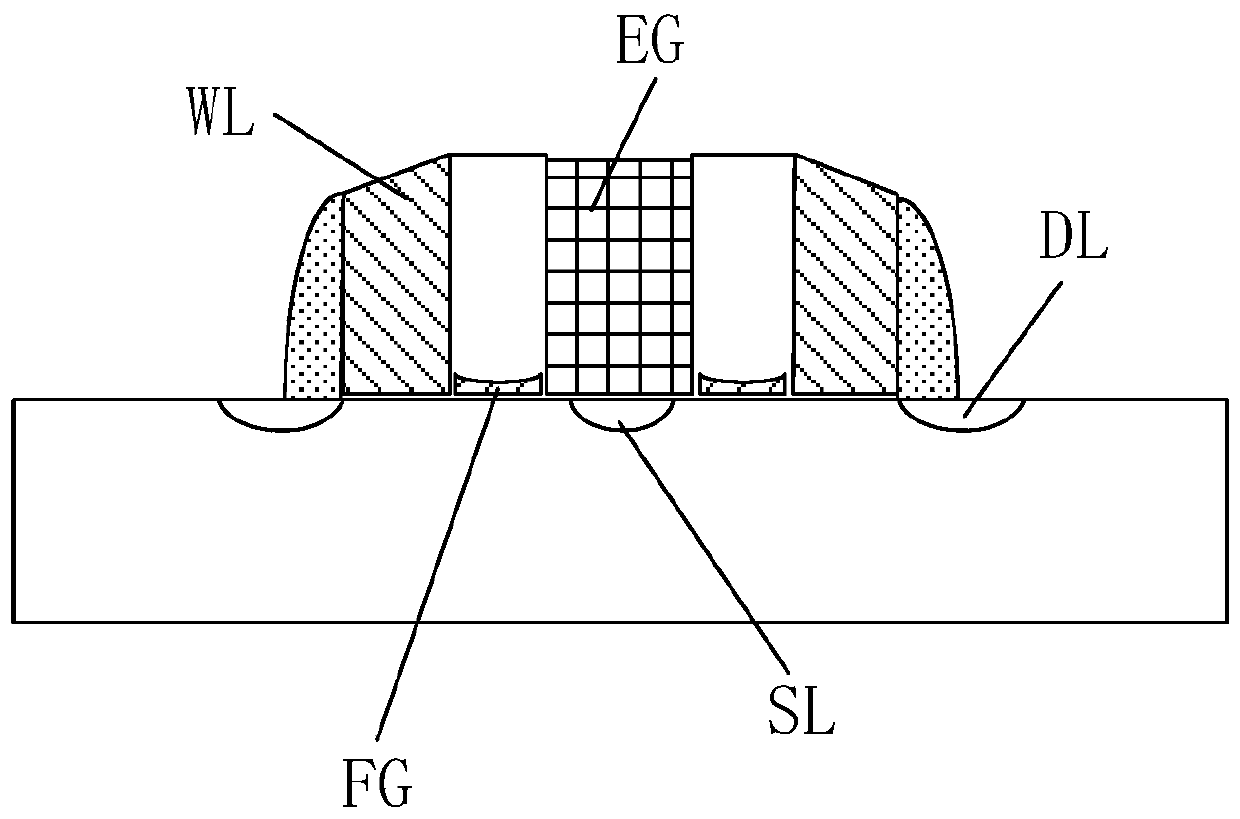

Method for improving efficiency of erasing floating gate

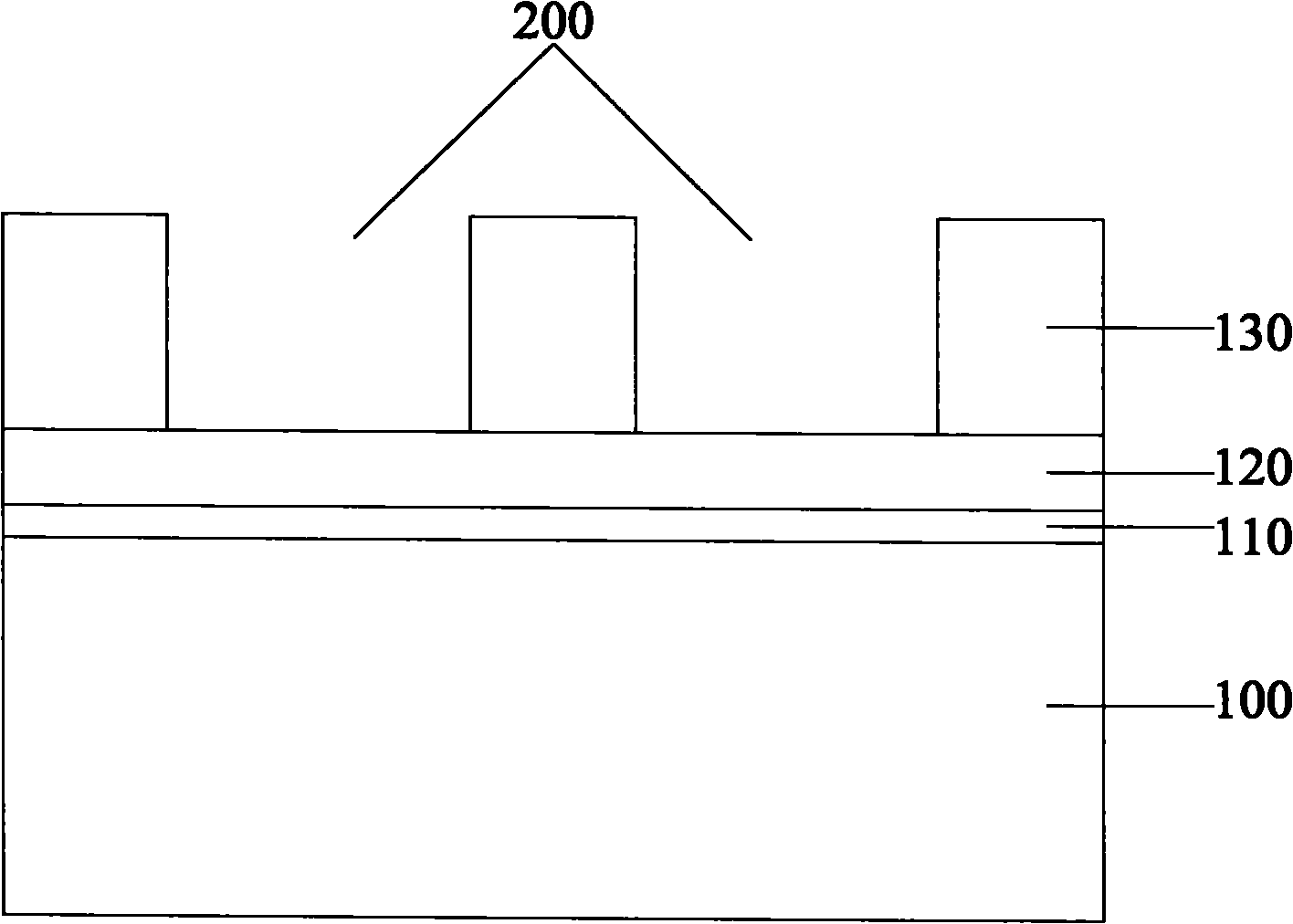

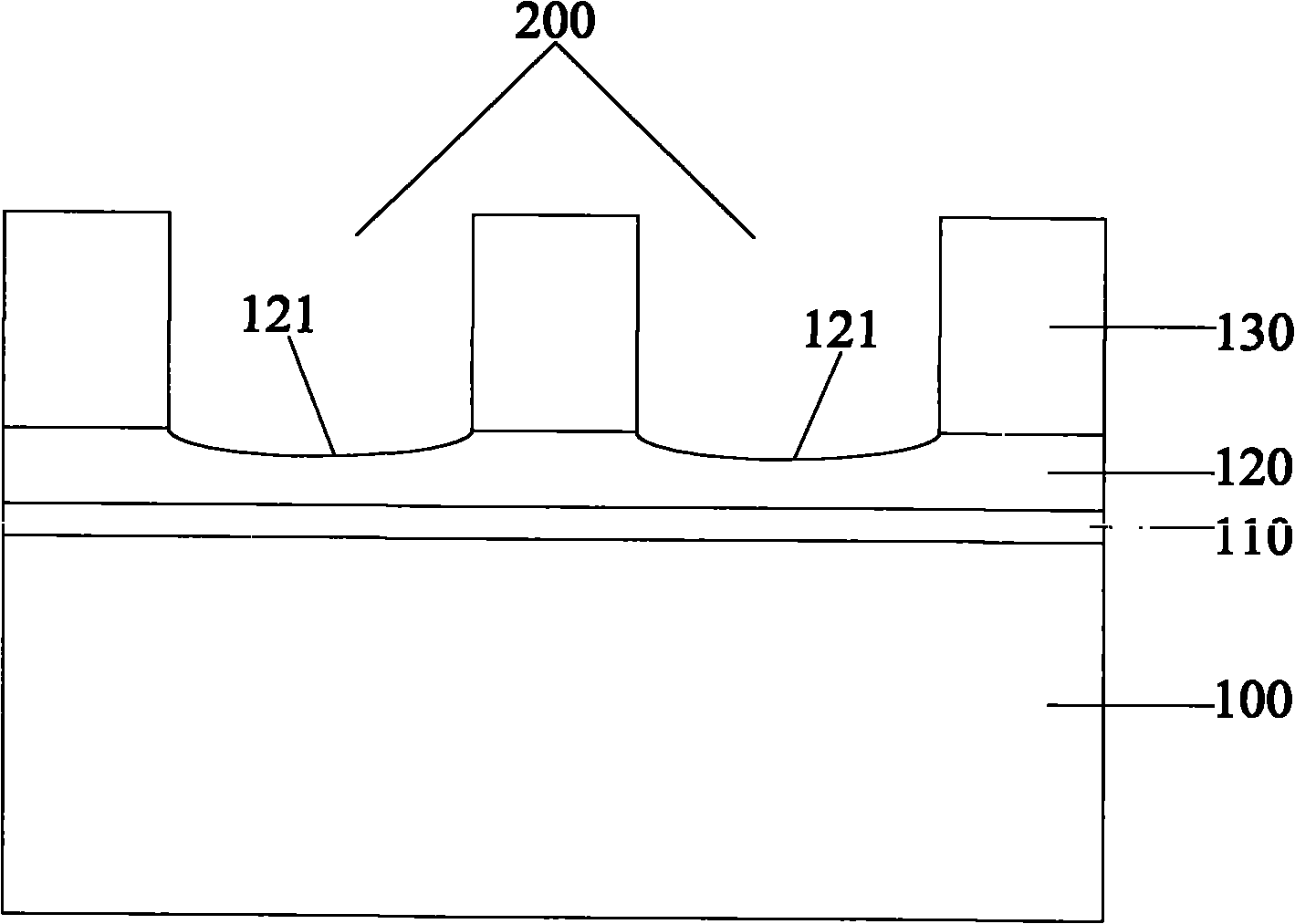

ActiveCN101882576AEnhanced electric fieldReduce the erase voltageSemiconductor/solid-state device manufacturingSilicon oxidePhotoresist

The invention discloses a method for improving the efficiency of erasing a floating gate, which comprises the following steps: sequentially forming a floating gate (FG) oxide layer, a FG polycrystalline silicon layer, an oxide layer-nitride layer-oxide layer (ONO) dielectric layer, a control gate (CG) polycrystalline silicon layer, a CG silicon nitride layer, a CG silicon oxide layer and a CG silicon nitride hard mask layer on a semiconductor substrate; coating photoresist on the CG silicon nitride hard mask layer, and patterning the photoresist; taking the patterned photoresist as a mask, and sequentially etching the CG silicon nitride hard mask layer, the CG silicon oxide layer, the CG silicon nitride layer, the CG polycrystalline silicon layer and the ONO dielectric layer to form two CGs; forming a CG side wall layer at two sides of each CG; forming a sacrificial layer at the outside of each CG side wall layer; taking the CG side wall layers, the sacrificial layer and the CG as masks, and etching the FG polycrystalline silicon layer to form FG; removing the sacrificial layer; and sequentially forming the oxide layer and depositing the polycrystalline silicon film outside the CG side wall layer and the FG, and finally forming the erasing gate EG by the polycrystalline silicon film. The method can effectively improve the efficiency of erasing the floating gate.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

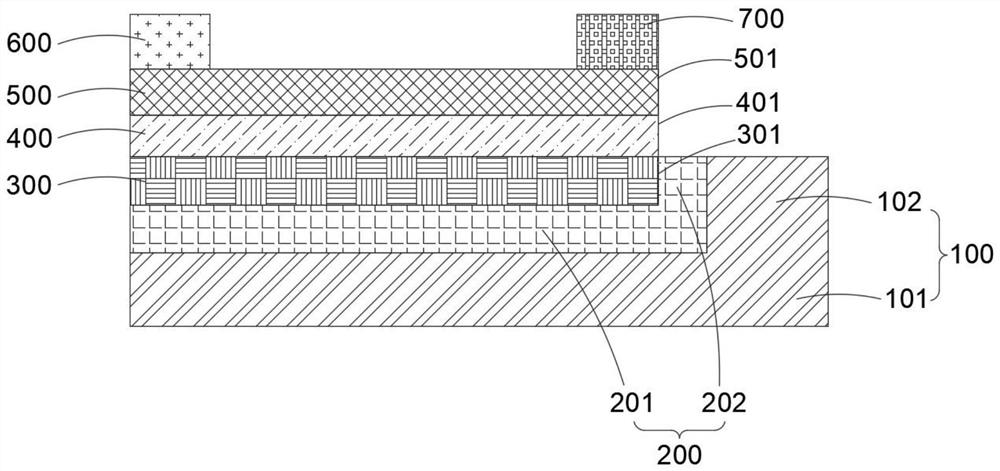

Nonvolatile memory manufacturing method thereof

ActiveCN105990360AHighly integratedThe overall thickness is thinSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

The invention provides a nonvolatile memory. The nonvolatile memory is provided with a storage unit, wherein the storage unit is provided with a stacked structure, floating gates, a tunneling dielectric layer, an erasing gate dielectric layer, an auxiliary gate dielectric layer, a source electrode region, a drain electrode region, control gates and an inter-gate dielectric layer; the stacked structure is provided with successively arranged gate dielectric layer, auxiliary gates, insulating layer and erasing gates; the floating gates are arranged at the side wall of the first side of the stacked structure; the tunneling dielectric layer is arranged below the floating gates; the erasing gate dielectric layer is arranged between the erasing gates and the floating gates; the auxiliary gate dielectric layer is arranged between the auxiliary gates and the floating gates; the source electrode region and the drain electrode region are respectively arranged at two sides of the stacked structure and the floating gates; the control gates are arranged on the source electrode region and the floating gates; and the inter-gate dielectric layer is arranged between the control gates and the floating gates.

Owner:IOTMEMORY TECH +1

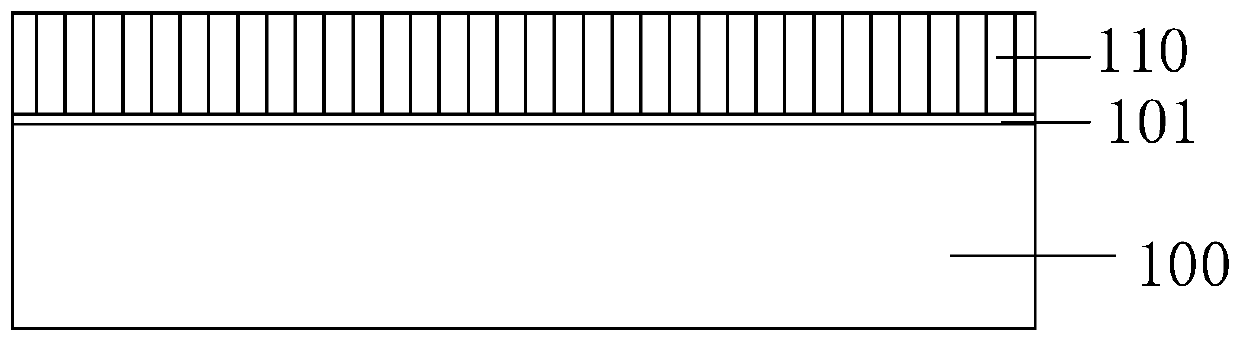

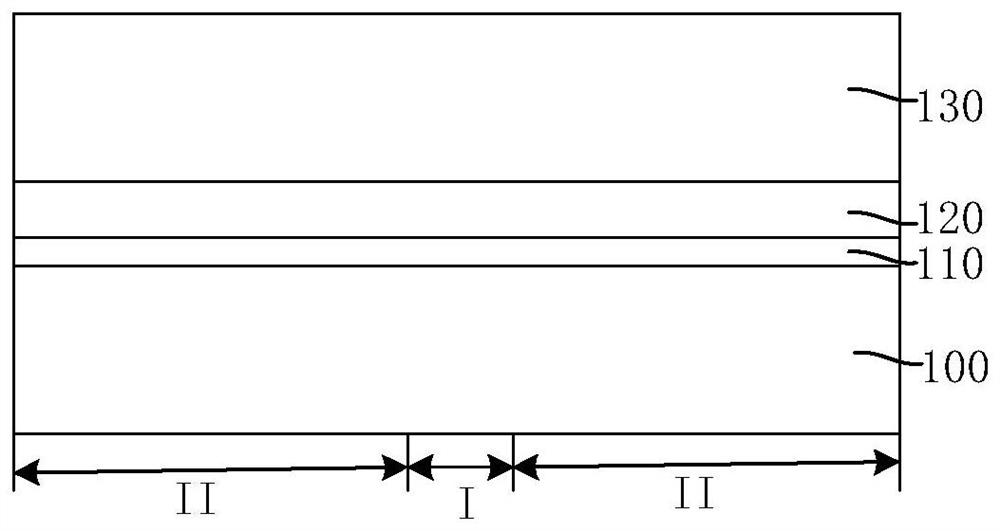

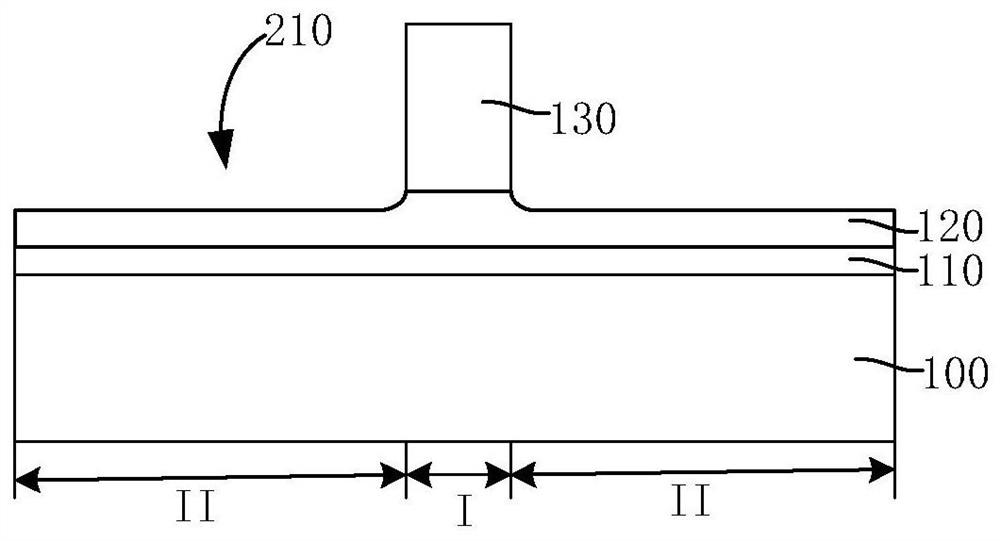

Memory and formation method thereof

ActiveCN109712981ASimple processReduced process flowSolid-state devicesSemiconductor devicesBit lineDielectric layer

A memory and a formation method thereof are disclosed. The method includes the following steps: a substrate is provided, the substrate includes erasure regions, floating gate regions and word line bitline regions, wherein the floating gate regions are located on both sides of the erasure regions, and the word line bit line regions are located on both sides of the erasure regions and the floatinggate regions; a floating grid electrode structure membrane and a dielectric layer located on the floating grid electrode structure membrane are formed on the substrate, and a first opening exposing the floating grid electrode structure membrane of the floating gate regions and the word line bit line regions are disposed in the dielectric layer; a first side wall is formed on the side wall of the first opening; a control grid electrode membrane is formed on the bottom of the first opening; a second side wall is formed on the side wall of the first side wall; the control grid electrode membraneand the floating grid electrode structure membrane exposed by the first side wall, the second side wall, and the dielectric layer are removed to form a floating gate structure layer, a control grid electrode layer and a second opening; the dielectric layer and the floating gate structure layer on the erasure regions are removed to form a third opening and a floating grid electrode structure; and an erasure grid electrode structure is formed in the third opening. The method enables the production efficiency of the memory to be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

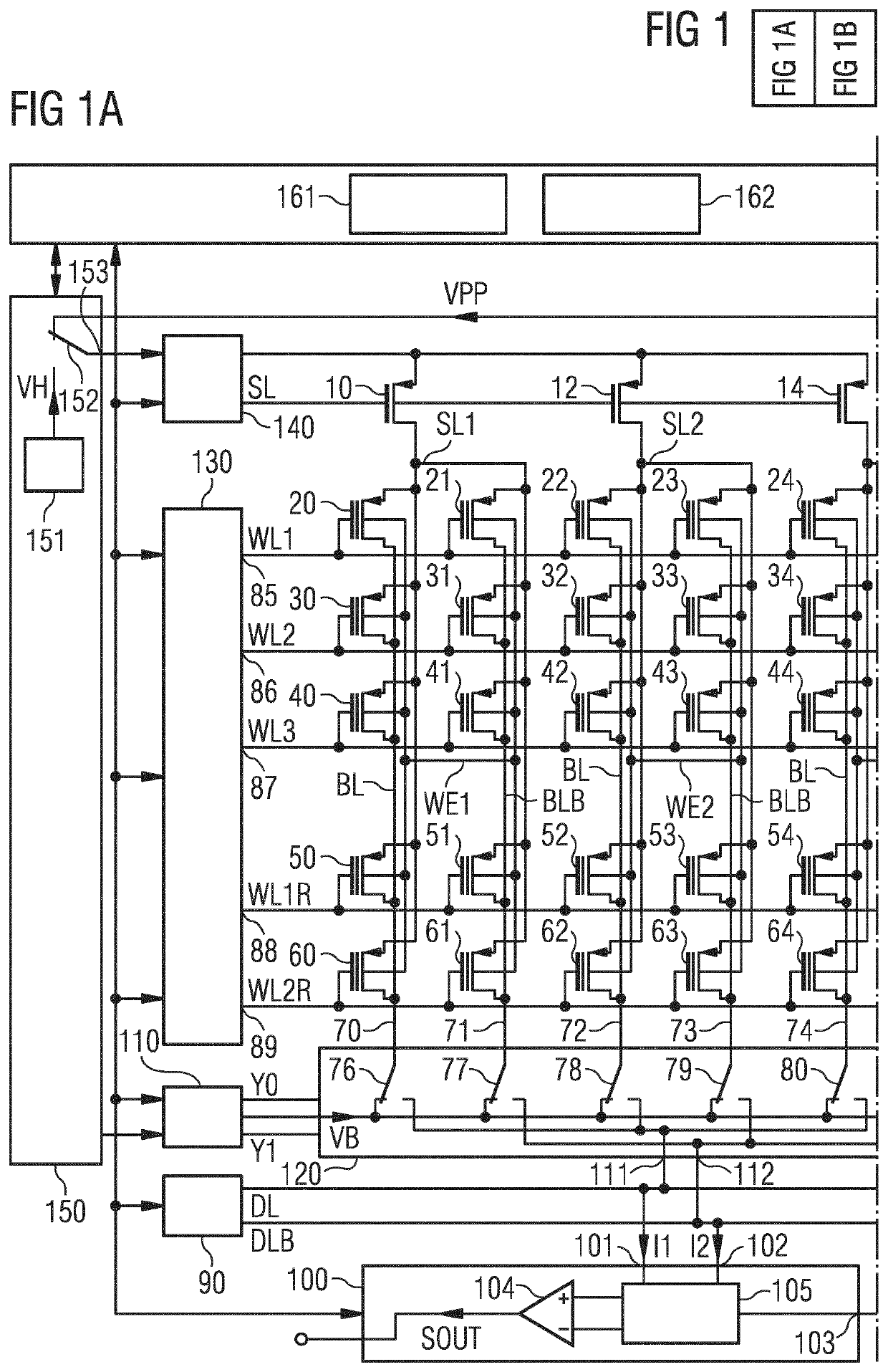

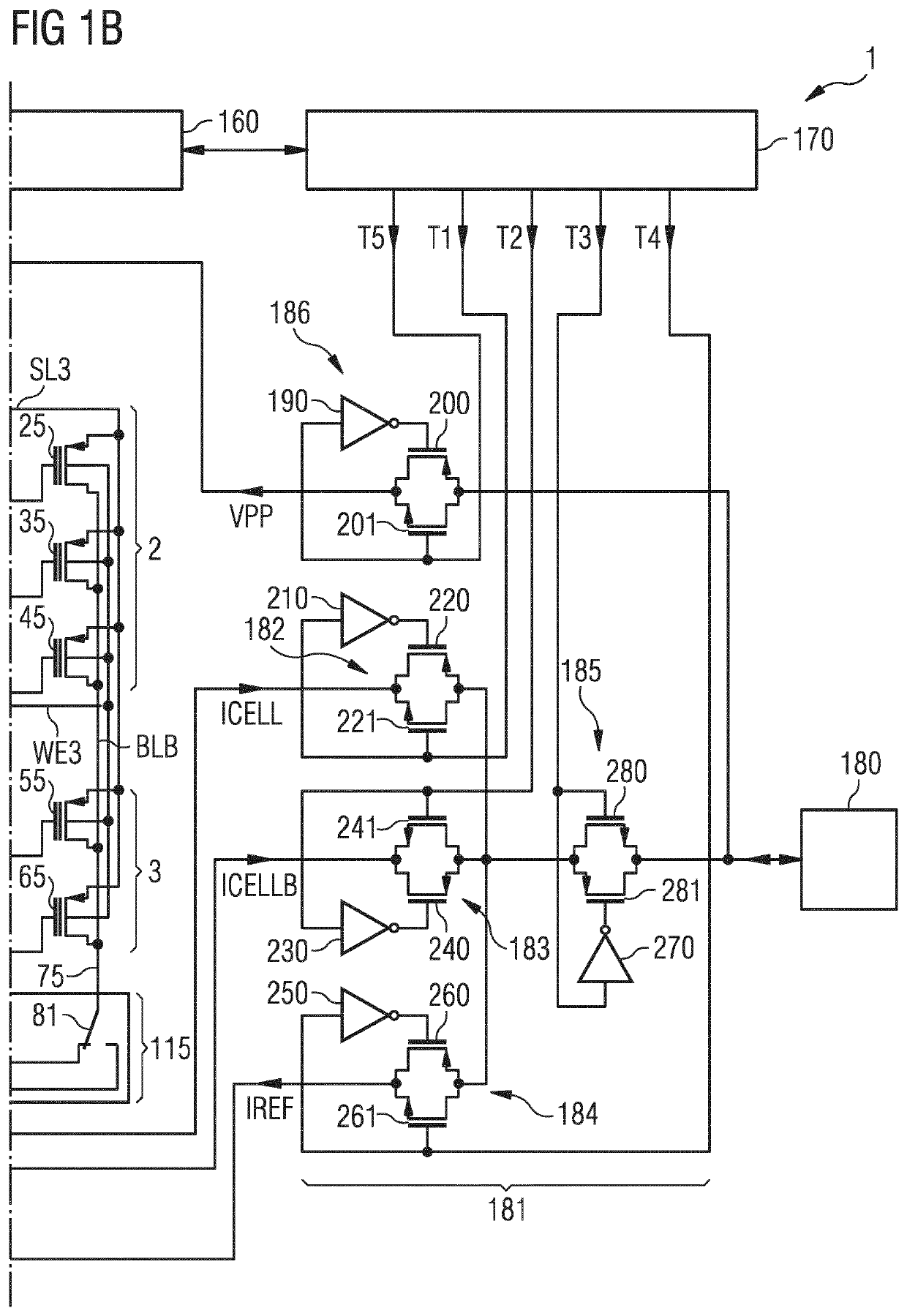

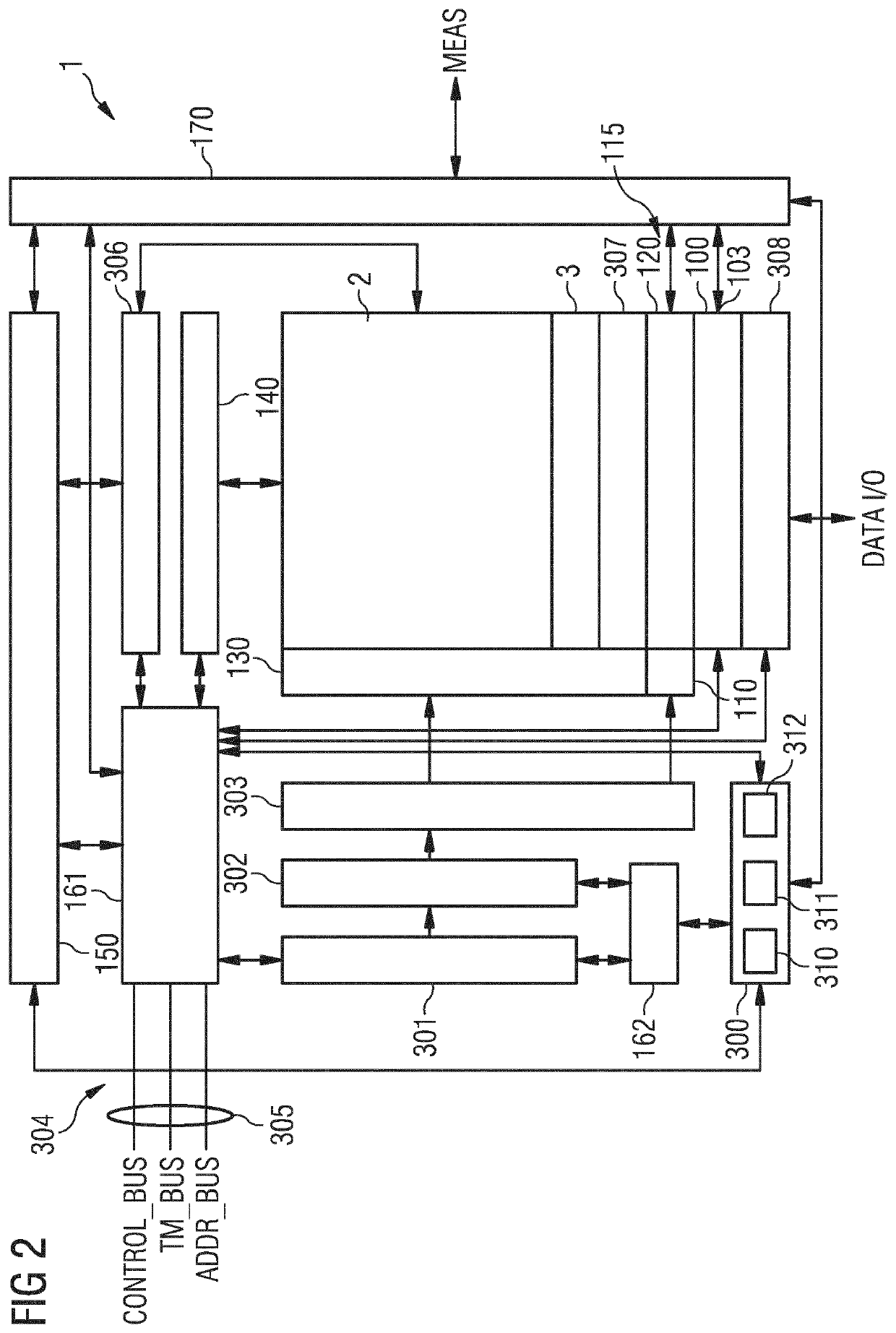

Memory arrangement and method for operating or testing a memory arrangement

A memory arrangement comprises a non-volatile memory plane (2), a replacement plane (3), an address select block (302), and a counter arrangement (300) having at least one counter (310 to 312). The at least one counter (310 to 312) is configured to be incremented at a write cycle of the memory arrangement (1). The address select block (302) is configured to switch from the non-volatile memory plane (2) to the replacement plane (3), if a counter value of the at least one counter (310 to 312) is higher than a predetermined limit.

Owner:AMS AG

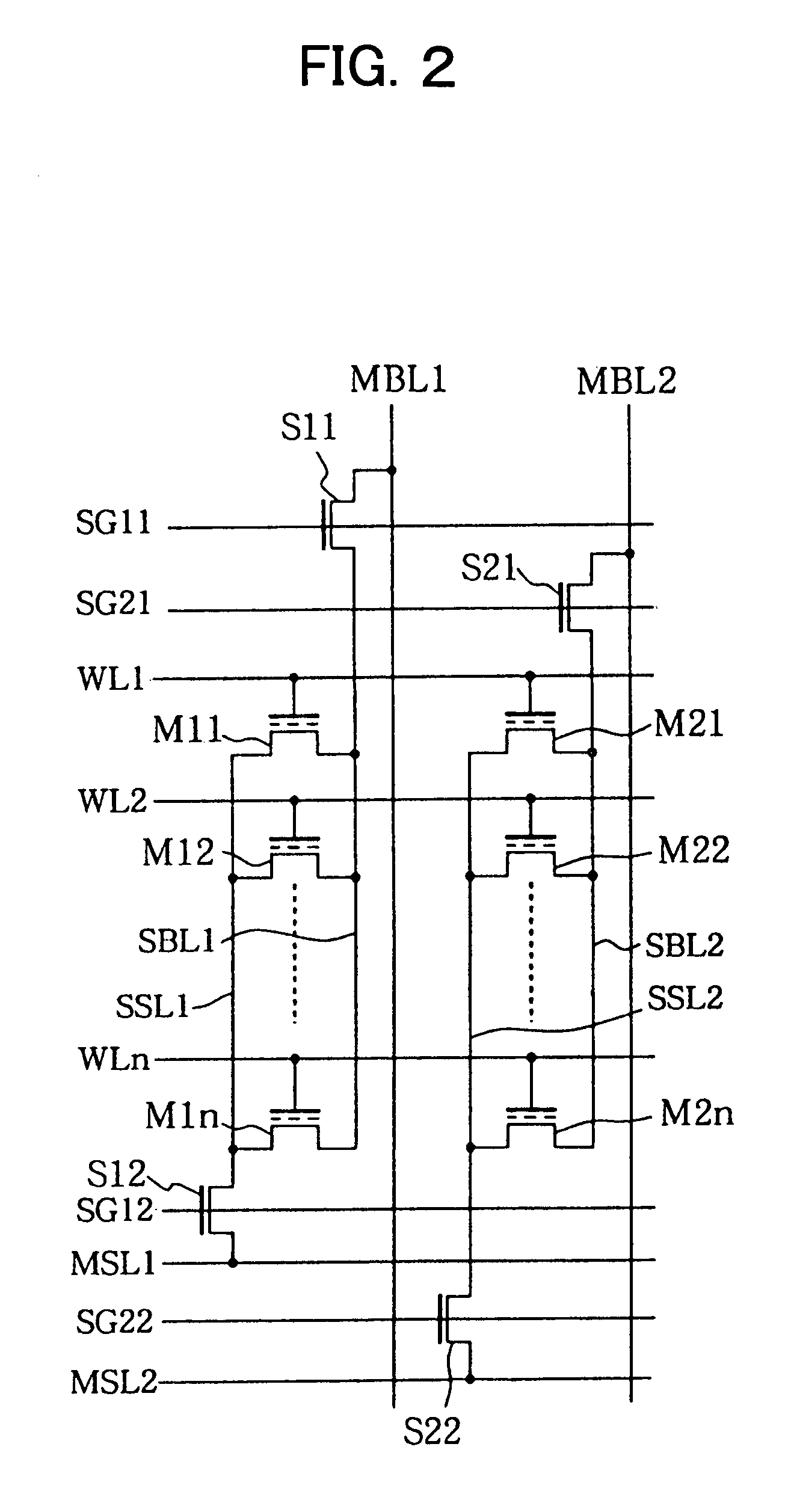

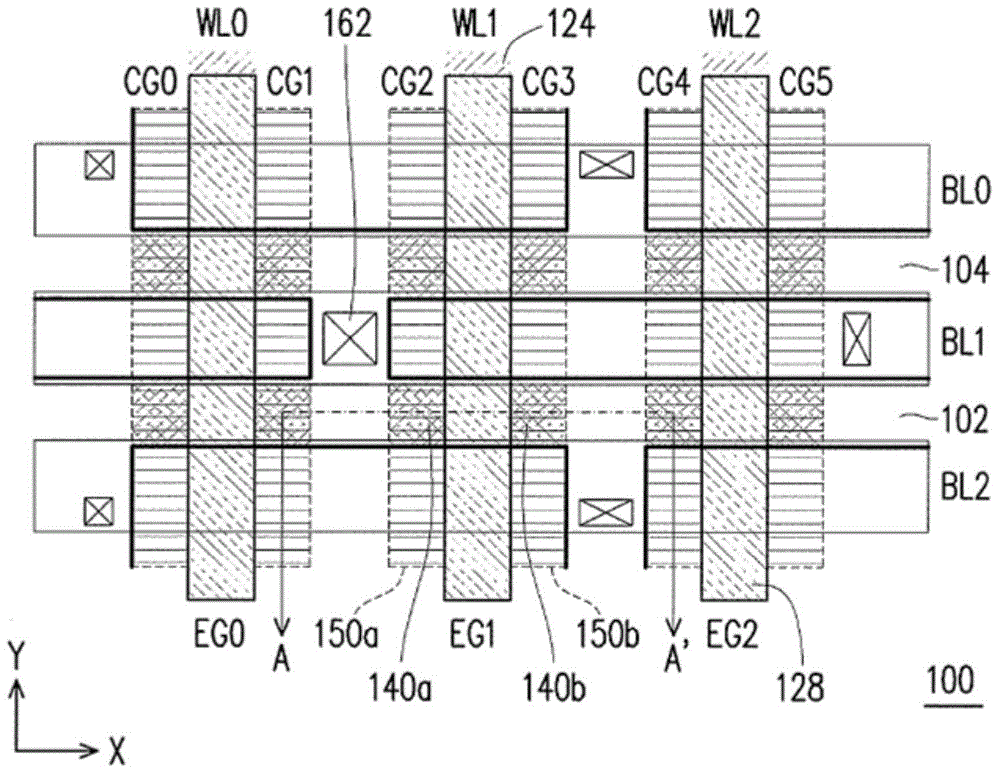

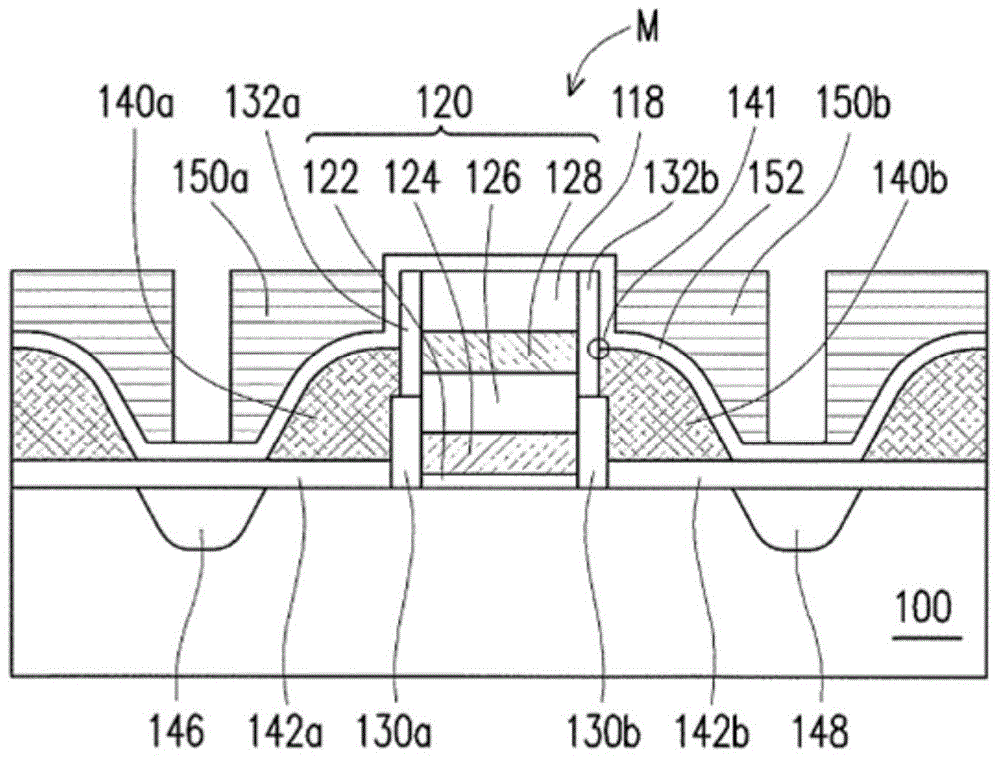

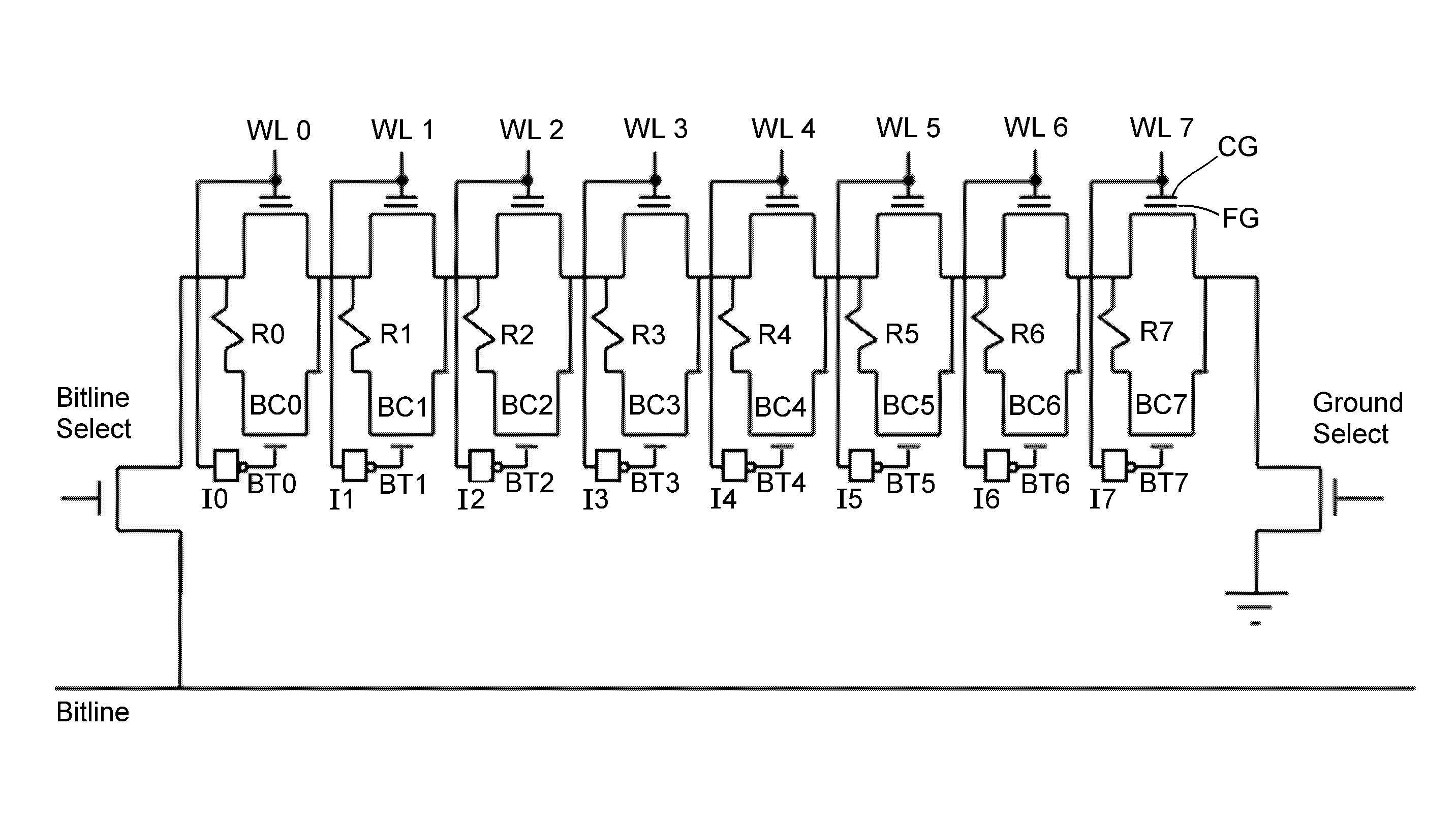

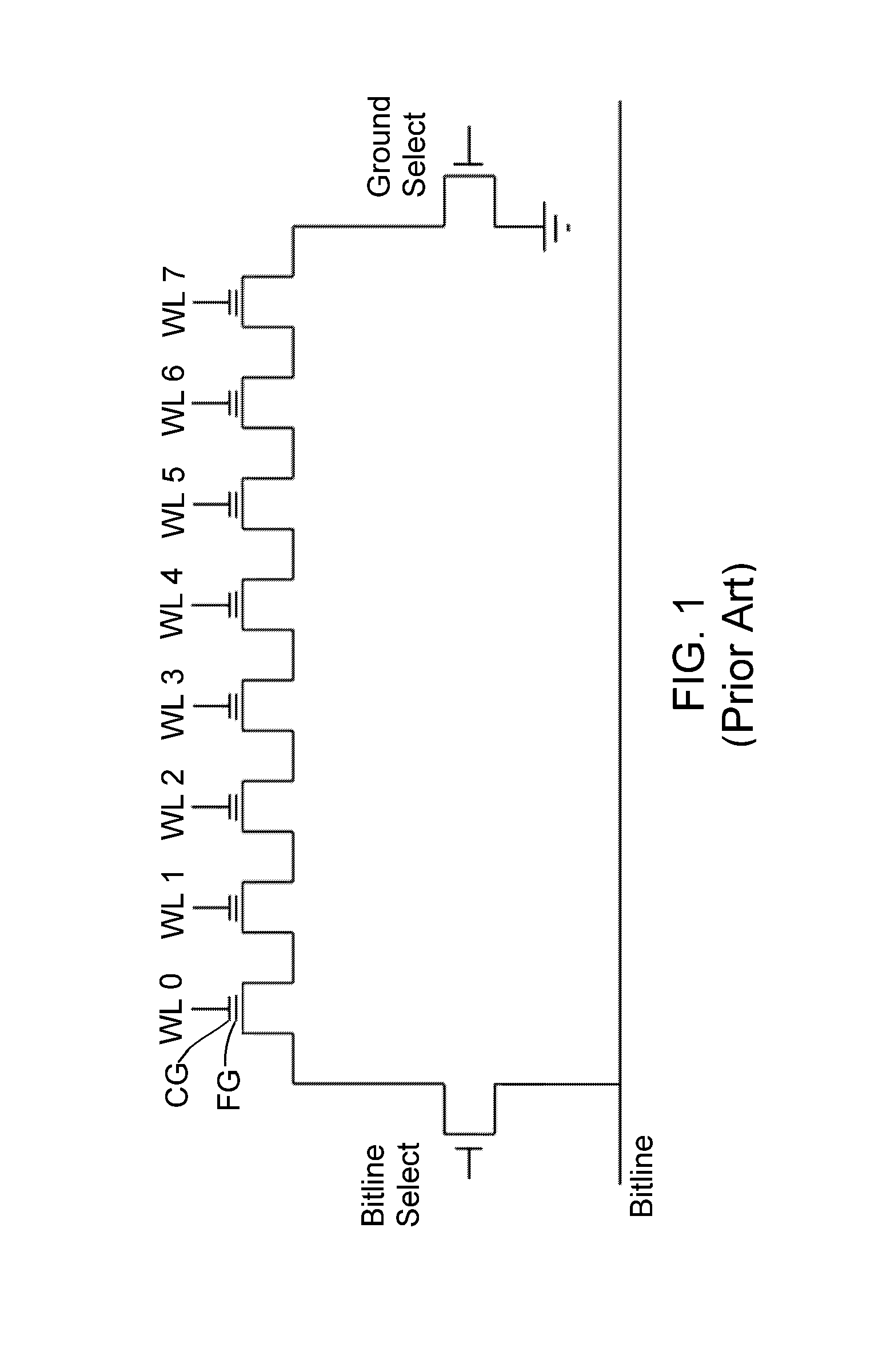

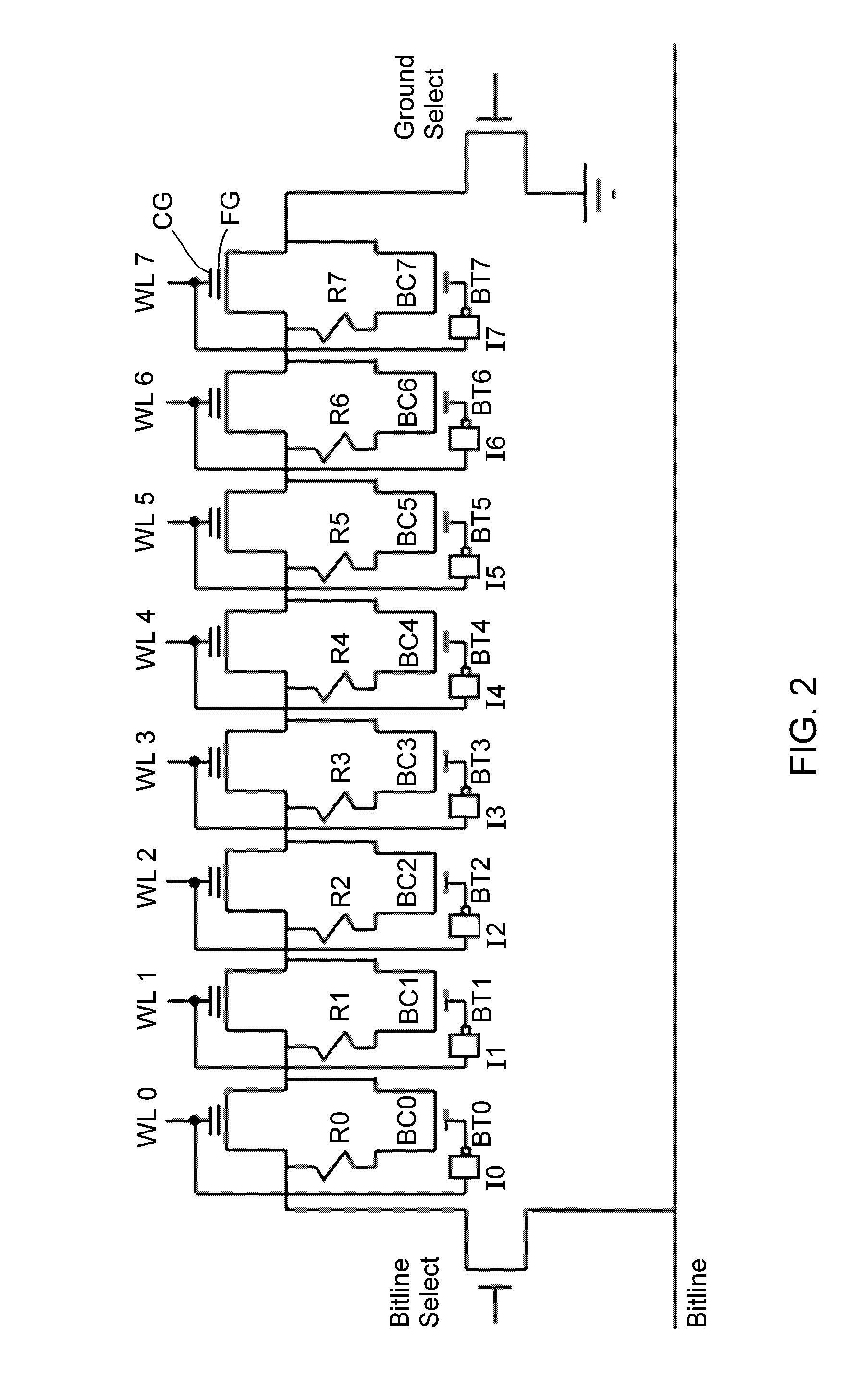

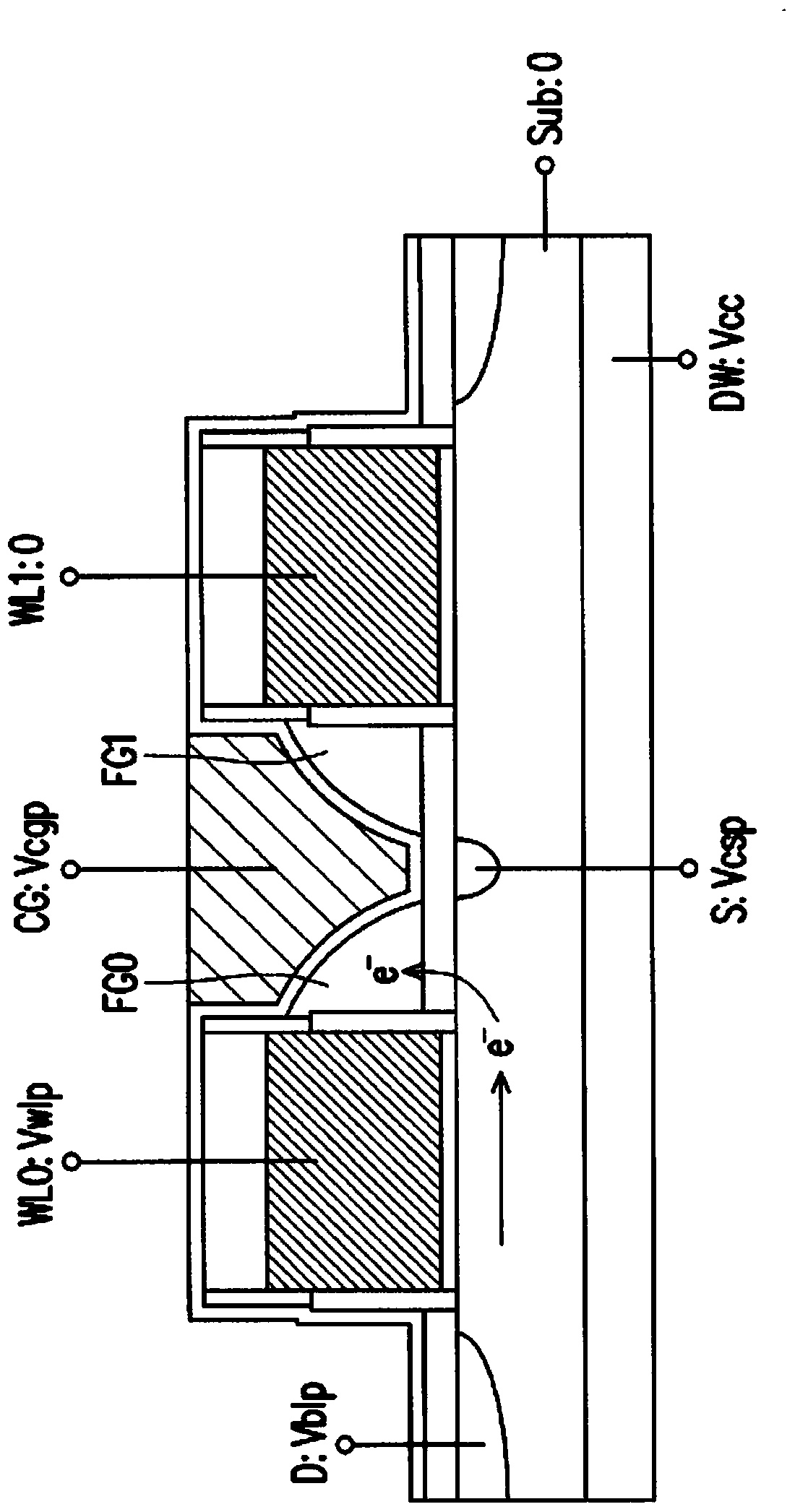

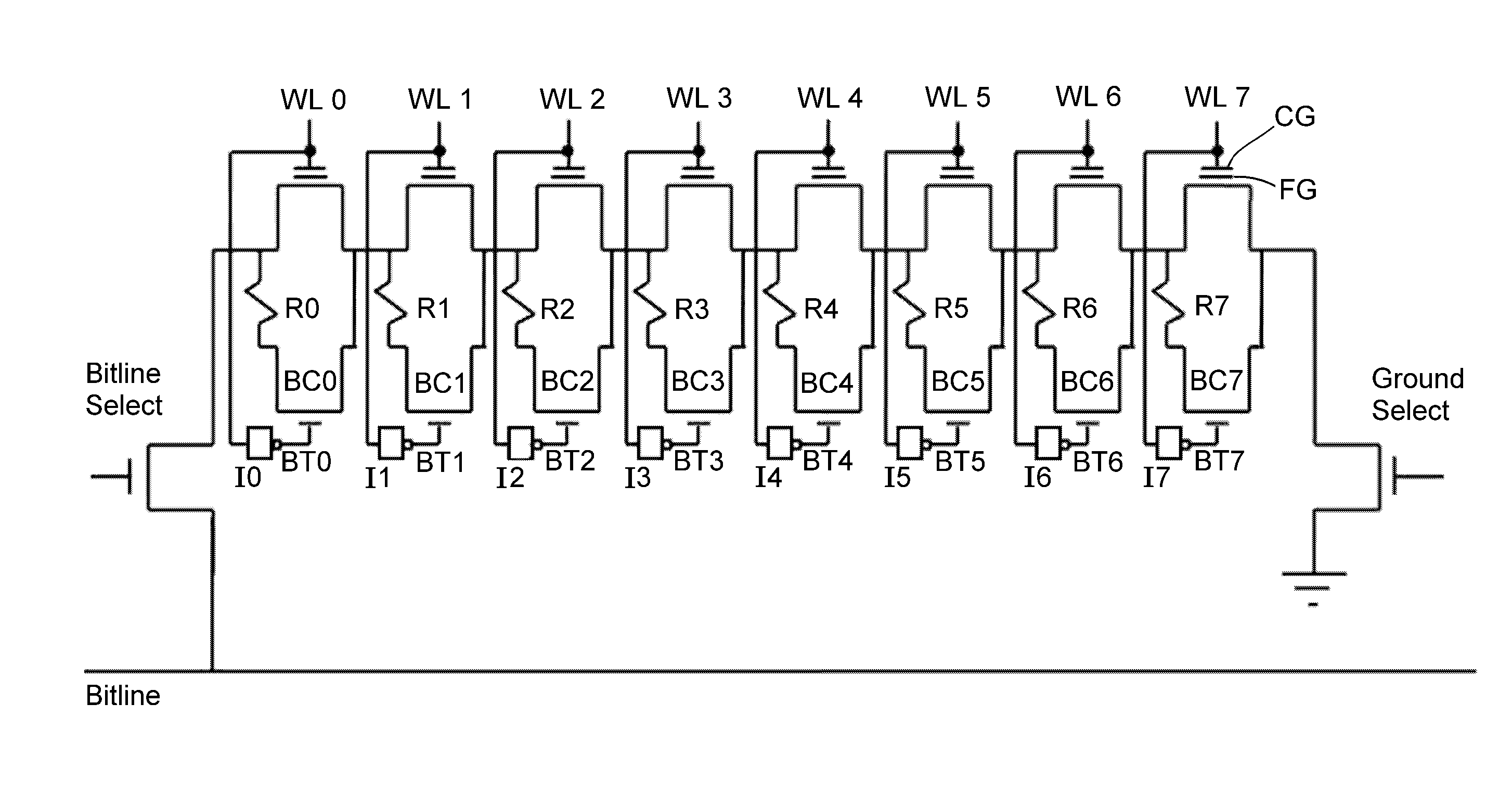

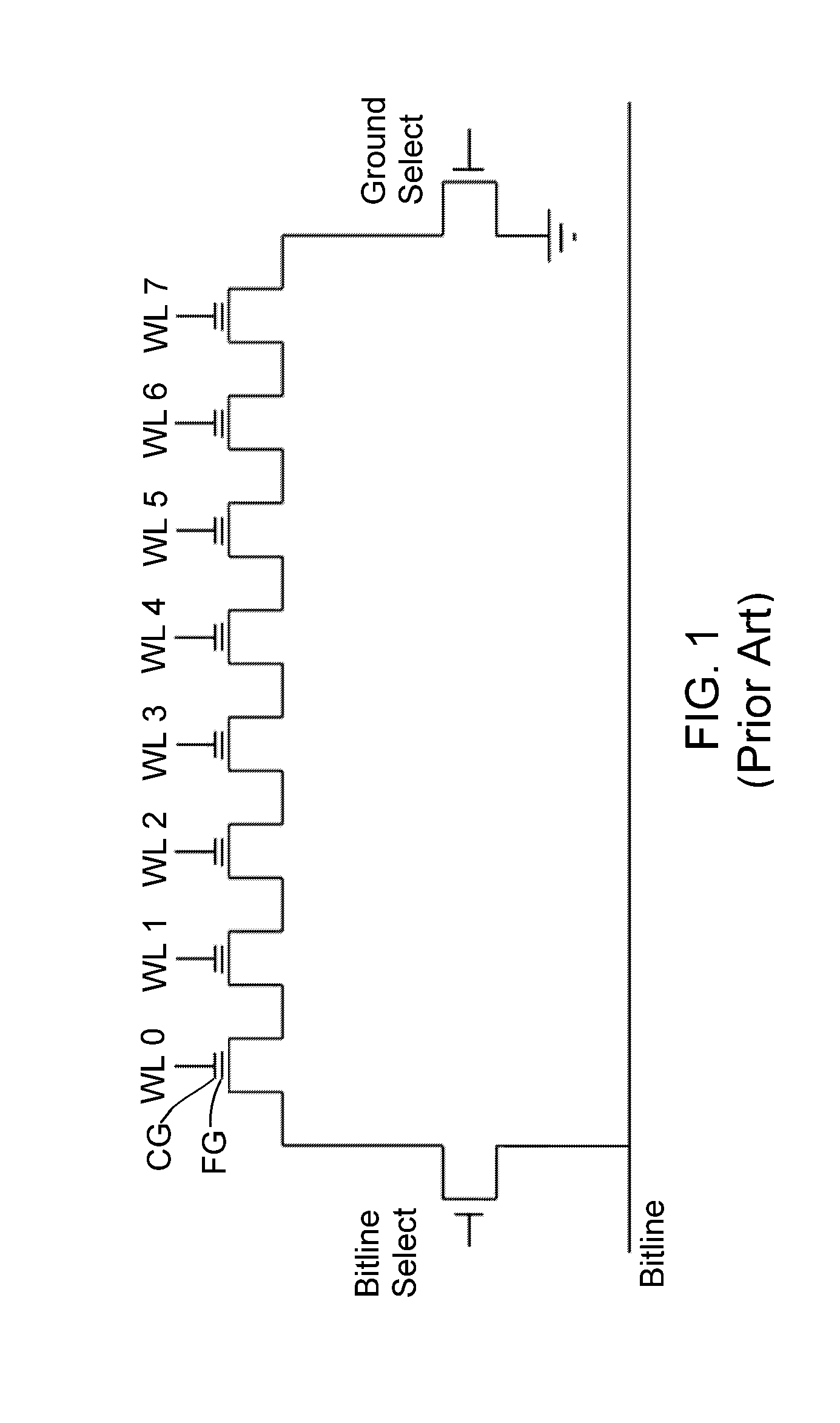

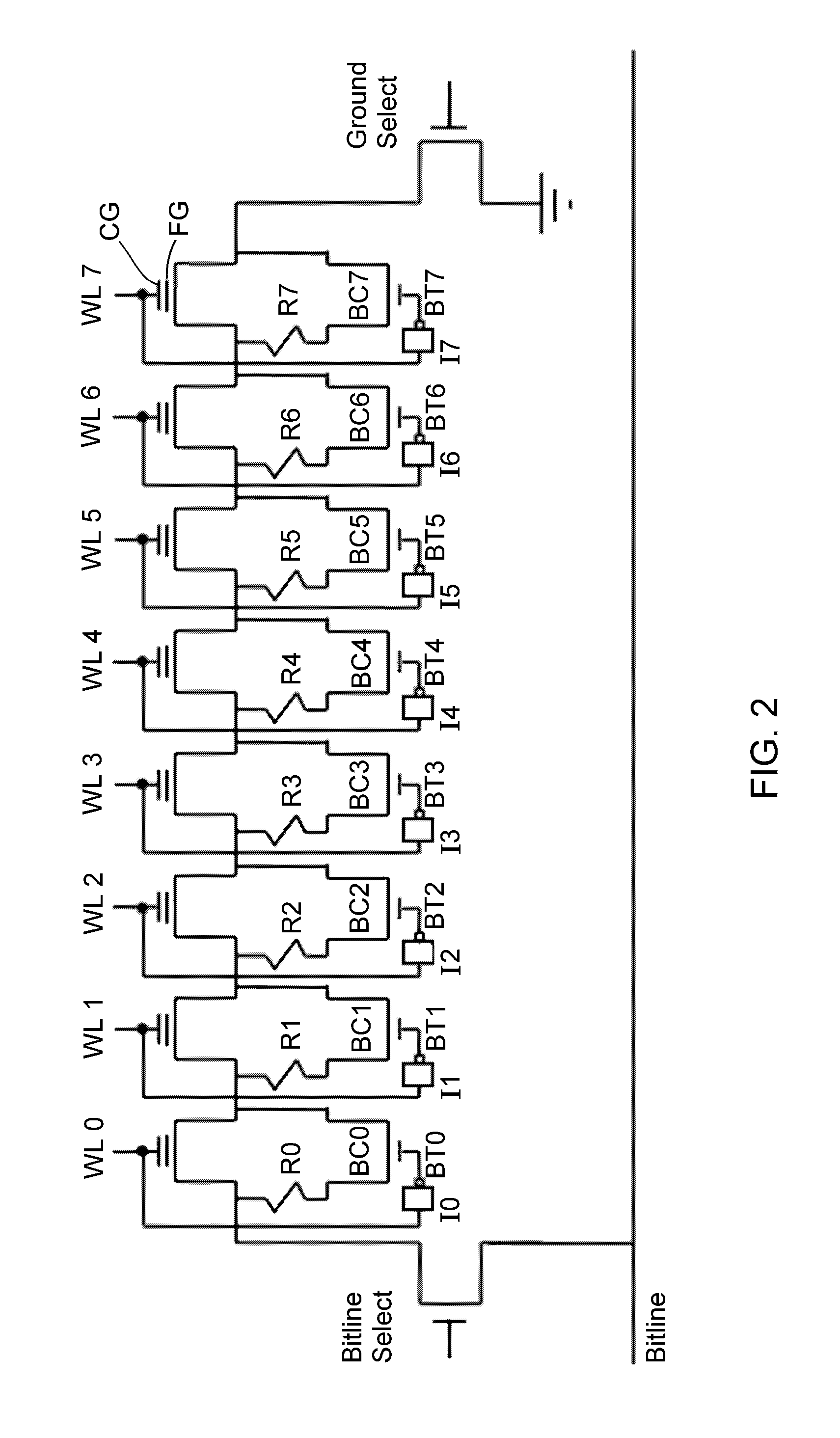

Flash memory device and method of operation

ActiveUS8488389B2Avoid over-erasingReduce the erase voltageRead-only memoriesDigital storageEngineeringVoltage

A NAND flash memory device and method of erasing memory cells thereof, wherein each cell is only subjected to the level of erase voltage needed to restore its nominal “erased” state. Each memory cell of the NAND flash memory device comprises a floating gate, a control gate connected to a wordline and receives a control voltage therefrom to induce a programming charge on the floating gate, and a bitline adapted to apply an erase voltage to deplete the floating gate of the programming charge. Each memory cell further includes circuitry for modulating the erase voltage according to the level of the programming charge on its floating gate.

Owner:KIOXIA CORP

Non-volatile Memory And Erasing Method Thereof

ActiveCN106158870AHighly integratedIncrease the clip areaSolid-state devicesSemiconductor devicesInsulation layerGate dielectric

The present invention provides a non-volatile memory having a memory cell and an erasing method thereof. The memory cell includes a stacked structure, a floating gate, a tunneling dielectric layer, an erasing dielectric layer, a source, a drain, a control gate and an inter-gate dielectric layer. The stacked structure includes a gate dielectric layer, a gate and an insulation layer disposed in the order. The floating gate is disposed on a first sidewall of the stacked structure. The tunneling dielectric layer is disposed under the floating gate. The erasing dielectric layer is disposed between the gate and the floating gate. The erasing dielectric layer includes a first portion and a second portion with a thickness less than or equal to the first portion, and a corner portion of the floating gate is adjacent to the second portion. The source and the drain are separately disposed on the two sides of the stacked structure and the floating gate. The control gate is disposed on the source and the floating gate. The inter-gate dielectric layer is disposed between the control gate and the floating gate, thereby being able to operate with a low operation voltage, and further increasing the reliability of a semiconductor element.

Owner:IOTMEMORY TECH +1

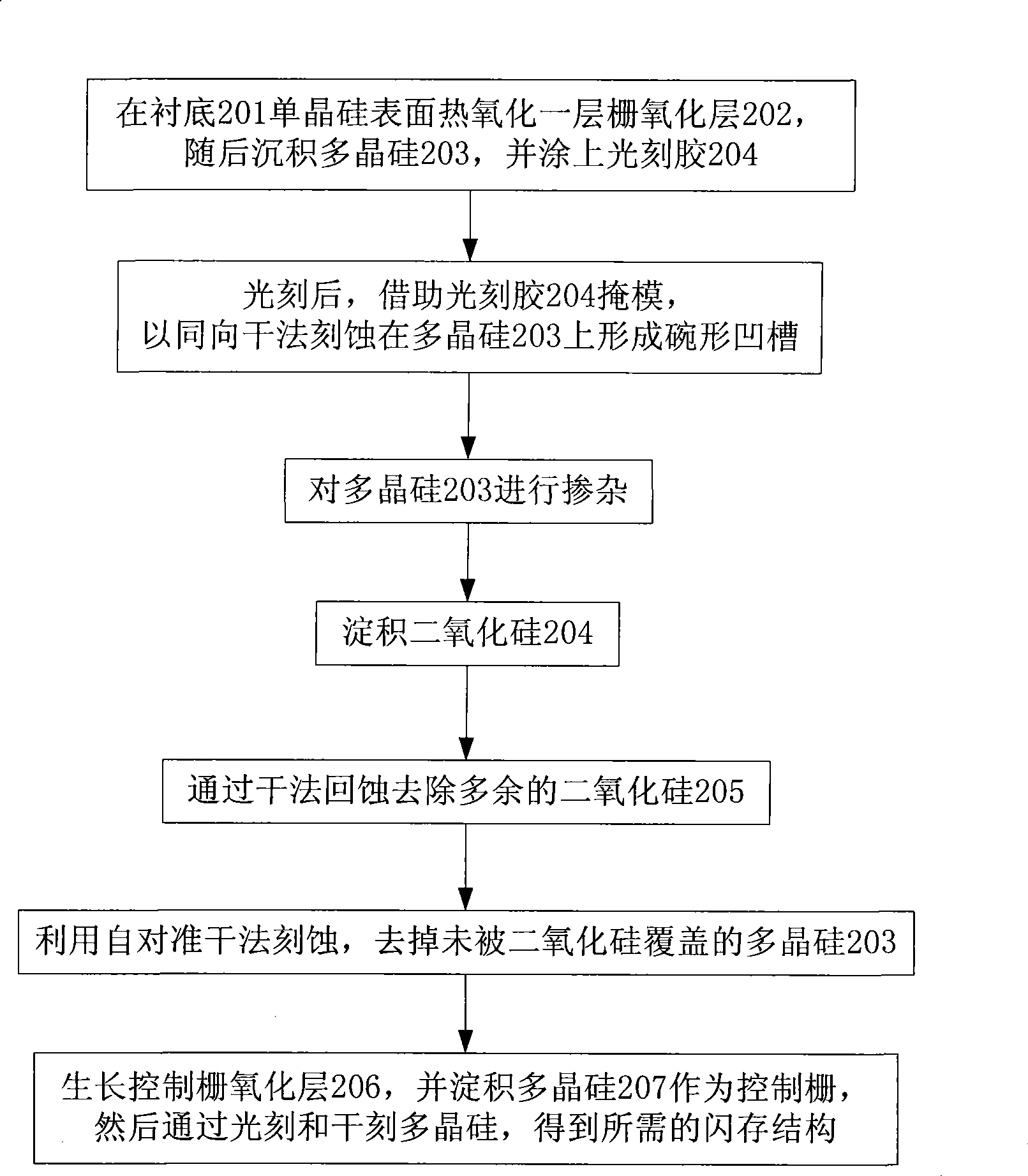

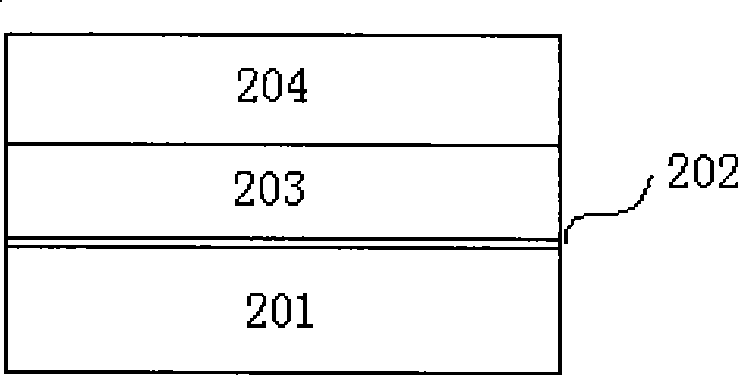

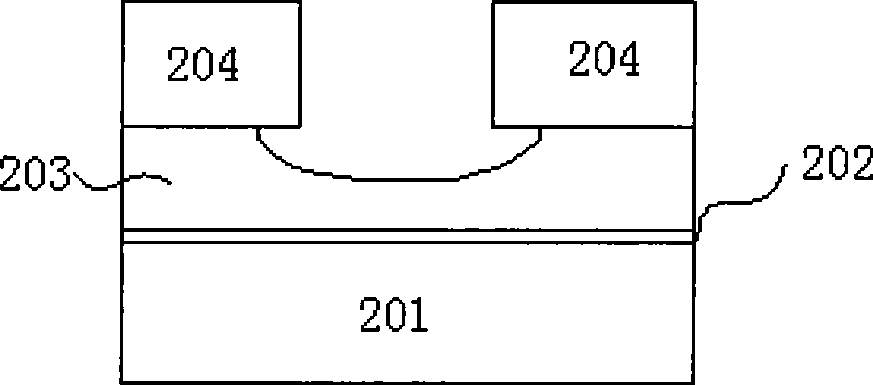

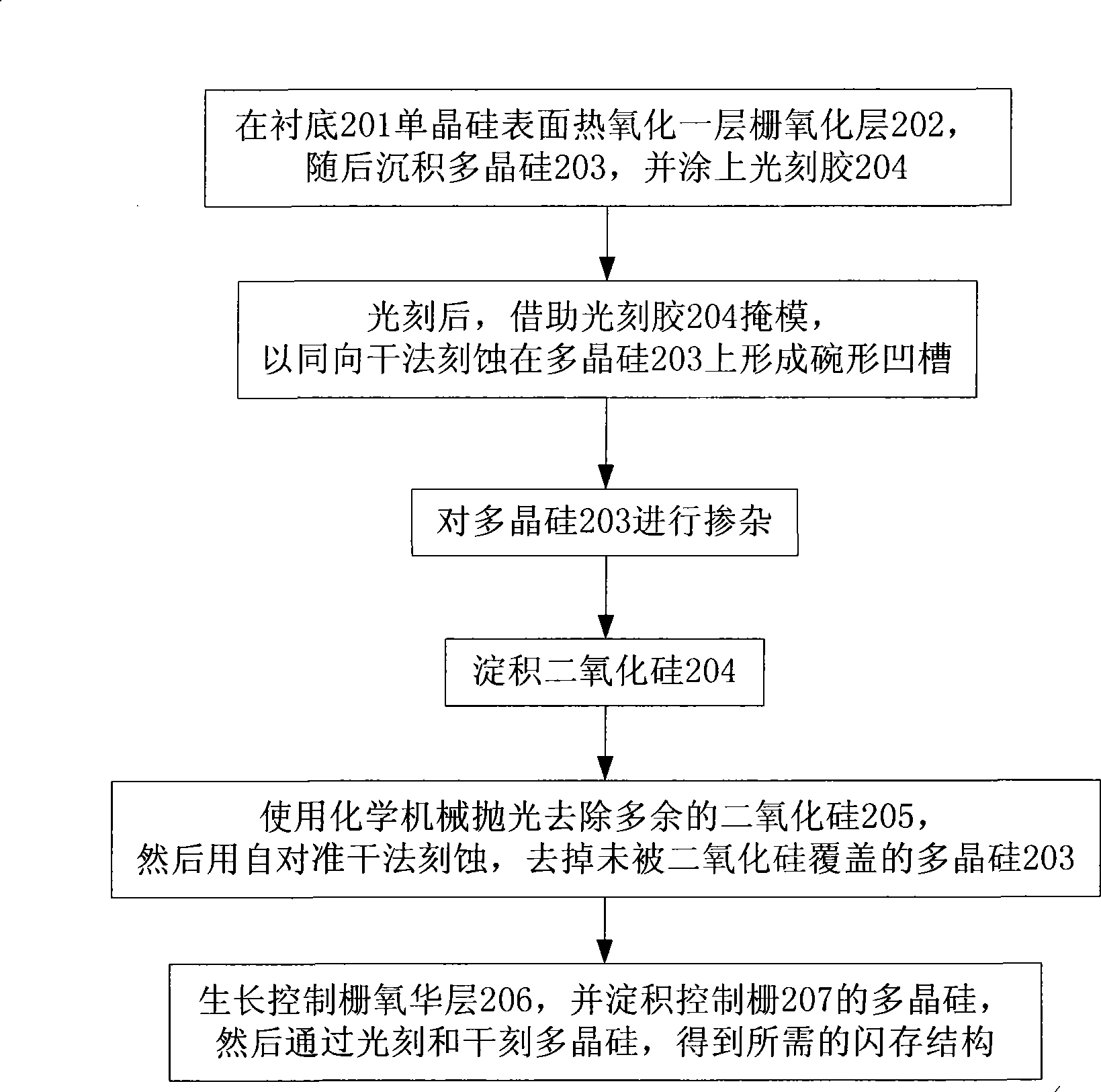

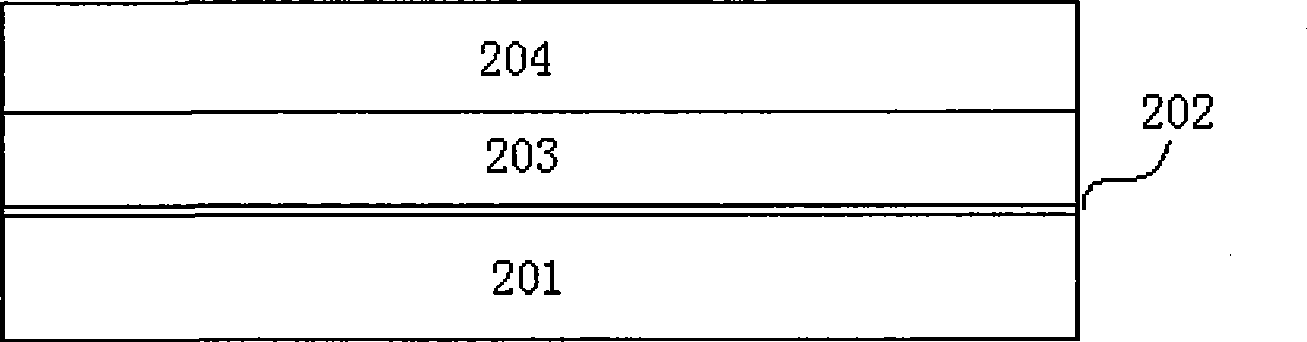

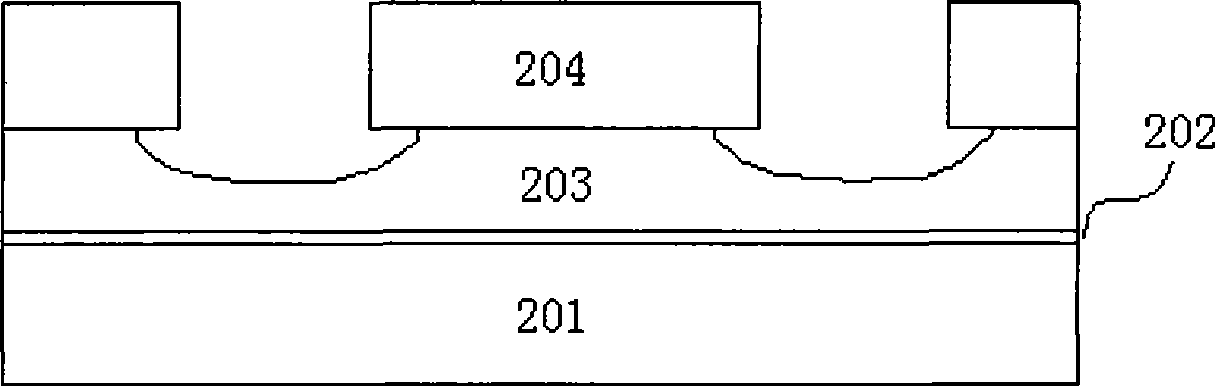

Production method for floating gate of flash memory in grating

InactiveCN101459065AReduce on-chip gapsEase of cutting-edge optimizationSemiconductor/solid-state device manufacturingSemiconductor devicesGratingSilicon dioxide

The invention discloses a manufacturing method for floating gates of split-gate flash memories, which comprises steps of firstly using photoresist as a mask and utilizing isotropic dry etching to form a bowl-shaped groove of a floating gate, secondarily, depositing a silicon dioxide layer and utilizing the dry etch-back technique to form a semicircular oxide layer, and finally, utilizing self-aligned dry etching to etch away polysilicon outside an oxide region, thereby obtaining sharp periphery of the floating gate, guaranteeing the shape of the finally formed floating gate be unaffected by other operating steps during the manufacturing process of split-gate flash memories, reducing step on chip in flash memory arrays of the split-gate flash memory, increasing production efficiency and further simplifying optimization for pointed ends of the floating gate with small fluctuation, besides, the manufacturing method is simple to realize and reduces manufacturing cost to some extent. The manufacturing method further can guarantee reducing erase failure and erase voltage when the flash memory executes erasing actions, and thereby the flash memory unit is easier to control.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

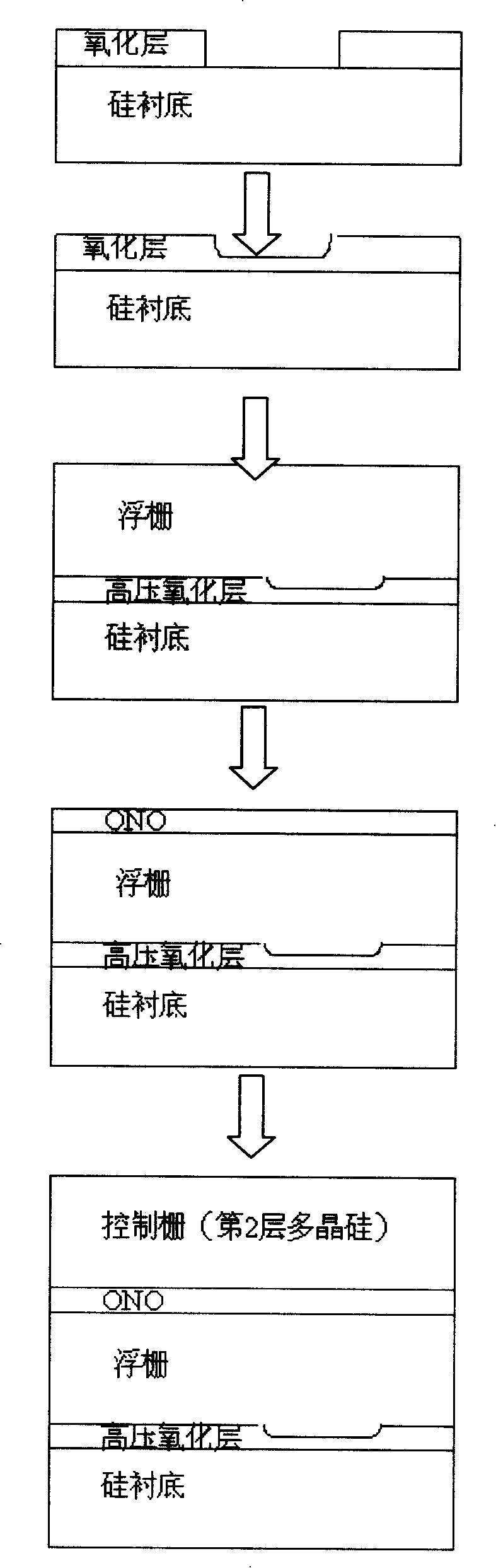

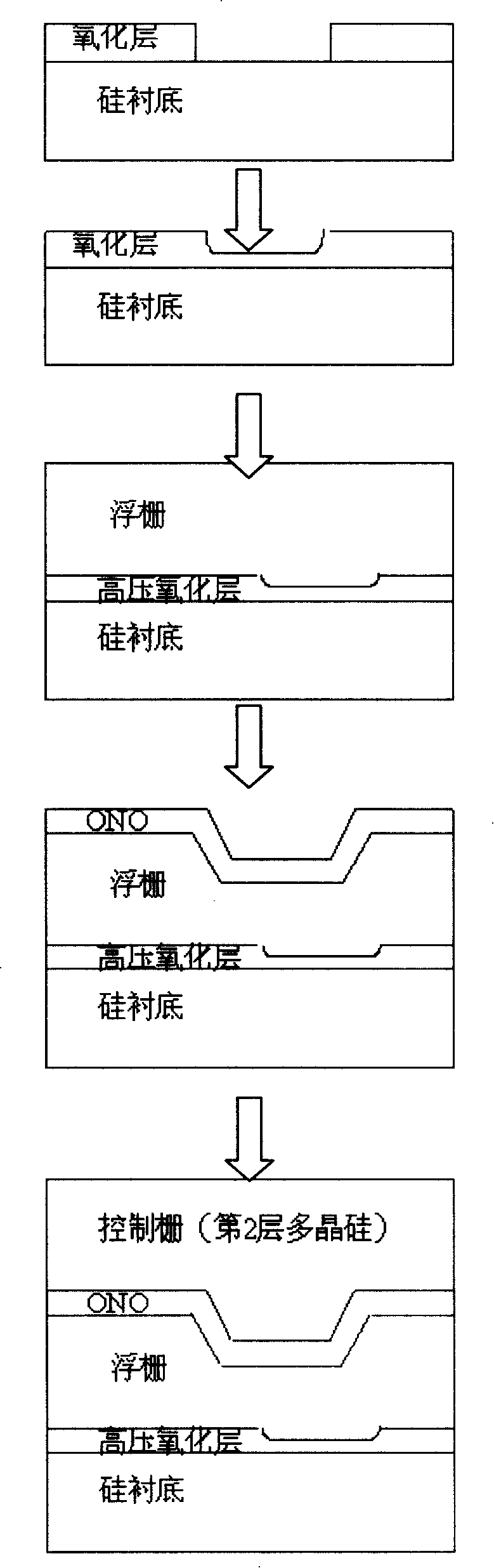

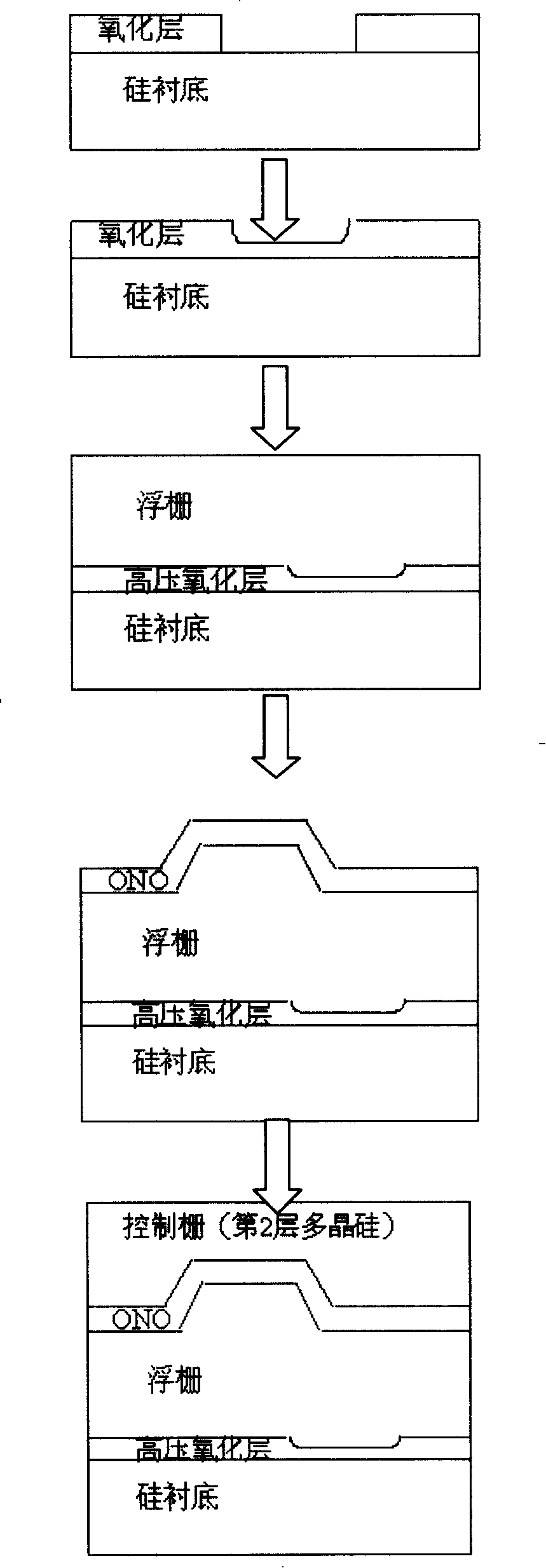

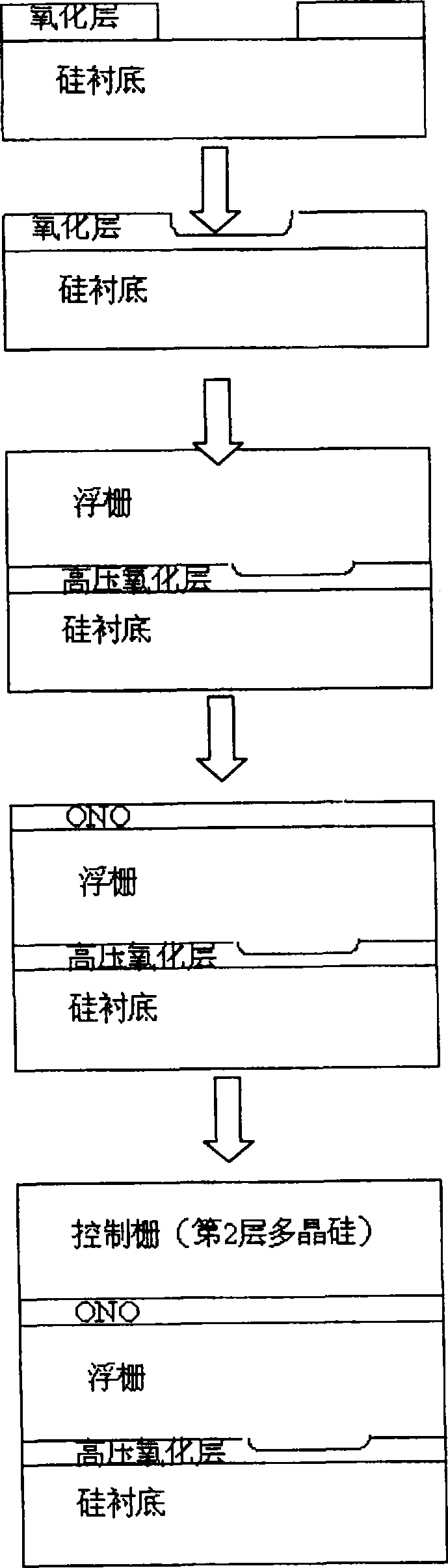

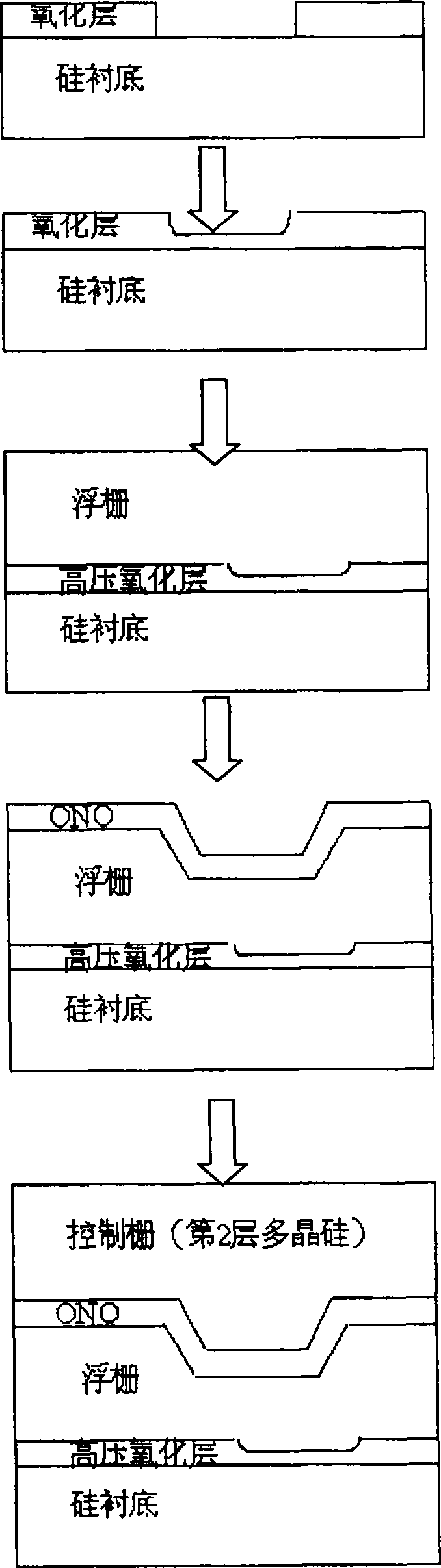

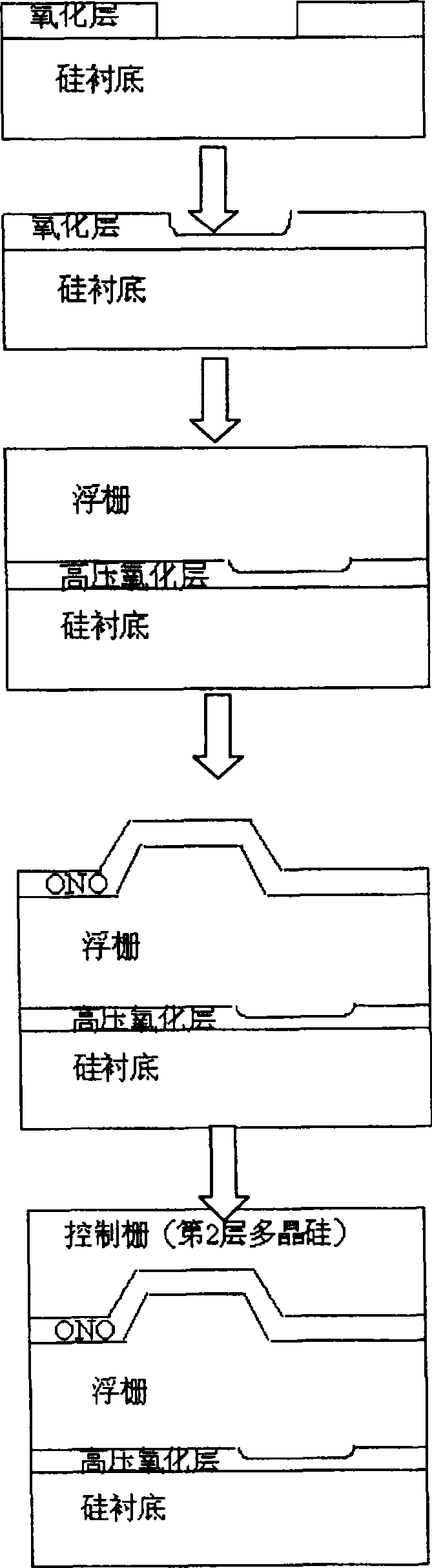

A making method of EEPROM for increasing coupling voltage of float grating

ActiveCN101188196AIncrease capacitanceImprove writing efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEtching

The invention discloses an EEPROM manufacture method which can increase the floating gate coupling voltage. The method besides includes steps of growing a high voltage oxide film, carrying out channel etching, growing a layer of channel oxides, growing a layer of floating gate polycrystals, growing a ONO, and growing two layers of the polycrystals; the floating gate etching is carried out after growing a layer is carried out and before growing the ONO is carried out. A pattern of the floating gate etching is composed of a cubic block or a plurality of small cubic blocks. Because the invention increases one time floating gate etching and the capacitance of the ONO in a traditional EEPROM manufacture method, that is, the coupling ratio and the coupling voltage of the floating gate are increased, the recordable efficiency of the EEPROM can be enhanced or the recordable voltage is decreased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

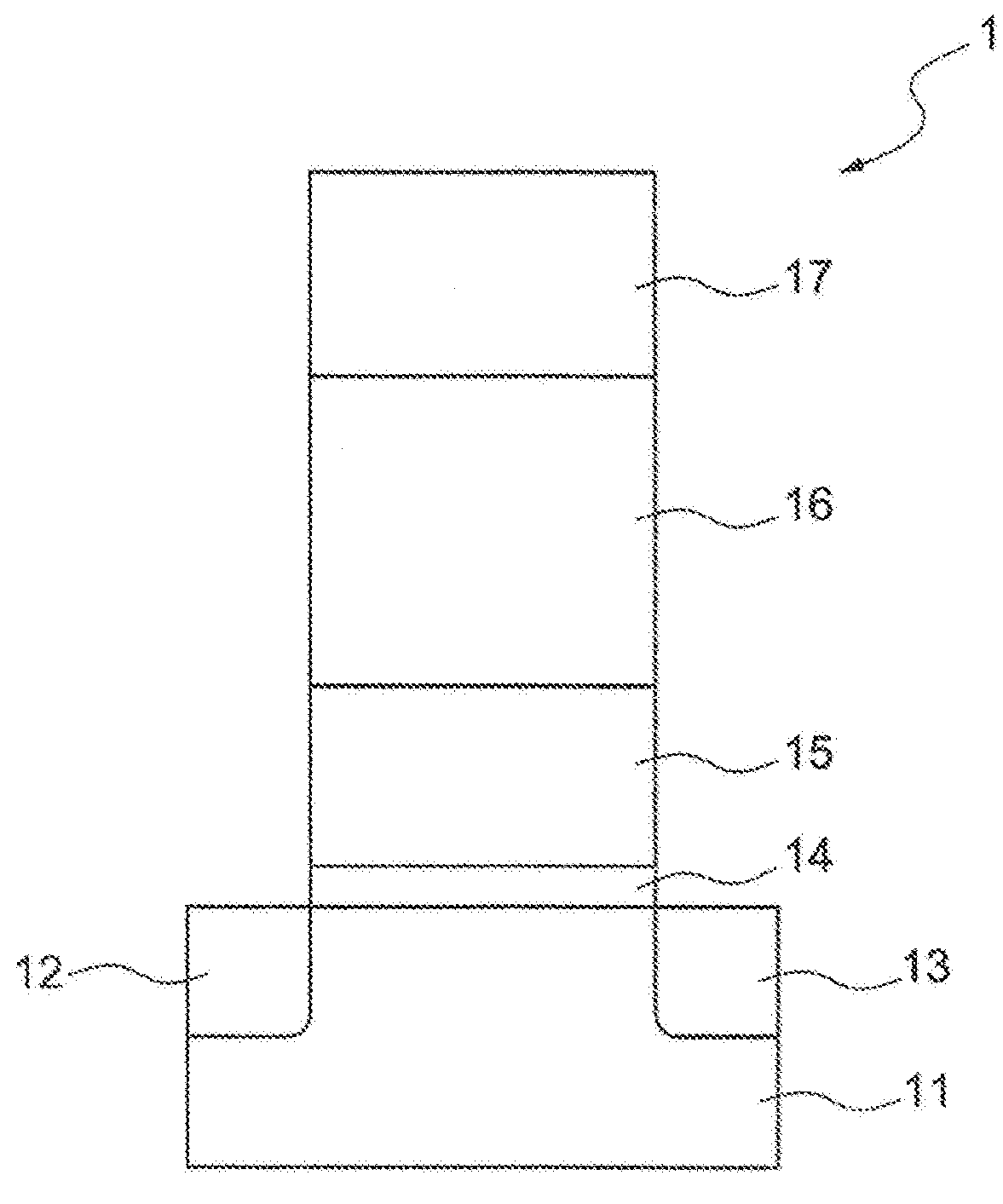

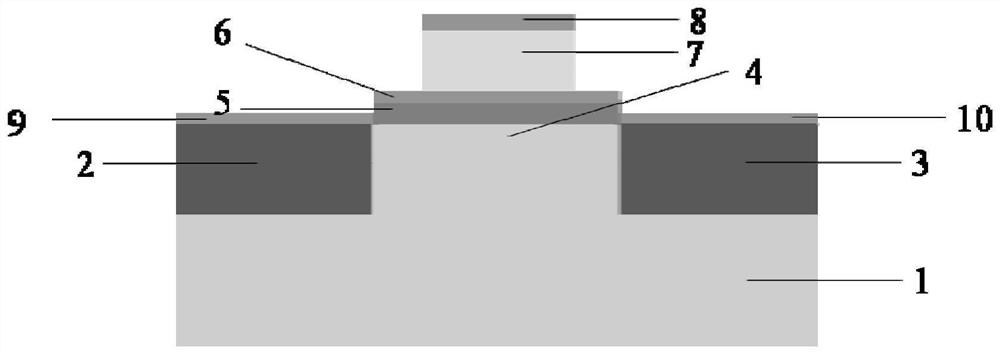

Thin film transistor memory and preparation method thereof

InactiveCN114122138APrevent leakageStrong reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesBottom gateThin membrane

A thin film transistor memory provided by the present invention comprises a back gate, a barrier layer, a floating gate, a tunneling layer, a channel, a source electrode and a drain electrode, the back gate comprises a bottom gate structure and a side gate structure, the side gate structure is arranged on a part of the upper surface of the bottom gate structure to form an L-shaped structure, the barrier layer is arranged on the upper surface of the bottom gate structure, and the floating gate is arranged on the upper surface of the bottom gate structure. The floating gate is arranged on the upper surface of the barrier layer, the upper surface of the floating gate is flush with the upper surface of the side gate structure, the tunneling layer is arranged on the upper surface of the floating gate, the channel is arranged on the upper surface of the tunneling layer, the source electrode and the drain electrode are arranged on the upper surface of the channel, and the side gate structure is arranged on the upper surface of the channel. According to the technical scheme, energy band regulation and control can be carried out on the floating gate through the side gate structure, so that the electronic erasing speed is increased, the electronic erasing voltage is reduced, the power consumption can be reduced, and as the channel is not in contact with the floating gate, the memory is not easy to leak and higher in reliability. The invention also provides a preparation method of the thin film transistor memory.

Owner:SHANGHAI INTEGRATED CIRCUIT MFG INNOVATION CENT CO LTD

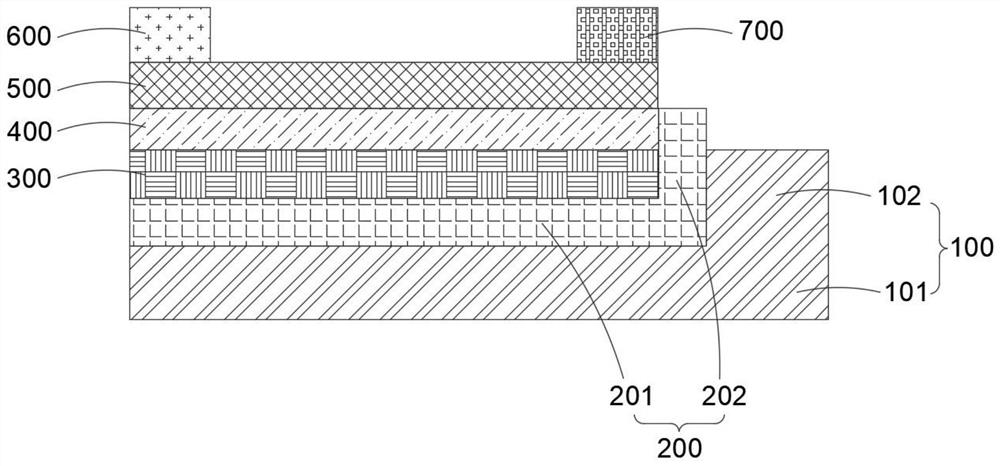

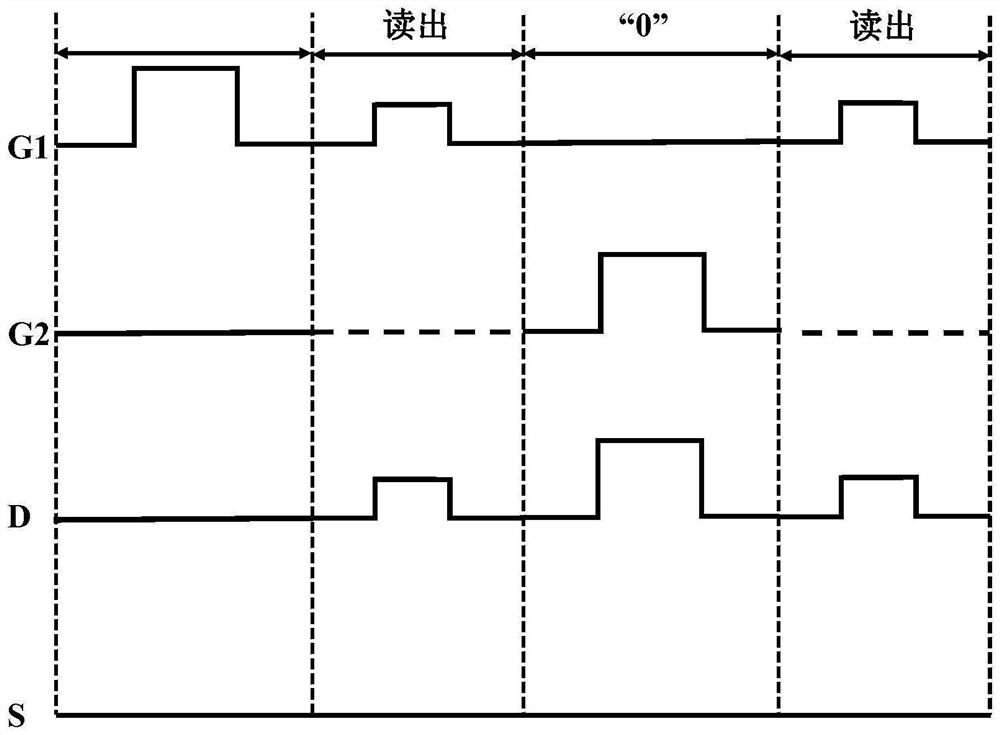

Double-gate ferroelectric transistor, preparation method and data erasing and reading method

PendingCN114530503AImprove fatigue resistancePrevent breakdownSemiconductor/solid-state device manufacturingDigital storageGate dielectricField-effect transistor

The invention belongs to the technical field of transistors, and discloses a double-gate ferroelectric transistor, a preparation method and a data erasing and reading method.The double-gate ferroelectric transistor comprises a substrate and a channel, the channel is arranged above a lining body and located in the middle of the lining body, and a source electrode region and a drain electrode region are arranged on the two sides of the channel respectively; a source electrode is arranged on the source electrode region, a drain electrode is arranged on the drain electrode region, and an insulating layer, a lower gate electrode, a ferroelectric gate dielectric layer and an upper gate electrode are sequentially arranged above the channel from bottom to top. The dual-gate ferroelectric field transistor has the beneficial effects that the erasing process is realized by adding pulses between the upper gate electrode and the lower gate electrode, so that voltage is prevented from falling on the insulating layer; the breakdown of the insulating layer caused by an overlarge electric field on the insulating layer is avoided, and the anti-fatigue property of the transistor is improved; and voltage division of the insulating layer can be avoided, so that the programming and erasing voltage and the working voltage of the ferroelectric field effect transistor are reduced.

Owner:XIDIAN UNIV

Non-volatile memory and erasing method thereof

ActiveCN106158870BHighly integratedThe overall thickness is thinSolid-state devicesSemiconductor devicesGate dielectricInsulation layer

The invention provides a non-volatile memory and an erasing method thereof. The non-volatile memory has a storage unit. The memory cell has a stacked structure, a floating gate, a tunnel dielectric layer, an erasure dielectric layer, a source region, a drain region, a control gate and an inter-gate dielectric layer. The stacked structure has a dielectric layer, a gate electrode, and an insulating layer arranged in sequence. The floating gate is disposed on the sidewall of the first side of the stacked structure. The tunnel dielectric layer is disposed under the floating gate. The erasure dielectric layer is disposed between the gate electrode and the floating gate electrode. The erasing dielectric layer includes a first portion and a second portion with a thickness less than or equal to the first portion, and a corner portion of the floating gate is adjacent to the second portion. The source region and the drain region are respectively disposed on both sides of the stacked structure and the floating gate. The control gate is disposed on the source region and the floating gate. The inter-gate dielectric layer is disposed between the control gate and the floating gate, which can operate at a low operating voltage, thereby increasing the reliability of the semiconductor device.

Owner:IOTMEMORY TECH +1

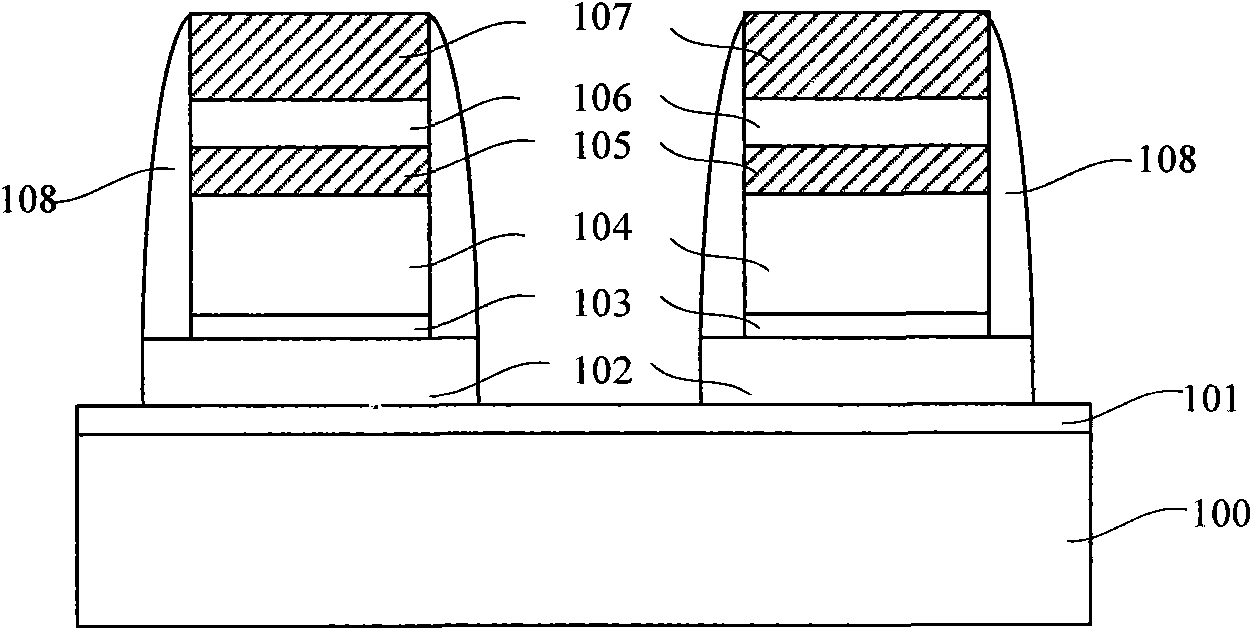

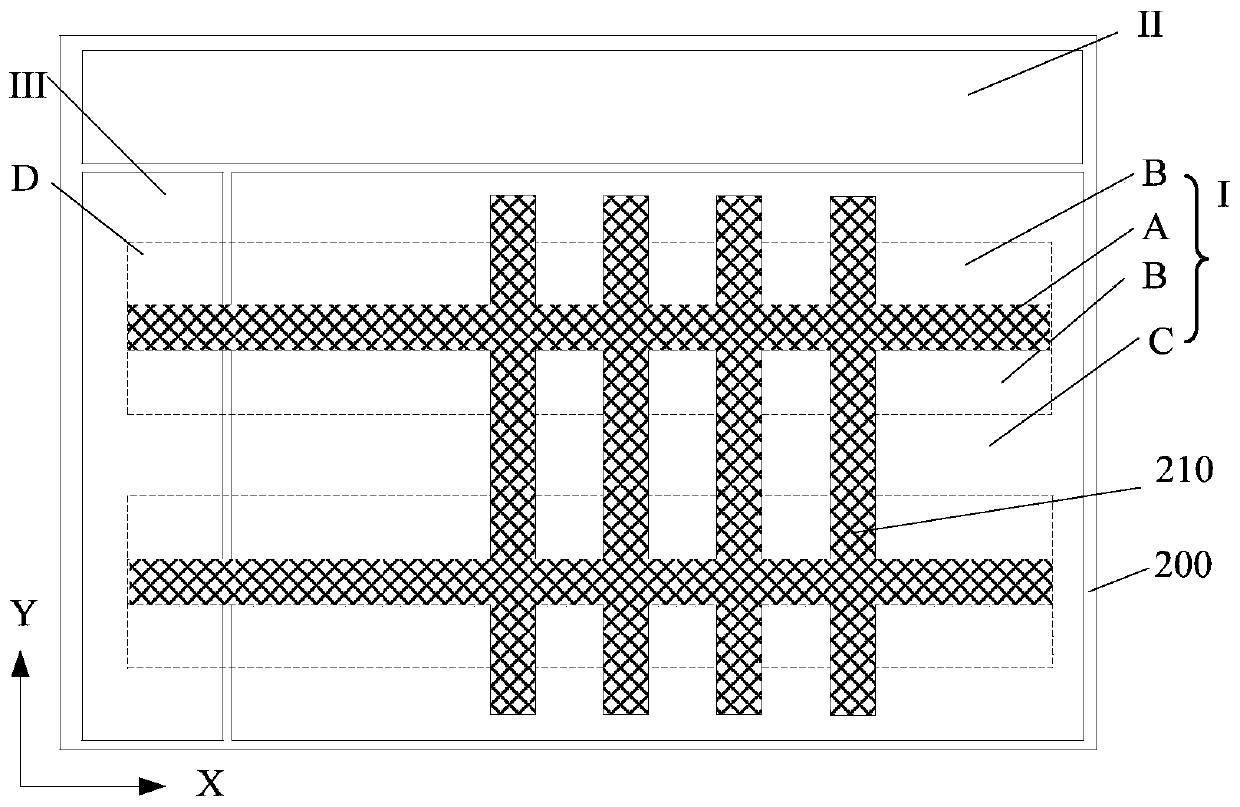

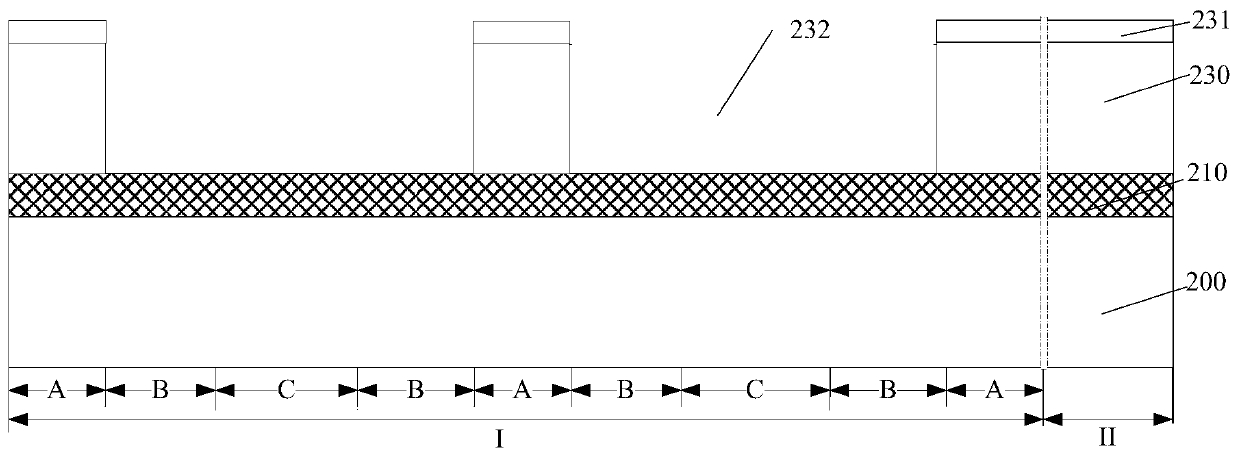

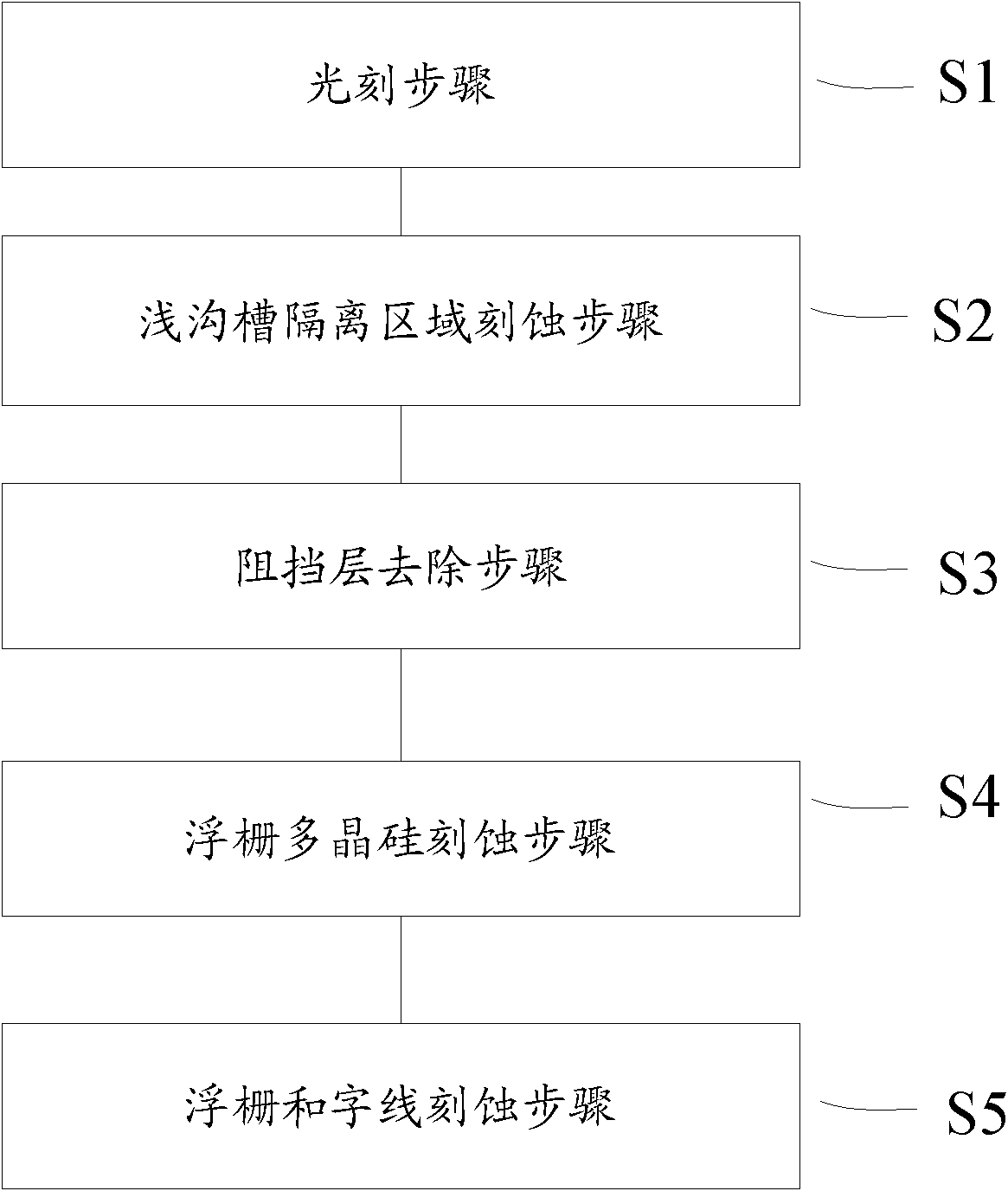

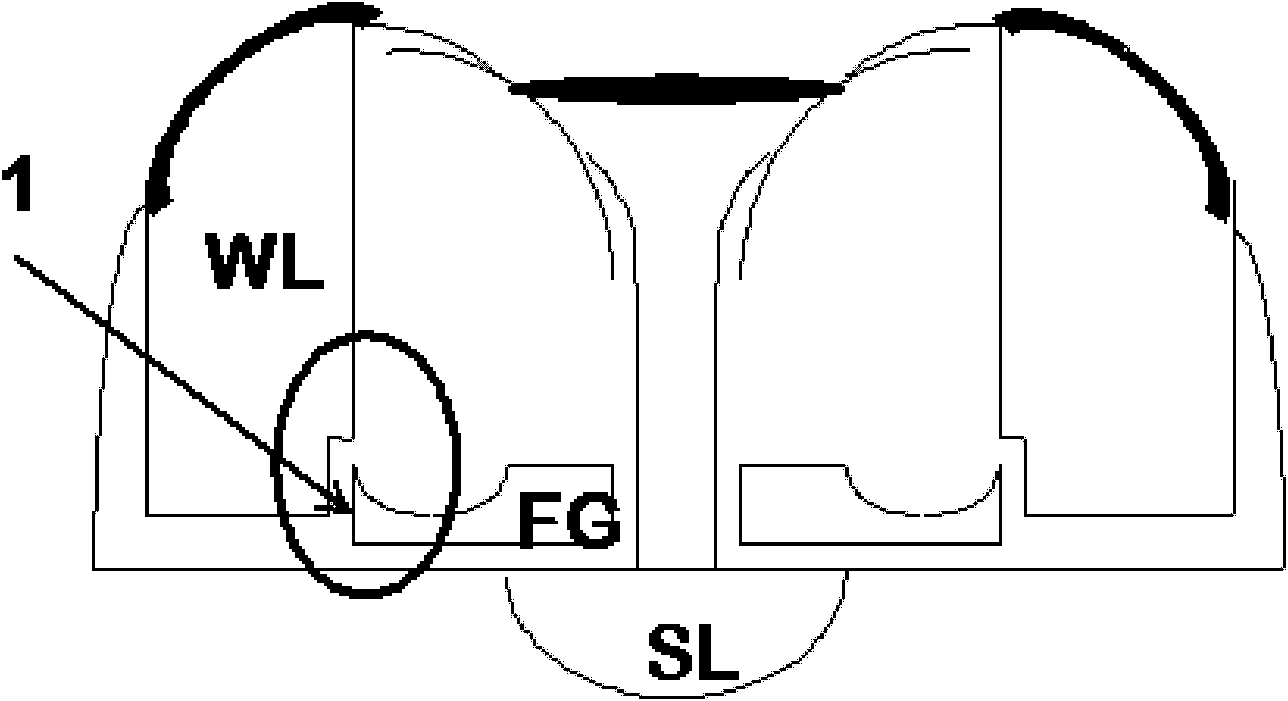

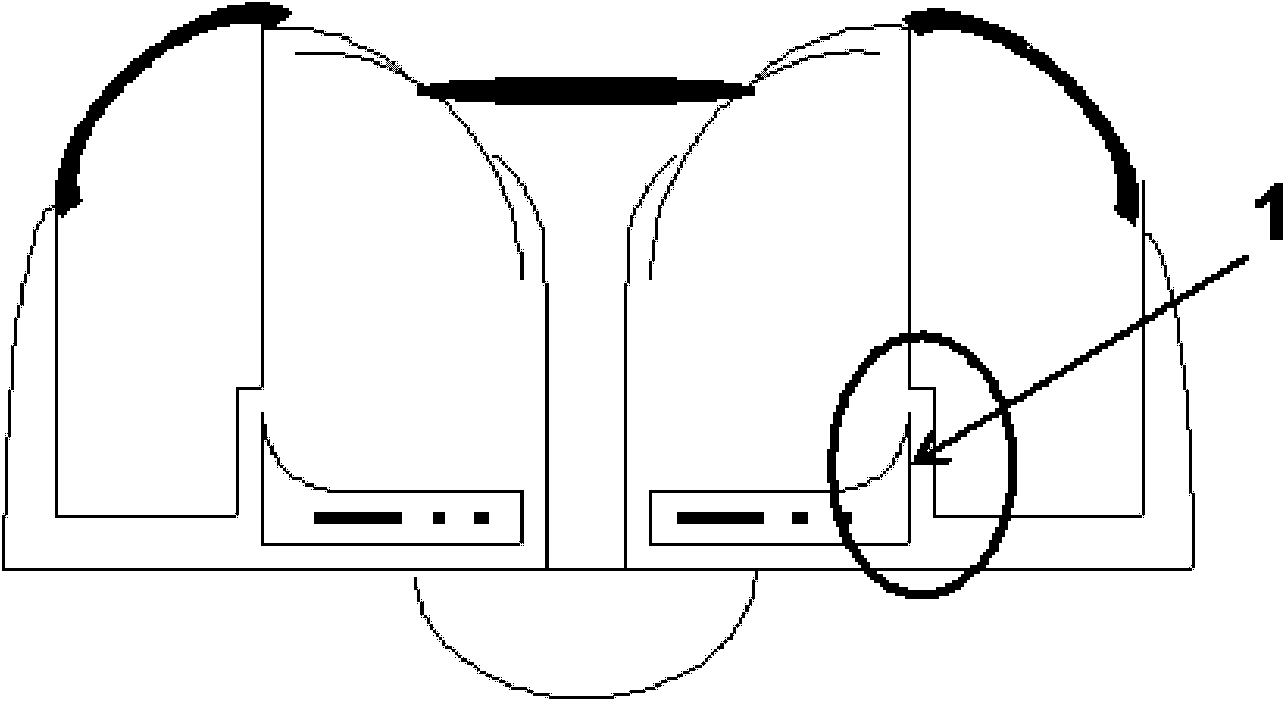

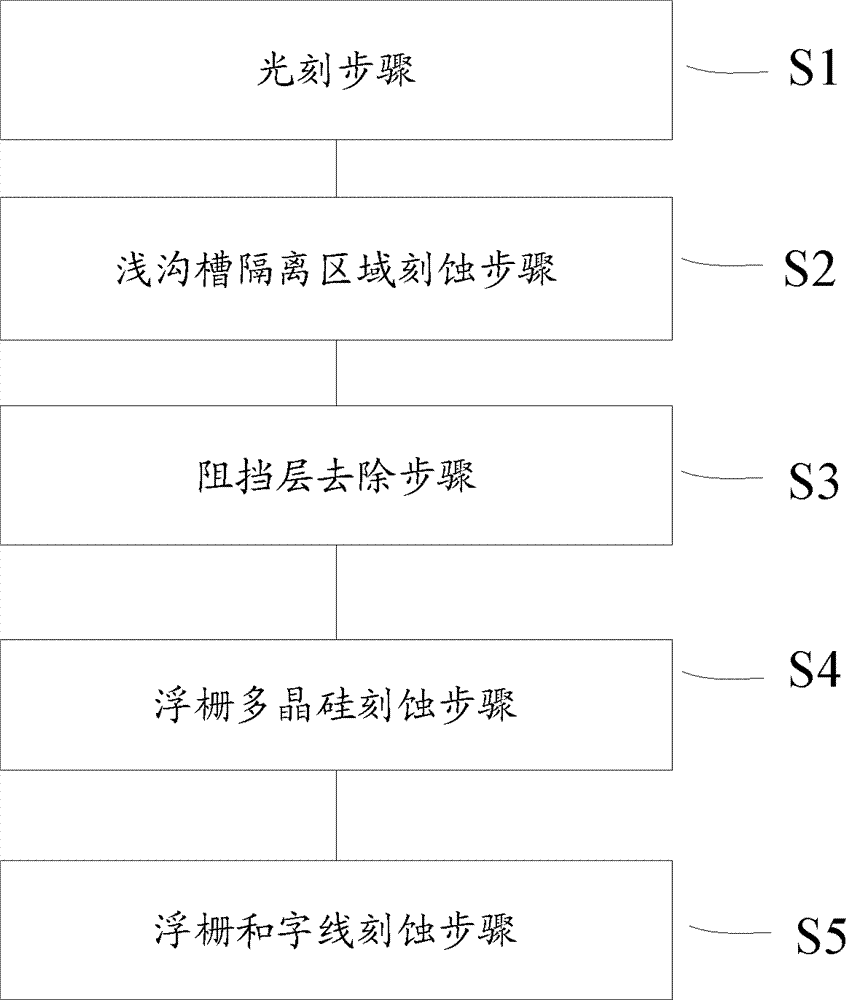

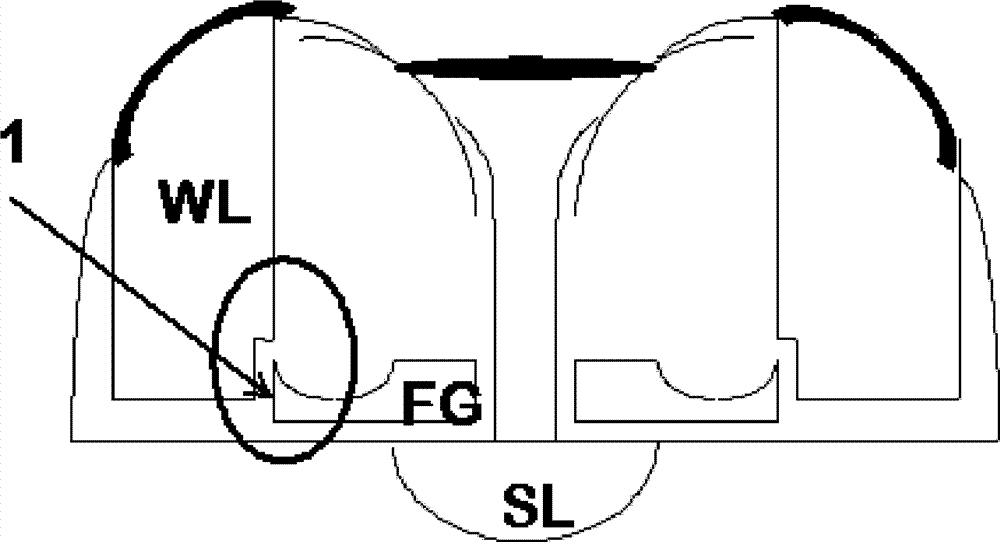

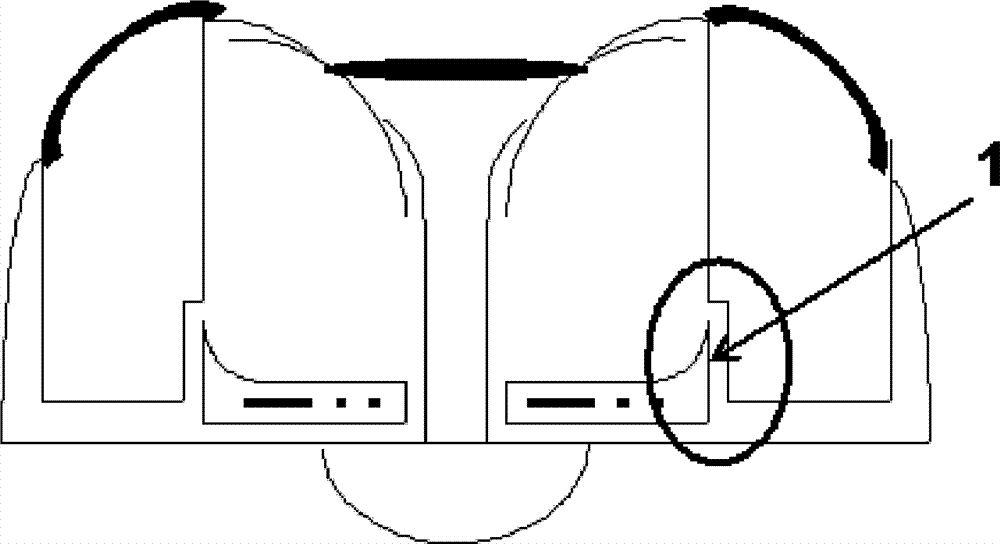

Split-gate type memory and manufacturing method thereof

ActiveCN102222646ADoes not increase production costsLower the altitudeTransistorSemiconductor/solid-state device manufacturingCapacitanceVoltage

The invention provides a split-gate type memory and a manufacturing method thereof. According to the manufacturing method of the split-gate type memory, provided by the invention, the method comprises: a photoetching step for defining a shallow trench isolated region; a step for etching the shallow trench isolated region, wherein the height of the shallow trench isolated region of a word line region of a unit array in the split-gate type memory is reduced; a barrier layer removing step for removing the barrier layers of the regions not covered by photoresistance; a floating gate (FG) polysilicon etching step for etching floating gate polysilicon not covered by the photoresistance; and an FG and word line etching step for etching an FG and a word line. The height of the top end of the FG of the split-gate type memory manufactured according to the manufacturing method of the split-gate type memory, provided by the invention, is lowered, the capacitance between the FG and the word line is reduced, and the capacitance between the FG and a select line is maintained invariable, therefore, the capacitance coupling efficiency is accordingly reduced so as to be helpful to improving programming efficiency and reducing an erasing voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for manufacturing split-gate memory and split-gate memory

ActiveCN102222646BDoes not increase production costsLower the altitudeTransistorSemiconductor/solid-state device manufacturingCapacitanceCapacitive coupling

The invention provides a split-gate type memory and a manufacturing method thereof. According to the manufacturing method of the split-gate type memory, provided by the invention, the method comprises: a photoetching step for defining a shallow trench isolated region; a step for etching the shallow trench isolated region, wherein the height of the shallow trench isolated region of a word line region of a unit array in the split-gate type memory is reduced; a barrier layer removing step for removing the barrier layers of the regions not covered by photoresistance; a floating gate (FG) polysilicon etching step for etching floating gate polysilicon not covered by the photoresistance; and an FG and word line etching step for etching an FG and a word line. The height of the top end of the FG of the split-gate type memory manufactured according to the manufacturing method of the split-gate type memory, provided by the invention, is lowered, the capacitance between the FG and the word line is reduced, and the capacitance between the FG and a select line is maintained invariable, therefore, the capacitance coupling efficiency is accordingly reduced so as to be helpful to improving programming efficiency and reducing an erasing voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

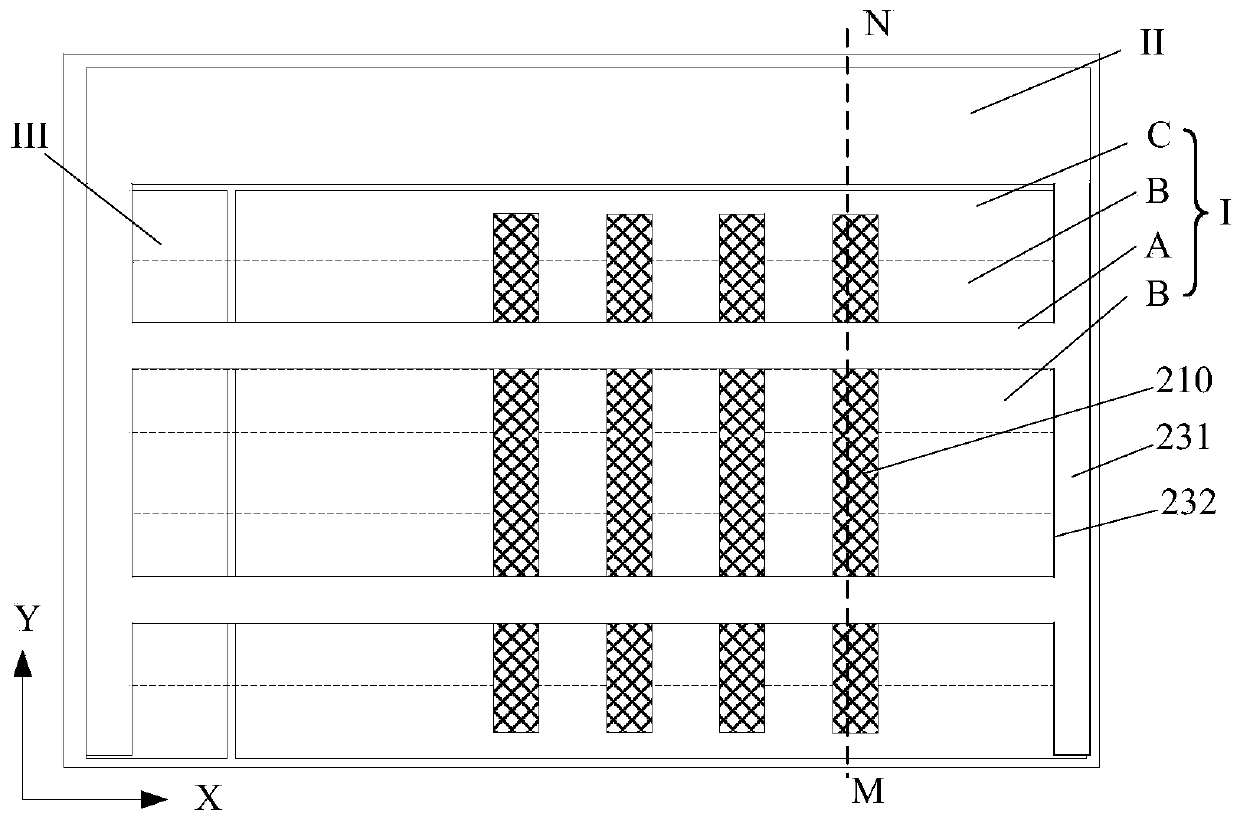

Split gate type memory and formation method thereof

ActiveCN109950245ASmall sizeGuaranteed Coupling CoefficientSolid-state devicesSemiconductor devicesEngineeringSource area

The invention relates to a split gate type memory and a formation method thereof The split gate type memory comprises a substrate, an erasing gate, a floating gate, a word line and insulating layers;source and drain areas are formed on the substrate, and a source line in contact connection with the source area is formed on the source area; the erasing gate is arranged on the source line; the floating gate and word line are arranged horizontally adjacent to each other on the substrate between the source and drain areas, the floating gate is close to the source line, and the word line is far from the source line; and the insulating layers are formed between the source line, erasing gate, floating gate and word line. The source line higher than the upper surface of the substrate is arranged,so that the floating gate and the source area form an overlapped area in the vertical direction, and the height of the source line is adjustable, so that a coupling efficiency between the floating gate and the source area is ensured while the wafer size is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for manufacturing flash memory floating gate

ActiveCN101414555AEase of cutting-edge optimizationSmall fluctuationSolid-state devicesSemiconductor/solid-state device manufacturingCompound (substance)Silicon dioxide

The invention discloses a method for manufacturing a flash floating gate, a bowl-shaped groove of the floating gate is formed by isotropic dry etching with the help of a photoresist mask; then silicon dioxide is deposited in the bowl-shaped groove, the silicon dioxide which is positioned at the outside of the bowl-shaped groove is removed by using the chemical polishing method, thereby forming the floating gate; and then polycrystalline silicon which is positioned out of a flash unit is removed by the self-alignment mode with the help of the dry etching to form the acute periphery of the floating gate, thereby ensuring the floating gate structure not to be affected by other operations during the manufacturing process of the flash, further improving the production efficiency and leading the process to be easy in the optimization of the tip of the floating gate and have smaller fluctuations. The method can reduce the erase failure and reduce the erase voltage in the implementation of the erase action of the flash, thereby leading the flash unit to be easier to control.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

non-volatile memory

ActiveCN106206588BPromote accumulationThe overall thickness is thinSolid-state devicesSemiconductor devicesGate dielectricInsulation layer

The invention provides a non-volatile memory, which has a storage unit. The memory cell has a stacked structure, first and second floating gates, an erasure gate dielectric layer, an auxiliary gate dielectric layer, first and second doped regions, and first and second control gates. The stacked structure has a gate dielectric layer, an auxiliary gate, an insulation layer and an erasure gate arranged in sequence. The first and second floating gates are respectively disposed on sidewalls on both sides of the stacked structure. The erase gate dielectric layer is disposed between the erase gate and the first and second floating gates. The auxiliary gate dielectric layer is disposed between the auxiliary gate electrode and the first and second floating gate electrodes. The first and second doping regions are respectively disposed on both sides of the stack structure and the first and second floating gates. The first and second control gates are respectively disposed on the first and second floating gates. The present invention can operate at low operating voltage, thereby increasing the reliability of semiconductor components.

Owner:IOTMEMORY TECH INC +1

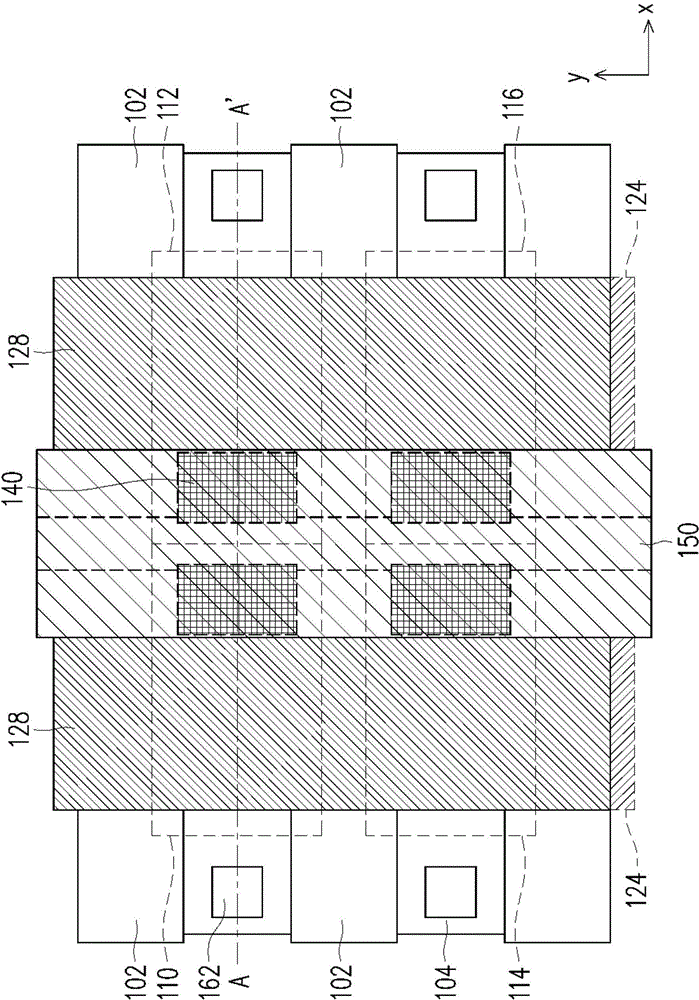

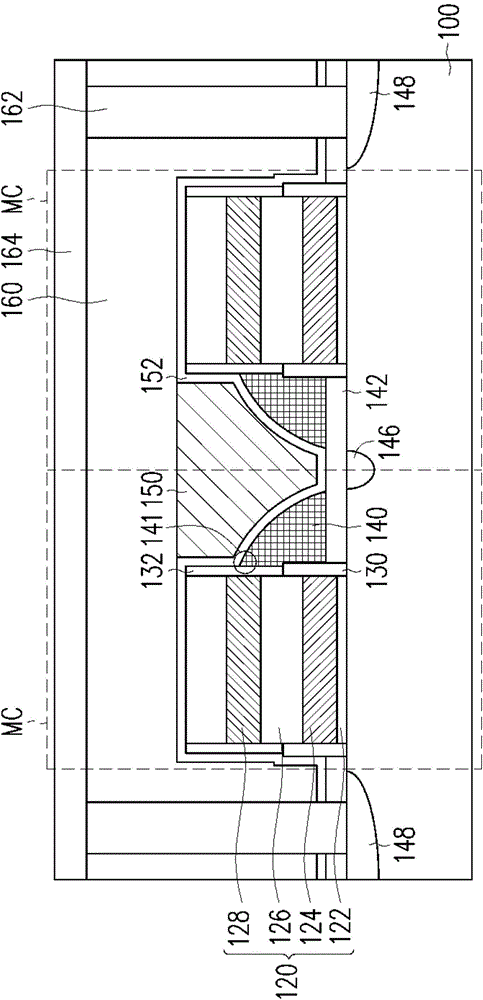

Memory and method of forming the same

ActiveCN109712981BSimple processSave a patterning processSolid-state devicesSemiconductor devicesBit lineEngineering

A memory and its formation method. The method includes: providing a substrate. The substrate includes an erasure area, a floating gate area and a word line bit line area arranged along a first direction. The floating gate area is located on both sides of the erasure area, and the word line area is arranged along a first direction. The line bit line area is located on both sides of the erase area and the floating gate area; a floating gate structure film and a dielectric layer located on the floating gate structure film are formed on the substrate, and the floating gate area and word line are exposed in the dielectric layer The first opening of the floating gate structure film in the bit line area; forming a first spacer on the sidewall of the first opening; forming a control gate film at the bottom of the first opening; forming a second spacer on the sidewall of the first spacer ; Remove the control gate film and floating gate structure film exposed by the first sidewall, the second sidewall and the dielectric layer to form a floating gate structure layer, a control gate layer and a second opening; remove the dielectric on the erased area layer and a floating gate structure layer to form a third opening and a floating gate structure; an erasure gate structure is formed in the third opening. The method improves memory production efficiency.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Flash memory device and method of operation

ActiveUS20110255337A1Reduce the erase voltageAvoid over-erasingRead-only memoriesDigital storageBit lineHemt circuits

A NAND flash memory device and method of erasing memory cells thereof, wherein each cell is only subjected to the level of erase voltage needed to restore its nominal “erased” state. Each memory cell of the NAND flash memory device comprises a floating gate, a control gate connected to a wordline and receives a control voltage therefrom to induce a programming charge on the floating gate, and a bitline adapted to apply an erase voltage to deplete the floating gate of the programming charge. Each memory cell further includes circuitry for modulating the erase voltage according to the level of the programming charge on its floating gate.

Owner:KIOXIA CORP

A making method of EEPROM for increasing coupling voltage of float grating

ActiveCN100501926CIncrease capacitanceImprove writing efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEtching

The invention discloses an EEPROM manufacture method which can increase the floating gate coupling voltage. The method besides includes steps of growing a high voltage oxide film, carrying out channel etching, growing a layer of channel oxides, growing a layer of floating gate polycrystals, growing a ONO, and growing two layers of the polycrystals; the floating gate etching is carried out after growing a layer is carried out and before growing the ONO is carried out. A pattern of the floating gate etching is composed of a cubic block or a plurality of small cubic blocks. Because the invention increases one time floating gate etching and the capacitance of the ONO in a traditional EEPROM manufacture method, that is, the coupling ratio and the coupling voltage of the floating gate are increased, the recordable efficiency of the EEPROM can be enhanced or the recordable voltage is decreased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Erasing method for nonvolatile memory

ActiveUS20100322014A1Erase the nonvolatile memoryErasing timeRead-only memoriesDigital storageBody contactElectric field

The present invention relates to an erasing method for nonvolatile memory, which uses forward bias between the source / drain region and body contact to inject majority carriers into the body, and then accelerates the majority carriers by an electric field between the body and the gate to energize the majority carriers to overcome the oxide barrier and to erase the nonvolatile memory.

Owner:ACER INC

Split-gate flash memory and forming method thereof

PendingCN112530956AImprove erase effectImproved Durability PropertiesTransistorSolid-state devicesMemory cellDynamic power dissipation

According to the split-gate flash memory and the forming method thereof provided by the invention, in the forming method of the split-gate flash memory, the floating gate tip is formed while the floating gate is formed, no process step is added in the whole process, and meanwhile, the newly added floating gate tip enhances the erasure capability of a memory cell and greatly improves the numericalvalue of current Ir1, so reliability of the memory cell is improved; the erase voltage on the erase gate during erase is reduced, so that the read operation interference is reduced, and the static power consumption and the dynamic power consumption of the split-gate flash memory for low-voltage read operation are reduced; in addition, the source line formed by the subsequent process only influences the erasing efficiency and does not influence the channel, so durability characteristic of the memory unit can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP