A making method of EEPROM for increasing coupling voltage of float grating

A production method and coupling voltage technology, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve problems such as operating voltage and erasing rate limitations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

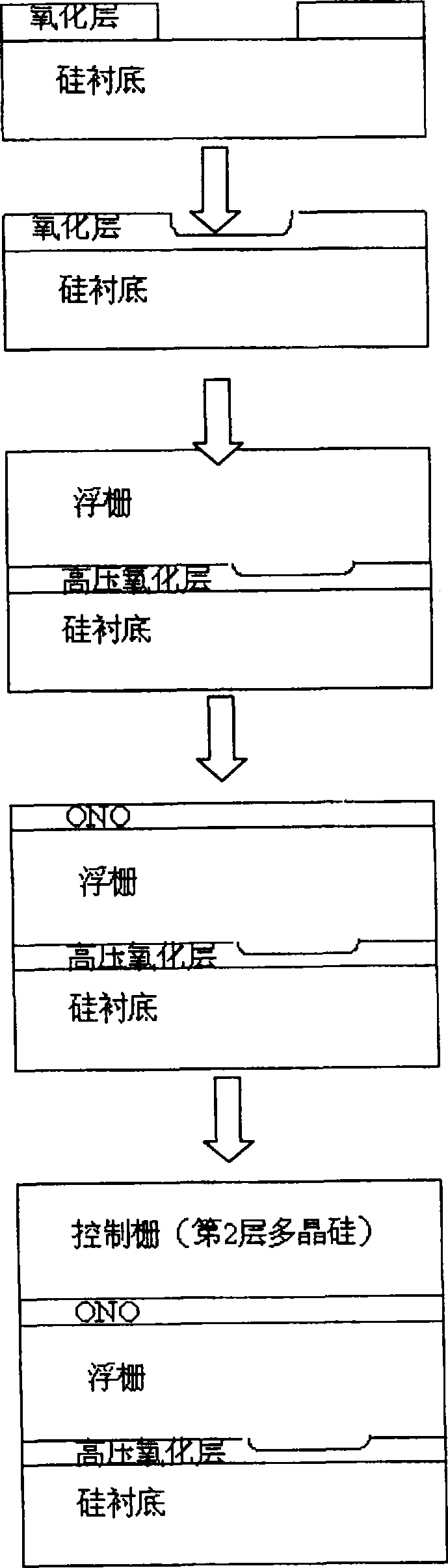

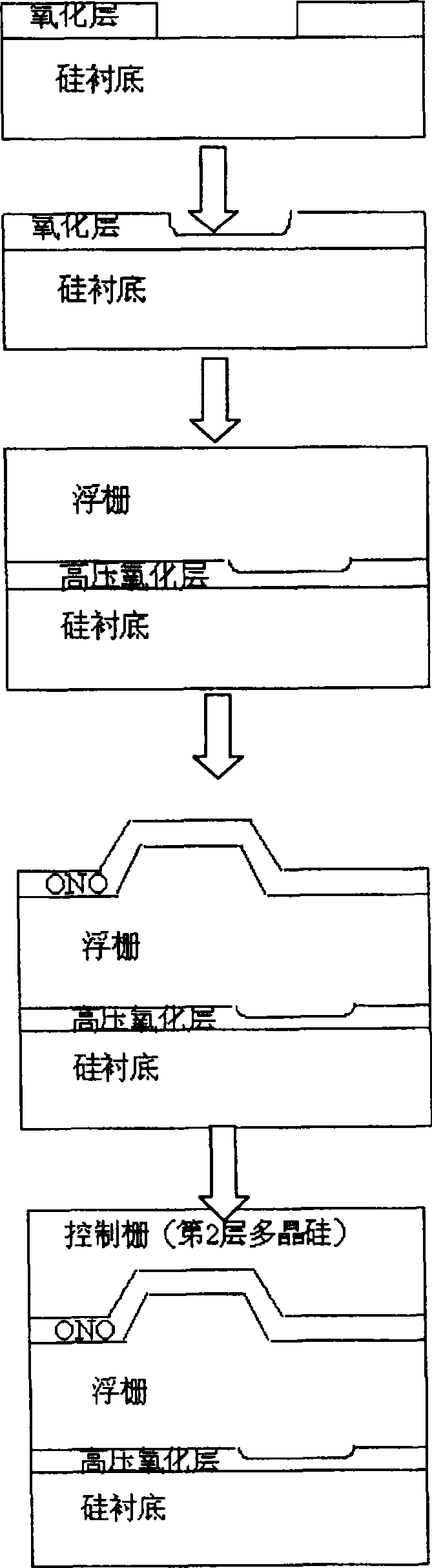

[0017] Such as figure 2 Shown is a specific embodiment of the method of the present invention.

[0018] Such as figure 2 , same as the production of the usual EEPROM, in this embodiment, a high-voltage oxide film is first grown, and then tunnel etching is performed; then a layer of 80A tunnel oxide is grown; and a layer of 1500A floating poly is grown; this embodiment and the traditional method The difference is that a step is added at this time, that is, floating gate etching. In this case, it is to dig a hole on the tunnel window; then grow ONO with a thickness of 60 / 60 / 60A (angstroms); then grow Poly2, The thickness is 2000A; the next steps are the same as the usual EEPROM production method.

Embodiment 2

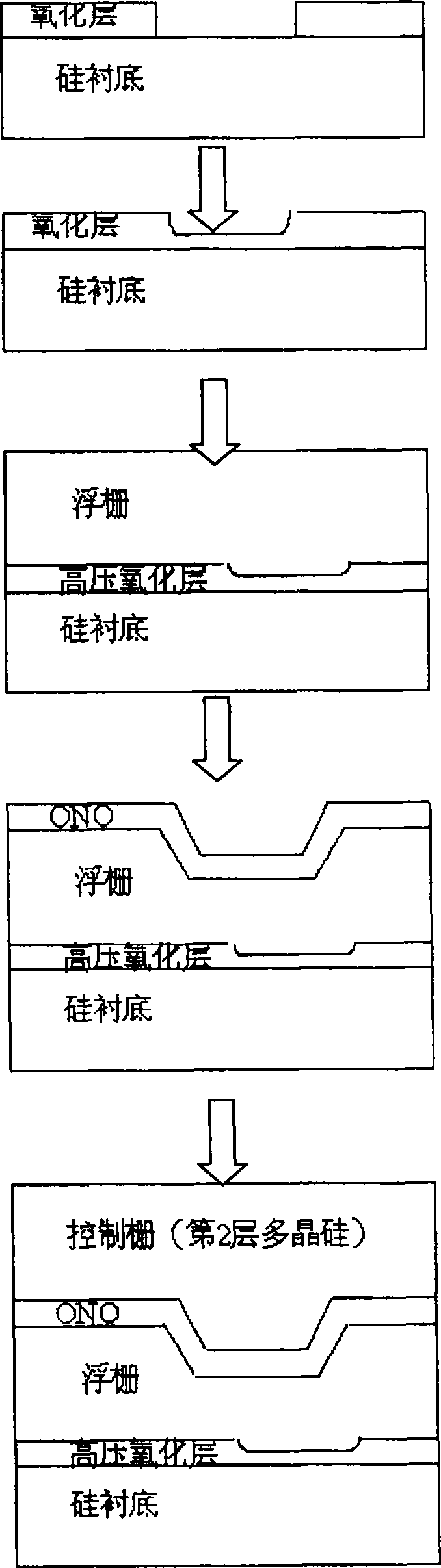

[0020] Such as image 3 Shown is another specific embodiment of the method of the present invention.

[0021] This example is the same as figure 2 The most important difference of the shown embodiment is that the etching pattern of the floating gate is different. In the above example, a hole is dug on the tunnel window, but in this example, the poly on the tunnel window is retained, and the poly next to it is dug out.

[0022] Figure 6 It is the effect comparison diagram of the inventive method and the traditional method, wherein Fig. a is the usual EEPROM storage unit structure under the traditional method, and Fig. b is figure 2 The structure of the EEPROM memory cell with increased floating gate etching shown in Figure c is image 3 Shown is the EEPROM memory cell structure with increased floating gate etching.

[0023] Next, let's compare the ONO capacitance and erase / write coupling ratio of the EEPROM Cell after adding an EEPROM floating gate etching (including dif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More