Splitting grid memory cell and operation method thereof

A technology of storage unit and operation method, applied in information storage, static memory, read-only memory, etc., can solve the problems of high cost and high cost of photomask, and achieve the effect of simplifying process steps, improving yield, and ensuring reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

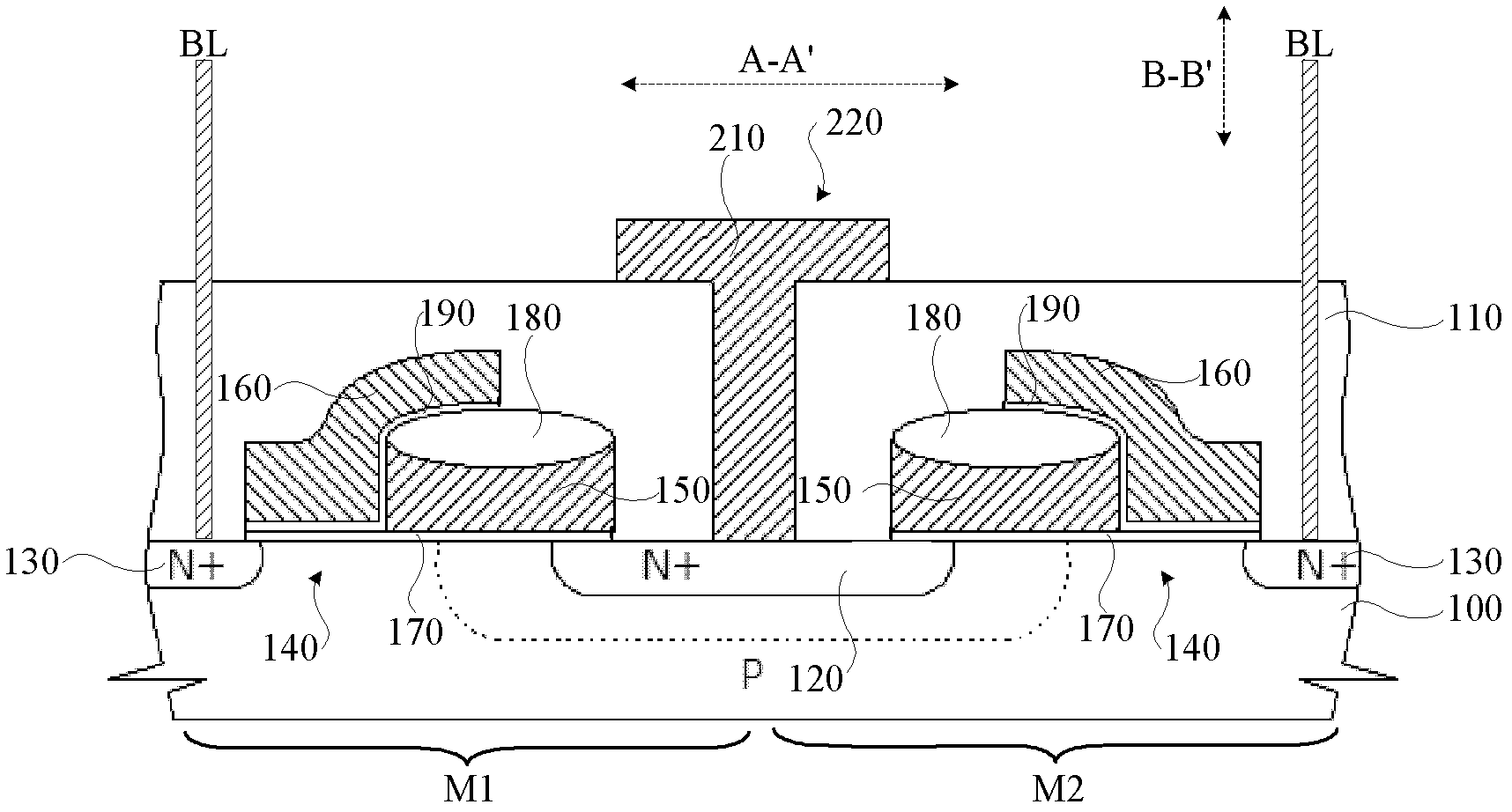

[0038]From the foregoing analysis, it can be seen that in the prior art, the voltage required for erasing the memory cell is 12V, and the positive 12V voltage is applied to the control gate, so it is necessary to form a 12V power supply circuit, but the technology in the art As is known to all, the size of the 12V device is relatively large, the production process is complicated, and the manufacturing cost is relatively high, which results in a large overall size and high cost of the memory unit.

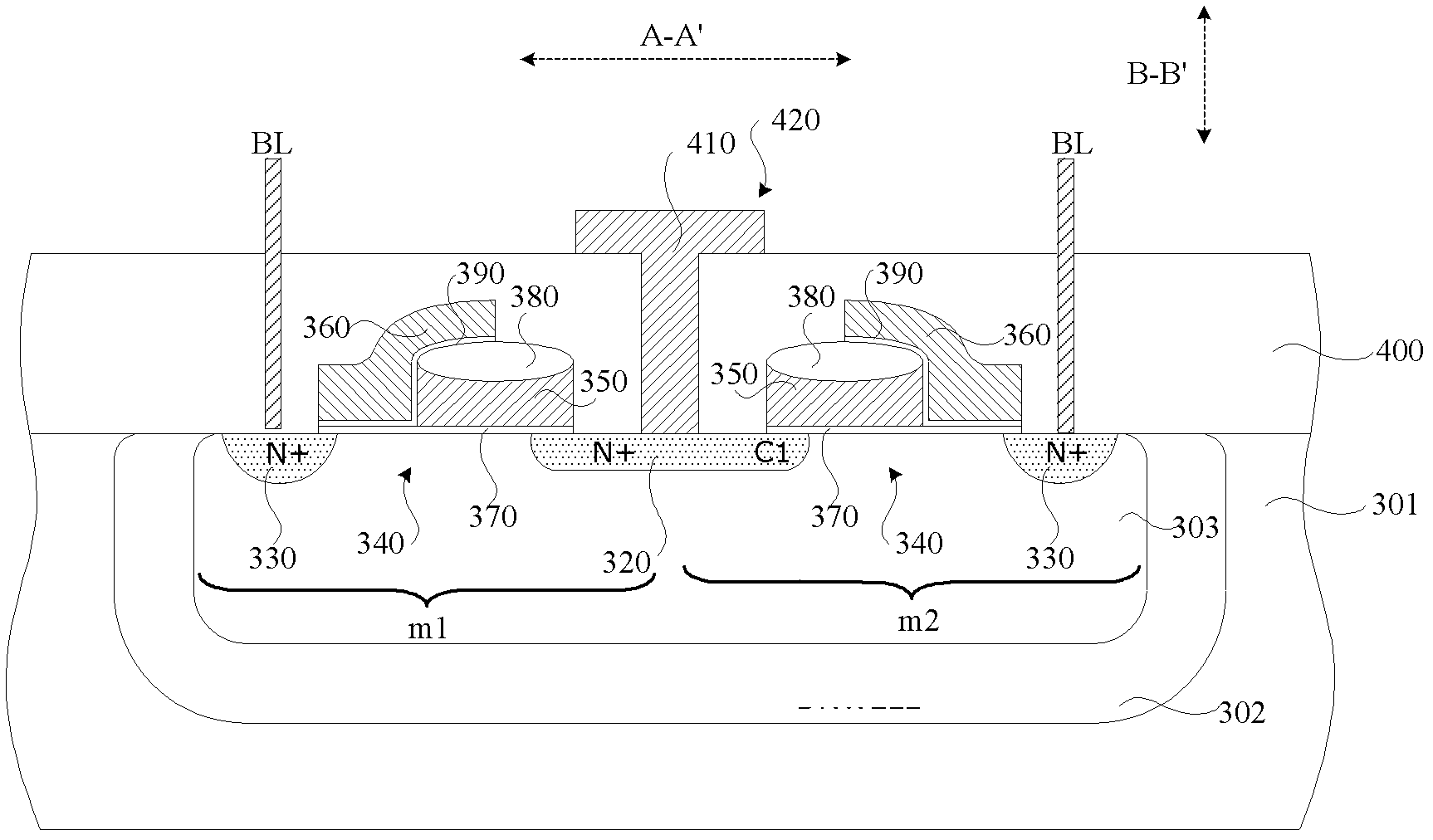

[0039] In order to solve this problem, the split gate memory cell of the present invention forms three doped regions (i.e. the first doped region, the second doped region and the third doped region) sequentially in its semiconductor substrate, so that in When erasing the memory cell, a negative erasing voltage can be applied to the third doped region. In this way, the forward erasing voltage applied to the control gate can be reduced, so that the formation of a 12V power supply circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More