Split gate type memory and formation method thereof

A split-gate memory, floating gate technology, applied in the direction of electric solid devices, semiconductor devices, electrical components, etc., can solve the problems of wafer size reduction, coupling area influence, etc., to reduce the coupling coefficient, reduce the erasing voltage, The effect of increasing the coupling area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] In order to describe the technical solution of the above invention in more detail, specific examples are listed below to demonstrate the technical effect; it should be emphasized that these examples are used to illustrate the present invention and not limit the scope of the present invention.

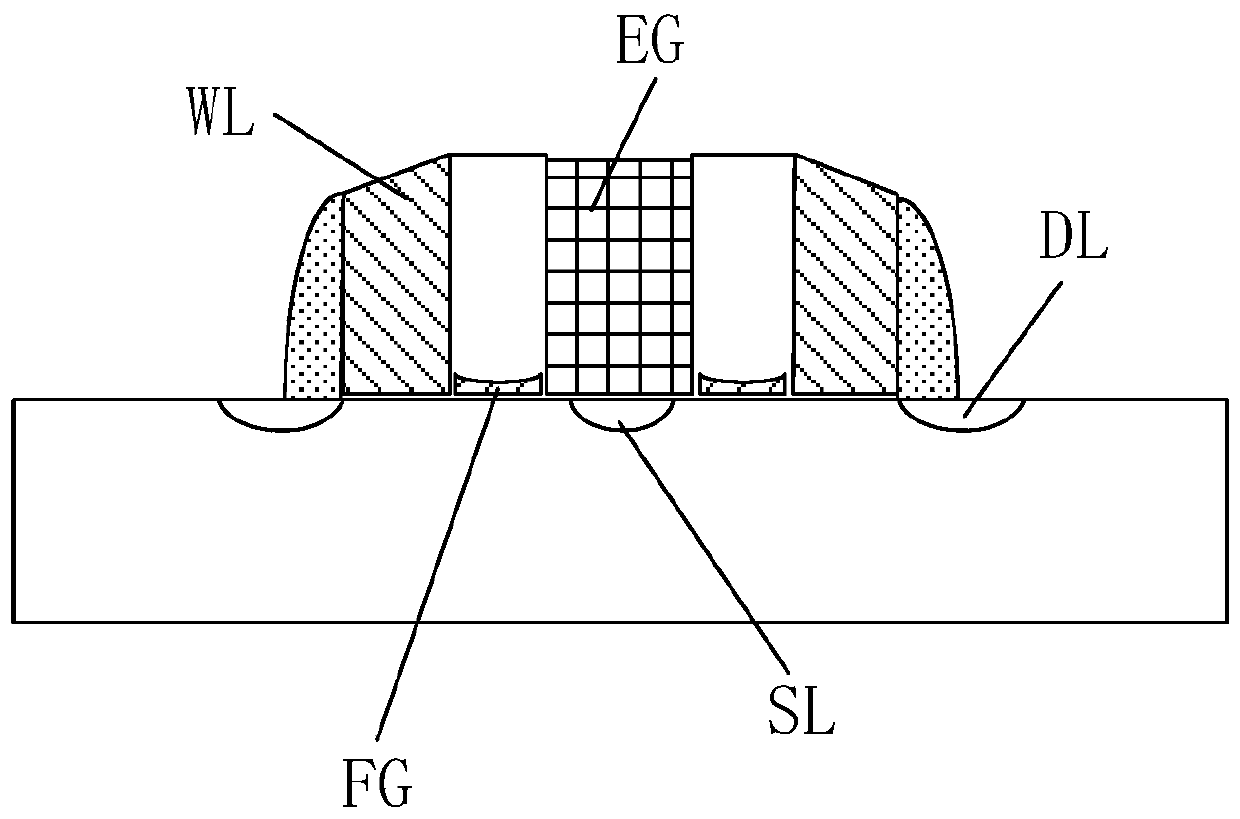

[0056] For the split-gate memory provided by the present invention, please refer to Figure 2s ,include:

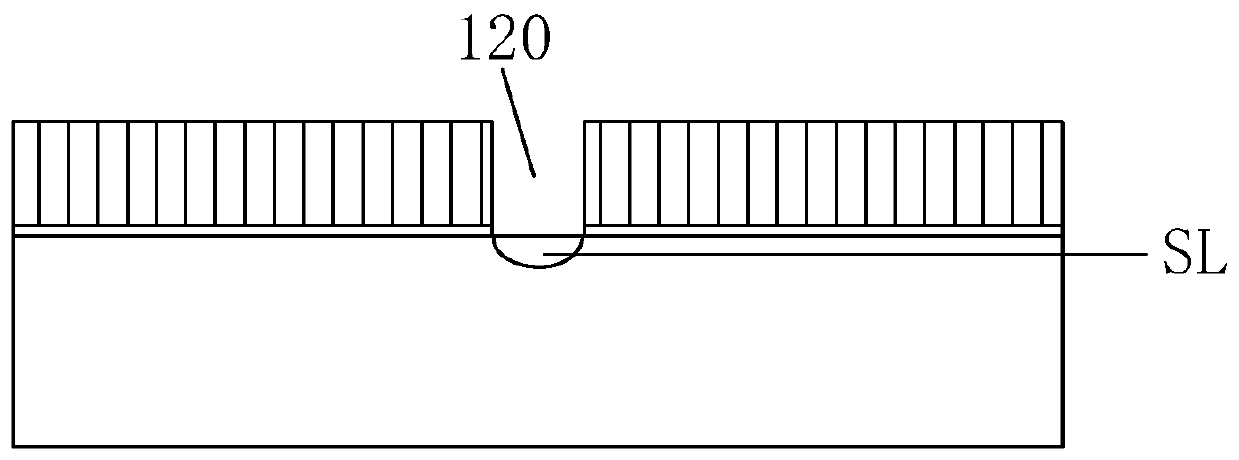

[0057] A substrate 100, on which a source region SL and a drain region DL are formed, and a source line 200 contacting and conducting with the source region SL is arranged above the source region SL, as extension of the source;

[0058] an erase gate 400 disposed above the source line 200; and

[0059] The floating gate FG and the word line WL are laterally adjacently arranged on the substrate 100 between the source region SL and the drain region DL, wherein the floating gate FG is close to the source line 200, so The word line WL is far away from the source line 200;

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More