Double-gate ferroelectric transistor, preparation method and data erasing and reading method

A technology of ferroelectric transistors and gate electrodes, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of not meeting the application requirements of high-performance devices, limited fatigue times of transistors, and poor anti-fatigue characteristics. Small programming and erasing voltages and operating voltages, avoiding voltage division, and improving the effect of anti-fatigue characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

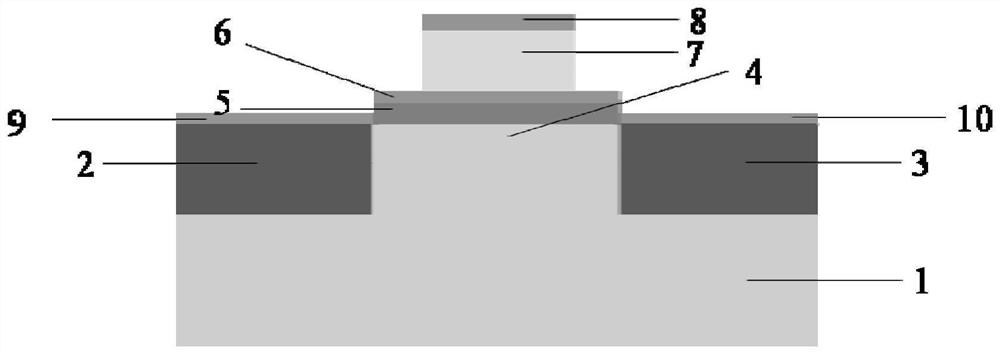

[0038] like figure 1 As shown, the present invention discloses a dual-gate ferroelectric transistor, comprising a substrate 1 and a channel 4, the channel 4 is arranged above the substrate and in the middle of the substrate, and the channels 4 are respectively arranged on both sides There are a source region 2 and a drain region 3; the source region 2 is provided with a source electrode 10, the drain region 3 is provided with a drain electrode 9, and the channel 4 is sequentially provided with Insulation layer 5 , lower gate electrode 6 , ferroelectric gate dielectric layer 7 and upper gate electrode 8 .

[0039] figure 1 The double-gate ferroelectric transistor can be obtained according to the preparation method of implementation 2. Those skilled in the art can also use other methods to obtain figure 1 Structure of a double-gate ferroelectric transistor. The insulating layer 5 will carry a relatively high voltage in conventional technical means and is easily broken down. ...

Embodiment 2

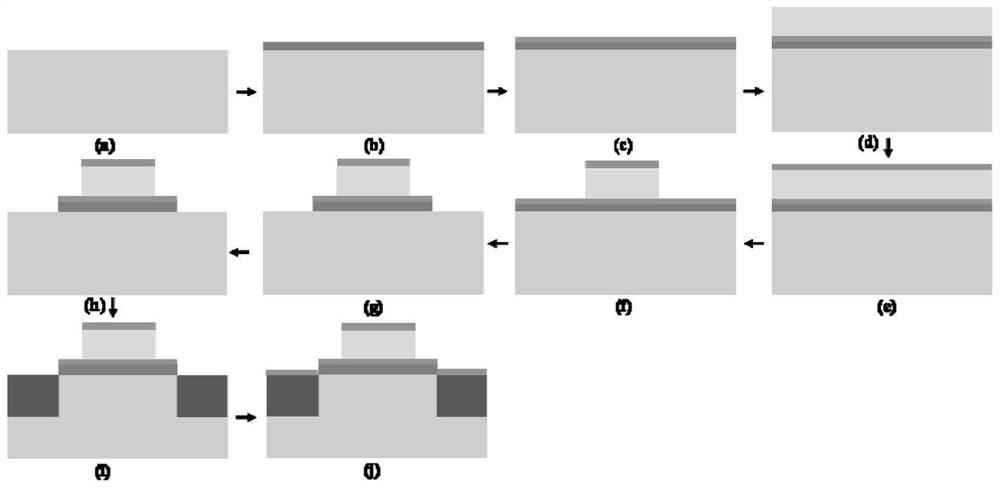

[0052] see image 3 , the invention discloses a preparation method of a double-gate ferroelectric transistor, comprising:

[0053] The substrate 1 is cleaned, and a SiO2 insulating layer 5 is grown on the substrate 1 through a dry oxygen process, see image 3 (a)(b);

[0054] A magnetron sputtering process is used to deposit TaN on the SiO2 insulating layer 5 to form a lower gate electrode 6, see image 3 (c);

[0055] A HfZrOx film is deposited on the lower gate electrode 6 to form a ferroelectric gate dielectric layer 7, see image 3 (d);

[0056] The magnetron sputtering process is used to deposit TaN on the ferroelectric gate dielectric layer 7 to form the upper gate electrode 8, see image 3 (e);

[0057] Using a photolithography process, the region of the upper gate electrode 8 is marked on the upper gate electrode 8;

[0058] Using an etching process, the excess parts around the area of the upper gate electrode 8 are etched to the surface of the lower gate elec...

Embodiment 3

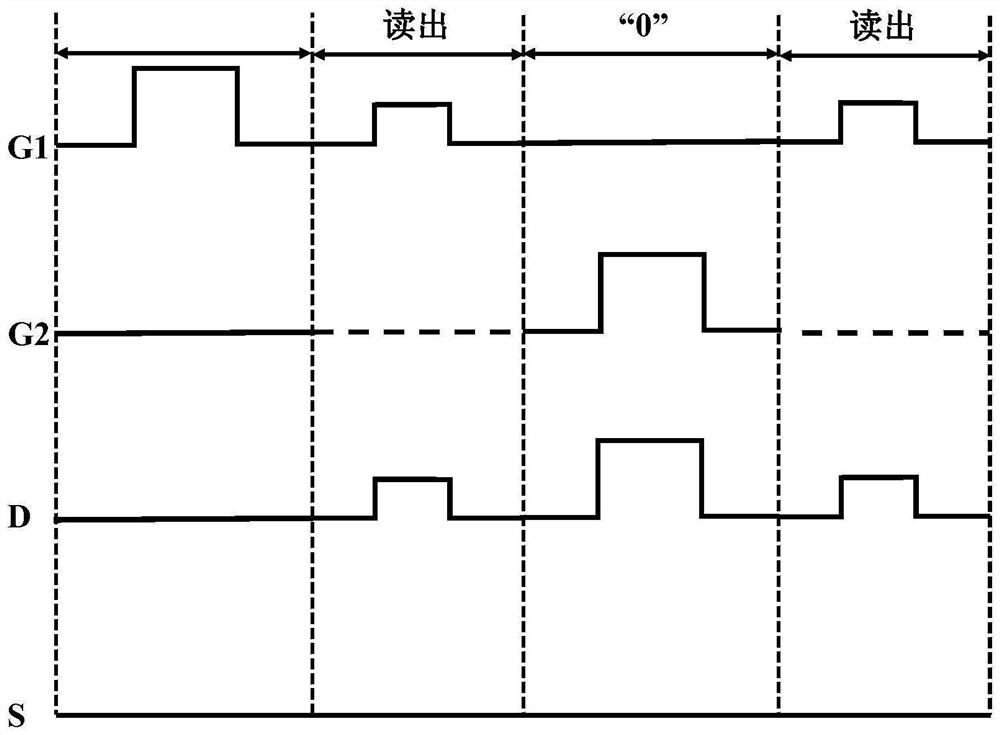

[0079] The switching electrode type data erasing / reading method of the present invention is realized based on the double-gate ferroelectric field effect transistor of the structure of the first embodiment. The timing diagram of the voltage changing with time for erasing and reading is as follows figure 2 As shown, the voltage waveform of the upper gate electrode 8 corresponds to G1, the voltage waveform of the lower gate electrode 6 corresponds to G2, the voltage waveform of the source electrode 10 corresponds to S, and the voltage waveform of the drain electrode 9 corresponds to D.

[0080] The invention discloses a data erasing, writing and reading method, applying the double-gate ferroelectric transistor described in Embodiment 1,

[0081] When writing data: a positive pulse voltage is applied between the upper gate electrode 8 and the lower gate electrode 6, the source electrode 10 is grounded, the potential of the drain electrode 9 and the lower gate electrode 6 are kept...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More