non-volatile memory

A non-volatile, memory technology, applied in semiconductor devices, electrical solid state devices, electrical components, etc., can solve the problems of lower reliability of memory elements, affect the electrical performance of storage cells, wear and tear the tunnel oxide layer, etc., and achieve reduction Effects of erasing voltage, increasing speed, and reducing operating voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

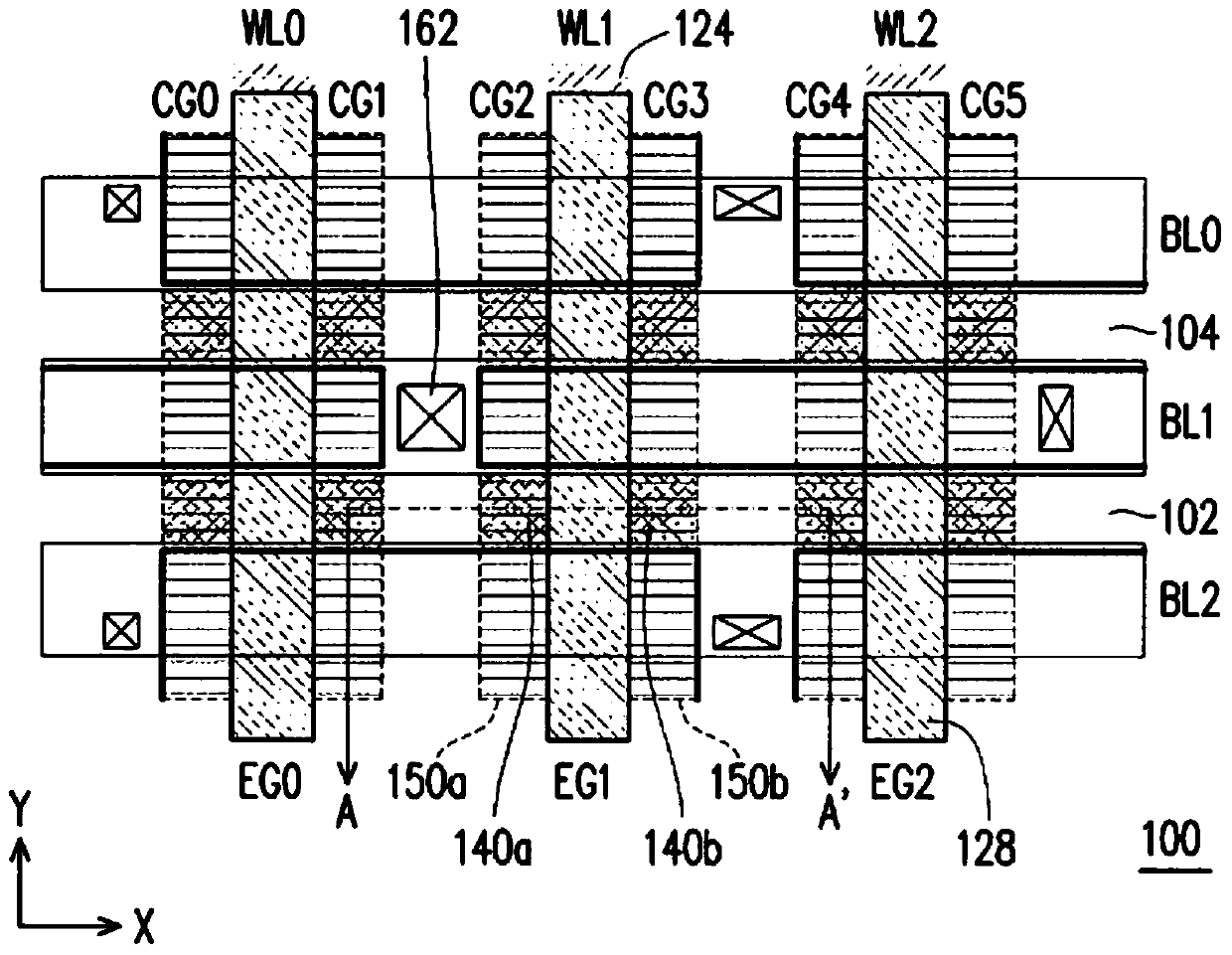

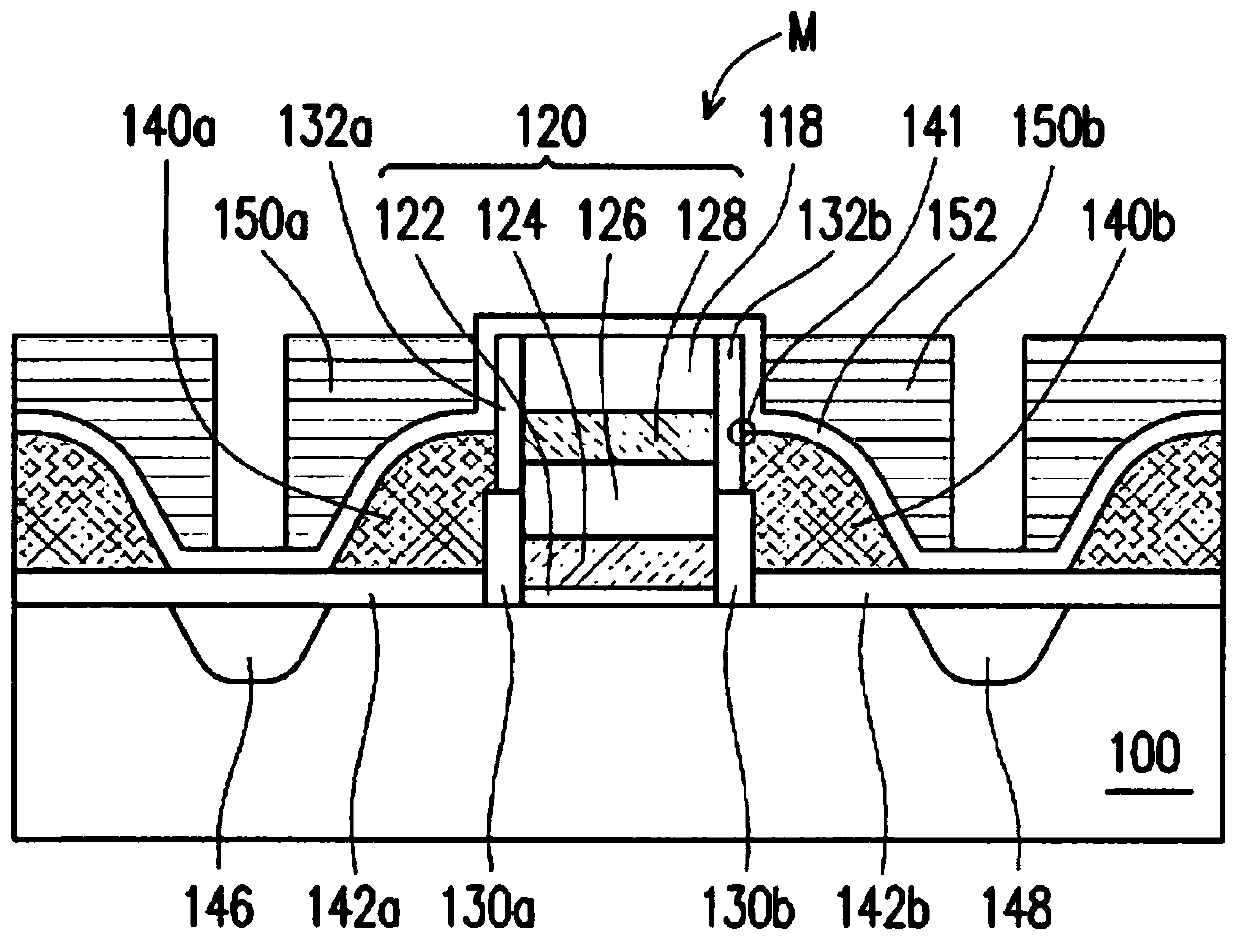

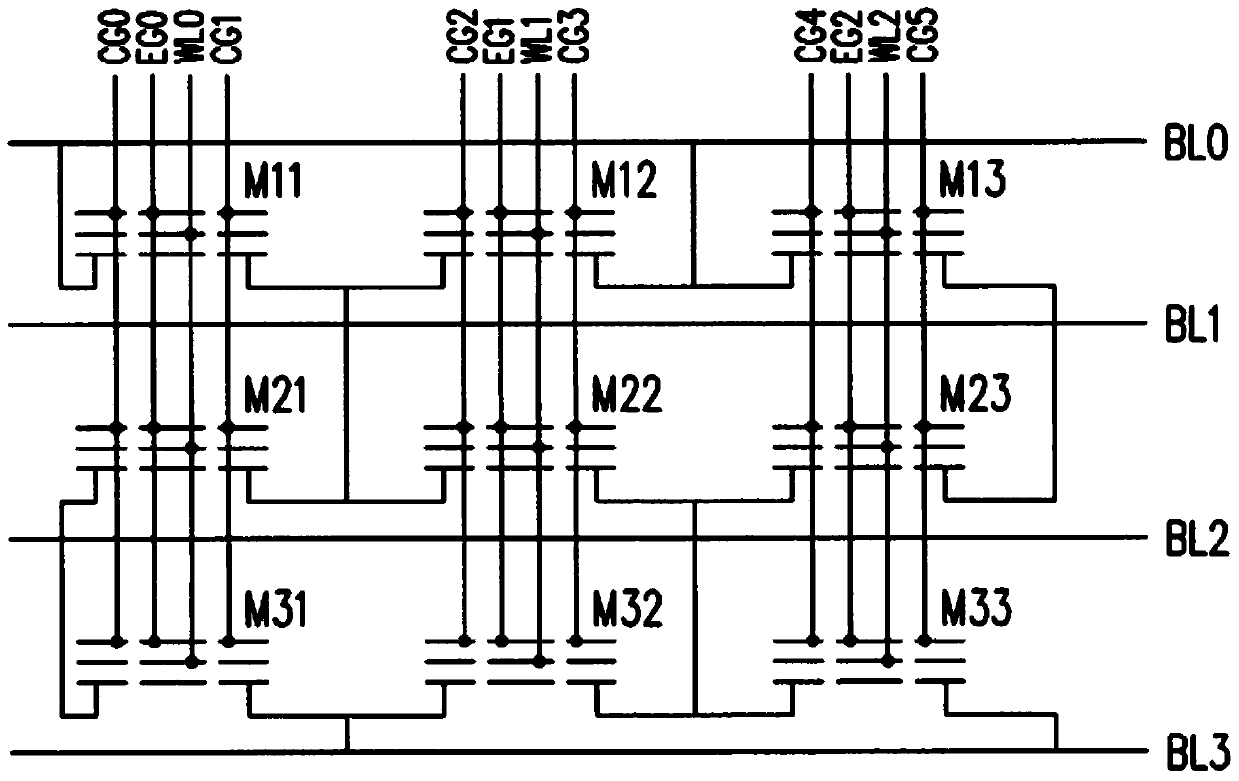

[0068] Figure 1A It is a top view of a non-volatile memory shown in an embodiment of the present invention. Figure 1B It is a schematic cross-sectional view of a non-volatile memory shown in an embodiment of the present invention. Figure 1B shown as along the Figure 1A Sectional view of line A-A' in the middle. Figure 1C It is a schematic circuit diagram of a non-volatile memory shown in an embodiment of the present invention.

[0069] Please refer to Figure 1A , Figure 1B and Figure 1C , the nonvolatile memory includes a plurality of memory cells M11-M33, word lines WL0-WL2, erase lines EG0-EG2, bit lines BL0-BL3, and control gate lines CG0-CG5. The memory cells M11-M33 are arranged in a row / column array.

[0070] A nonvolatile memory is provided on the substrate 100 . For example, an isolation structure 102 is disposed in the substrate 100 to define an active region 104 . The isolation structure 102 is, for example, a shallow trench isolation structure.

[007...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More