Split-gate type memory and manufacturing method thereof

A technology of split-gate memory and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of improving the capacitive coupling rate, gate polysilicon residue, etc., and achieve the improvement of capacitive coupling rate, The effect of reducing erase voltage, increasing process cost and memory production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

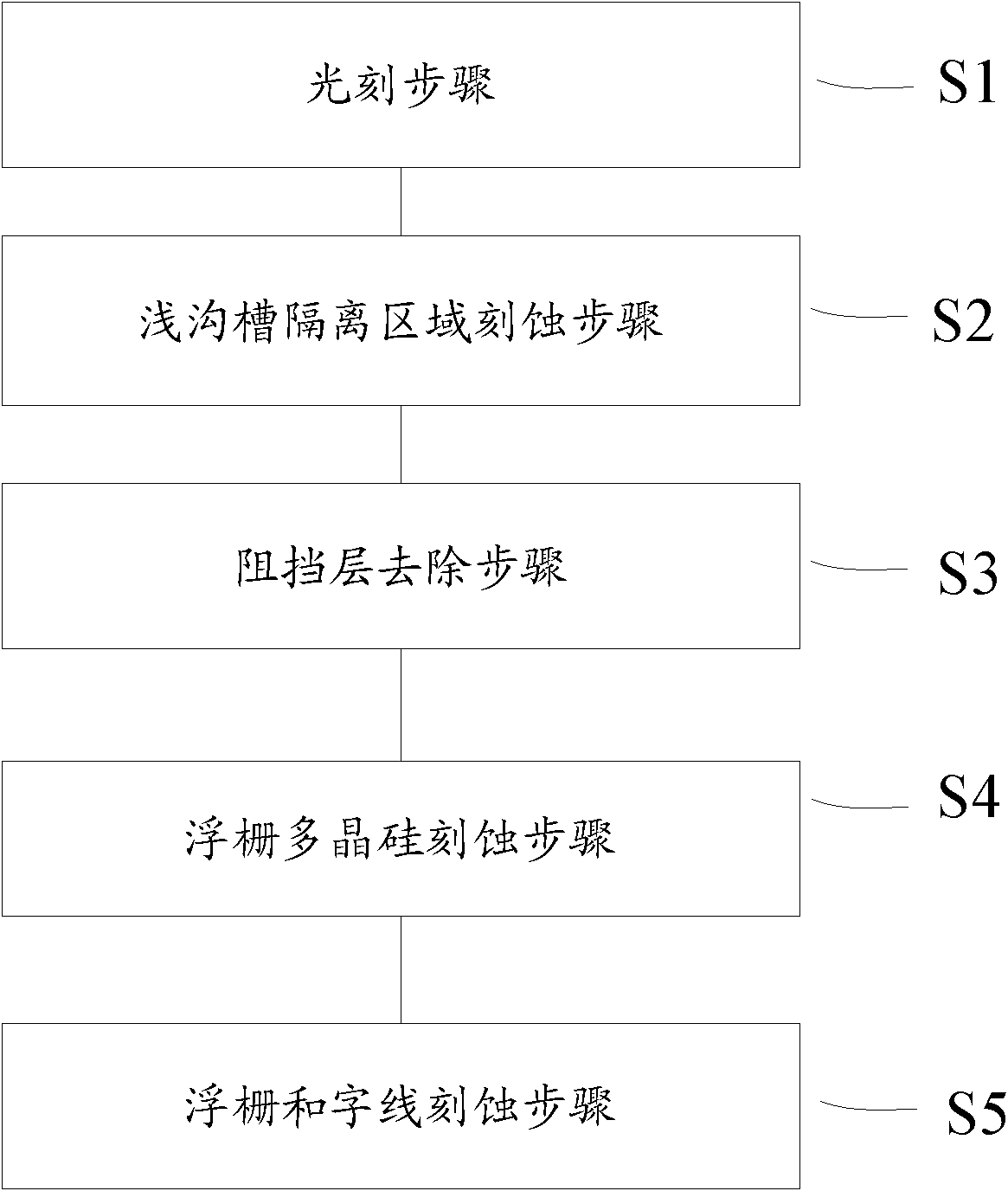

[0024] figure 1 A flow chart of a method for manufacturing a split-gate memory according to an embodiment of the present invention is schematically shown.

[0025] like figure 1 As shown, the manufacturing method of split-gate memory according to the present invention includes:

[0026] First, a photolithography step S1 is performed to define shallow trench isolation regions. For the photolithography step S1, any suitable method known in the art may be used, which is not specifically limited in the present invention.

[0027] The shallow trench isolation area etching step S2 is then performed, wherein the height of the shallow trench isolation in the word line area of the cell array of the split-gate memory is reduced, thereby preventing po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More