Patents

Literature

46results about How to "No increase in process cost" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Low-attenuation and few-mode fiber

ActiveCN104714273ALow DGD valueLow refractive indexOptical fibre with multilayer core/claddingUltrasound attenuationFew mode fiber

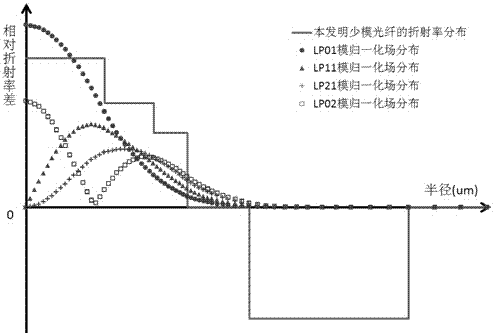

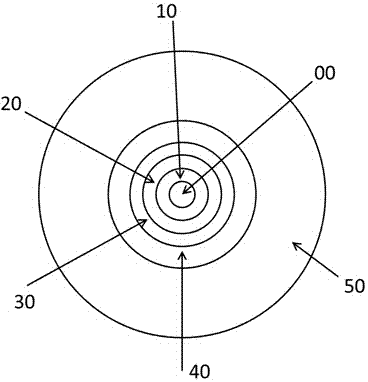

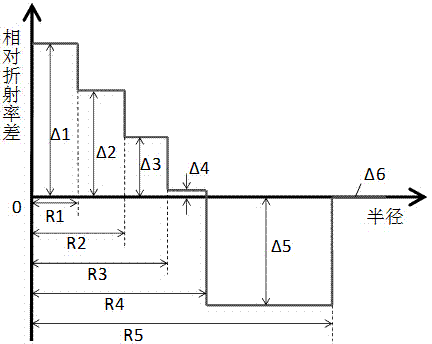

The invention relates to a low-attenuation and few-mode fiber. A core layer has three layers and comprises three claddings from inside to outside; the relative refractive index difference delta 1 of a first core layer is 0.34%-0.45%, R1 ranges from 4.5 mu m to 7.5 mu m, the relative refractive index difference delta 2 of a second core layer is 0.20%-0.29%, R2ranges from8 mu m to 10 mu m, the relative refractive index difference delta 3 of a third core layer is 0.15%-0.24%, R3 ranges from 10 mu m to 13 mu m, the relative refractive index difference delta 4 of a first cladding is minus 0.02%-0.02%, R4 ranges from14 mu m to 18 mu m, the second cladding is a concave cladding, the relative refractive index difference delta 5 of the second cladding is minus 0.8%-minus 0.4%, R5 ranges from19 mu m to 31 mu m, and a third cladding is a pure quartz glass layer. According to the low-attenuation and few-mode fiber, four stable transmission modes are supported within 1550 nm, small DGD is provided, the process is simple, and the manufacturing is easy; at the same time, the low-attenuation and few-mode fiber has low attenuation and better bending resistance.

Owner:SHANTOU HIGH TECH ZONE AOXING OPTICAL COMM EQUIP

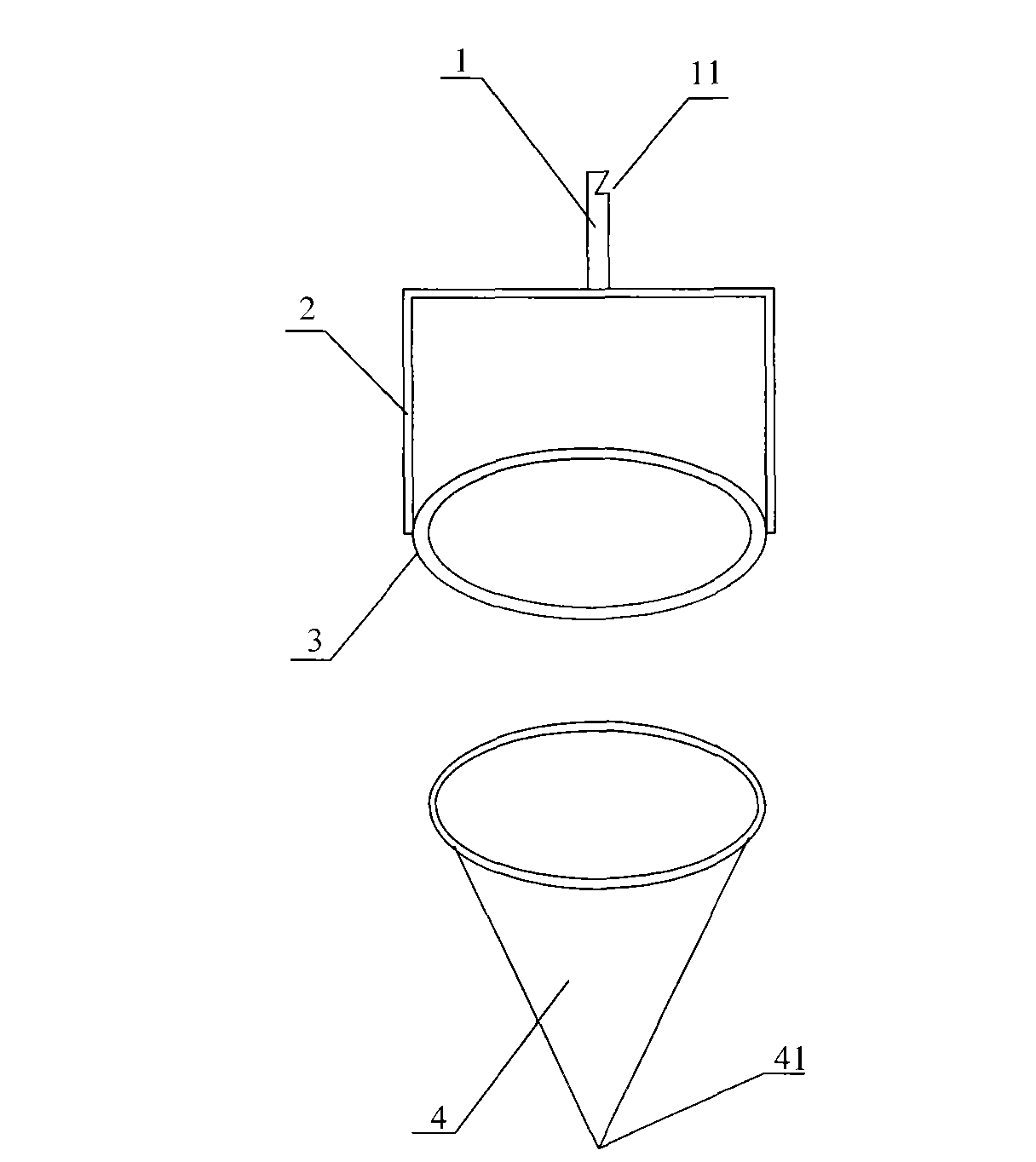

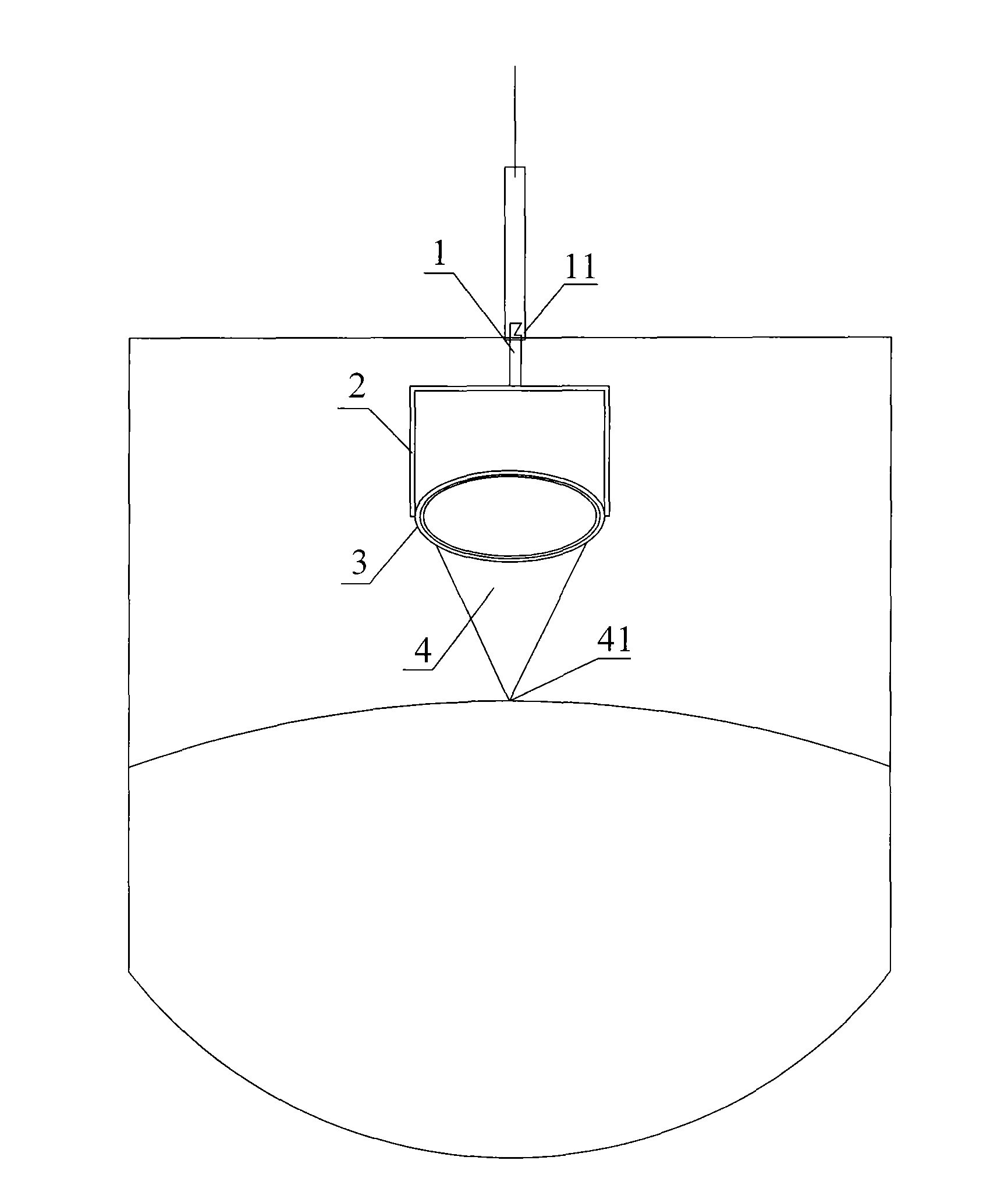

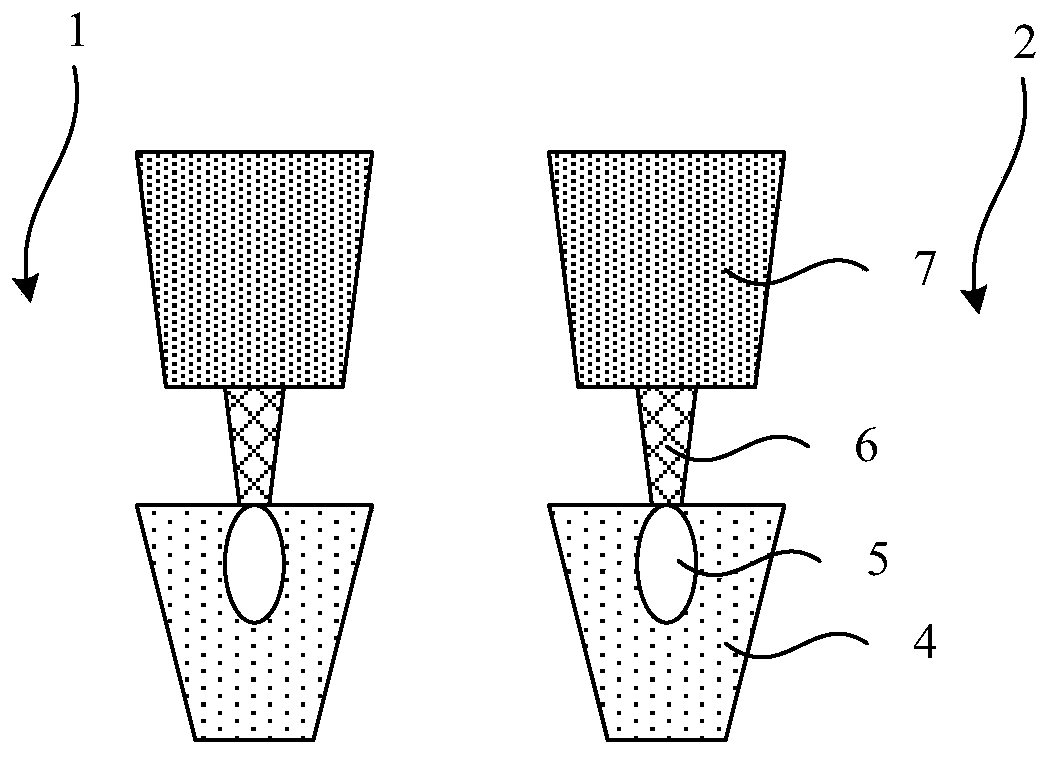

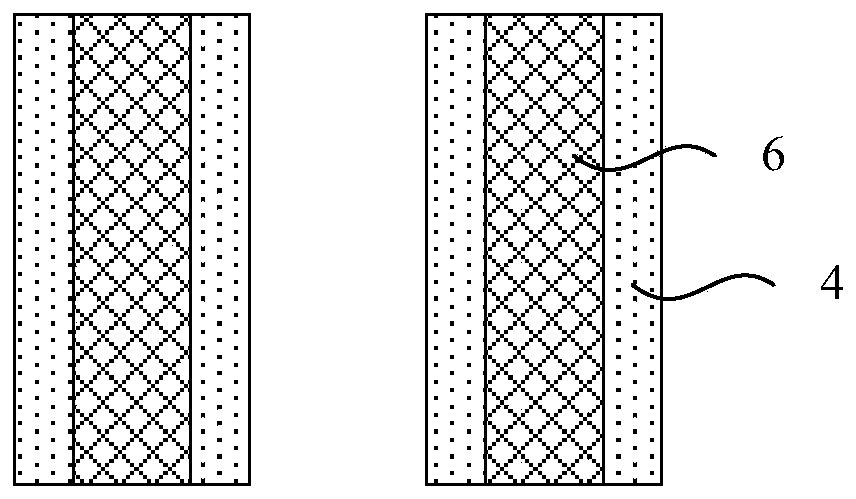

Gallium doping method of Czochralski silicon monocrystalline and doping device thereof

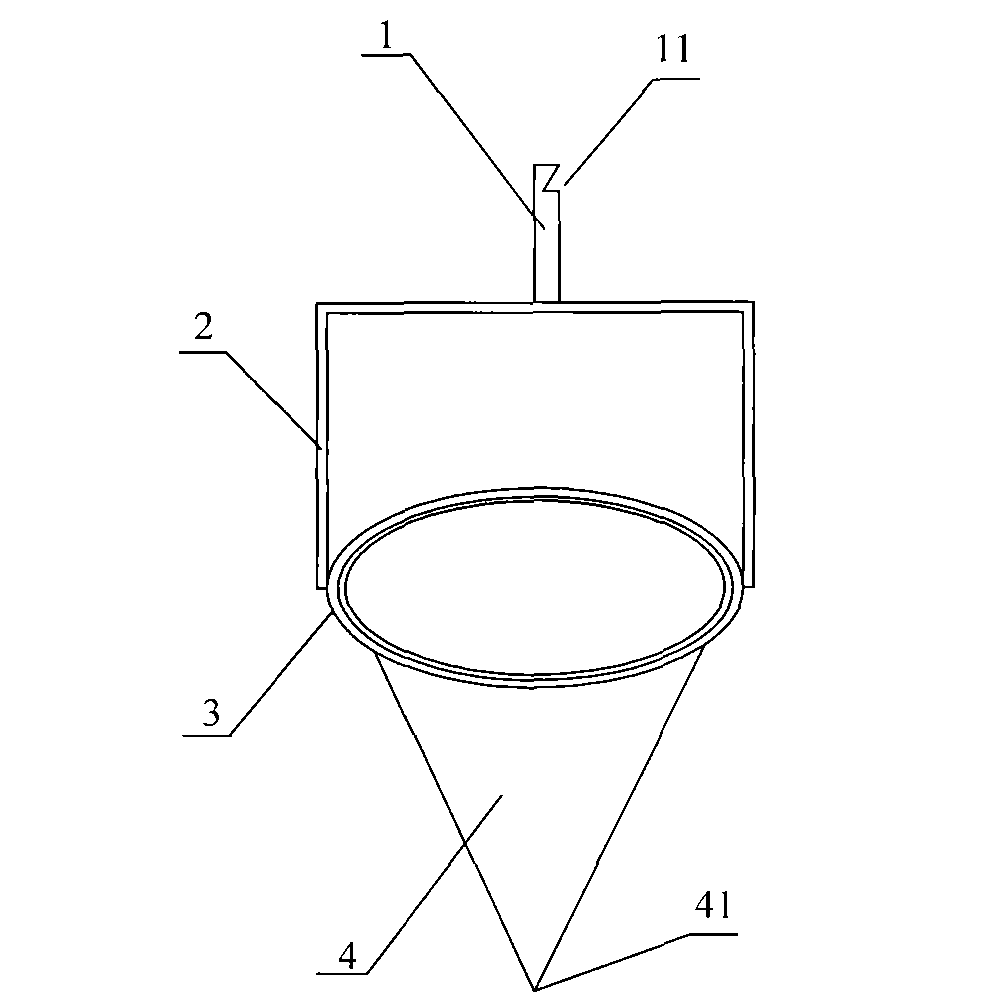

The invention discloses a gallium doping device, comprising a flying ring (2), a ring-shaped fixed sleeve (3) and a hollow cone (4), wherein the flying ring (2) is made of high-purity quartz, the hollow cone (4) is made of high-purity monocrystalline silicon, the ring-shaped fixed sleeve (3) is connected with the hollow cone (14), one end of the flying ring (2) is connected with the ring-shaped fixed sleeve (3), the other end of the flying ring (2) is connected with a handle part (1), and the handle part (1) is provided with a groove (11) which is matched with a crystal seed chuck on a crystal seed rod. The invention also discloses a doping method of gallium of Czochralski silicon monocrystalline through the gallium doping device. The invention can effectively avoid the poor influence on crystal growing caused by the splash of silicon melt.

Owner:ZHEJIANG HAINA SEMICON CO LTD

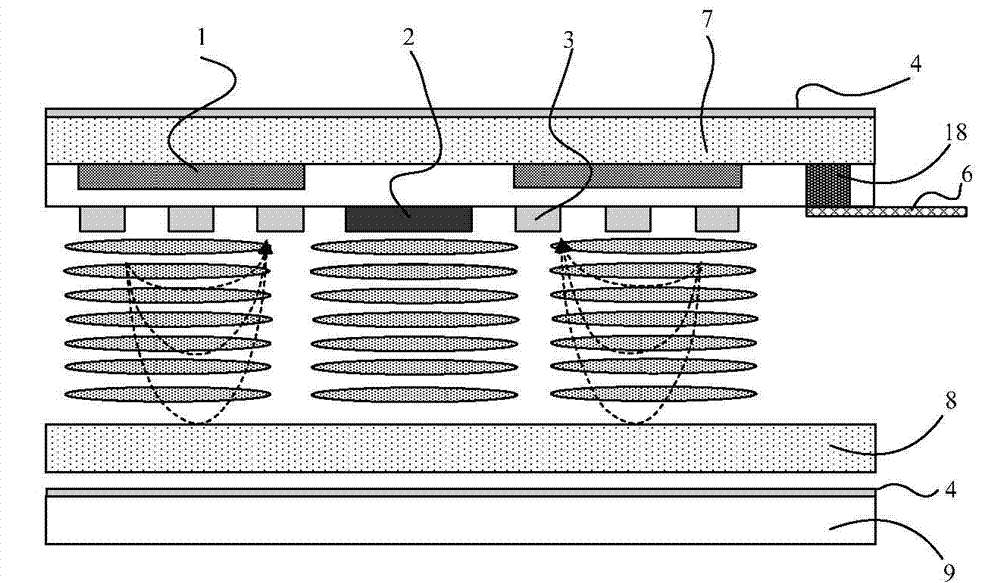

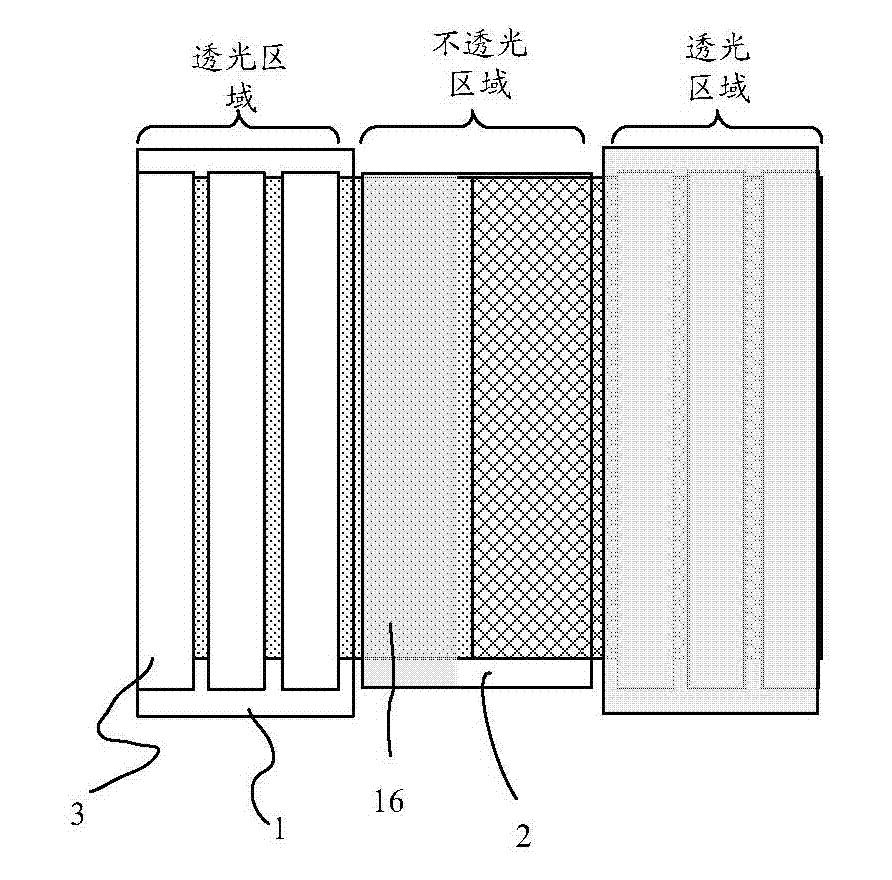

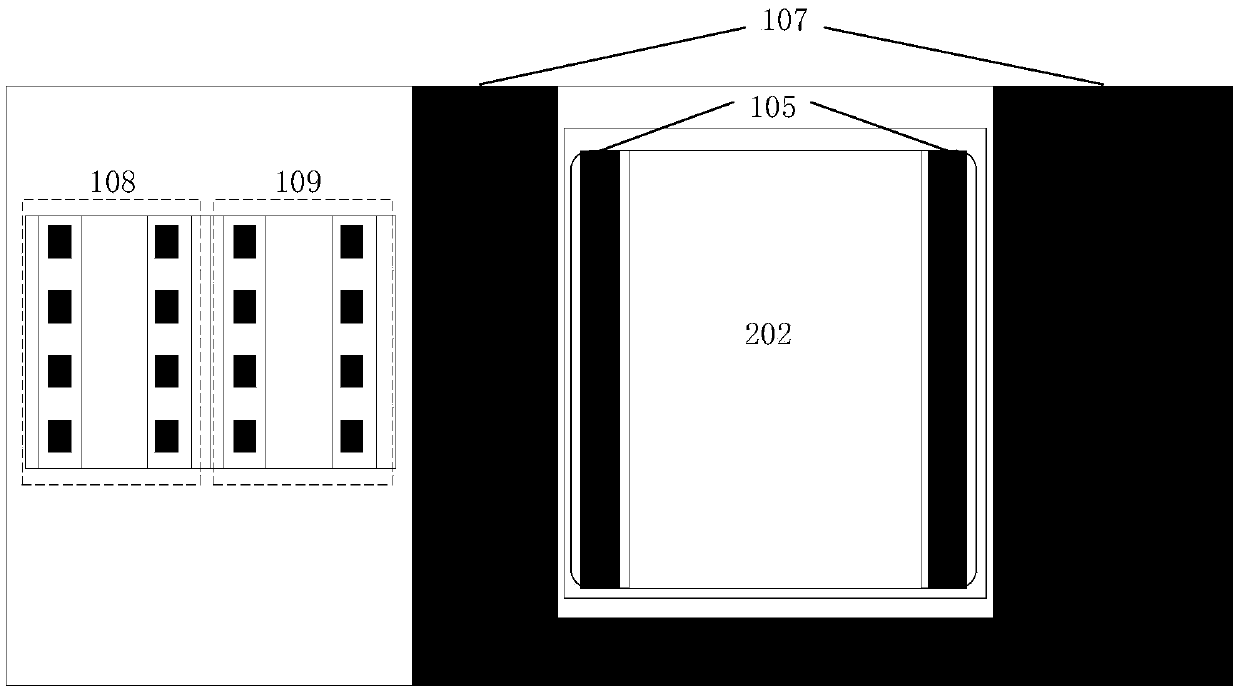

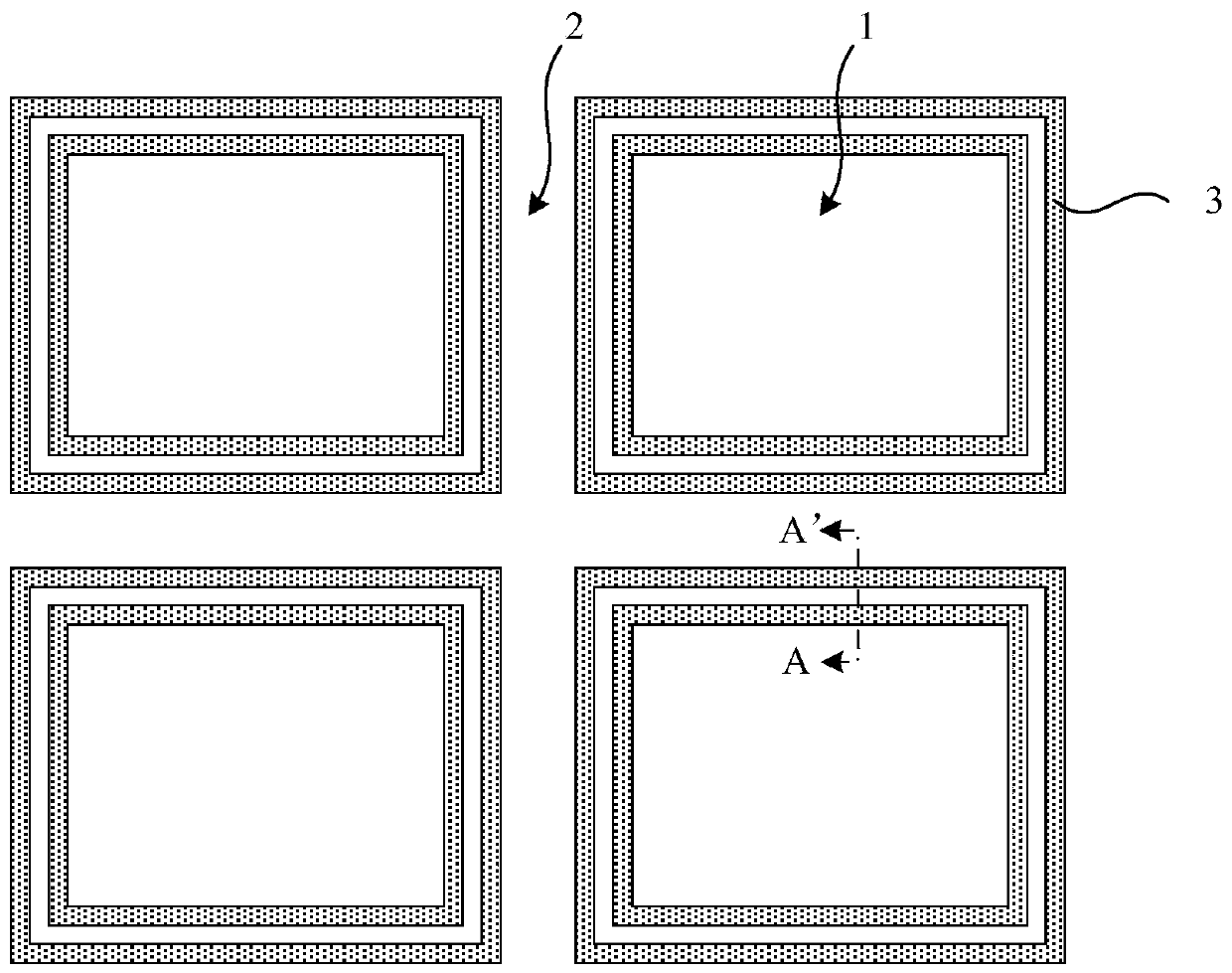

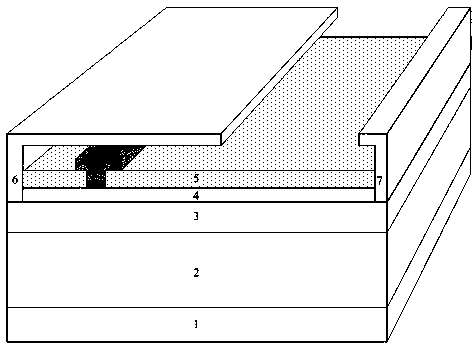

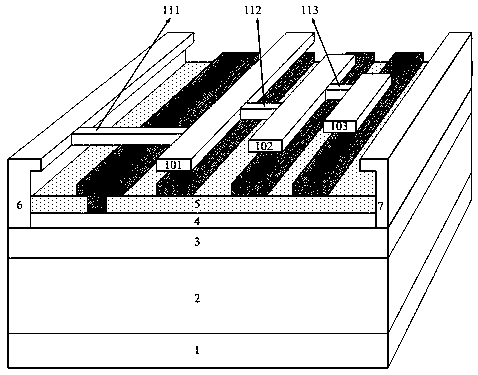

Naked eye 3D (Three Dimensional) touch device and production method thereof and display device

ActiveCN103529584ARealize the touch functionIncrease added valueNon-linear opticsInput/output processes for data processing3d patterningDisplay device

The invention discloses a naked eye 3D (Three Dimensional) touch device and a production method thereof and also discloses a display device which comprises the naked eye 3D touch device; the naked eye 3D touch device comprises a first substrate, a second substrate and a liquid crustal layer which is arranged between the first substrate and the second substrate; a surface of the first substrate, which is towards the liquid crystal layer, is sequentially provided with a public electrode, an insulating layer, slit electrode units and touch electrode units; the slit electrode units and the touch electrode units are oppositely arranged; the touch electrode units and the slit electrode units are arranged in an interval mode; every slit electrode unit comprises at least two slit electrodes; the touch electrode units comprise at least two touch electrodes; touch electrodes which are arranged in the same touch electrode unit are arranged in the same layer and insulated t each other. According to the naked eye 3D touch device, 3D display and touch are perfectly integrated and touch functions under 2D and 3D patterns are achieved under the premise that a 3D function is uniformly displayed.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

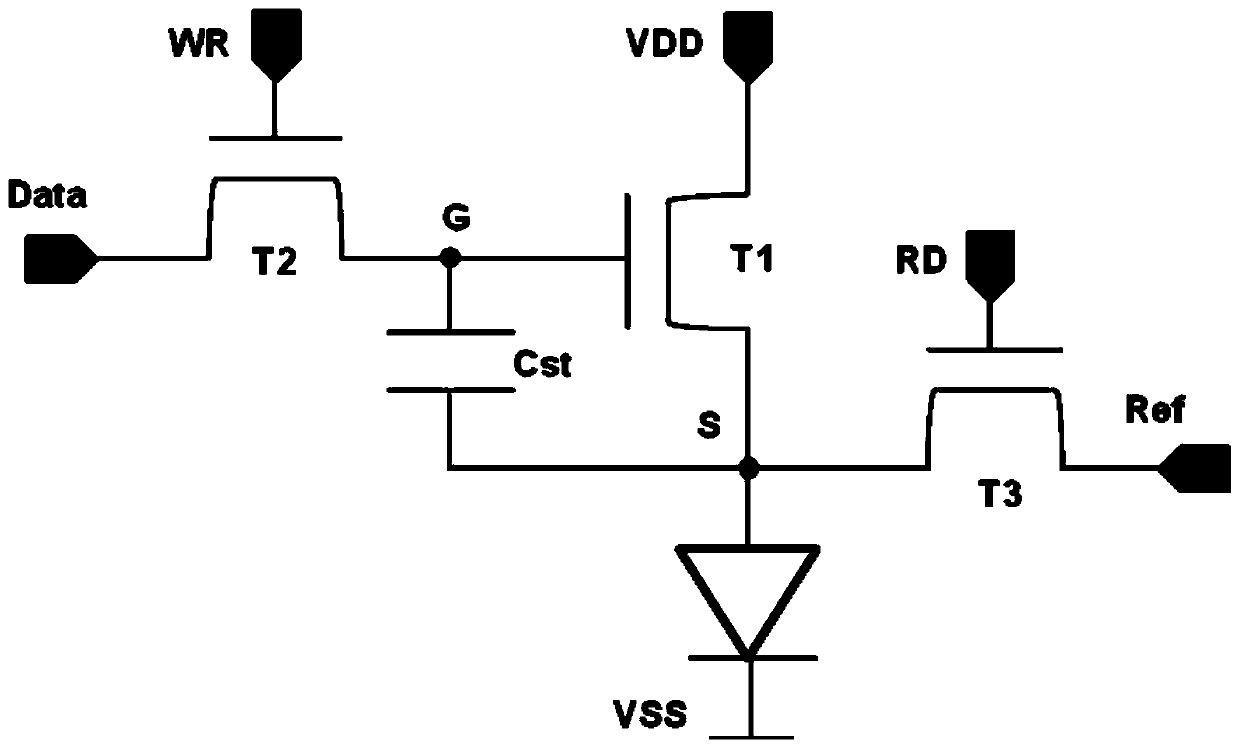

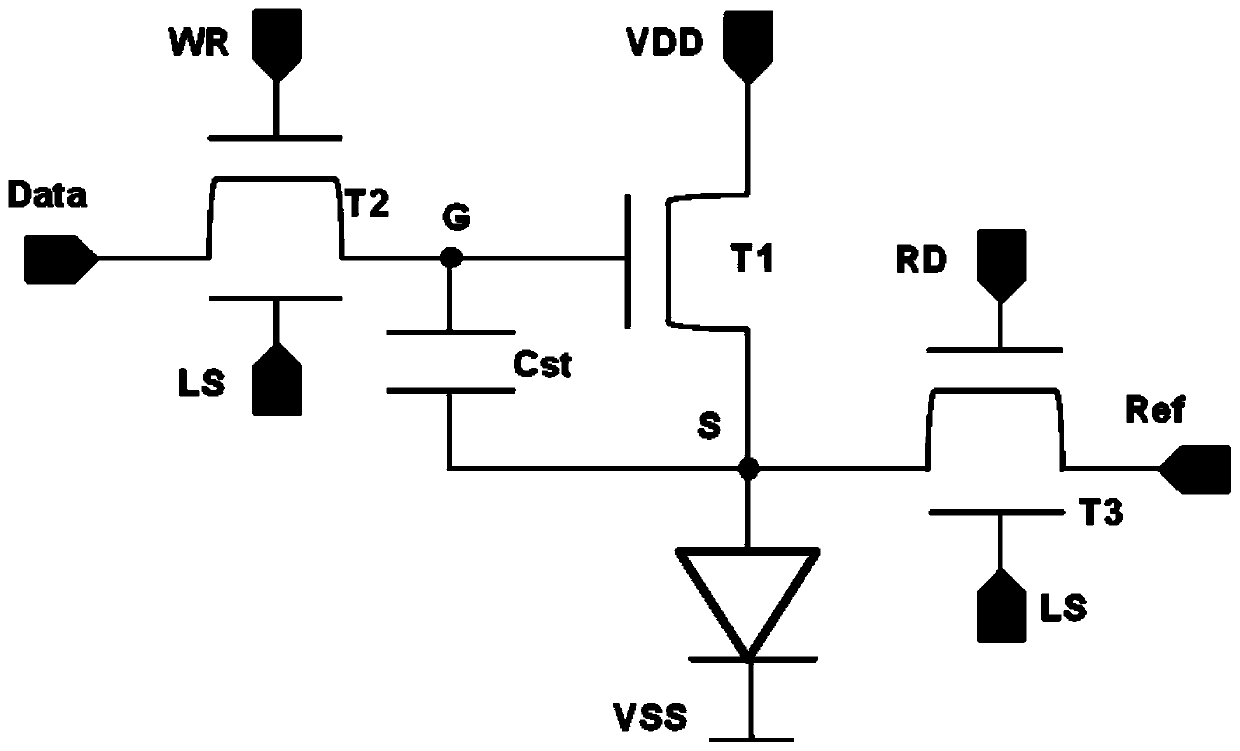

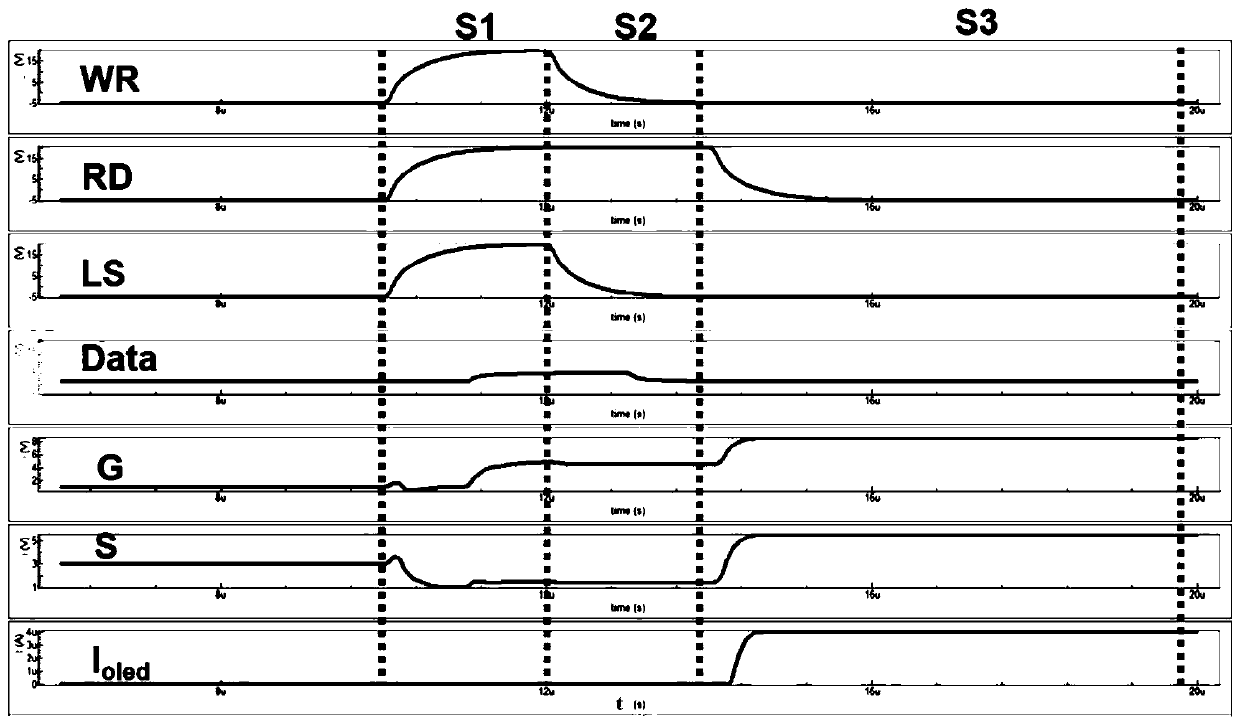

AMOLED pixel driving circuit, pixel driving method and display panel

InactiveCN111261110AImprove the display effectImprove qualityStatic indicating devicesHemt circuitsCapacitor

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

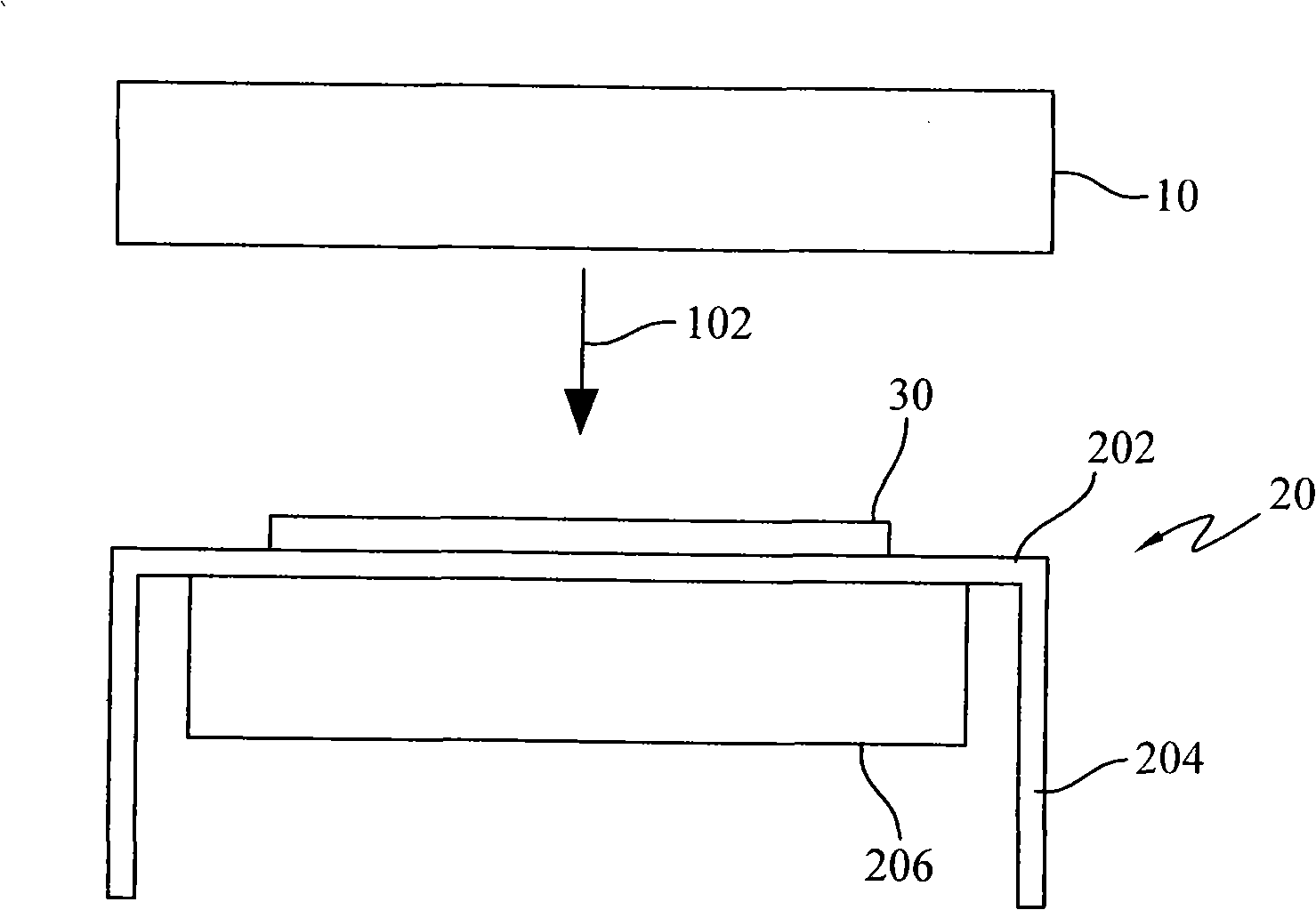

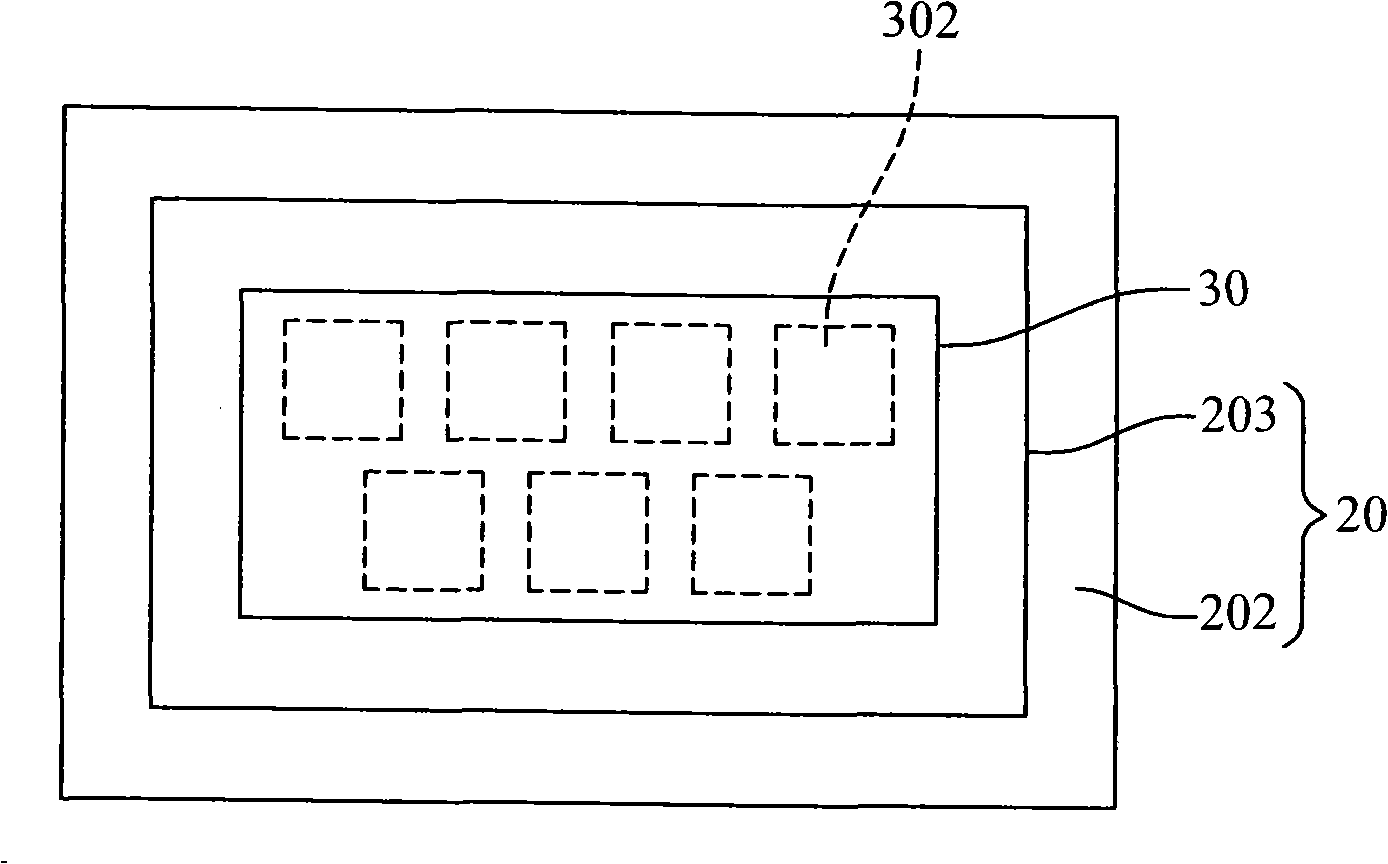

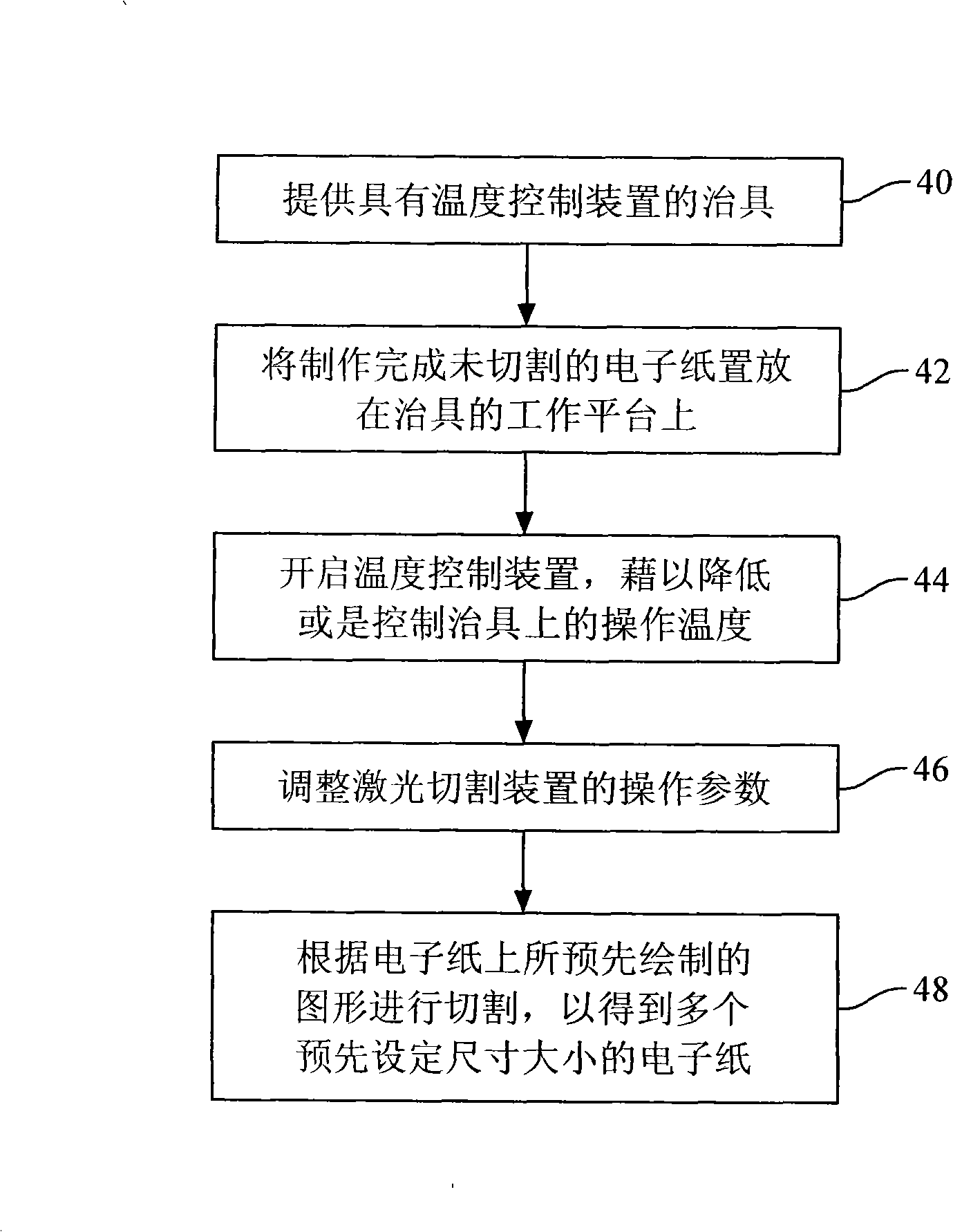

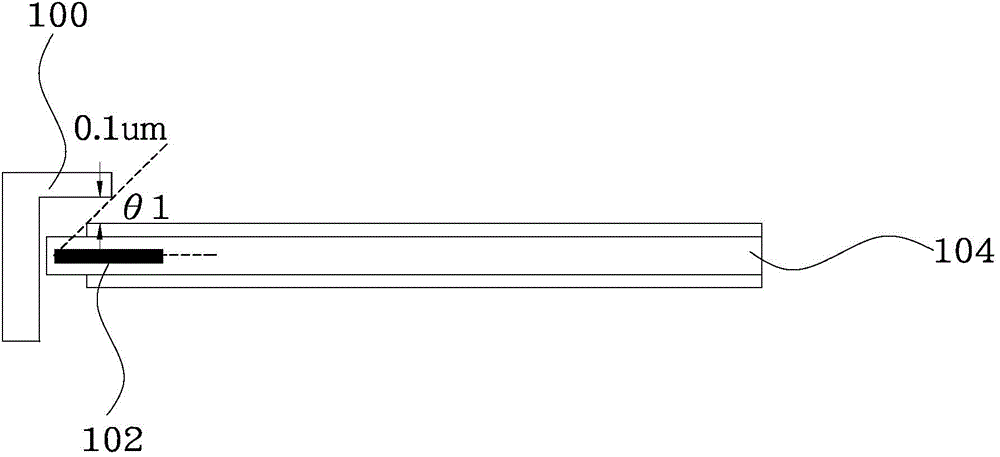

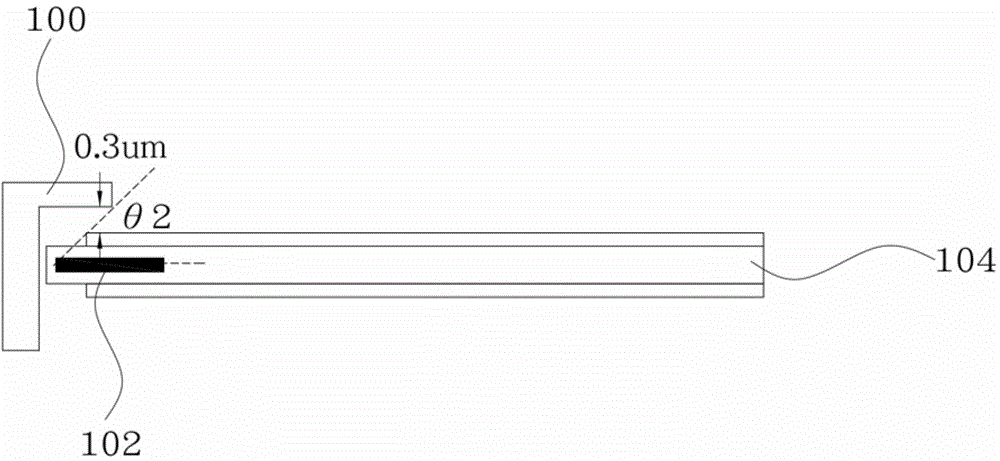

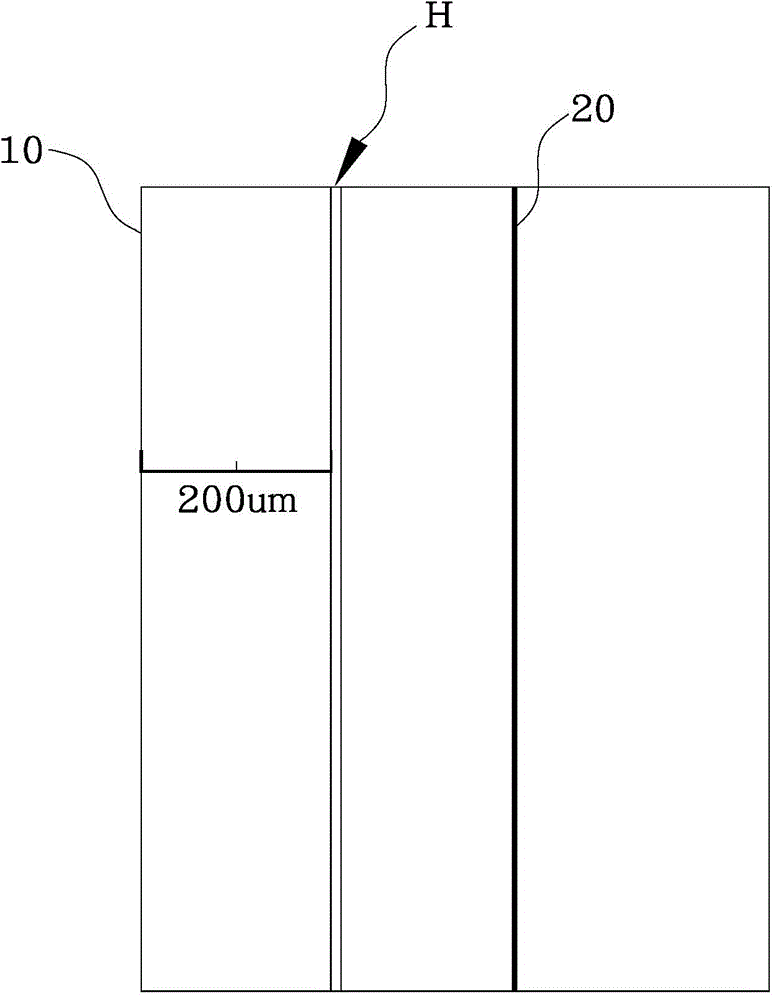

Electronic paper laser cutting process

InactiveCN101284332AImprove the excellent rateAvoid destructionLaser beam welding apparatusTemperature controlLaser cutting

The invention provides a method for cutting electronic paper by using laser and aims to cut the electronic paper with high qualification rate and quality by utilizing laser cutting in coordination with a jig with a temperature controlling device. The method comprises the steps of providing a jig with a temperature controlling device; putting finished but uncut electronic paper on the platform of the jig, wherein the electronic paper has pre-designed cutting patterns; starting the temperature controlling device inside the jig to control or reduce the heat generated during operation; adjusting operating parameters of a laser cutting device; and cutting the patterns to be cut on the electronic paper to get electronic paper with pre-designed size.

Owner:陈锡富

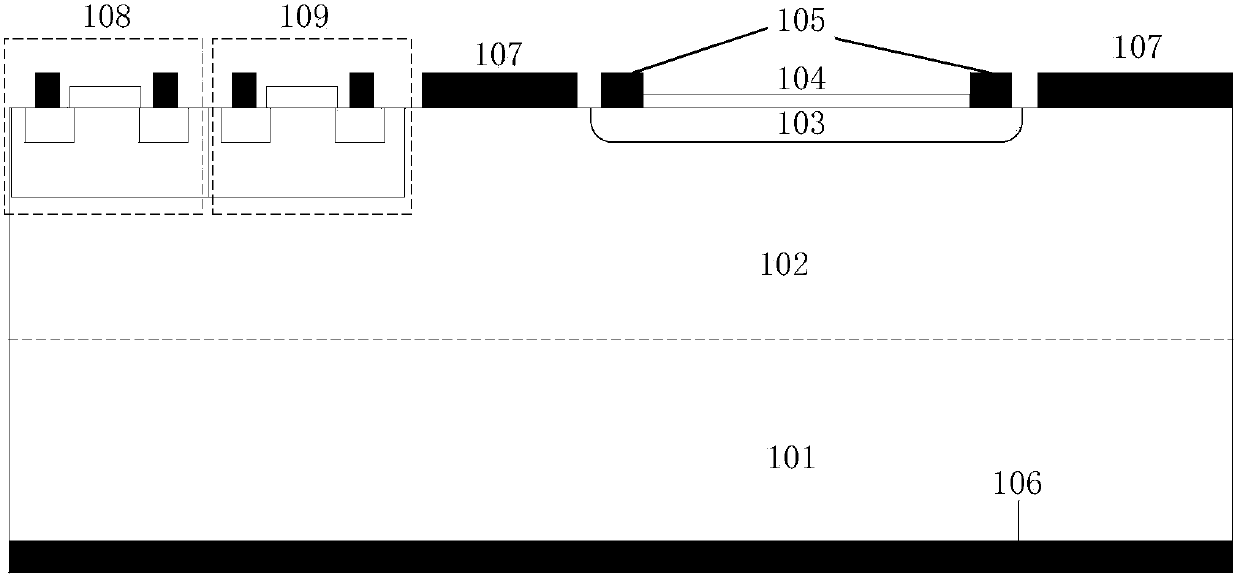

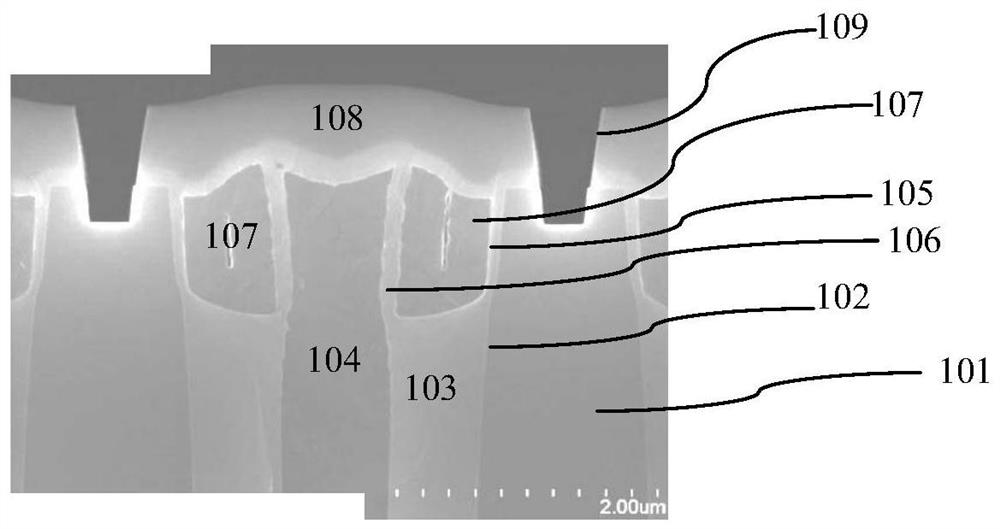

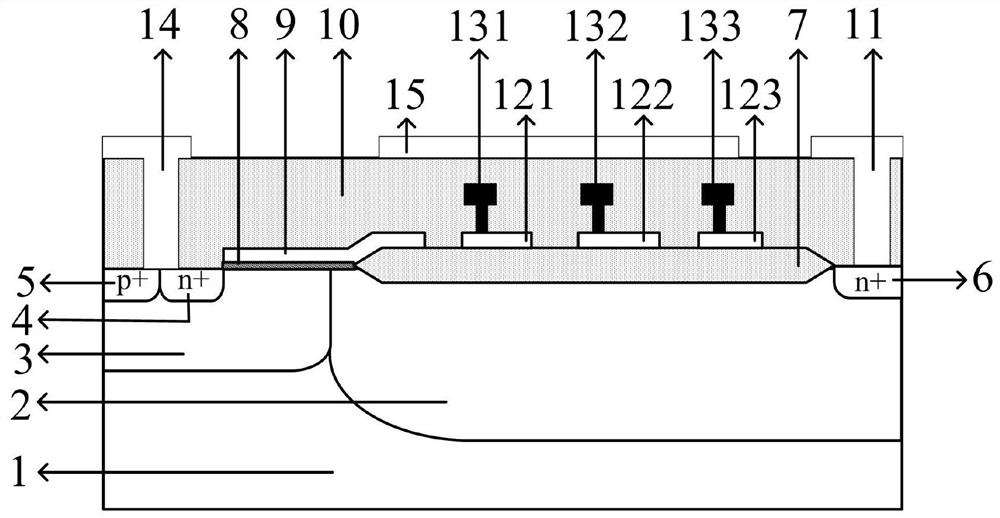

Rapid photo detector

InactiveCN103594468AEliminate generation conditionsQuick responseSolid-state devicesSemiconductor devicesPhotovoltaic detectorsElectronic component

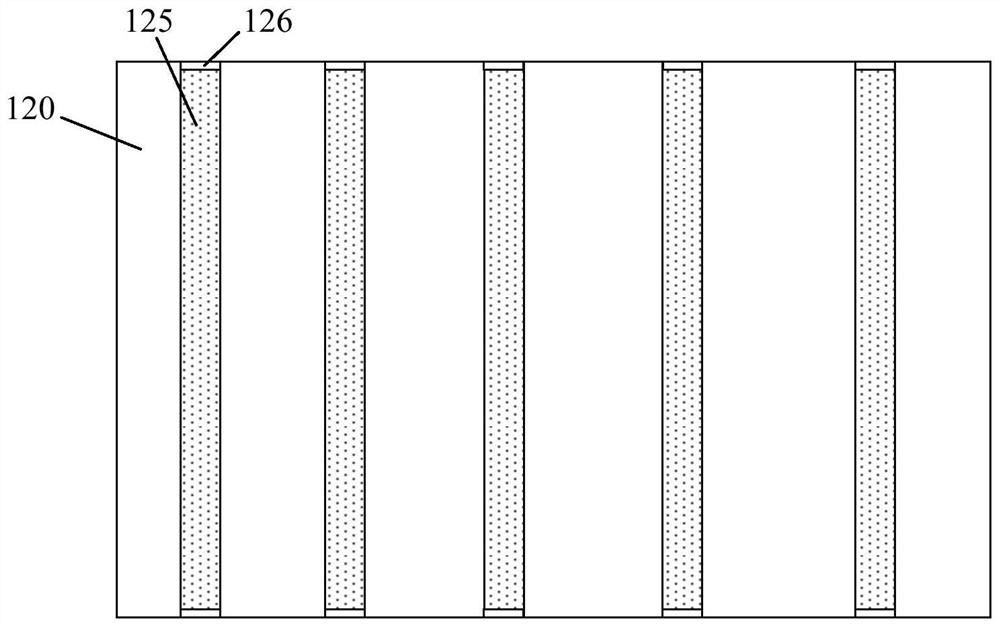

The invention relates to a rapid photo detector, belonging to the electronic component technology. The rapid photo detector comprises a photodiode and an amplification circuit connected with the photodiode, wherein the photodiode comprises an N+ substrate 101, an N- epitaxial layer 102, anode metal electrodes 105 and a cathode metal electrode 106, the N- epitaxial layer 102 is arranged at the upper end surface of the N+ substrate 101, a P+ injection area 103 is arranged in the N- epitaxial layer 102, and an anti-reflection coating 104 and the anode metal electrodes 105 are arranged at the upper end surface of the P+ injection area; and the amplification circuit is composed of multiple NMOS tubes 108 and PMOS tubes 109. The rapid photo detector is characterized in that a light shield layer is arranged between the photodiode and the amplification circuit, and the light shield layer is used for shielding light for non photosensitive areas. The rapid photo detector has the advantages that the generation condition for slow photo-generated carriers is fundamentally eliminated, and the response speed of the photo detector is greatly increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

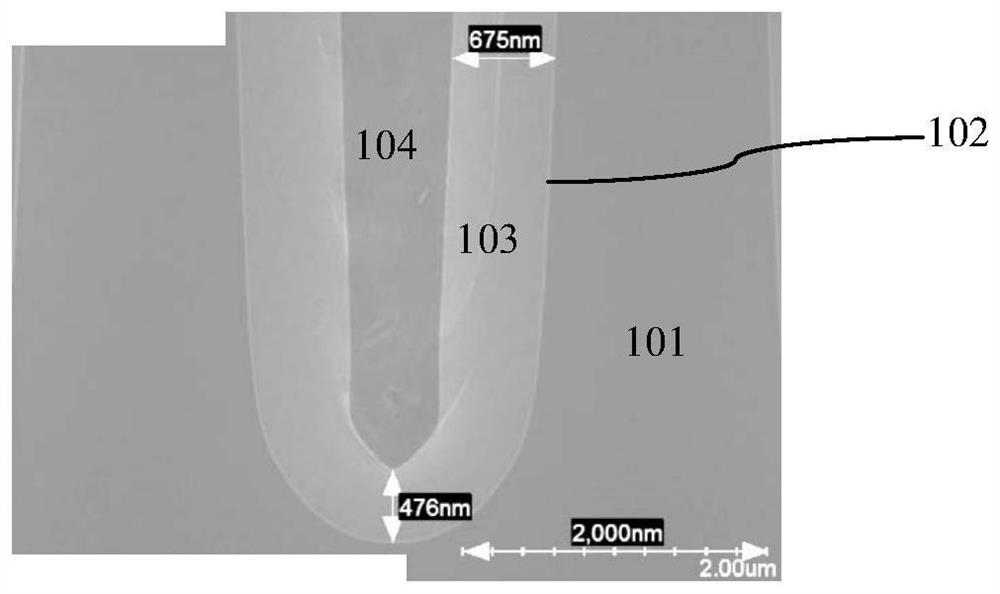

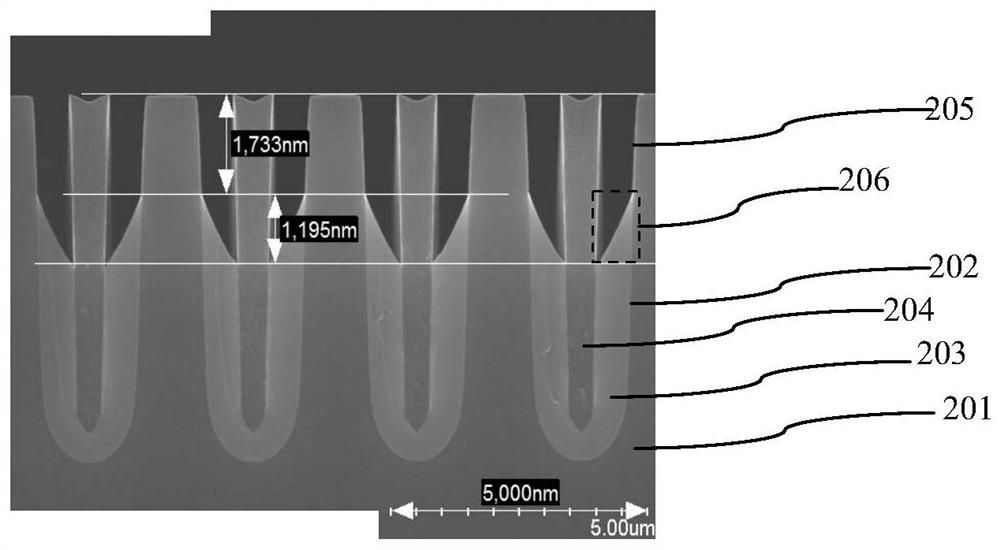

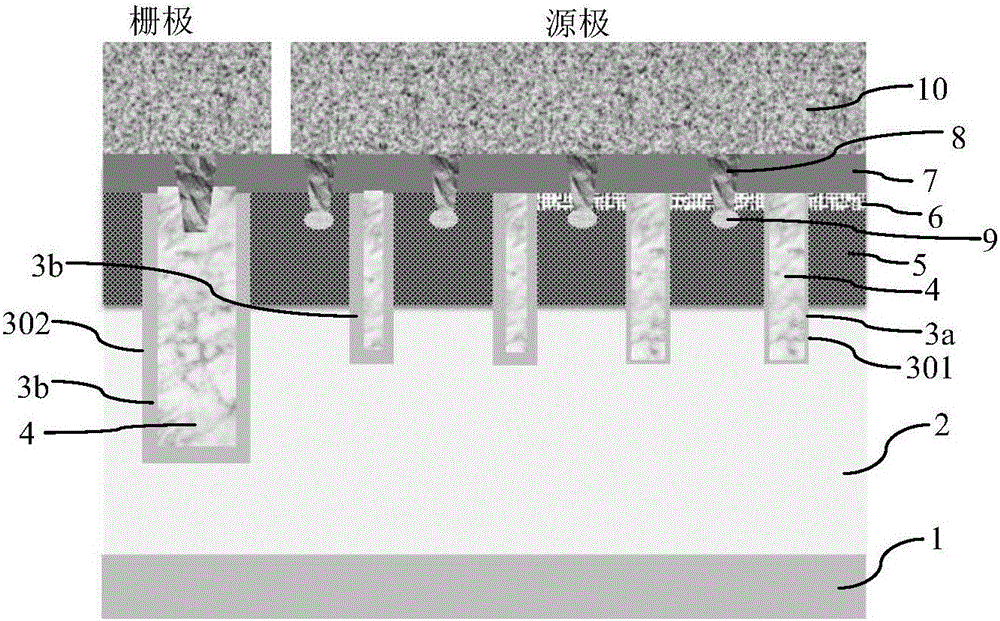

Shield gate trench power device and manufacturing method thereof

ActiveCN111883592ALower on-resistanceIncreasing the thicknessEfficient power electronics conversionSemiconductor/solid-state device manufacturingGate dielectricEngineering

The invention discloses a shield gate trench power device. A gate structure of a device unit region comprises a shielding dielectric layer formed on the inner side surface of a gate trench; the shielding dielectric layer is formed by superposing a thermal oxidation layer and a CVD dielectric layer; active polycrystalline silicon is filled in a gap region formed by filling the shielding dielectriclayer; top trenches formed by etching part of the shielding dielectric layer close to the side surface of the gate trench are formed in two sides of the source polysilicon, and the top trenches are completely located in the thermal oxide layer; the shielding dielectric layer between the second side surface of the top trench and the source polysilicon is used as an inter-polysilicon dielectric layer; the top trench is filled with a polysilicon gate, and a gate dielectric layer is formed on the first side surface of the top trench. The invention further discloses a manufacturing method of the shield gate trench power device. According to the invention, the thickness uniformity of the side wall and the bottom shielding dielectric layer of the trench can be improved, so the voltage resistanceof the device can be ensured, the on resistance of the device can be reduced, and the gate-source capacitance of the device can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

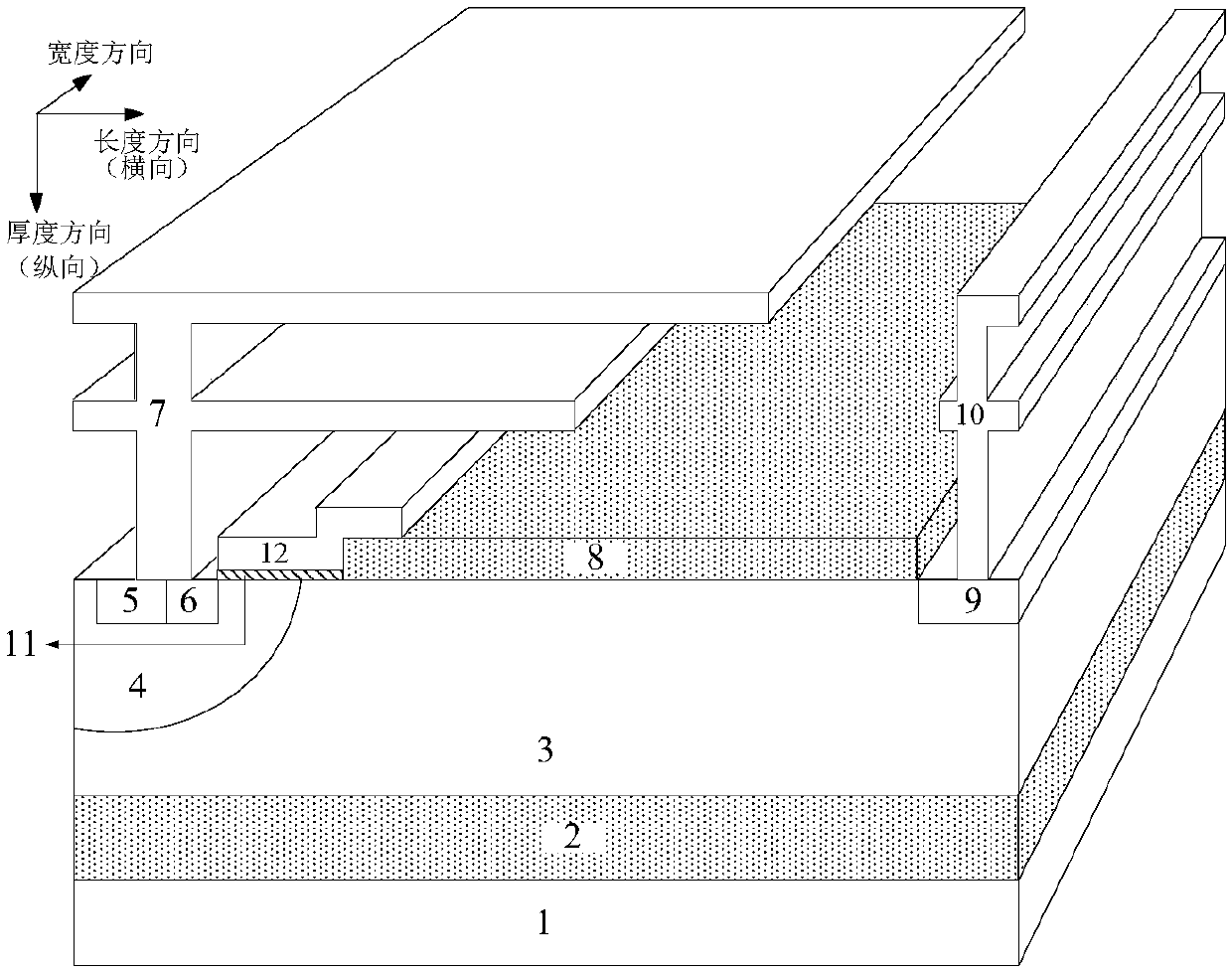

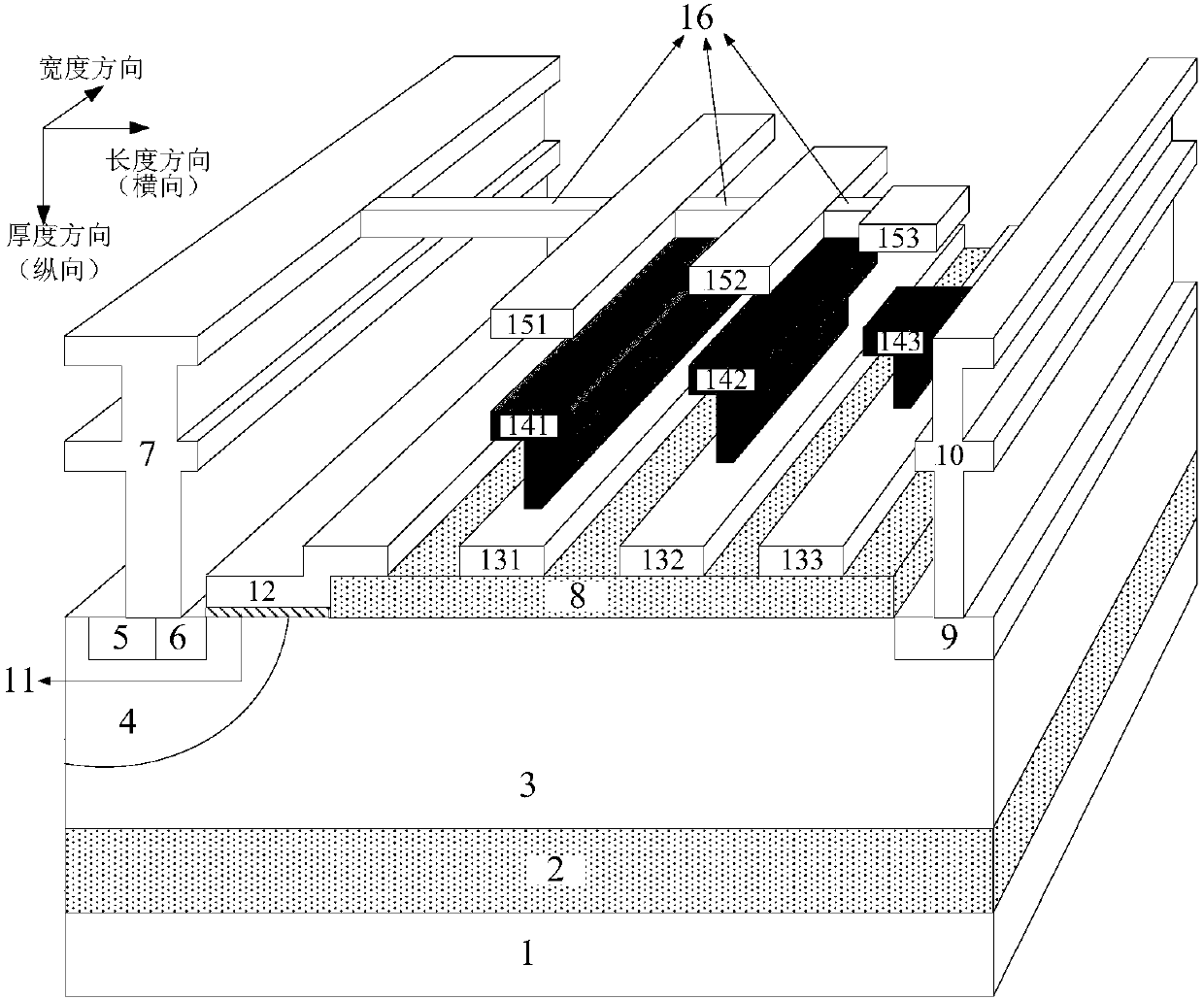

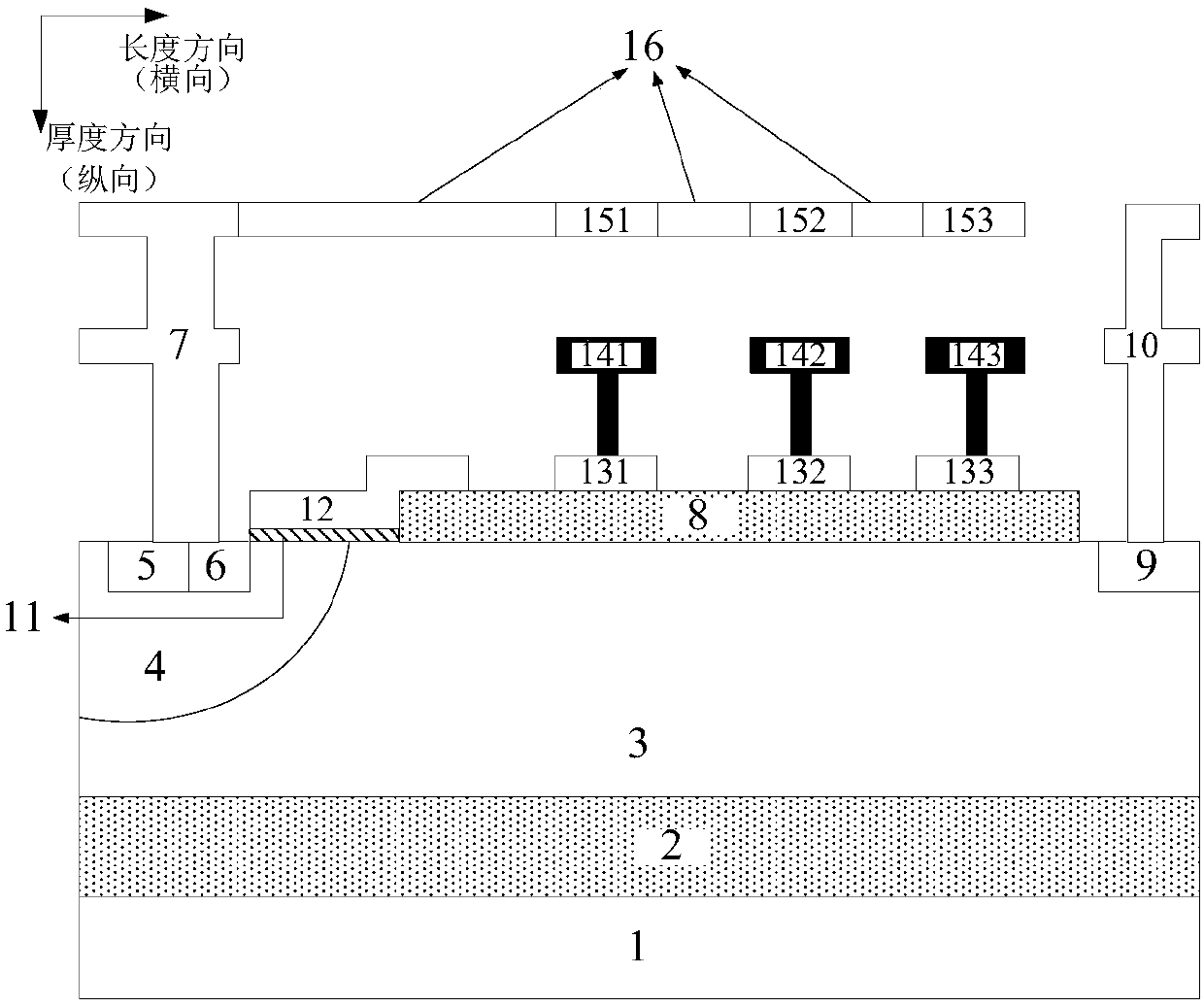

Lateral double-diffused metal oxide semiconductor field effect transistor with adjustable field plates

ActiveCN107680997AImprove lateral pressure resistanceUniform distribution of transverse electric fieldSemiconductor devicesCapacitanceField-effect transistor

The invention provides a lateral double-diffused metal oxide semiconductor field effect transistor with adjustable field plates. The lateral double-diffused metal oxide semiconductor field effect transistor comprises a field oxide layer and a drift region located at the lower part of the field oxide layer, wherein the surface of the field oxide layer is provided with a plurality of adjustable field plates; two adjacent adjustable field plates are spaced at a set distance; and each adjustable field plate is connected with a regulating capacitor. Inductive charge quantity and inductive potentialon each adjustable field plate can be adjusted through adjusting the sizes of the adjustable field plates and positive and negative electrodes of the regulating capacitor, so that uniform surface transverse electric field distribution is obtained in the drift region. According to the lateral double-diffused metal oxide semiconductor field effect transistor, the surface transverse electric field distribution of the drift region can be improved and the lateral double-diffused metal oxide semiconductor field effect transistor has very high lateral voltage endurance capability and very low on-resistance.

Owner:UNIV OF JINAN

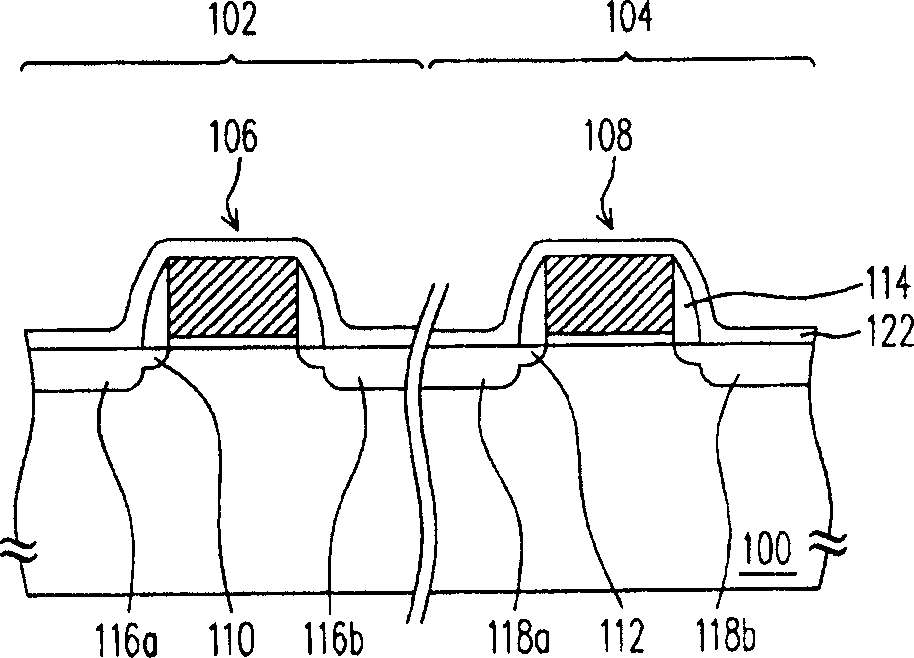

Semiconductor device

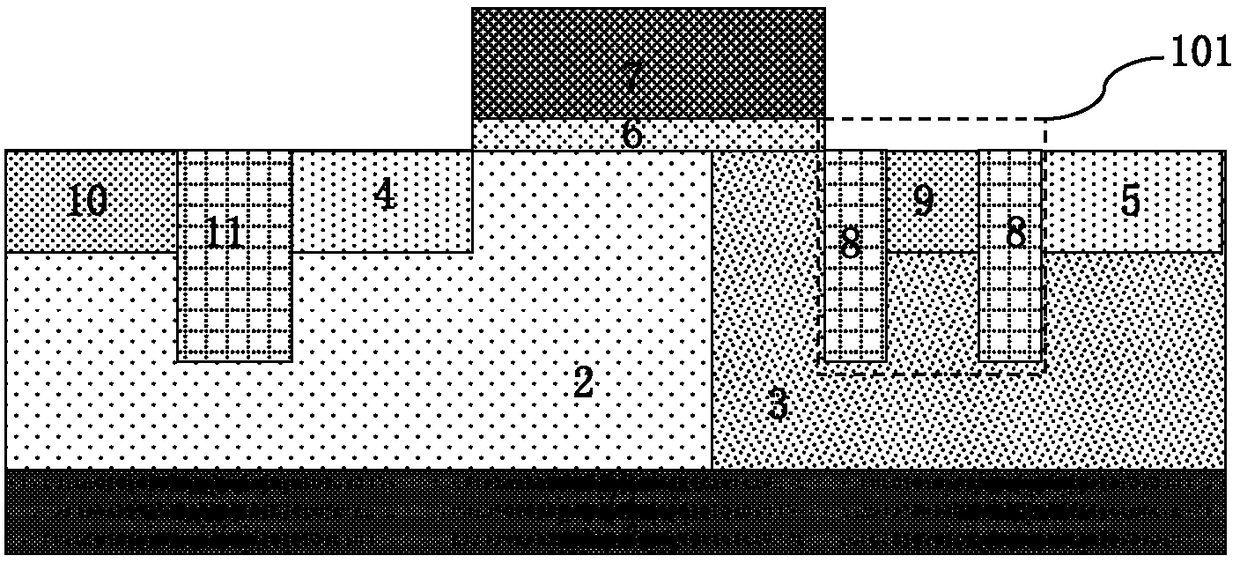

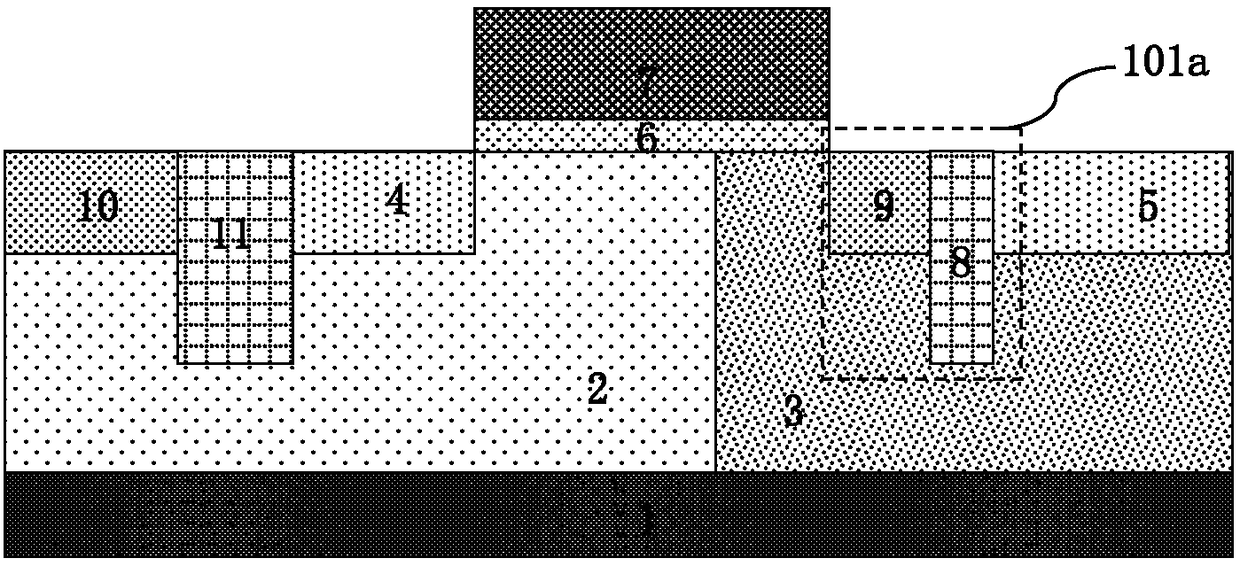

InactiveCN108630745AIncrease exhaustReduce electric field strengthSemiconductor devicesGate dielectricDevice material

The invention discloses a semiconductor device. The semiconductor device comprises a channel region, a drift region, a gate structure formed by overlapping a gate dielectric layer and a polysilicon gate, a source region and a drain region, wherein the drain region and a second side of the gate structure are separated by a distance; a drain terminal combination structure formed by more than one first doped region opposite to drain region doping and more than one first shallow trench field oxide is formed between the drain region and a second side of the gate structure; the top of the drain region is connected to a drain electrode formed by a front metal layer through a contact hole, and the first doped region is floated; when the semiconductor device works, through the drain terminal combination structure, the depletion of the drift region is increased and the electric field intensity of the drift region is reduced, and the reliability of the device is improved. According to the device,the reliability of the device can be improved, the characteristics of the native device cannot be influenced, the process cost is not increased, and a selection is provided for high-voltage application.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

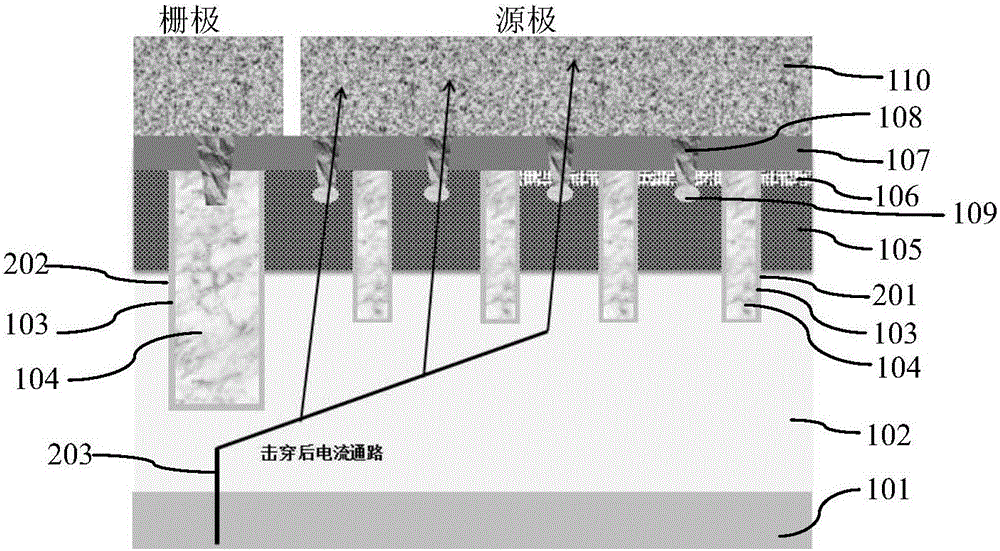

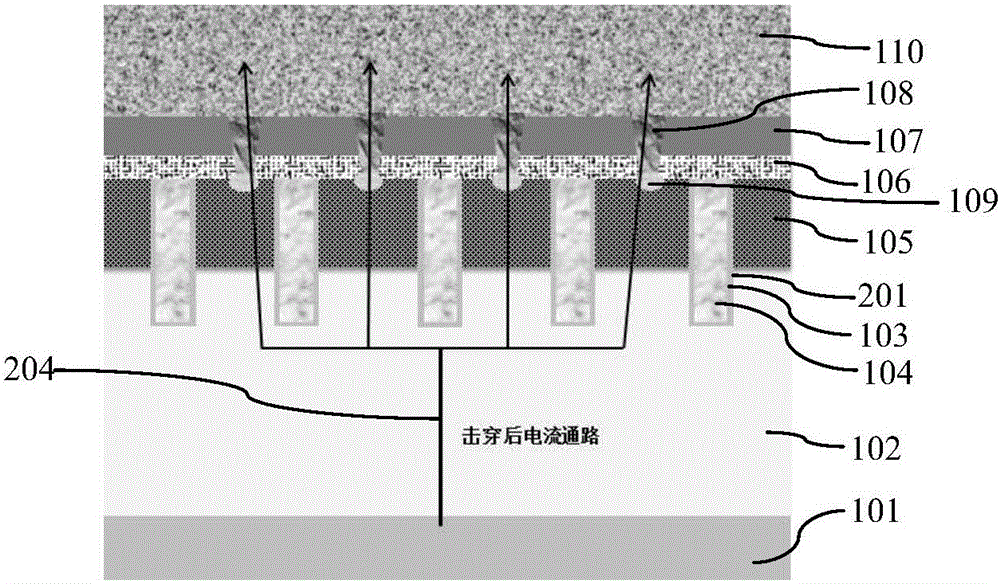

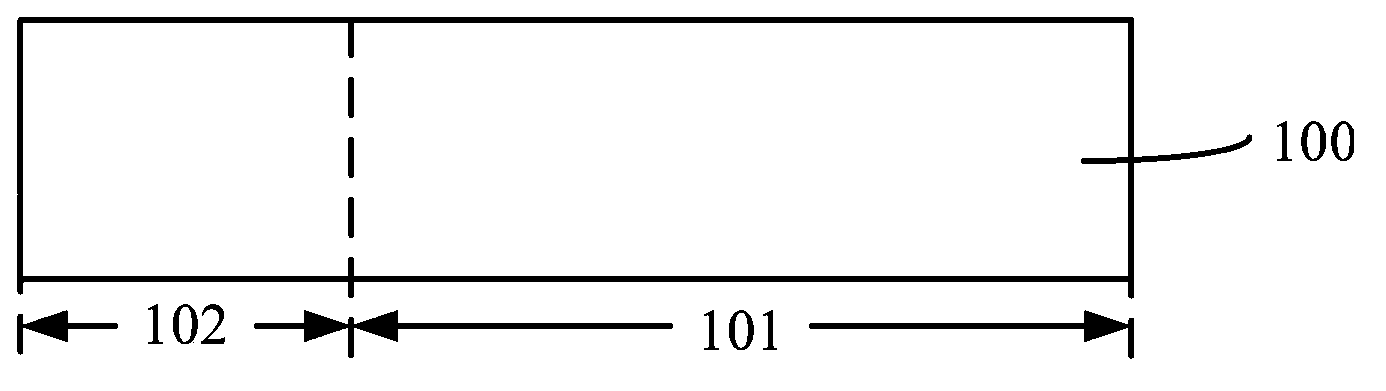

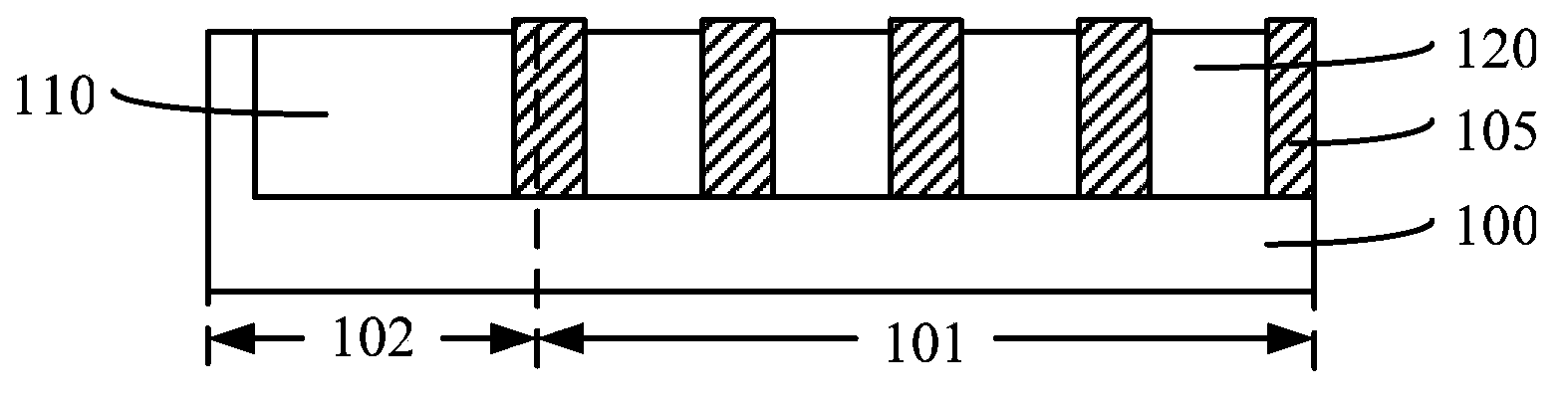

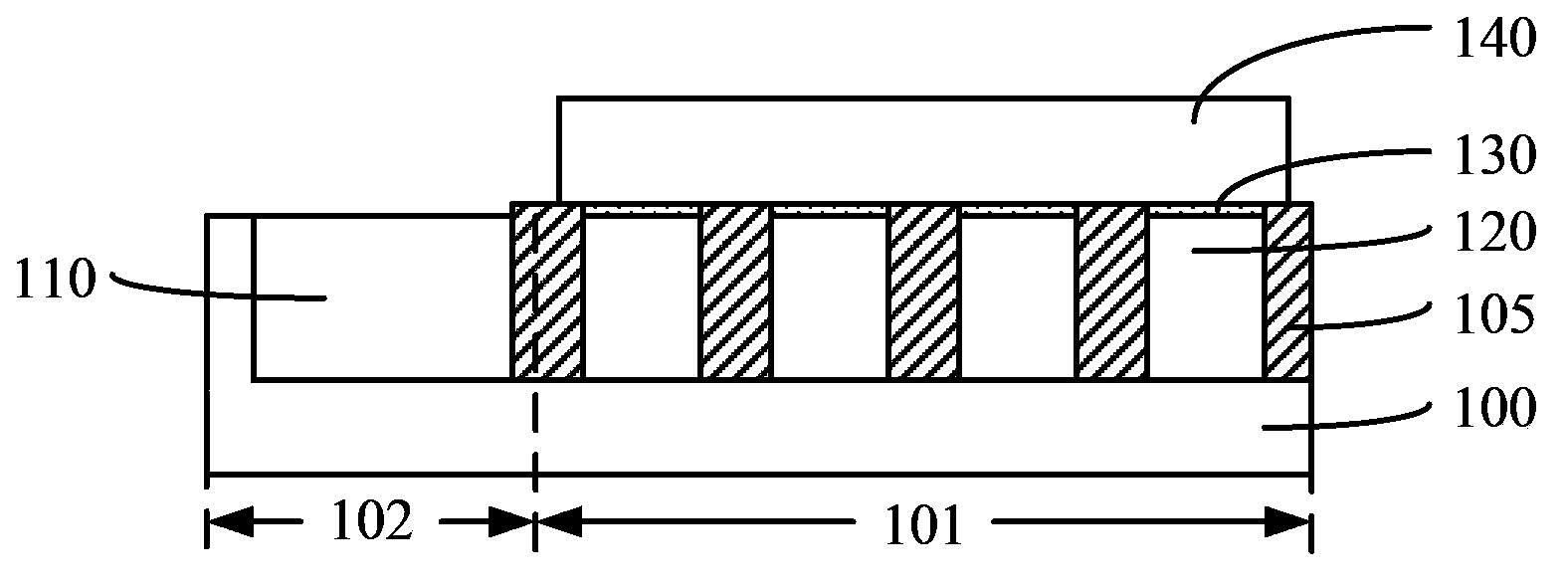

Trench-gate power MOSFET and manufacturing method

ActiveCN105932064AReduce electric field strengthImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricLithography process

The invention discloses a trench-gate power MOSFET. The thicknesses of first gate dielectric layers in trenches in an internal region and second gate dielectric layers in the trenches in an edge region are independently set; and the thicknesses of the second gate dielectric layers are greater than those of the first gate dielectric layers. A threshold voltage of a device is adjusted through the thicknesses of the first gate dielectric layers; the electric field strength in the edge region is reduced and the voltage-withstand capability of the edge region is improved by increasing the thicknesses of the second gate dielectric layers; breakdown of the device is demanded in the internal region; and the impact resistance of the device is improved. The invention further discloses a manufacturing method of the trench-gate power MOSFET. The breakdown voltage of the device can be improved; and the anti-UIS impact ability of the device is improved. Independent adjustment of the thicknesses of the first gate dielectric layers and the second gate dielectric layers is achieved by source injection lithography; and an extra lithography process is not needed, so that the process cost is not increased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

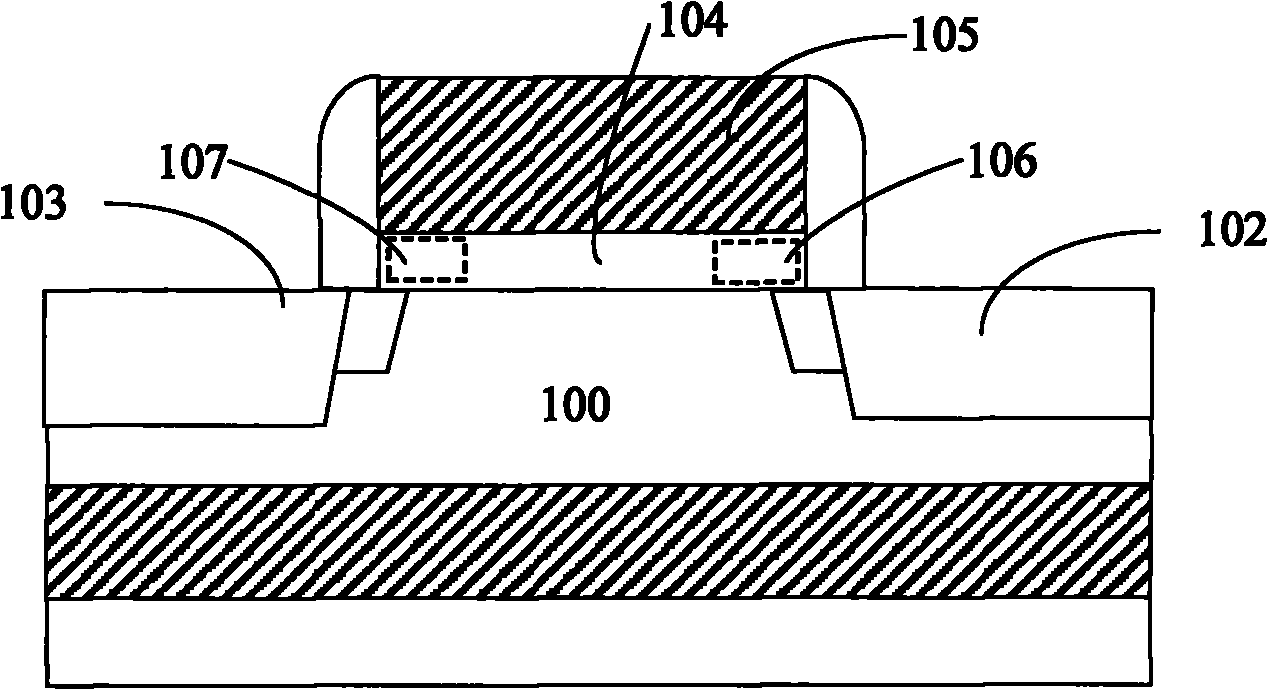

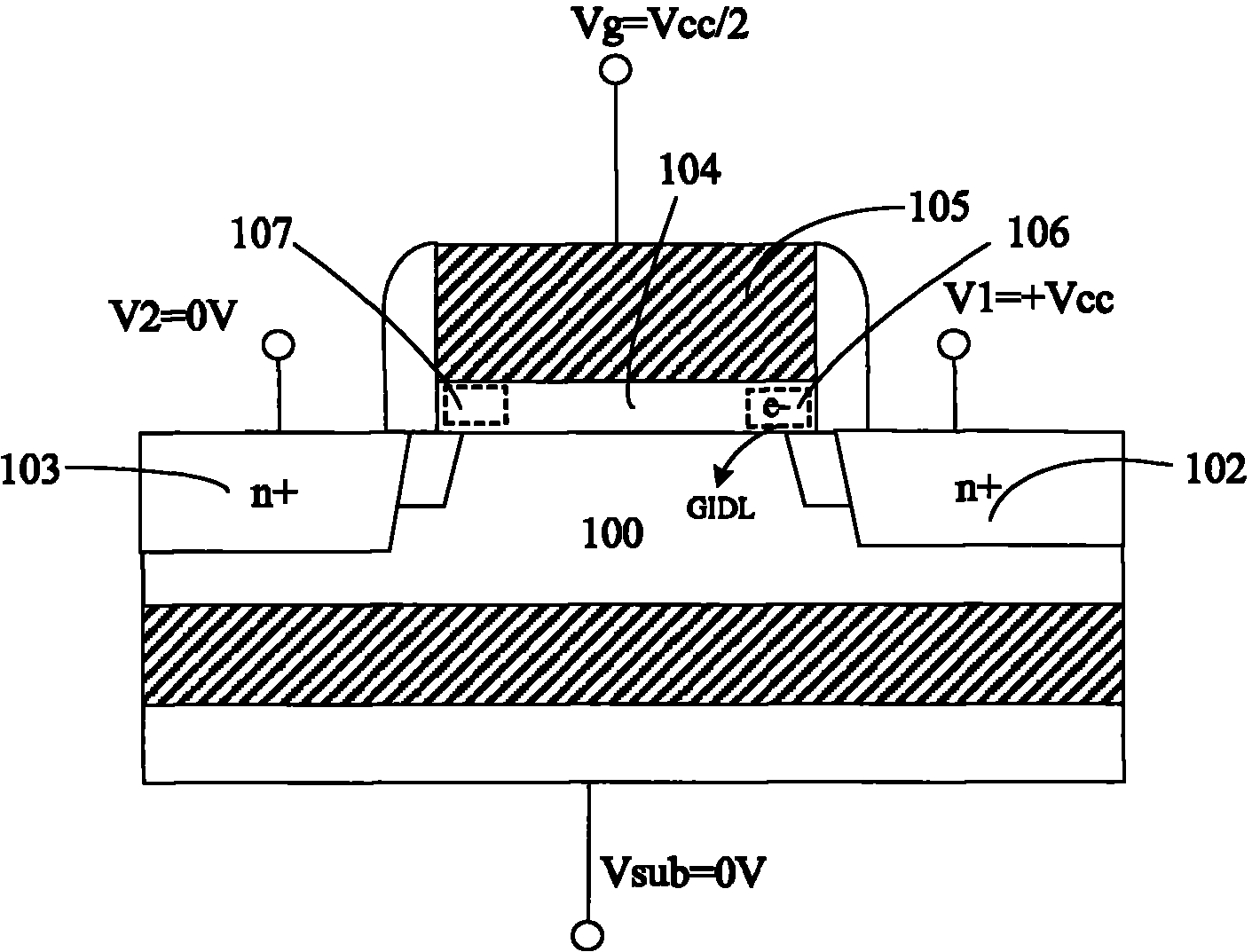

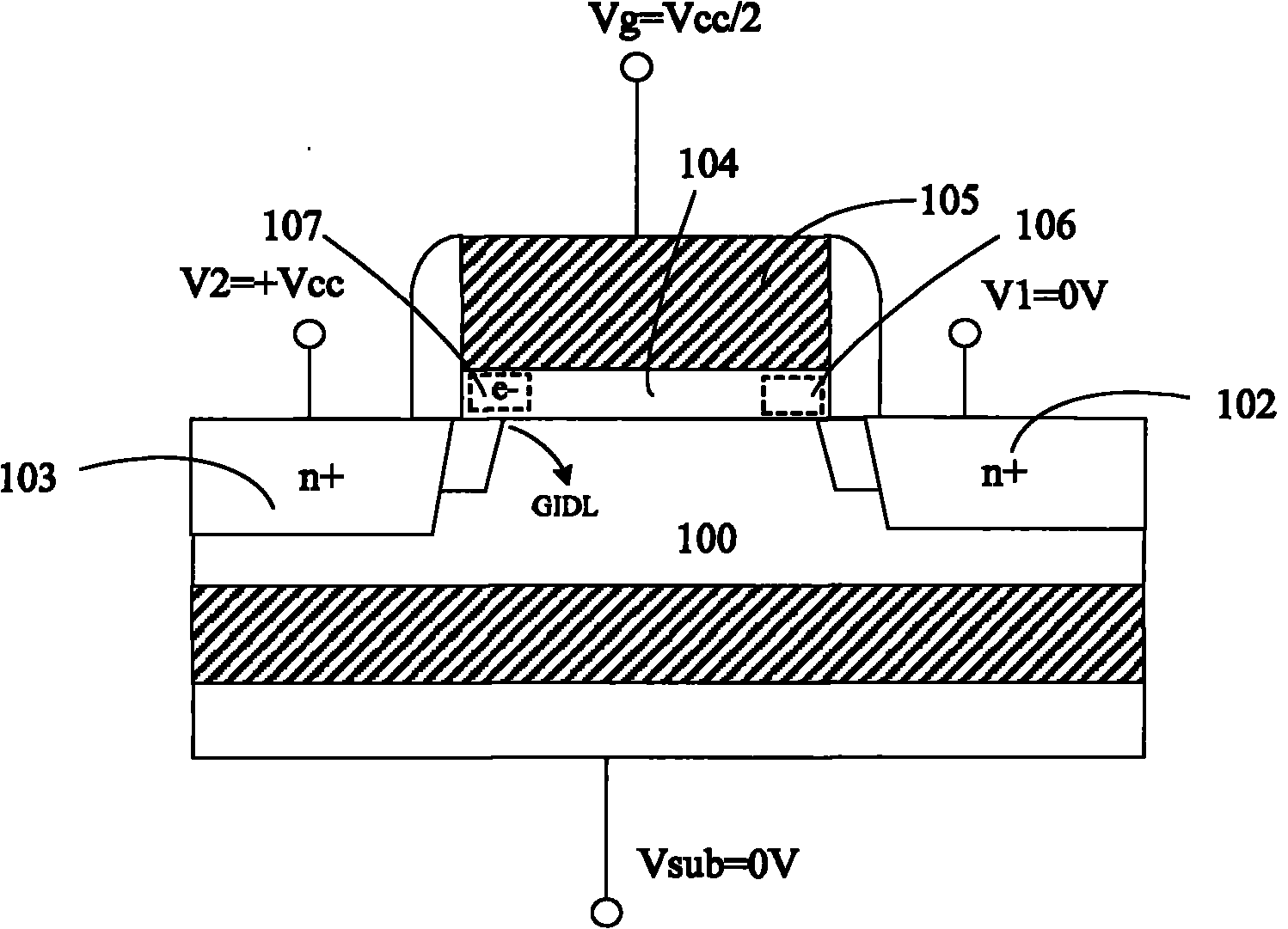

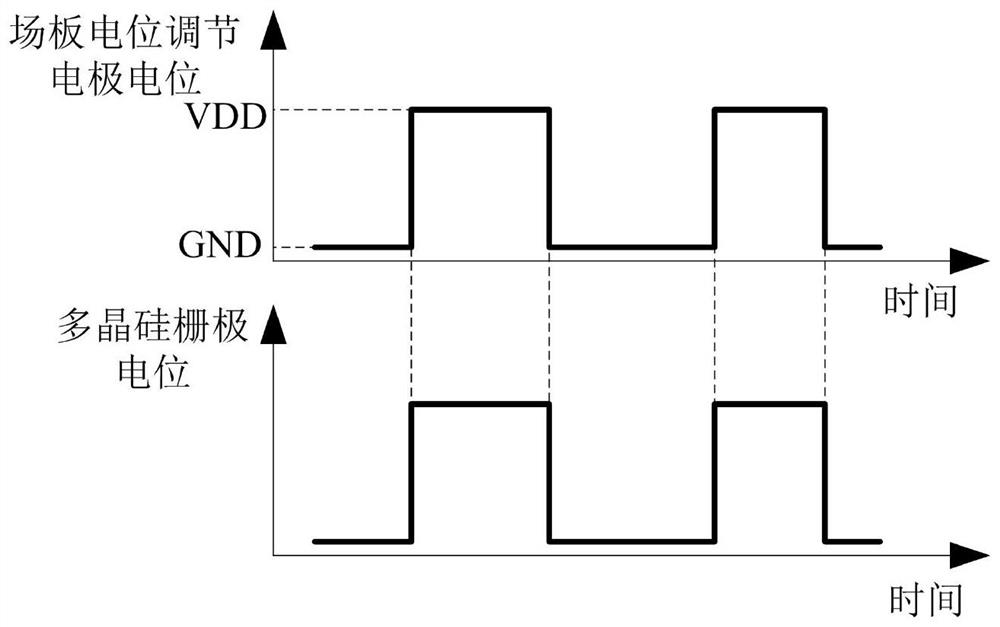

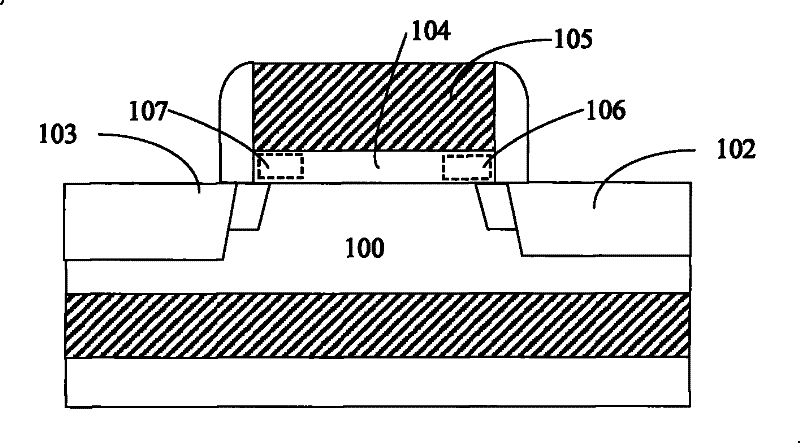

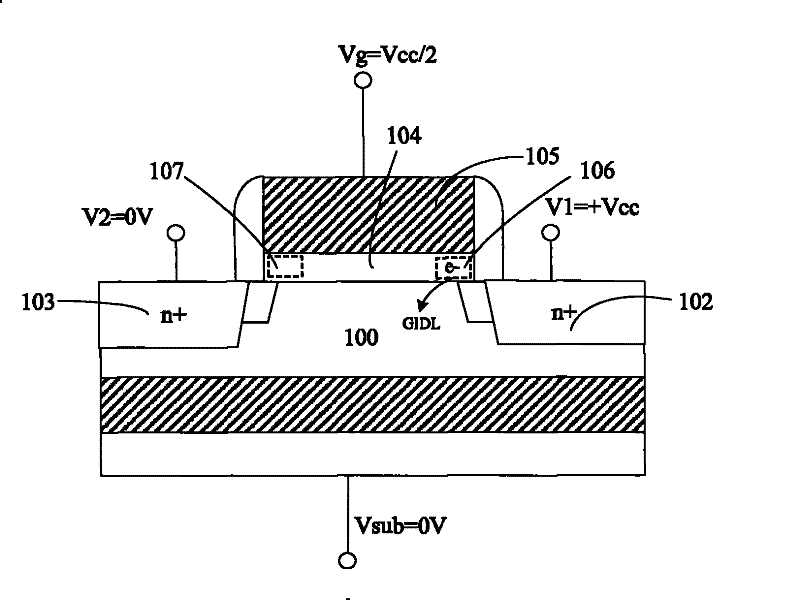

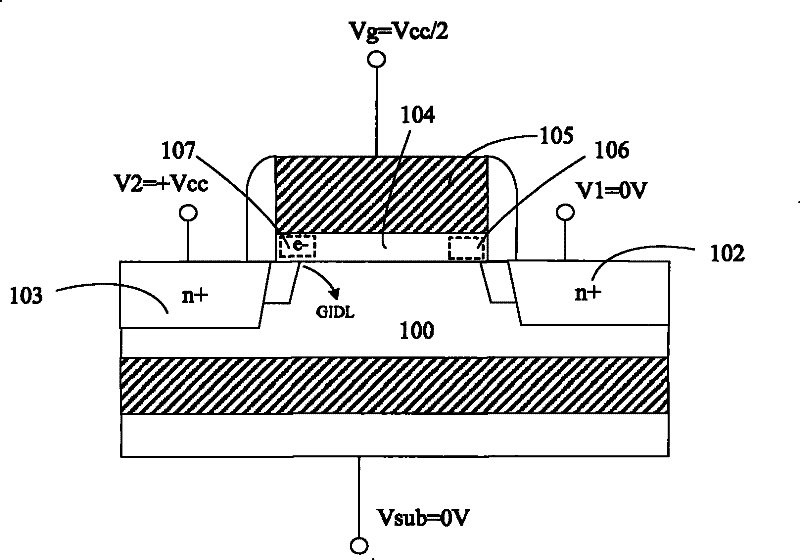

Semiconductor memory unit, driving method thereof and semiconductor memory

InactiveCN101826531AReduce leakage currentImprove performanceSolid-state devicesRead-only memoriesElectric forceDiffusion

The invention relates to a semiconductor memory unit, a driving method thereof and a semiconductor memory, wherein the semiconductor memory unit comprises silicon on an insulator, a first diffusion region, a second diffusion region, a grid dielectric layer, a grid electrode, a first electric charge storage region and / or a second electric charge storage region, wherein the first diffusion region and the second diffusion region are positioned in top-layer silicon and mutually separated, and the conduction types of the first diffusion region and the second diffusion region are the same; the grid dielectric layer and the grid electrode are sequentially positioned on the top-layer silicon above a channel region; and the first electric charge storage region and / or the second electric charge storage region are / is respectively positioned in the grid dielectric layer and close to the part between the channel region and the first diffusion region and in the grid dielectric layer and close to the part between the channel region and the second diffusion region, and the first electric charge storage region and / or the second electric charge storage region are / is formed through electric field force. In the invention, the first electric charge storage region and / or the second electric charge storage region are / is formed in the grid dielectric layer through the electric field force to form the memory unit, and the memory unit is compatible with a traditional logic circuit forming process, thereby improving the performance of an integrated circuit and reducing the power consumption.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

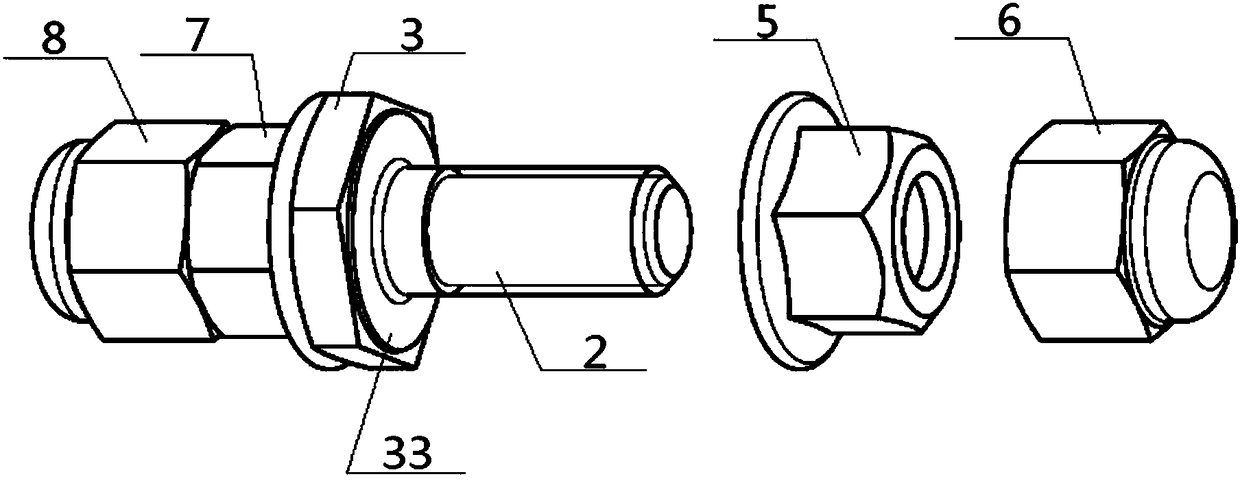

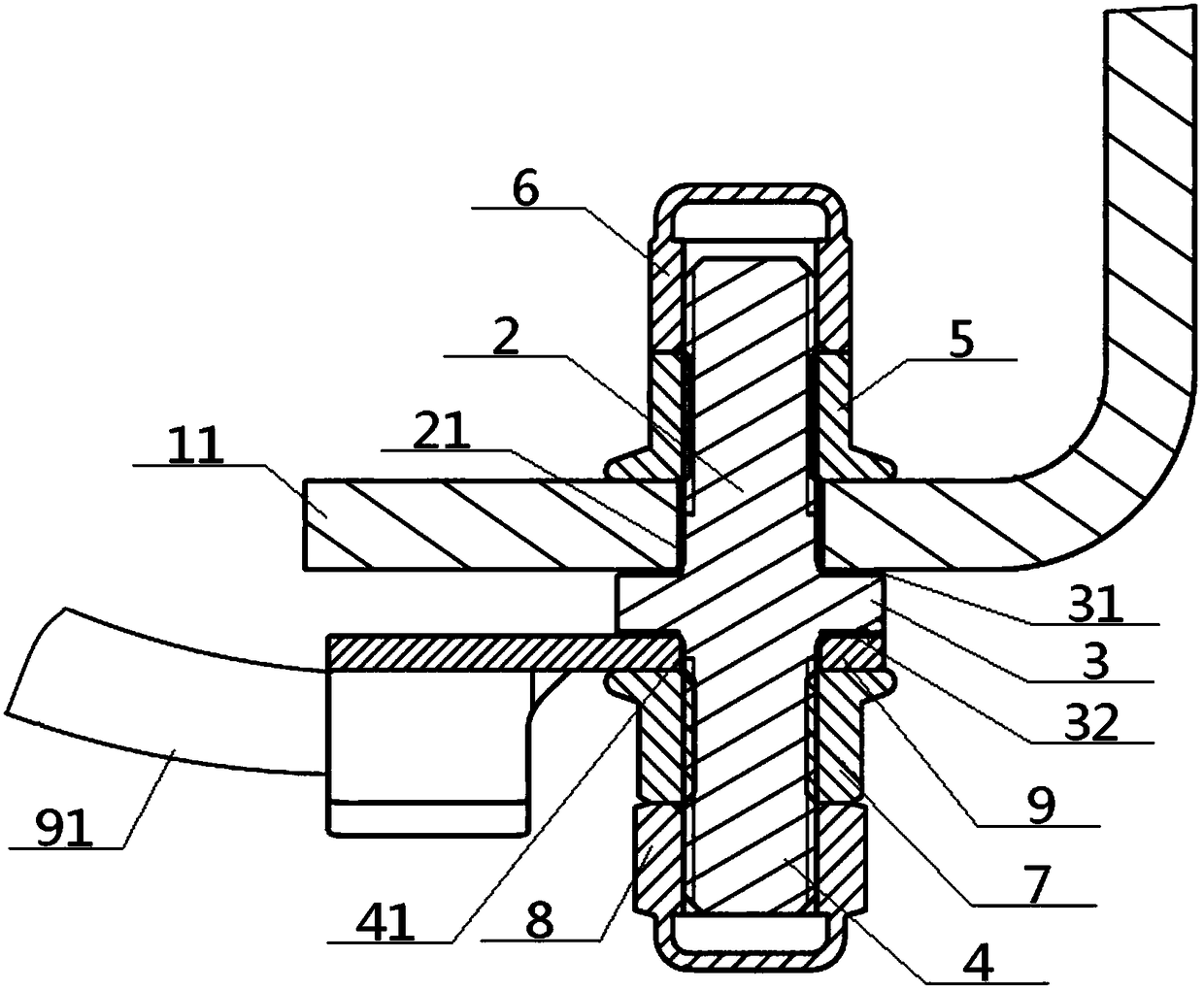

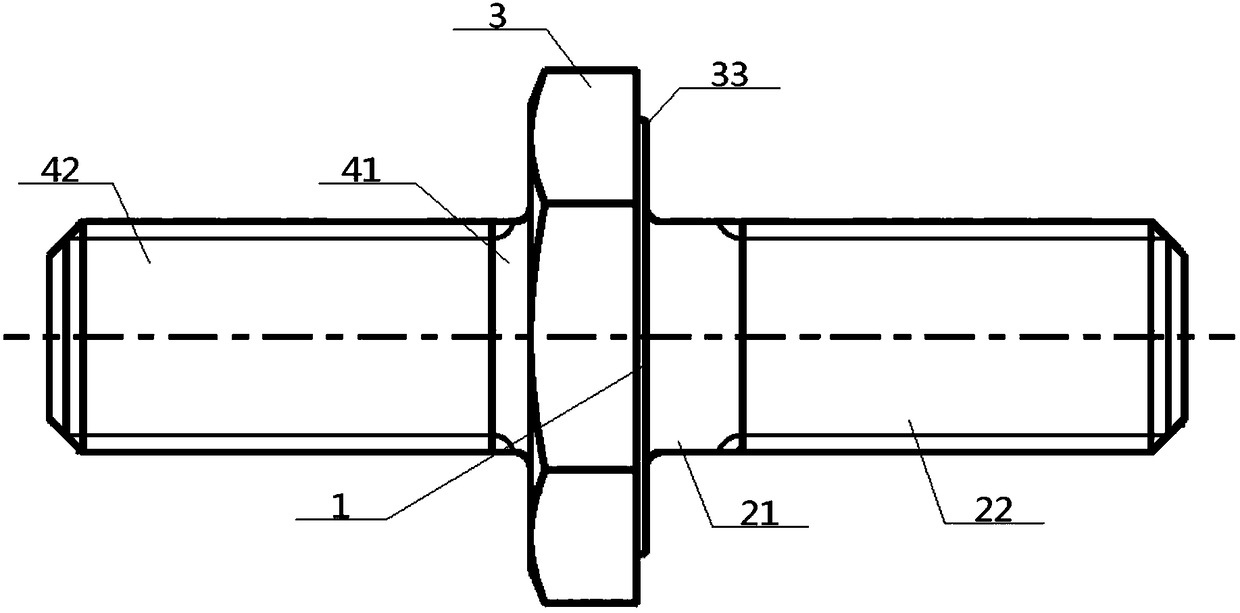

Common grounding structure and use method thereof

ActiveCN108155490AAvoid corrosionNot easy to corrodeLine/current collector detailsConnection contact member materialElectricityMechanical engineering

The invention relates to a common grounding structure. The structure comprises a mounting bolt, a mounting nut, a wiring bolt and a wiring nut, the mounting bolt and the wiring bolt are connected to form a double-head grounding bolt of an integrated structure through a boss, and the two side surfaces of the boss are a common conduction contact surface and a wiring conduction contact surface; the mounting nut and a mounting covering cap sleeve the periphery of the mounting bolt from inside to outside, the wiring nut and a wiring covering cap sleeve the periphery of the wiring bolt from inside to outside, and the diameter of the boss is larger than the diameters of the mounting bolt and the wiring bolt. According to the common grounding structure, it can be guaranteed that the conduction contact surfaces are not easily corroded, the electric performance is not easily aged and lowered, the technology is convenient and easy to implement, the anti-loosening and protection effects are extremely good, and the production cost is low.

Owner:DONGFENG COMML VEHICLE CO LTD

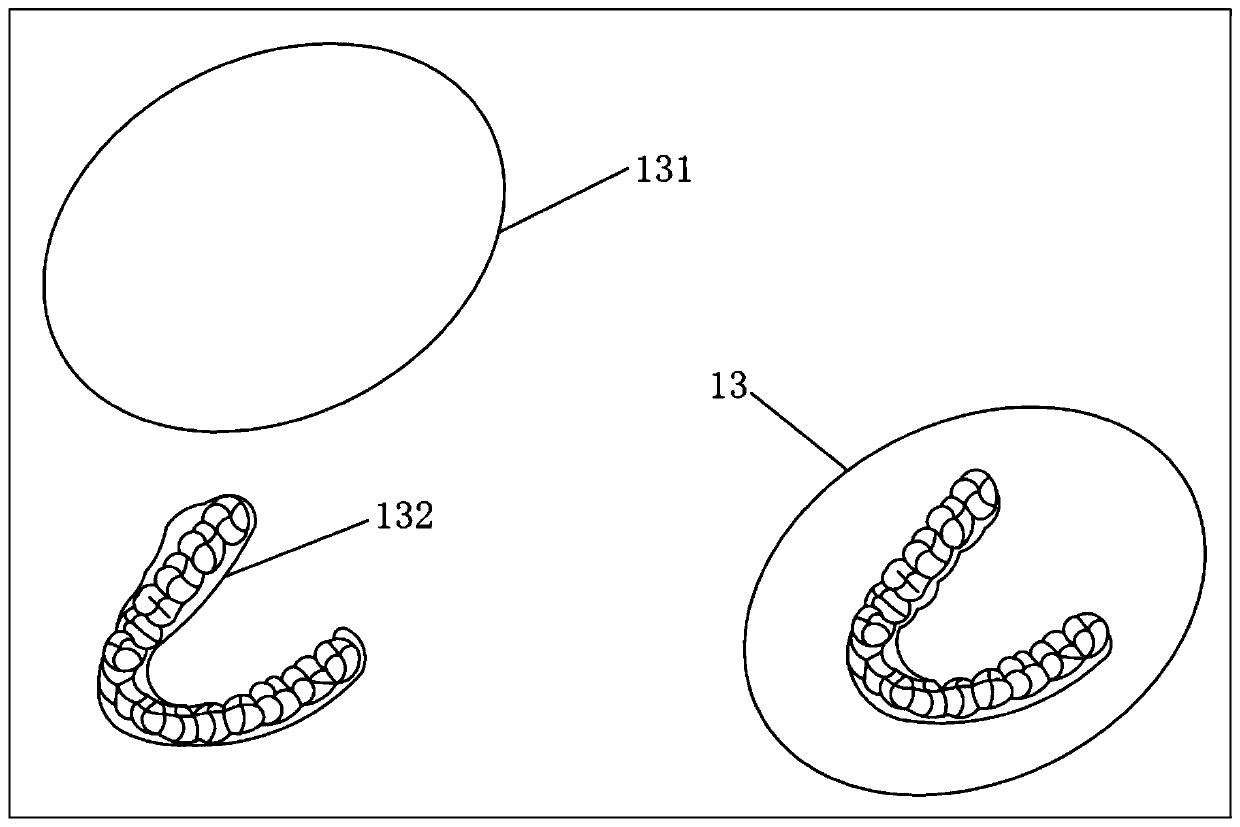

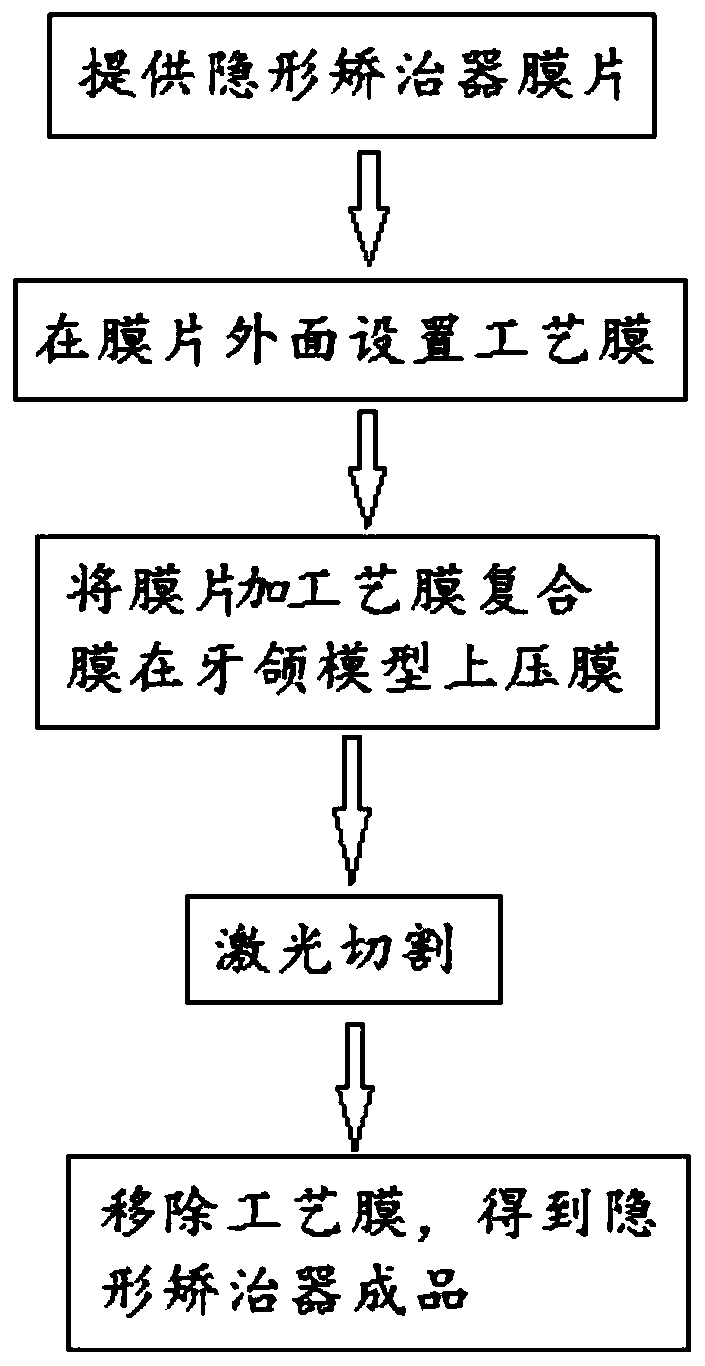

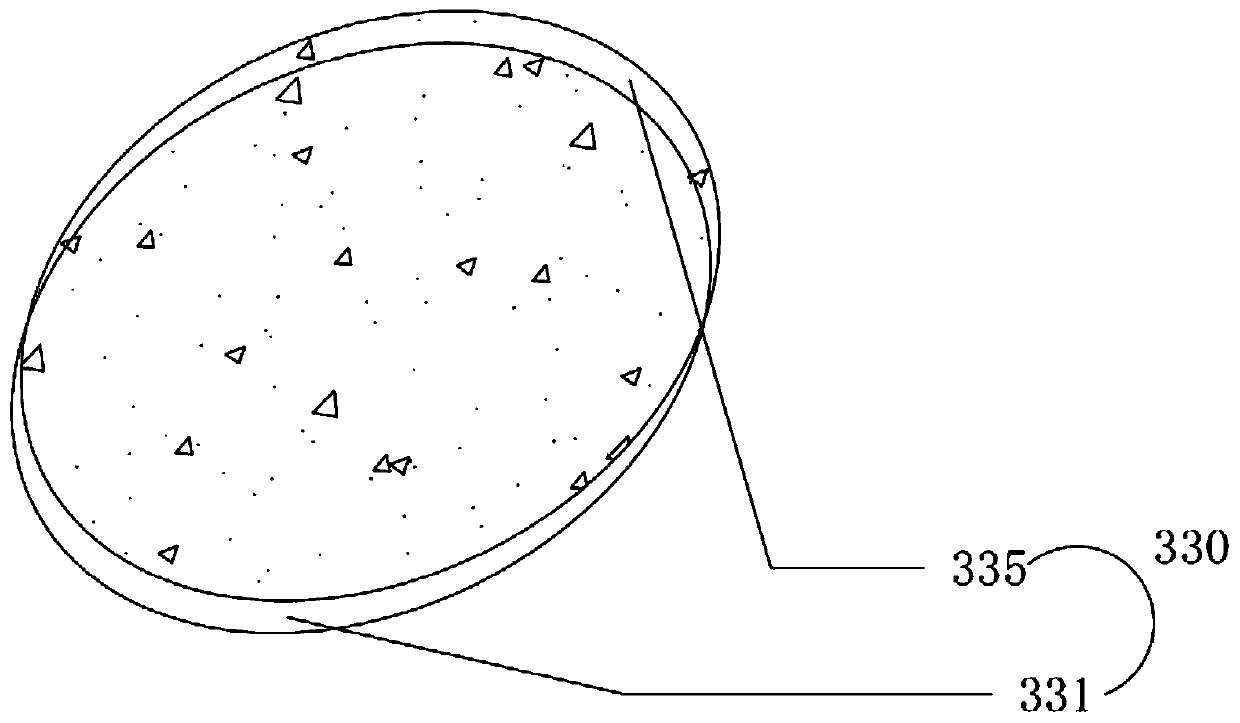

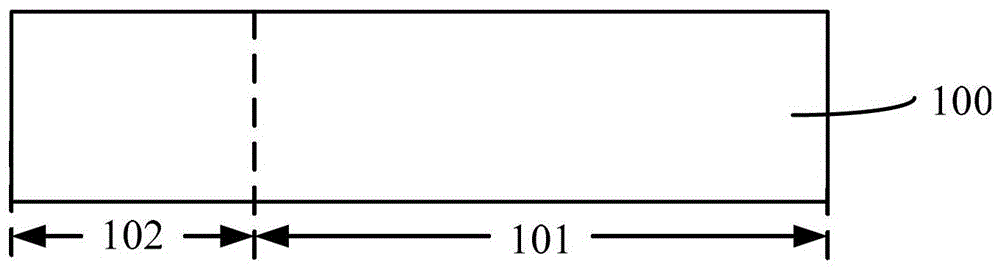

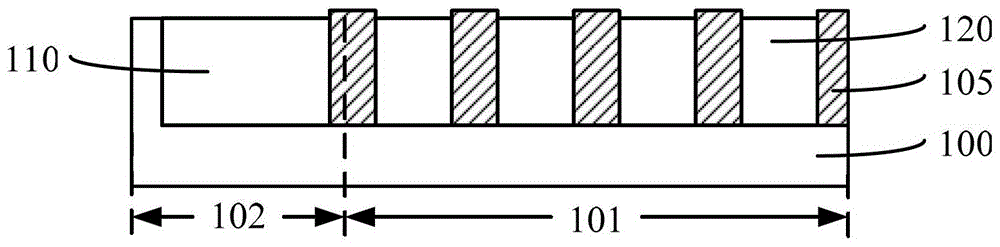

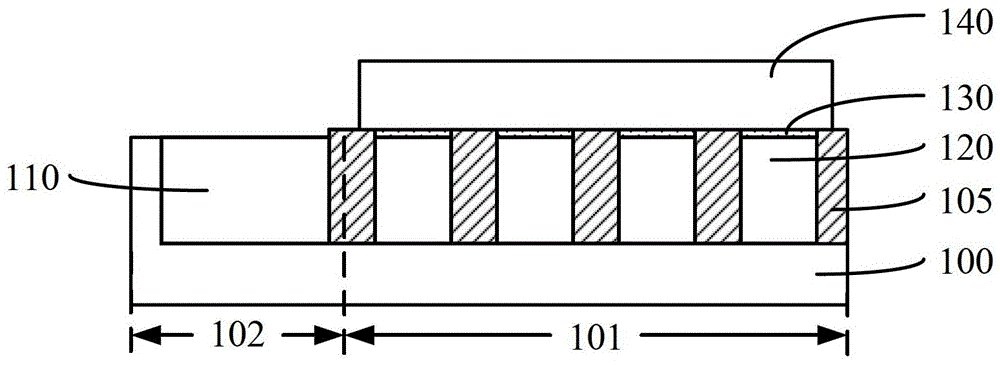

Invisible appliance production method

PendingCN110539473AMeet quality requirementsNo increase in process costOthrodonticsLaser beam welding apparatusEngineeringLaser cutting

The invention relates to the technical field of dental orthodontics, and specifically discloses an invisible appliance production method. The invisible appliance production method comprises the following steps of: providing a diaphragm for making an invisible appliance; arranging a layer of process film on the outer surface of the diaphragm; placing the diaphragm and one surface opposite to the outer surface provided with the process film on a dental model for film pressing to obtain the invisible appliance to be cut; performing laser cutting on the invisible appliance to be cut along a predetermined cutting path, wherein laser is incident from one side of the process film, the laser cuts through the process film and the diaphragm simultaneously, and the diaphragm and the process film arenot mixed at the cutting path; and removing the process film to obtain the invisible appliance. The invisible appliance production method solves the adverse effect on the quality of the appliance caused by smoke dust generated in the laser cutting process of the existing invisible appliance production.

Owner:浙江正雅齿科股份有限公司

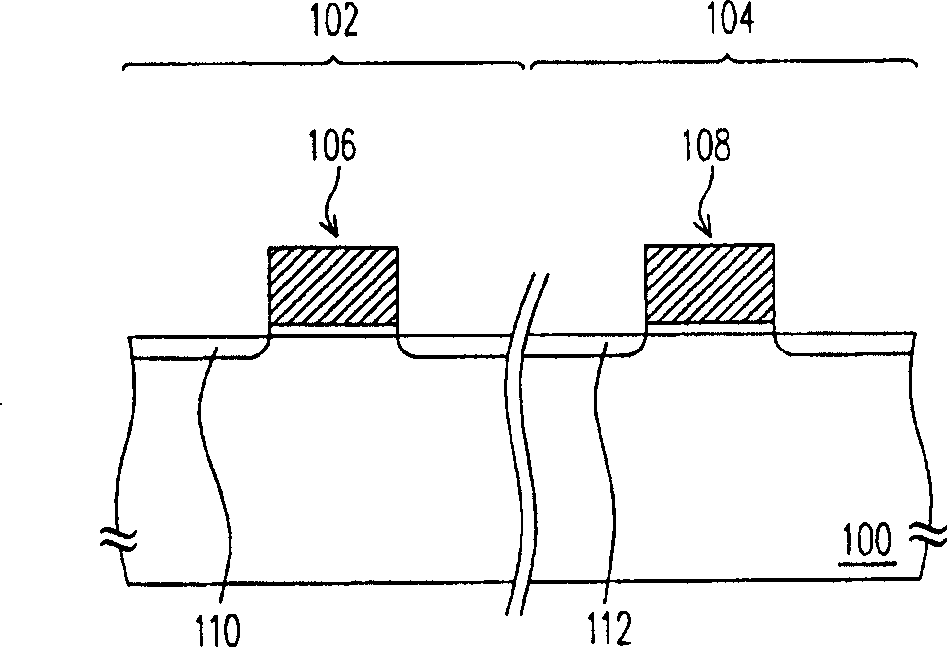

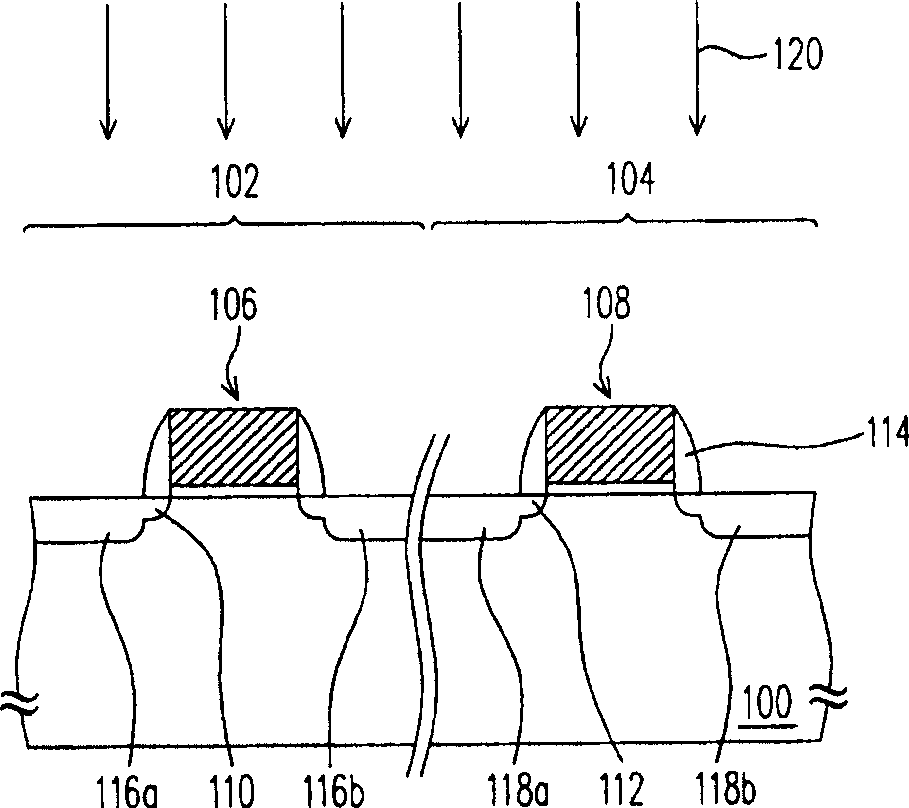

Production of semiconductor component and method for adjusting component channel area lattice distance

InactiveCN1855392AImprove performanceIncrease charge mobilitySemiconductor/solid-state device manufacturingMetallurgyMetal silicide

The method comprises: forming several grid structures on the substrate; forming a corresponding source region and a drain region on the portion of substrate aside each grid structure; forming a self-alignment metal silicides barrier layer on the substrate to overlap the grid structure and the surface of exposed substrate; making annealing practice, and when the annealing practice is made, the self-alignment metal silicides barrier layer will generate a tensile stress to make the substrate under the grid structure suffered the tensile stress; removing a portion of self-alignment metal silicides barrier layer to expose a portion of grid structure and a portion of substrate surface; making the self-alignment metal silicides process.

Owner:UNITED MICROELECTRONICS CORP

Anti-fuse structure and method for forming the same

ActiveCN104103624ALower programming voltageNo increase in process costSemiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

An anti-fuse structure and a method for forming the same. The anti-fuse structure includes: a semiconductor substrate including an anti-fuse area and an interconnection area; a shallow trench isolation structure located inside the semiconductor substrate and isolating the anti-fuse area into at least one active area; a gate oxide located on an entire surface of the active area, the thickness of a gate oxide on an edge position of the active area is smaller than that of a gate oxide in a middle position; a gate electrode located on a surface of the gate oxide and a surface of part of the shallow trench isolation structure; and a first electrode located on a surface of the interconnection area of the semiconductor substrate, the first electrode being electrically connected with the active area. Since a thinner gate oxide is formed on an edge part of the whole active area, the area of the thinner gate oxide becomes larger, and thus a programming voltage for programming of gate oxide anti-fuse is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

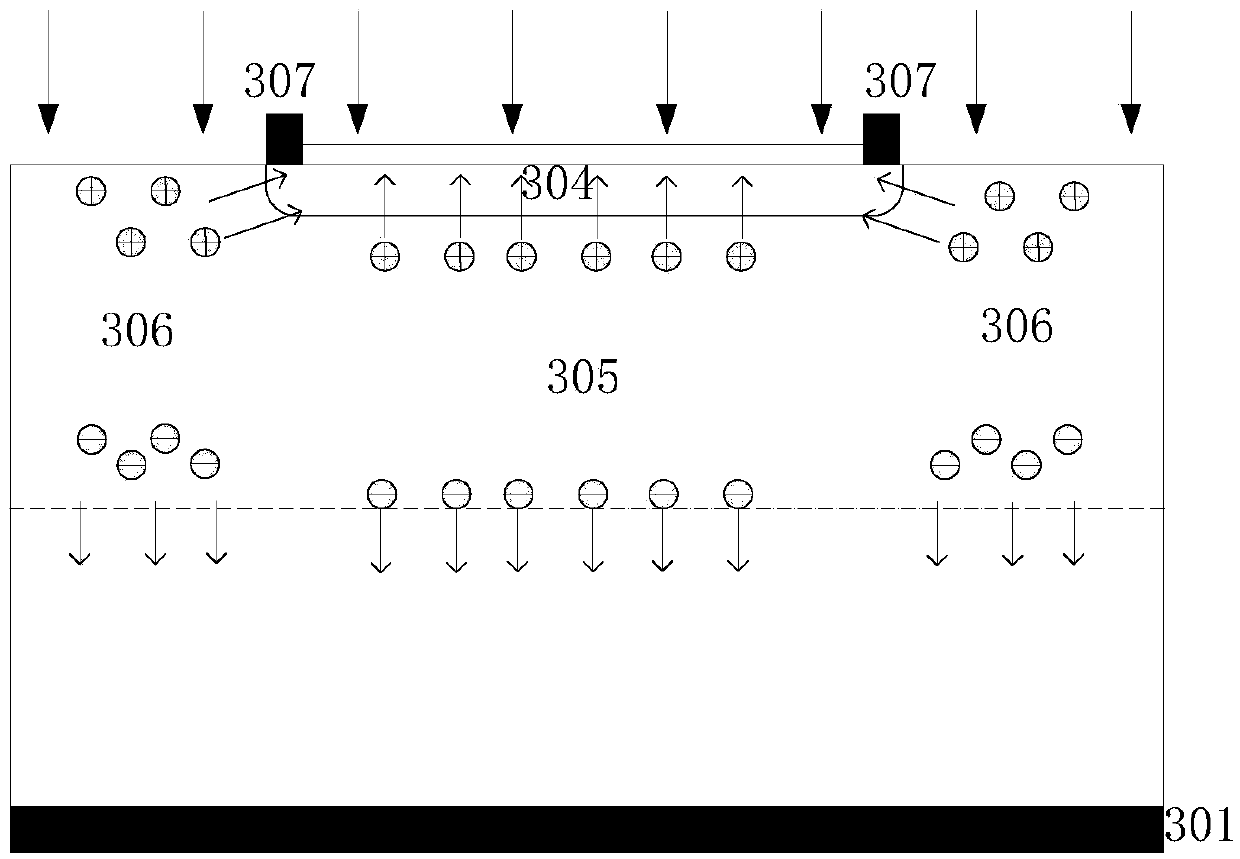

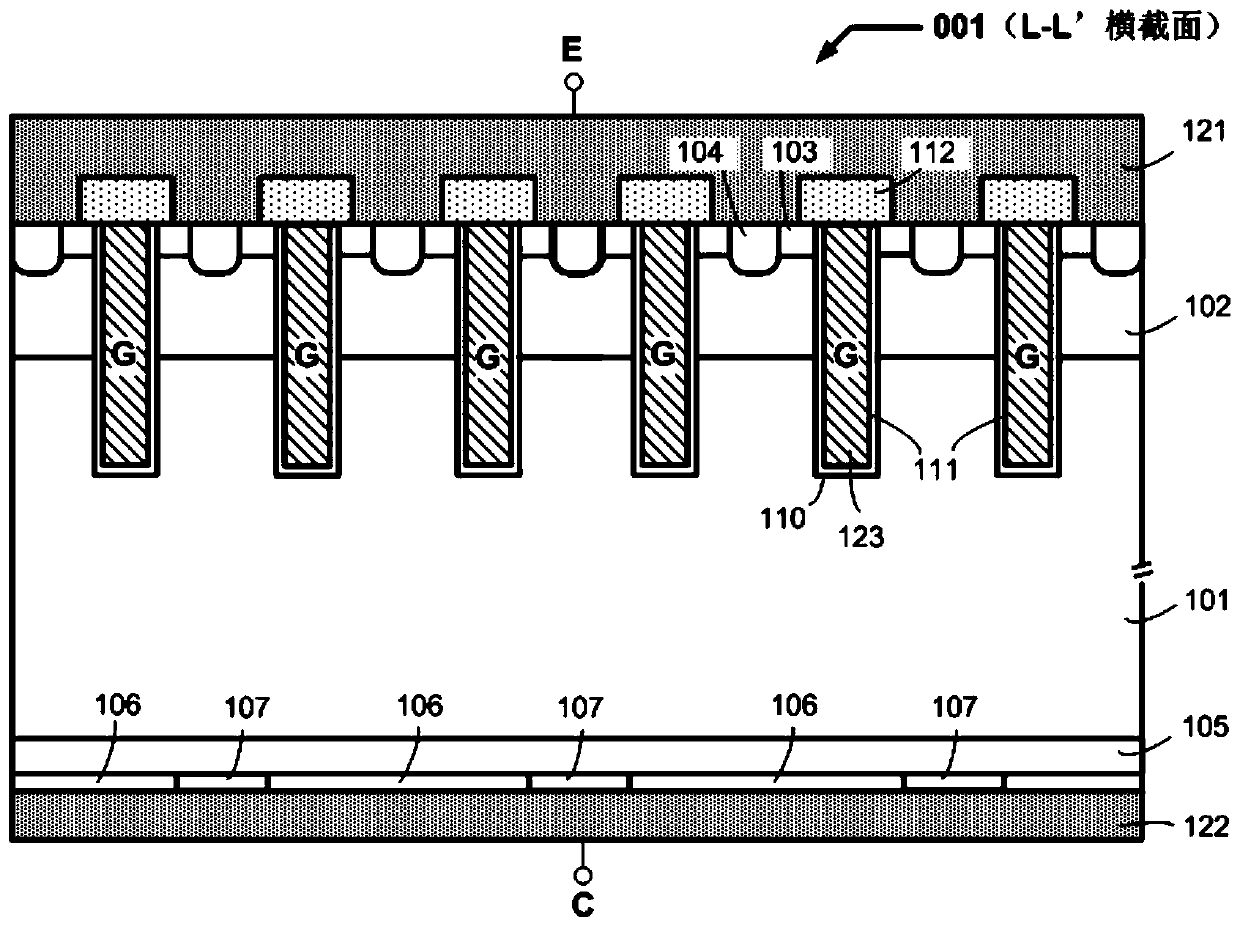

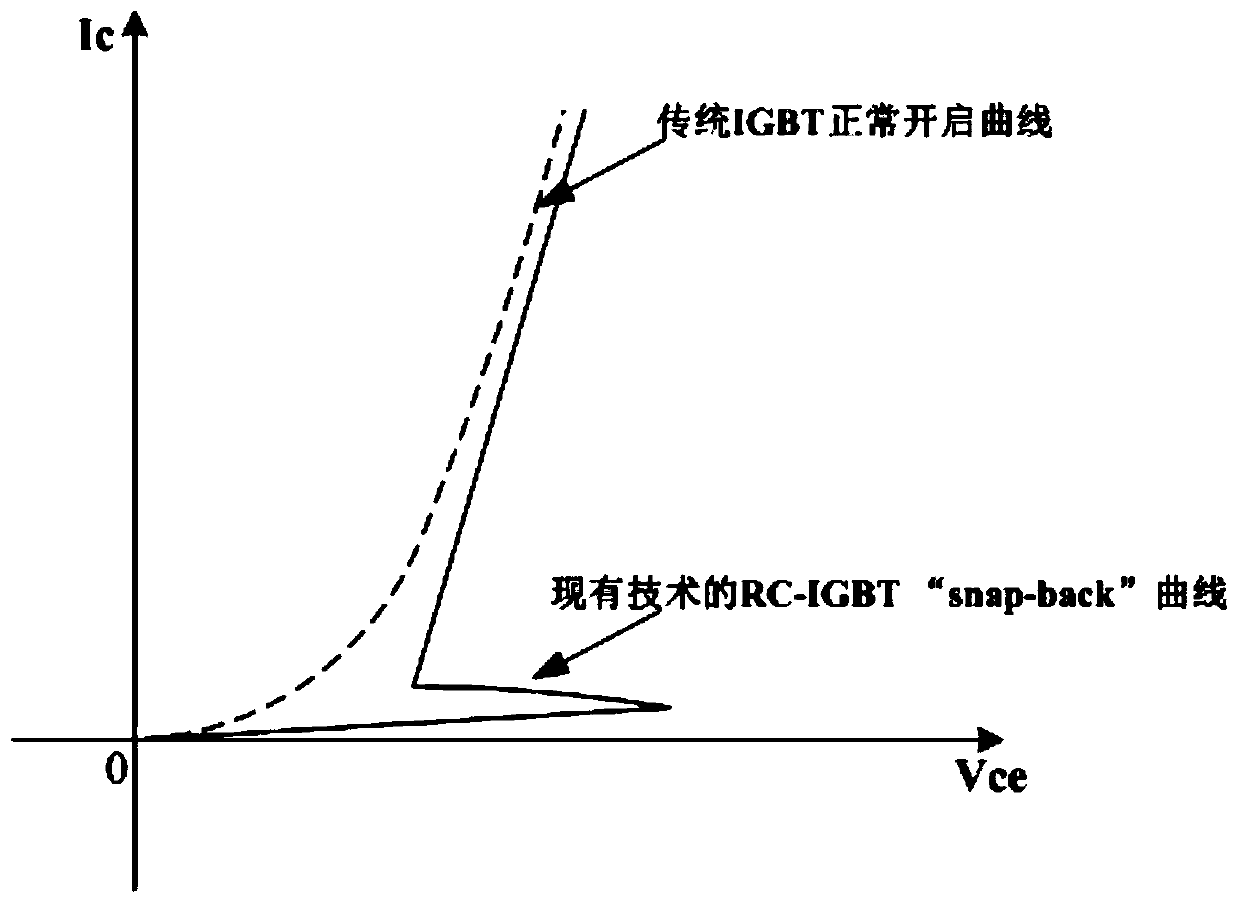

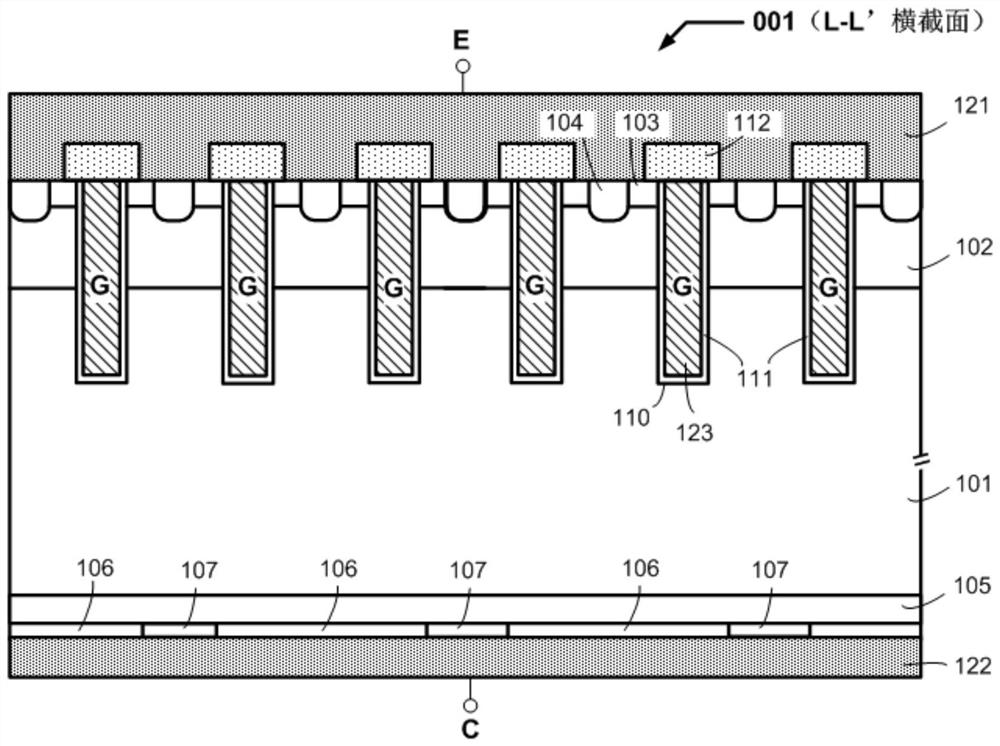

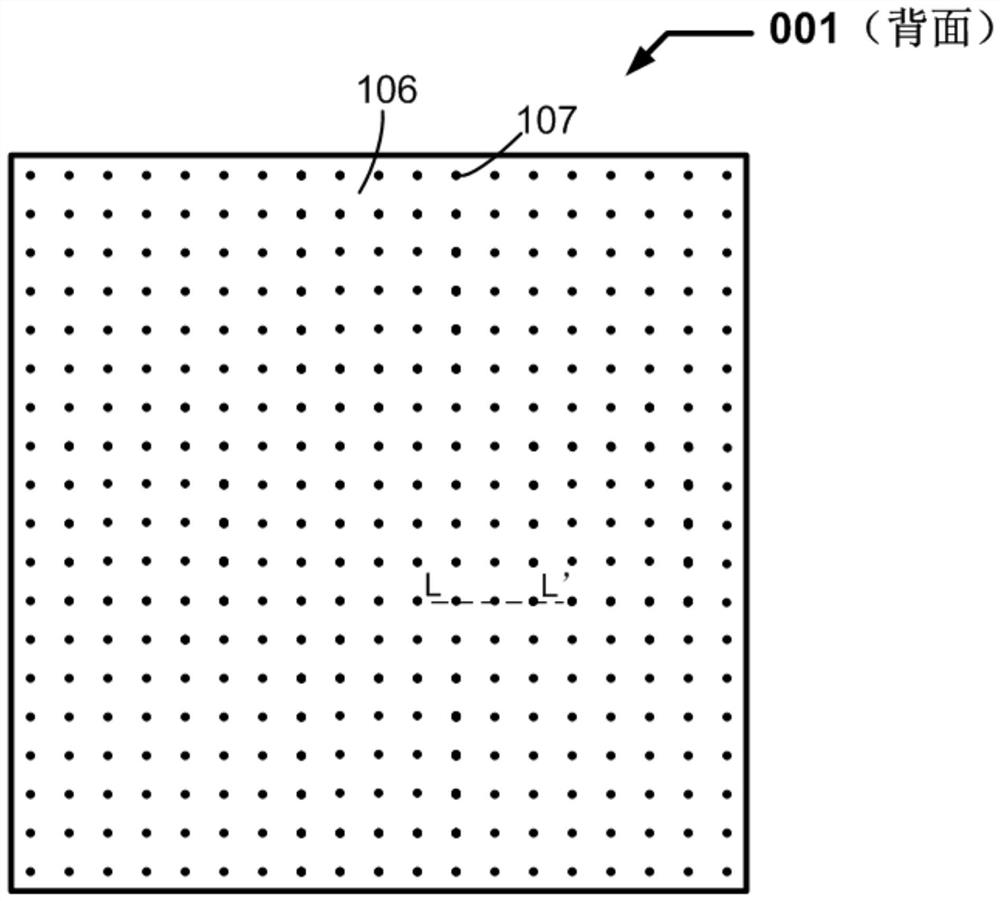

Reverse conducting insulated gate bipolar transistor

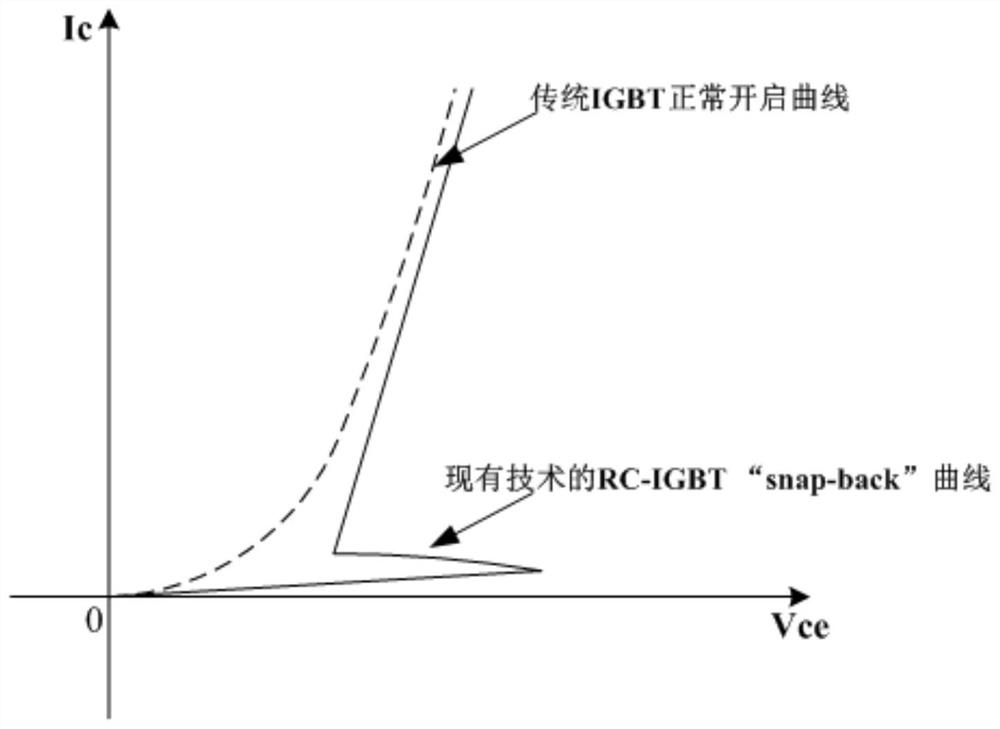

ActiveCN109728085ALower forward conduction resistanceHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceState of art

A reverse conducting insulated gate bipolar transistor (RC-IGBT) is provided. The present invention relates to a power semiconductor device. In view of the problem of an RC-IGBT device in the prior art, the present invention provides a design scheme which can solve the problem in the prior art by optimizing the distribution of the n+ cathode region on the back side of the RC-IGBT device. Comparedwith a conventional RC-IGBT device, the RC-IGBT device of the present invention, by special design of the back structure, can suppress the turn-on voltage jumpback problem of the device whiling maintaining the low forward and reverse on-state loss of the device and not increasing the process cost, and is beneficial to improvement in the reliability of the RC-IGBT in practical application.

Owner:安建科技(深圳)有限公司

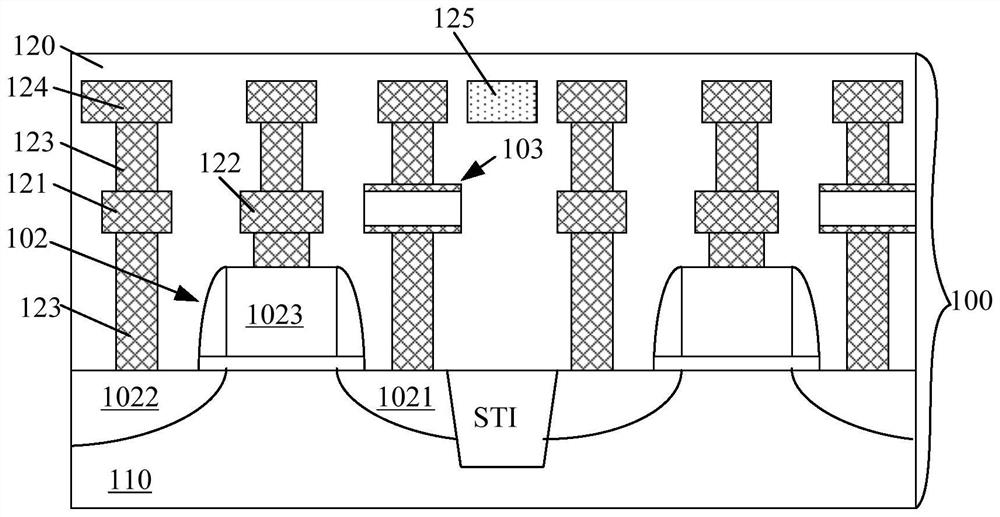

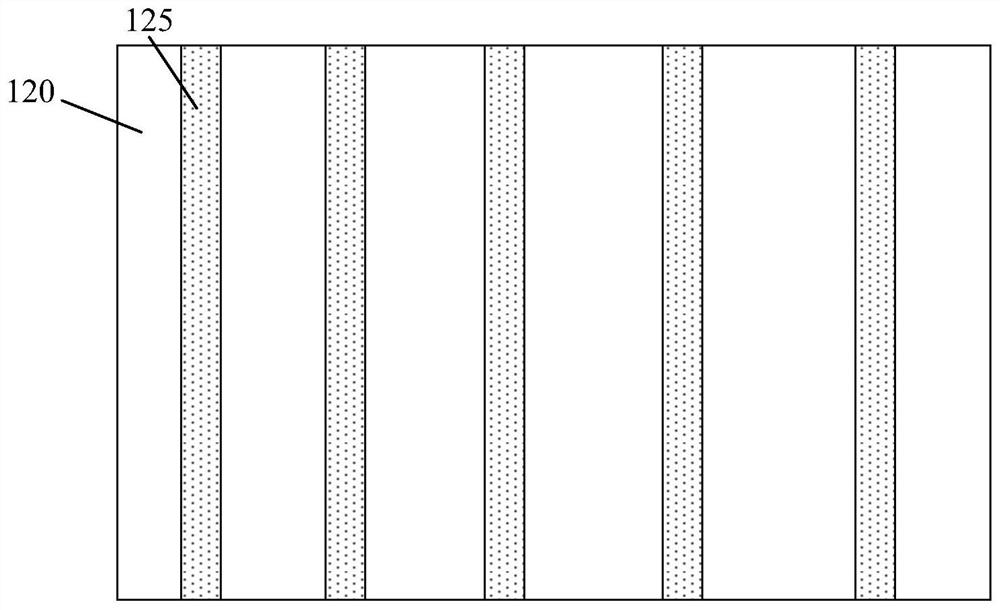

Memory and forming method thereof

PendingCN112054026AImprove storage densityIncrease process costTransistorSemiconductor/solid-state device detailsPhysicsLogic circuitry

The invention relates to a memory and a forming method thereof, and the memory comprises: a first base which comprises a first substrate, wherein a storage array formed on the front surface of the first substrate, and a first dielectric layer covering the storage array; a second base which comprises a second substrate, a logic circuit formed on the front surface of the second substrate and a second dielectric layer covering the logic circuit; and a metal heat dissipation line which is formed in the first dielectric layer and / or the second dielectric layer, wherein the first base and the secondbase are connected in a stacked and bonded mode. The storage density of the memory is improved.

Owner:CHANGXIN MEMORY TECH INC

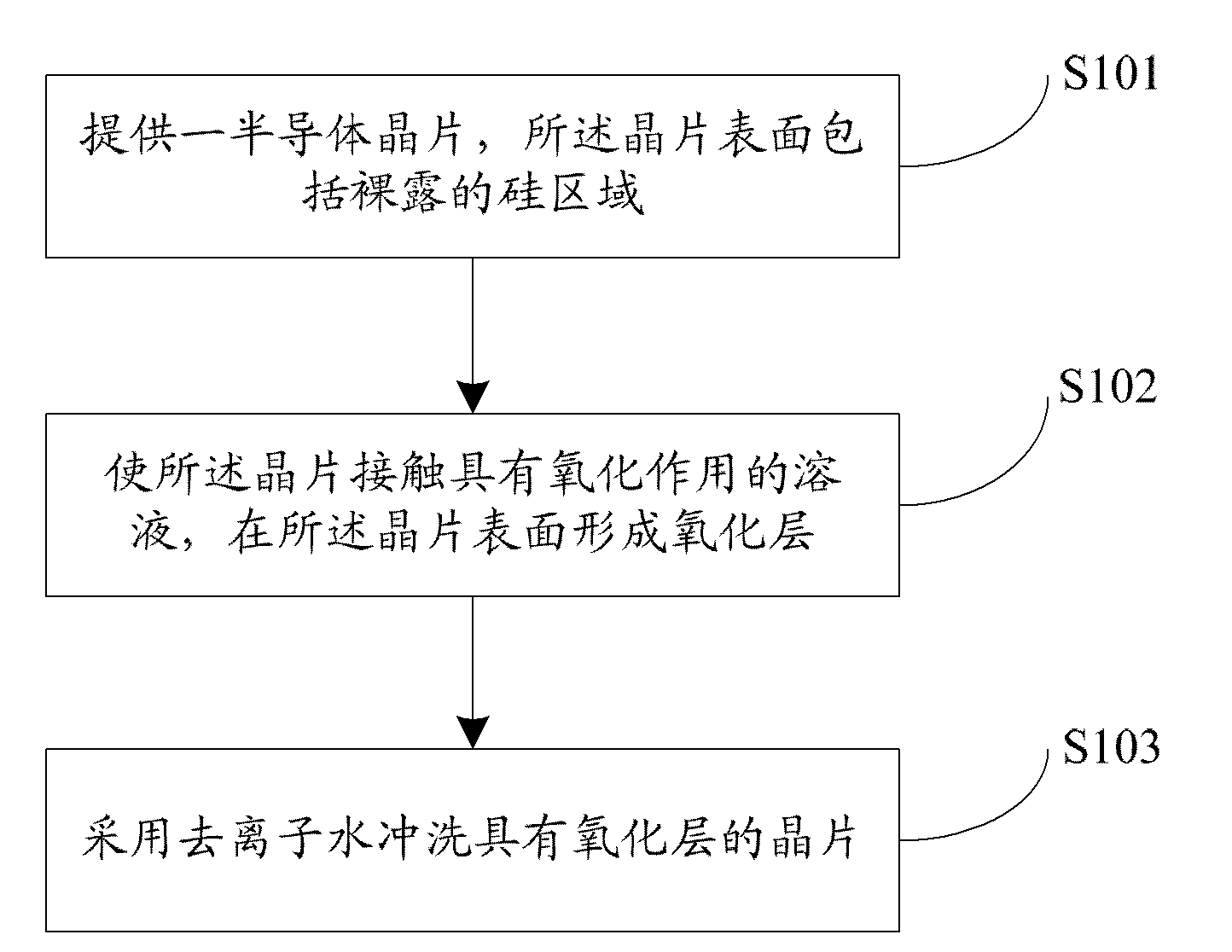

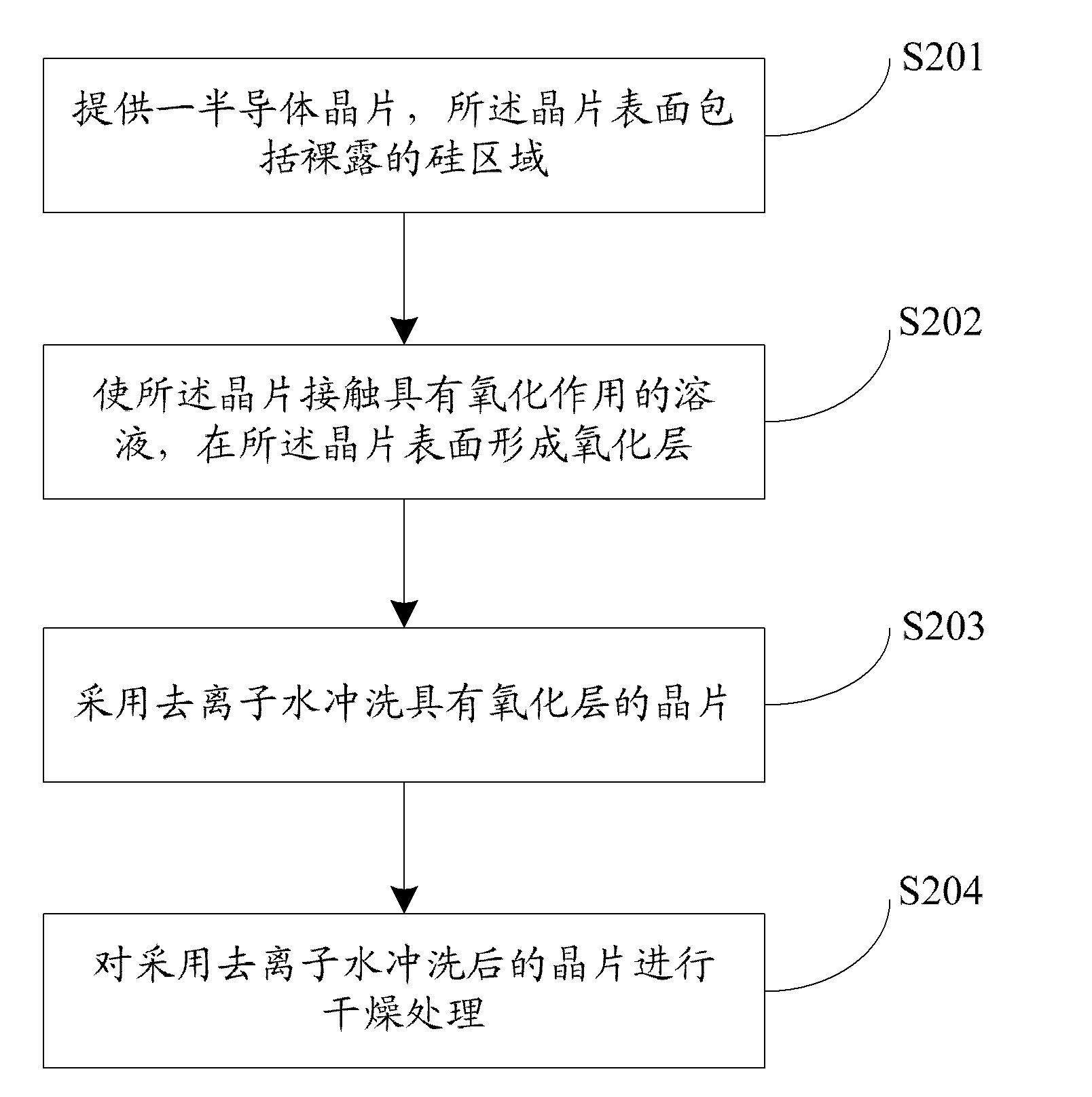

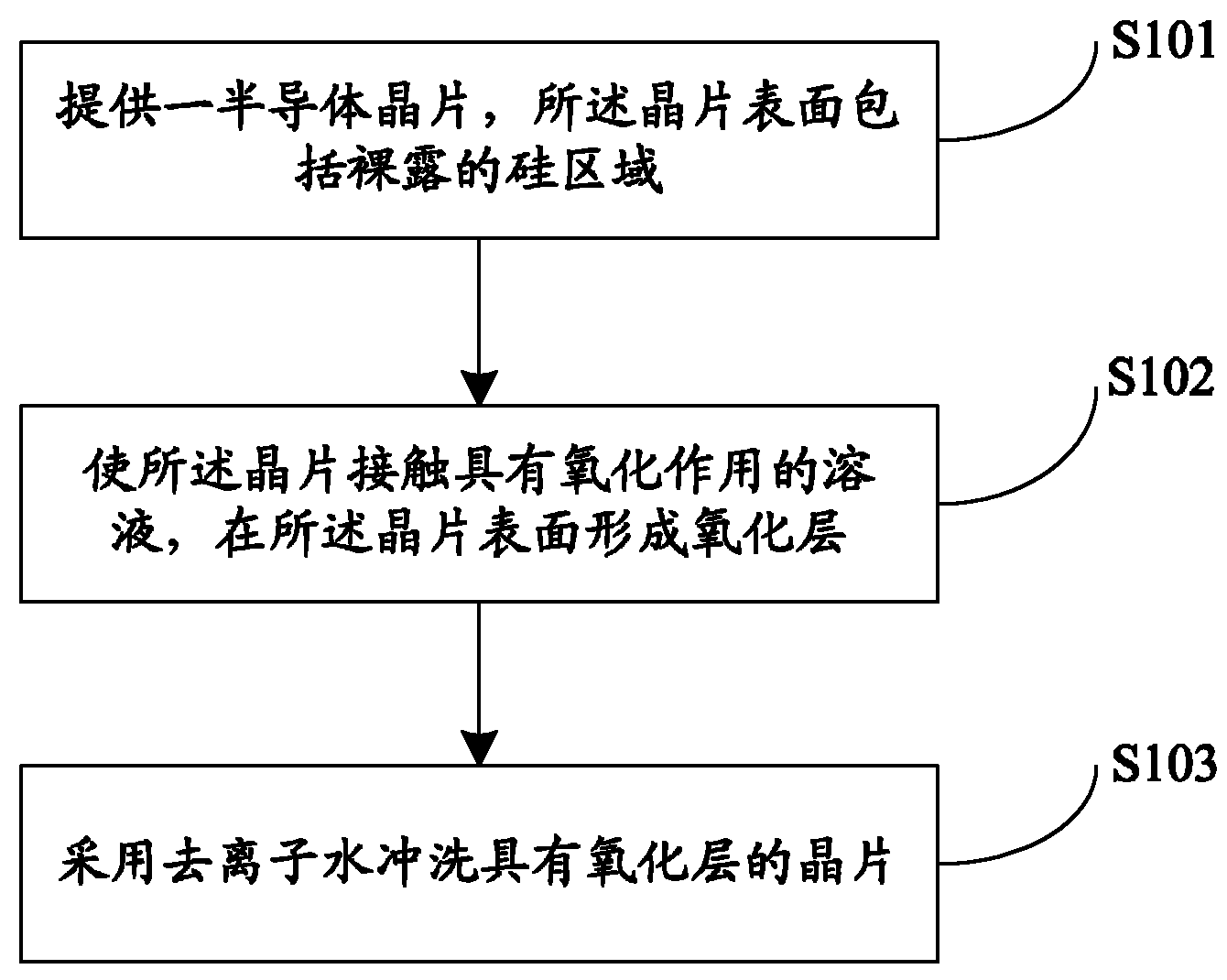

Wet chemical cleaning method

InactiveCN102468130AReduce the likelihood of formingNo increase in process costSemiconductor/solid-state device manufacturingIonSurface oxidation

The embodiment of the invention discloses a wet chemical cleaning method. The wet chemical cleaning method comprises the following steps of: providing a semiconductor wafer, wherein the surface of the wafer comprises an exposed silicon region; contacting the wafer with a solution with an oxidation effect and forming an oxidation layer on the surface of the wafer; and washing the wafer with the oxidation layer by using deionzied water. By the method, one thin oxidation layer is formed on the surface of the semiconductor wafer and silicon exposed on the surface of the wafer is prevented from being directly contacted with the deionized water, so that when the wafer is washed by using the deionized water, no exposed silicon is dissolved into water, the silicon is not separated out in the subsequent drying process and the possibility of forming water track on the surface of the semiconductor wafer is reduced. According to the method, the solution with the oxidation effect in the conventional production process can be adopted, so the process cost is reduced.

Owner:CSMC TECH FAB1 +1

Semiconductor device and producing method thereof

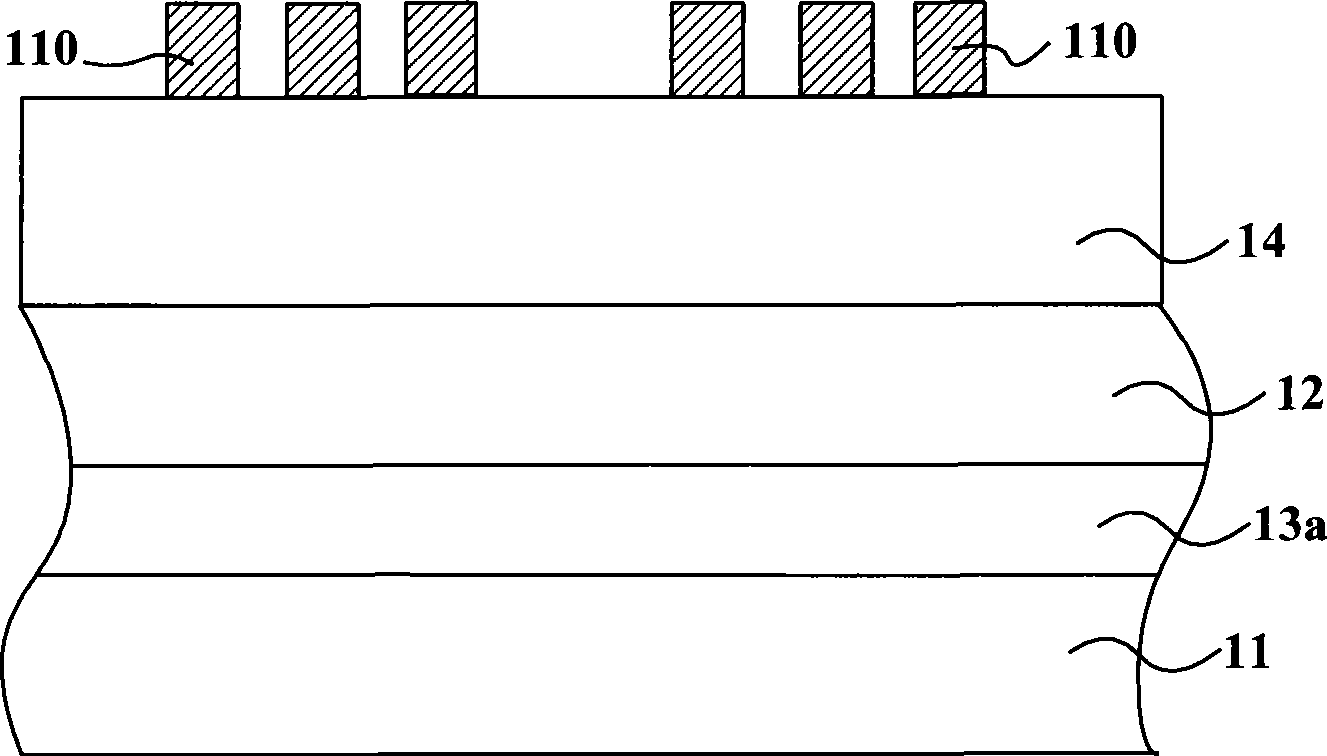

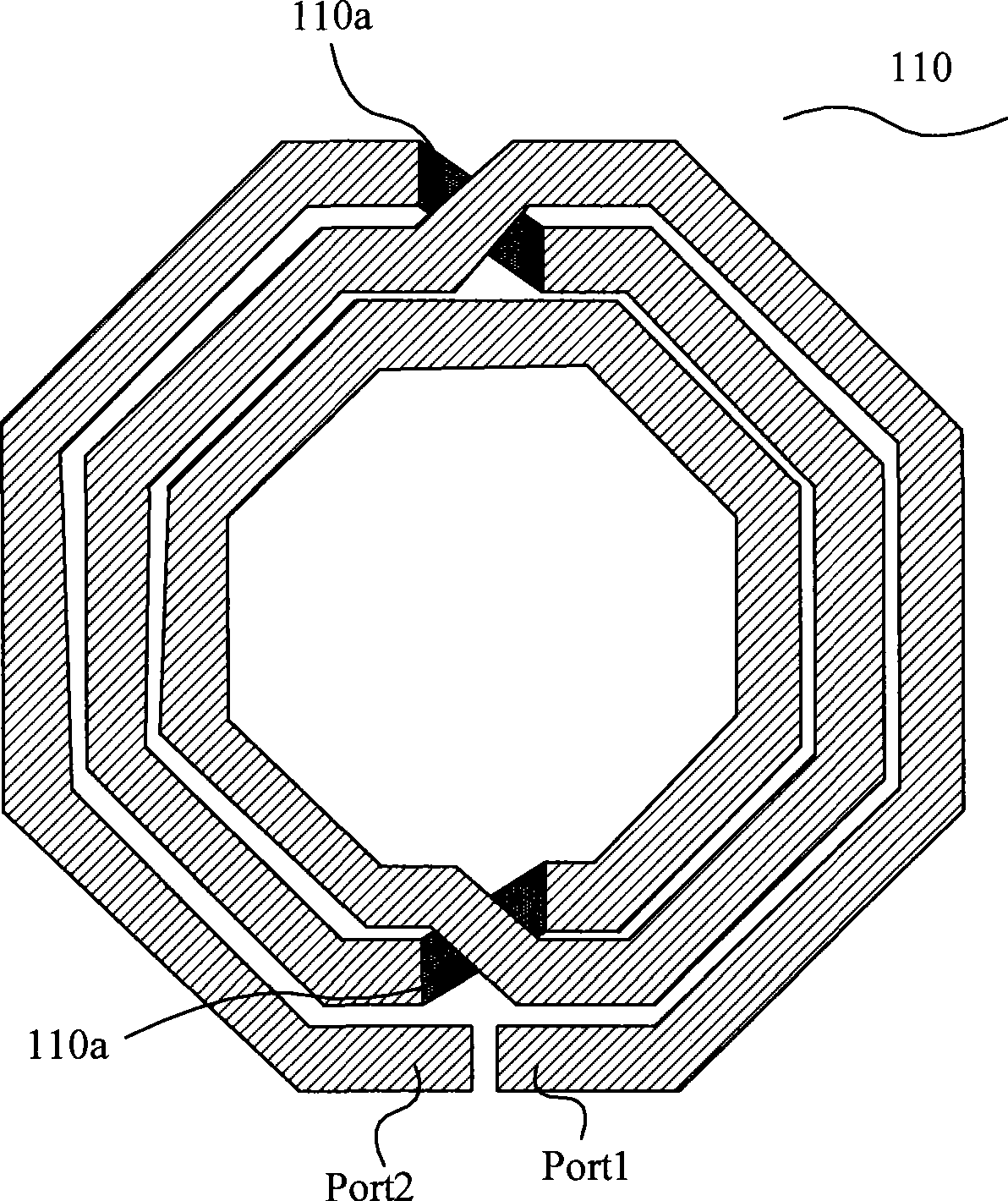

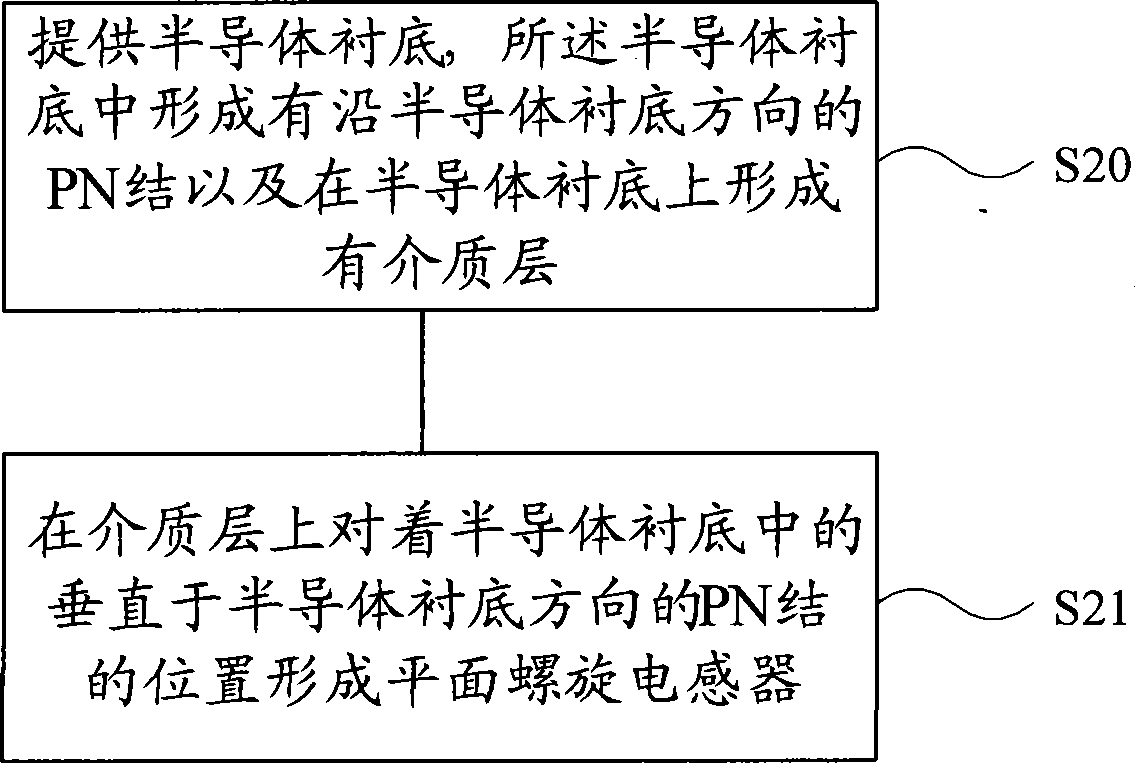

ActiveCN101459177AReduce lossNo increase in process costSolid-state devicesSemiconductor/solid-state device manufacturingPlanar spiral inductorsP–n junction

A manufacturing method for semiconductor devices comprises steps of providing a semiconductor substrate, wherein a PN junction is formed in the semiconductor substrate along the direction of the semiconductor substrate and a dielectric layer is formed on the semiconductor substrate, and forming a planar spiral inductor facing the position of the PN junction which is in the semiconductor substrate and is perpendicular to the direction of the semiconductor substrate on the dielectric layer. The invention further provides a semiconductor device. The planar spiral inductor facing the position of the PN junction which is in the semiconductor substrate and is perpendicular to the direction of the semiconductor substrate is formed on the dielectric layer, thereby reducing the loss of the planar spiral inductor in the semiconductor substrate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

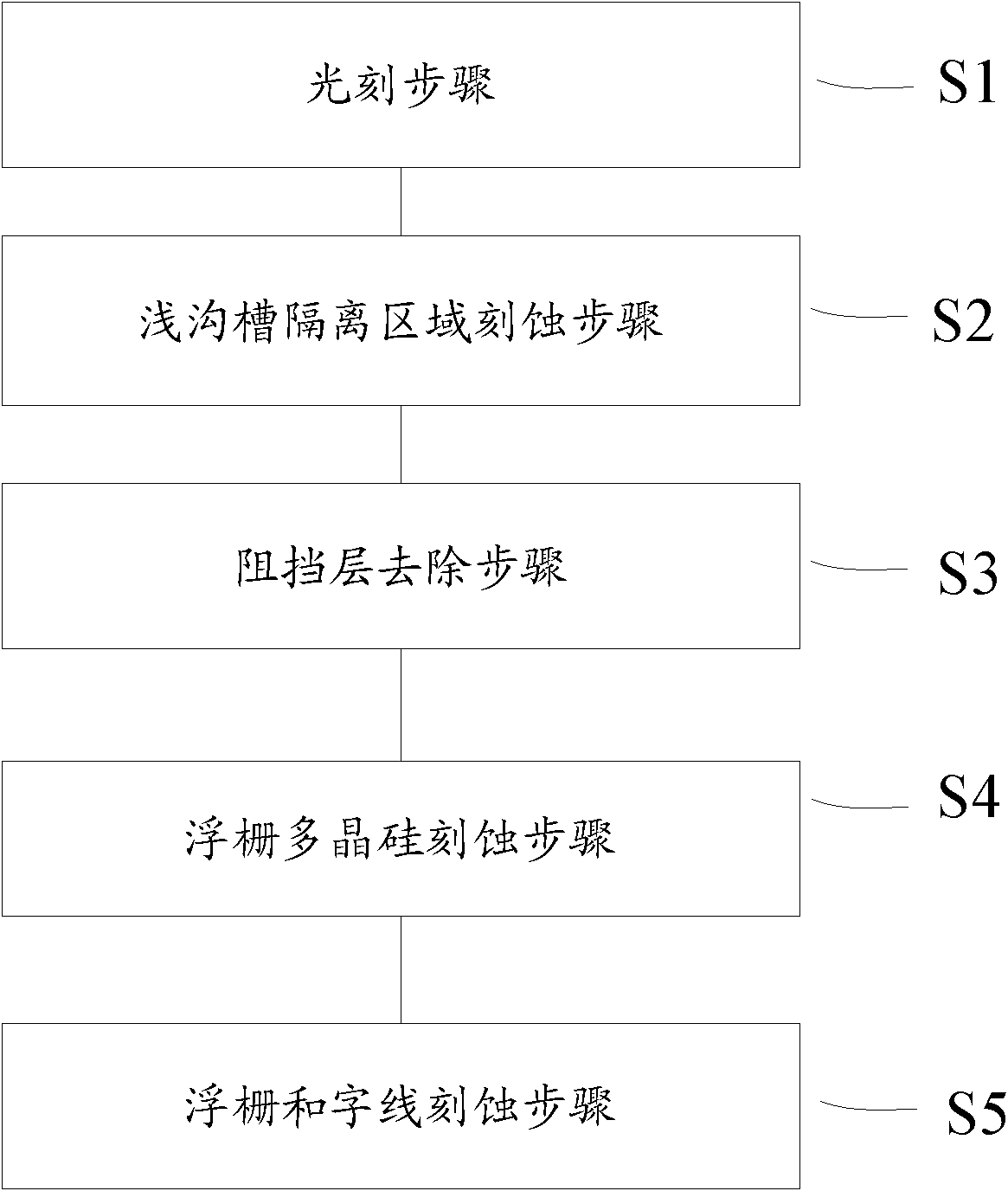

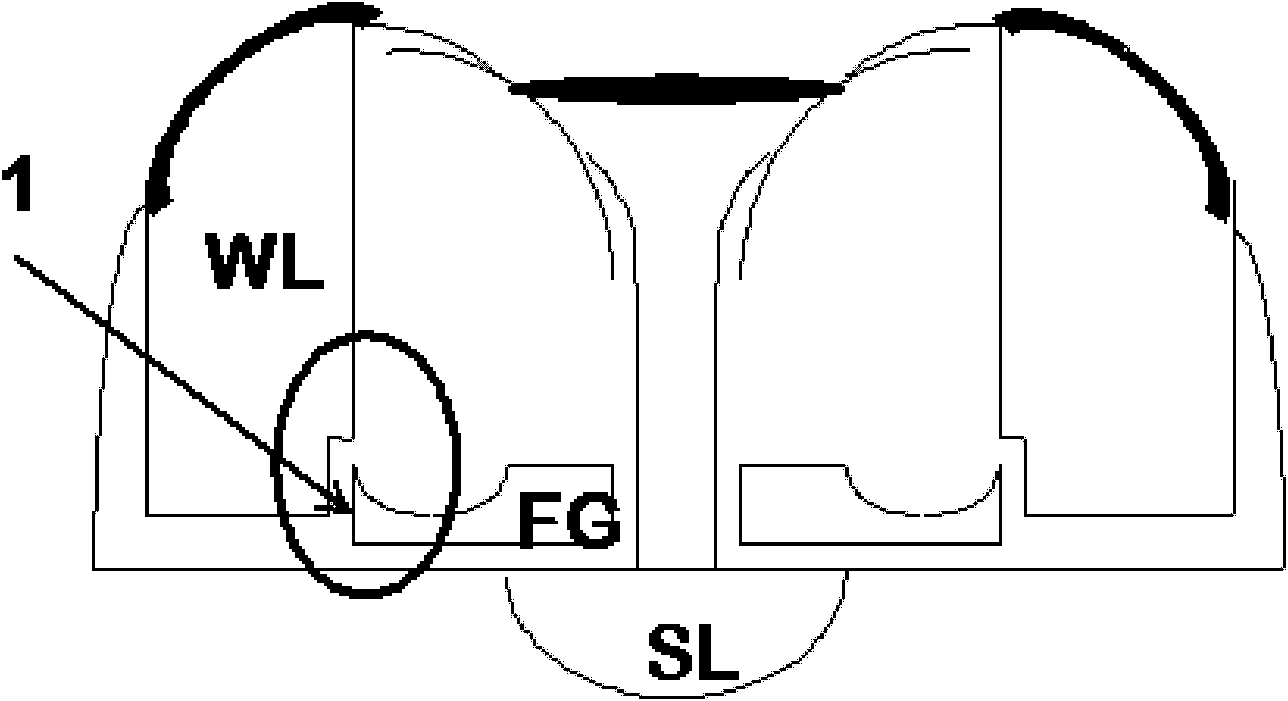

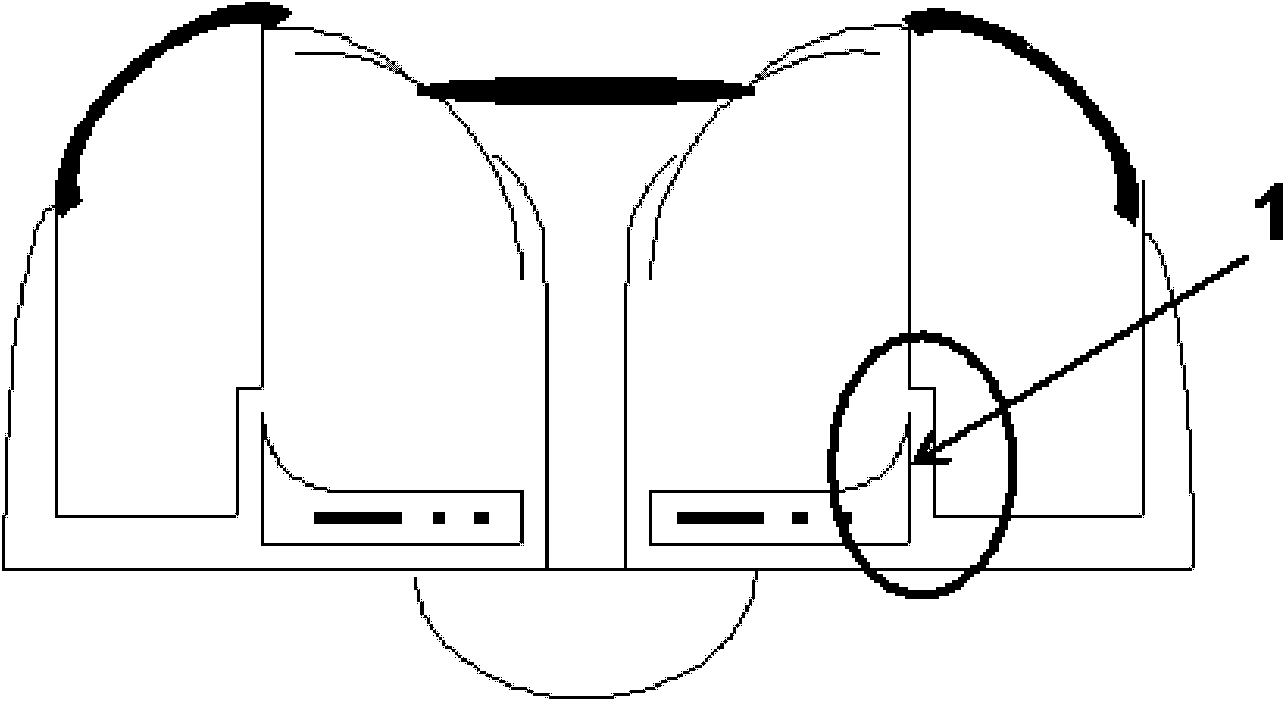

Split-gate type memory and manufacturing method thereof

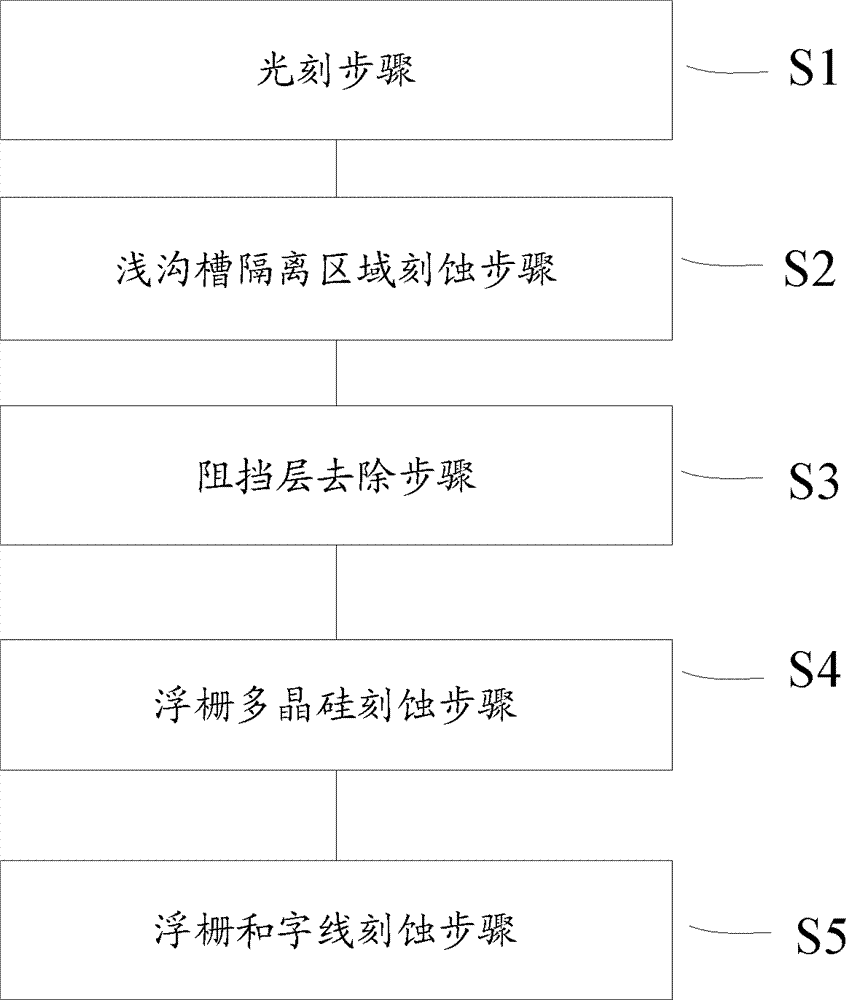

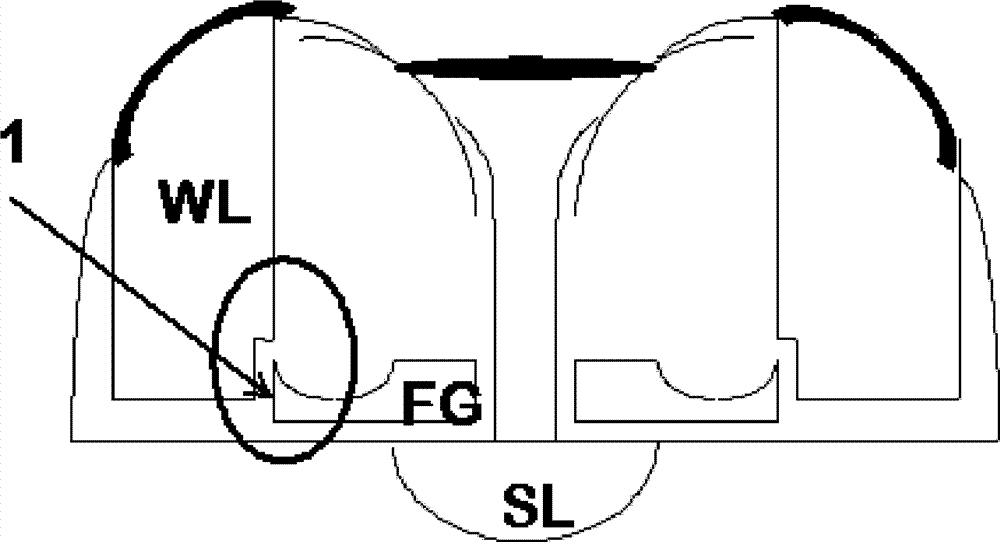

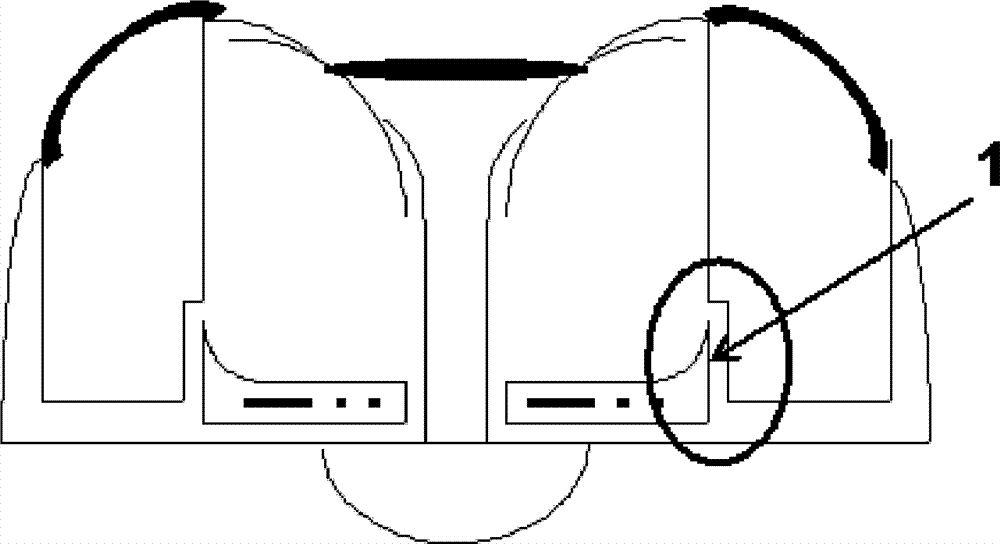

ActiveCN102222646ADoes not increase production costsLower the altitudeTransistorSemiconductor/solid-state device manufacturingCapacitanceVoltage

The invention provides a split-gate type memory and a manufacturing method thereof. According to the manufacturing method of the split-gate type memory, provided by the invention, the method comprises: a photoetching step for defining a shallow trench isolated region; a step for etching the shallow trench isolated region, wherein the height of the shallow trench isolated region of a word line region of a unit array in the split-gate type memory is reduced; a barrier layer removing step for removing the barrier layers of the regions not covered by photoresistance; a floating gate (FG) polysilicon etching step for etching floating gate polysilicon not covered by the photoresistance; and an FG and word line etching step for etching an FG and a word line. The height of the top end of the FG of the split-gate type memory manufactured according to the manufacturing method of the split-gate type memory, provided by the invention, is lowered, the capacitance between the FG and the word line is reduced, and the capacitance between the FG and a select line is maintained invariable, therefore, the capacitance coupling efficiency is accordingly reduced so as to be helpful to improving programming efficiency and reducing an erasing voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A Reverse Conduction Insulated Gate Bipolar Transistor

ActiveCN109728085BNo increase in process costImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceElectrical polarity

A reverse conduction type insulated gate bipolar transistor, the invention relates to power semiconductor devices, aiming at the problems existing in RC-IGBT devices in the prior art, the invention provides a design scheme: by optimizing the backside n of the RC-IGBT device + The distribution of the cathode region can solve the problems existing in the prior art. Compared with the traditional RC-IGBT device, the RC-IGBT device of the present invention can maintain a lower positive direction of the device through the special design of the back structure. On the basis of suppressing the turn-on voltage rebound problem of the device without increasing the reverse conduction loss and the process cost, it is beneficial to improve the reliability of the RC-IGBT in practical applications.

Owner:安建科技(深圳)有限公司

Method for manufacturing split-gate memory and split-gate memory

ActiveCN102222646BDoes not increase production costsLower the altitudeTransistorSemiconductor/solid-state device manufacturingCapacitanceCapacitive coupling

The invention provides a split-gate type memory and a manufacturing method thereof. According to the manufacturing method of the split-gate type memory, provided by the invention, the method comprises: a photoetching step for defining a shallow trench isolated region; a step for etching the shallow trench isolated region, wherein the height of the shallow trench isolated region of a word line region of a unit array in the split-gate type memory is reduced; a barrier layer removing step for removing the barrier layers of the regions not covered by photoresistance; a floating gate (FG) polysilicon etching step for etching floating gate polysilicon not covered by the photoresistance; and an FG and word line etching step for etching an FG and a word line. The height of the top end of the FG of the split-gate type memory manufactured according to the manufacturing method of the split-gate type memory, provided by the invention, is lowered, the capacitance between the FG and the word line is reduced, and the capacitance between the FG and a select line is maintained invariable, therefore, the capacitance coupling efficiency is accordingly reduced so as to be helpful to improving programming efficiency and reducing an erasing voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Integrated circuit protection structure and manufacturing method thereof

ActiveCN110021573BInfluence gapBig gapSemiconductor/solid-state device detailsSolid-state devicesEngineeringInterconnection

The invention provides an integrated circuit protection structure and a manufacturing method thereof. The integrated circuit protection structure comprises at least one ring of annular structure, wherein the annular structure comprises a first interconnection layer, a through hole layer and a second interconnection layer, wherein the first interconnection layer comprises at least one conductive part; the through hole layer comprises at least one conductive through hole, wherein the conductive through hole is connected to the upper portion of the conductive part, and the center of the conductive through hole deviates from the center of the conductive part; and the second interconnection layer comprises at least one conductive wire, wherein the conductive wire is connected above the conductive through hole. The asymmetric design is adopted for the axial symmetric design, wherein the center of the conductive through hole is deviated from the center of the lower-layer conductive part through transverse displacement, so that the conductive through hole completely or partially avoids the part of a hole of the lower conductive part, the conductive through hole can be effectively filled, the high-quality and reliable functions of a sealing ring, a protection ring and the like are facilitated, and influence to the later process is avoided. In addition, by adopting the scheme of the invention, the additional process cost is not increased.

Owner:YANGTZE MEMORY TECH CO LTD

Lateral double diffused metal oxide semiconductor field effect transistor with potential floating field plate

ActiveCN107871778BEvenly distributedImprove lateral pressure resistanceSemiconductor devicesPhysical chemistryField-effect transistor

The invention discloses an N-type lateral double-diffused metal oxide semiconductor field effect transistor with a charge-adjustable field plate, comprising: a P-type semiconductor substrate, on which an N-type drift region and a P-type semiconductor substrate are arranged. type well, an N-type source region, a P-type contact region, and a gate oxide layer are arranged on the P-type well, and an N-type drain region and a field oxide layer are arranged on the N-type drift region, and it is characterized in that the field oxide layer There are multiple charge-adjustable field plates on the surface, and each charge-adjustable field plate is connected with a metal induction layer, and a source metal is connected to the P-type contact area and the N-type source area, and the source metal Completely cover all metal sensing layers. This structure can obtain a uniform surface lateral electric field distribution in the entire drift region of the device, has a high lateral withstand voltage capability, and can increase the doping concentration of the drift region of the device while maintaining a high breakdown voltage, thereby obtaining low conduction resistance.

Owner:UNIV OF JINAN

Semiconductor memory unit, driving method thereof and semiconductor memory

InactiveCN101826531BReduce leakage currentImprove performanceSolid-state devicesRead-only memoriesDielectric layerSilicon on insulator

The invention relates to a semiconductor memory unit, a driving method thereof and a semiconductor memory, wherein the semiconductor memory unit comprises silicon on an insulator, a first diffusion region, a second diffusion region, a grid dielectric layer, a grid electrode, a first electric charge storage region and / or a second electric charge storage region, wherein the first diffusion region and the second diffusion region are positioned in top-layer silicon and mutually separated, and the conduction types of the first diffusion region and the second diffusion region are the same; the griddielectric layer and the grid electrode are sequentially positioned on the top-layer silicon above a channel region; and the first electric charge storage region and / or the second electric charge storage region are / is respectively positioned in the grid dielectric layer and close to the part between the channel region and the first diffusion region and in the grid dielectric layer and close to the part between the channel region and the second diffusion region, and the first electric charge storage region and / or the second electric charge storage region are / is formed through electric field force. In the invention, the first electric charge storage region and / or the second electric charge storage region are / is formed in the grid dielectric layer through the electric field force to form thememory unit, and the memory unit is compatible with a traditional logic circuit forming process, thereby improving the performance of an integrated circuit and reducing the power consumption.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

High electron mobility transistor with coupling field plates

ActiveCN108847422AStrong lateral pressure resistanceUniform distribution of transverse electric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesCouplingOptoelectronics

The present invention provides a high electron mobility transistor with coupling field plates. The transistor comprises a substrate. A buffer layer is arranged on the substrate, a channel layer is arranged on the buffer layer, a source electrode, a drain electrode and a barrier layer is arranged on the channel layer, the source electrode and the drain electrode are located on both ends of the barrier layer, and the barrier layer is located between the source electrode and the drain electrode. A dielectric layer and a gate electrode are arranged on the barrier layer. The surface of dielectric layer, between the gate electrode and the drain electrode, is provided with a plurality of coupling field plates, a coupling electrode is arranged on each coupling field plate, and each coupling electrode is connected with the source electrode via the corresponding metal interconnecting wire. According to the transistor, the coupling potential of each coupling field plates is changed via the size design of the corresponding coupling electrode and the corresponding coupling field plate, so that the regulating effect of coupling field plates on transverse electric field(s) is changed, the transverse electric field distribution of device(s) is optimized, and the transverse voltage endurance capability of the device(s) is improved.

Owner:济南半一电子有限公司

Dyeing process taking active emerald blue as main material

The invention relates to a dyeing process taking active emerald blue as a main material. The dyeing process comprises the following steps that 1) to-be-dyed cloth is added into a dyeing machine, the to-be-dyed cloth is enabled to be soaked in water, and then the dyeing machine is operated; 2) dye and anhydrous sodium sulphate are separately added into the dyeing machine; and 3) alkali is added into the dyeing machine; wherein the steps satisfy the following conditions that (1) the dye comprises the active emerald blue; (2) a bath ratio of the to-be-dyed cloth to dye liquor is 1:(6 to 8), wherein the dye liquor is composed of the dye and the water, a weight of the dye is equal to or more than 1% of a weight of the to-be-dyed cloth, a dosage of the anhydrous sodium sulphate is 30 g / L to 70 g / L, and a dosage of the alkali is 15 g / L to 20 g / L; (3) after the anhydrous sodium sulphate is added, the anhydrous sodium sulphate can be uniformly distributed on the to-be-dyed cloth and in the water; and (4) after the alkali is added, the dye can be fixed on the to-be-dyed cloth. According to the process, other auxiliaries do not need to be added, dyeing defects can be effectively reduced onlyby adjusting the adding sequence and proportion of the dye, the anhydrous sodium sulphate and the alkali, the process complexity and the cost cannot be increased, even the process can be simplified, the cloth cover quality can be improved, and the dyeing effect is stable and reliable.

Owner:通亿(泉州)轻工有限公司

Advanced hyper view angle display for reducing leakage of light

InactiveCN104614894AEffective occlusionWill not cause greenish phenomenonNon-linear opticsDisplay deviceSealant

The invention provides an advanced hyper view angle display for reducing leakage of light. The advanced hyper view angle display comprises a colored optical filter glass substrate, a thin film transistor array substrate, a black matrix and a sealant, wherein the sealant is used for enabling the colored optical filter glass substrate to be adhered to the thin film transistor array substrate; the black matrix is arranged on the colored optical filter glass substrate, and extends to a cutting line of the colored optical filter glass substrate at least. Compared with the prior art, the black matrix of the advanced hyper view angle display provided by the invention extends to the cutting line of the colored optical filter glass substrate, so that light projected by a backlight on the lower side can be shielded more effectively, and the leakage of light is reduced. In addition, the black matrix is cut off because of being provided with an opening part in the path, which avoids the phenomenon that a black screen with conductivity is greenish. Moreover, an additive special process are not needed, so that the process cost is not increased.

Owner:AU OPTRONICS CORP

Antifuse structure and method of forming same

ActiveCN104103624BLower programming voltageNo increase in process costSemiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

An anti-fuse structure and a method for forming the same. The anti-fuse structure includes: a semiconductor substrate including an anti-fuse area and an interconnection area; a shallow trench isolation structure located inside the semiconductor substrate and isolating the anti-fuse area into at least one active area; a gate oxide located on an entire surface of the active area, the thickness of a gate oxide on an edge position of the active area is smaller than that of a gate oxide in a middle position; a gate electrode located on a surface of the gate oxide and a surface of part of the shallow trench isolation structure; and a first electrode located on a surface of the interconnection area of the semiconductor substrate, the first electrode being electrically connected with the active area. Since a thinner gate oxide is formed on an edge part of the whole active area, the area of the thinner gate oxide becomes larger, and thus a programming voltage for programming of gate oxide anti-fuse is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A method for obtaining ultra-fine pearlite of low-carbon and low-alloy black skin forged steel shaft

ActiveCN106834650BImprove mechanical propertiesHigh yield strengthFurnace typesHeat treatment furnacesAlloyPearlite

The invention relates to a method for obtaining a low-carbon low-alloy black skin forged-steel shaft superfine pearlite. The method comprises the steps that a decarburized layer on the surface of a low-carbon low-alloy black skin forged-steel shaft is utilized as a protective layer, the high-temperature black skin forged-steel shaft and cooling liquid perform transient heat exchange, the cooling speed is reduced through the protective layer, and accordingly a superfine pearlite structure is obtained. The method comprises the following steps that (a) the black skin forged-steel shaft is put in a heat treatment furnace and is heated to reach 30-50 DEG C above critical temperature, and heat preservation is performed for set time; (b) the shaft is discharged out of the furnace and precooled, wherein precooling is performed for set time; (c) the high-temperature black skin forged-steel shaft is put in the cooling liquid for transient cooling, and accordingly the superfine pearlite structure is obtained. By adopting the obtained superfine pearlite structure, the low-carbon low-alloy black skin forged-steel shaft can have good mechanical property, and especially the yield strength can be improved by 25-35% while the process cost is not increased.

Owner:ZHONGJUXIN OCEAN ENG EQUIP CO LTD