Patents

Literature

34results about How to "Will not increase the difficulty of the process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

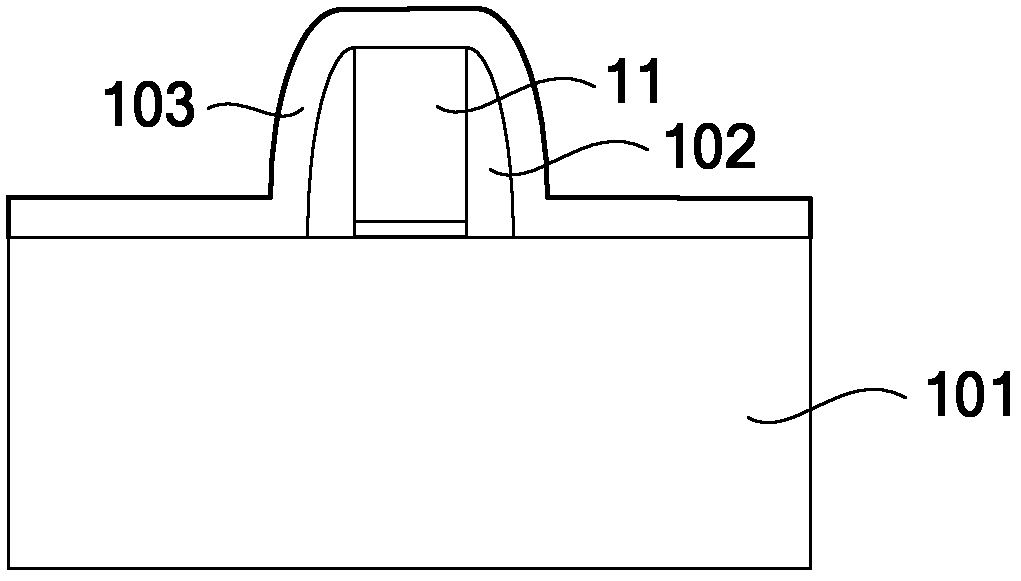

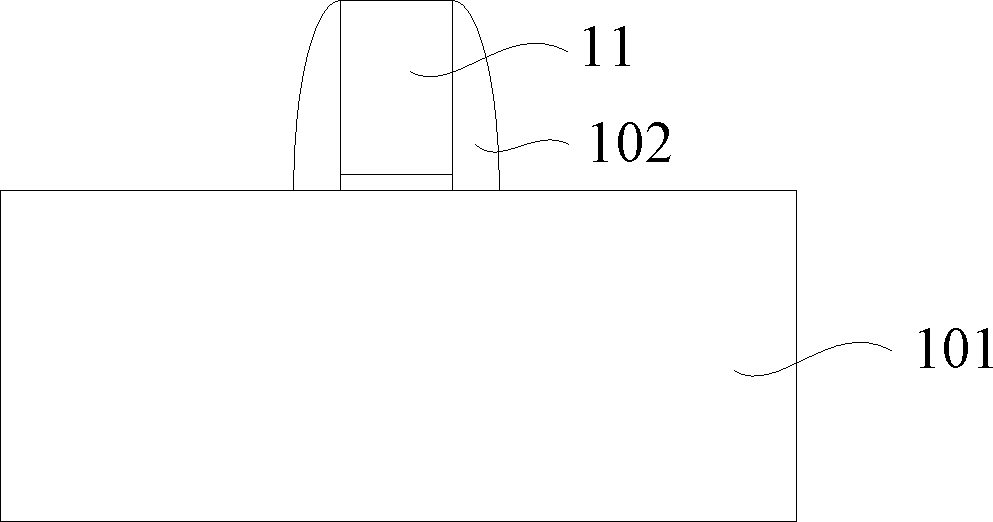

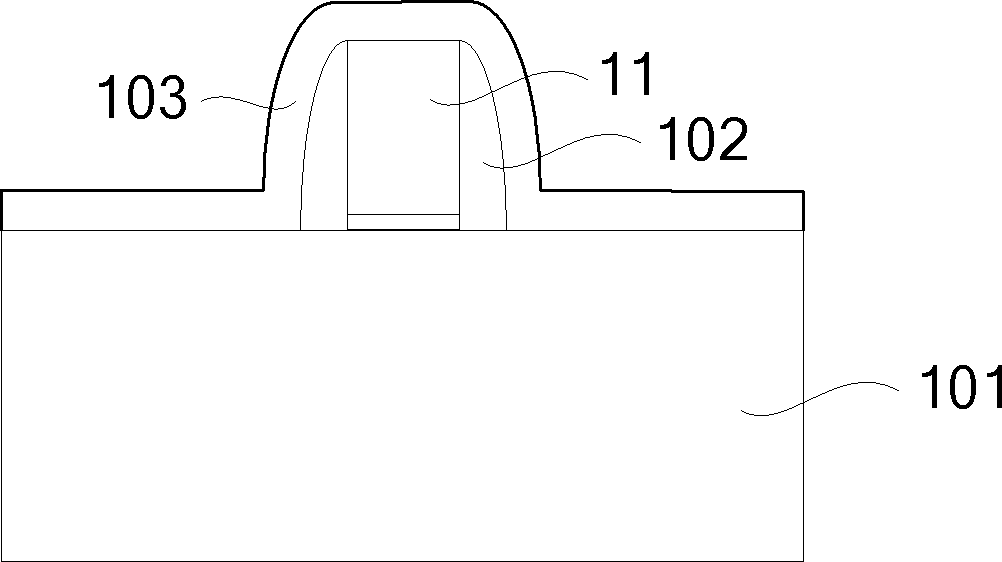

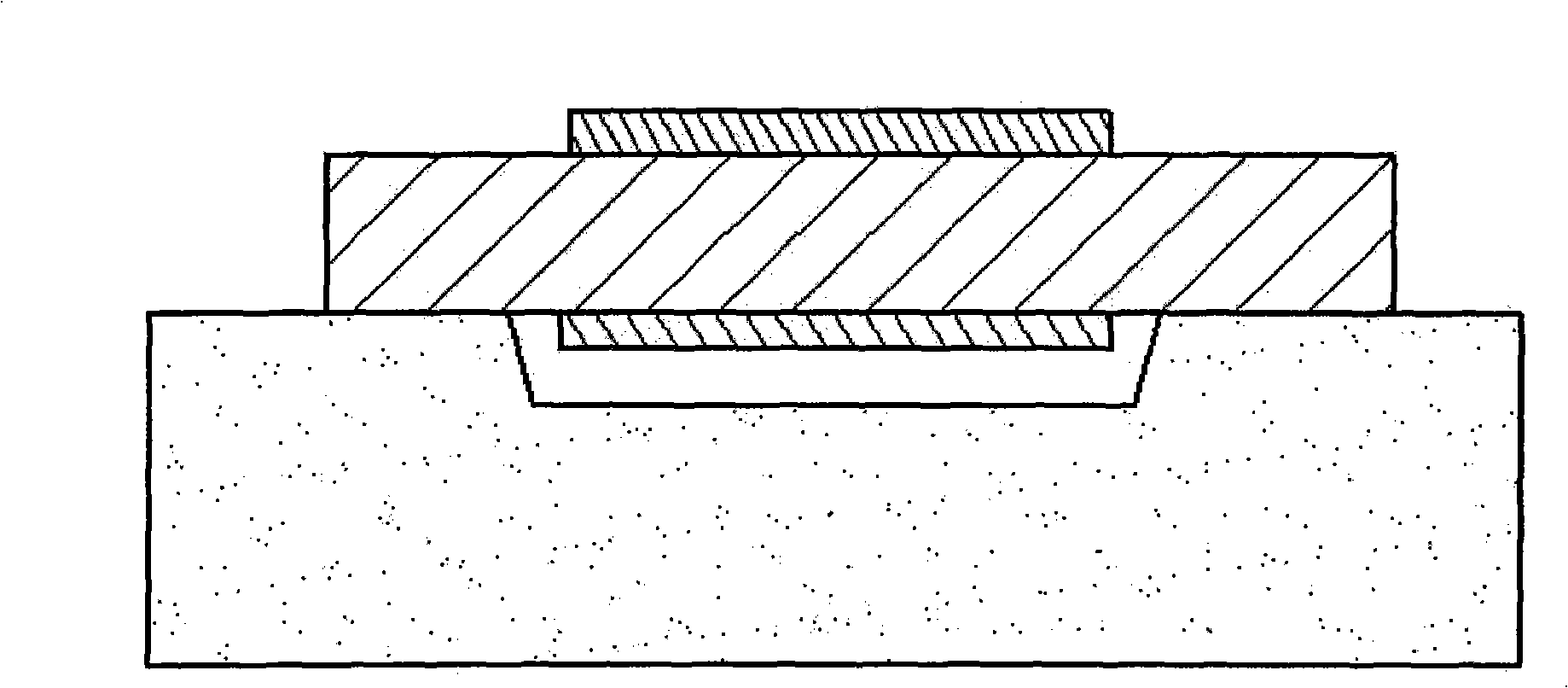

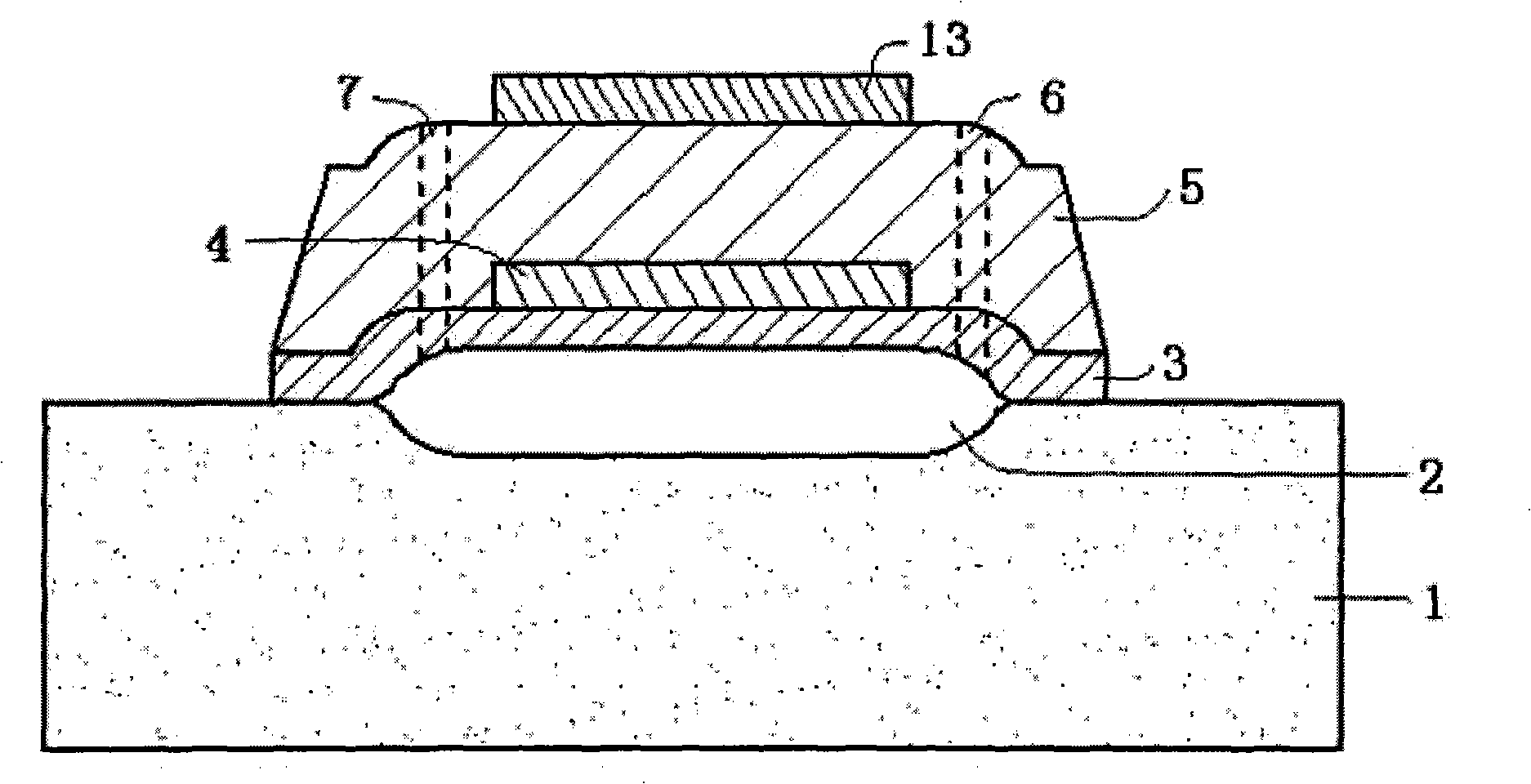

Film bulk acoustic wave resonator and preparation method thereof

InactiveCN101465628AHigh application frequencyReduce the requirements of the manufacturing process for equipmentImpedence networksThin-film bulk acoustic resonatorBulk acoustic wave

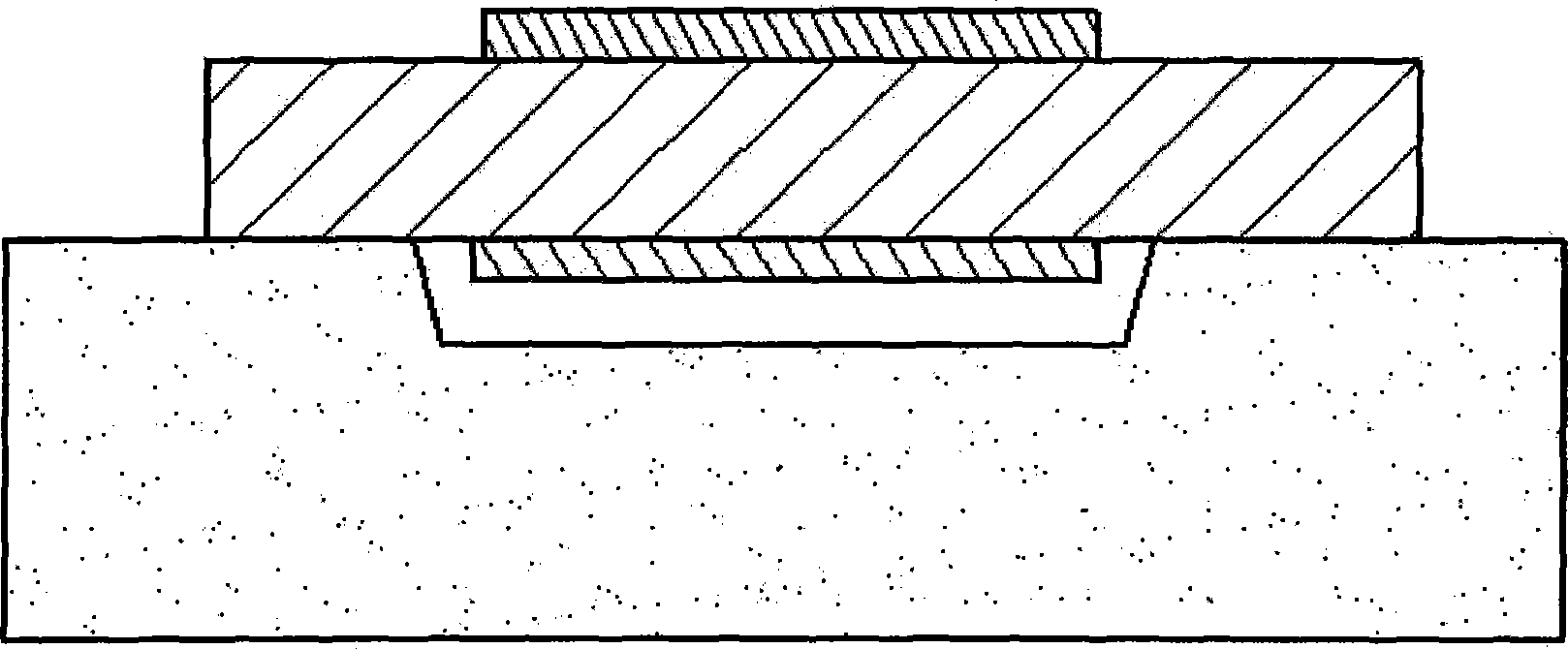

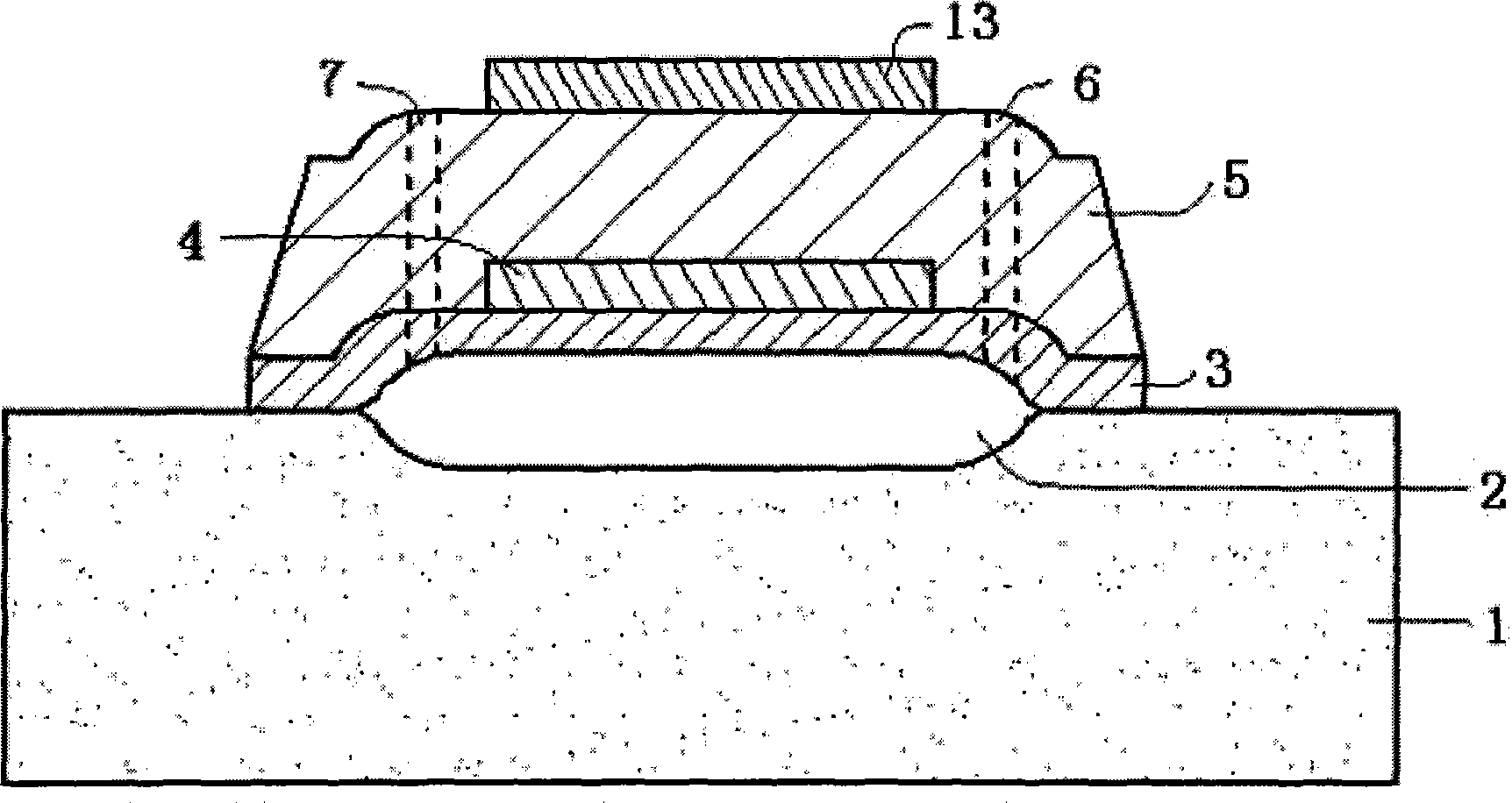

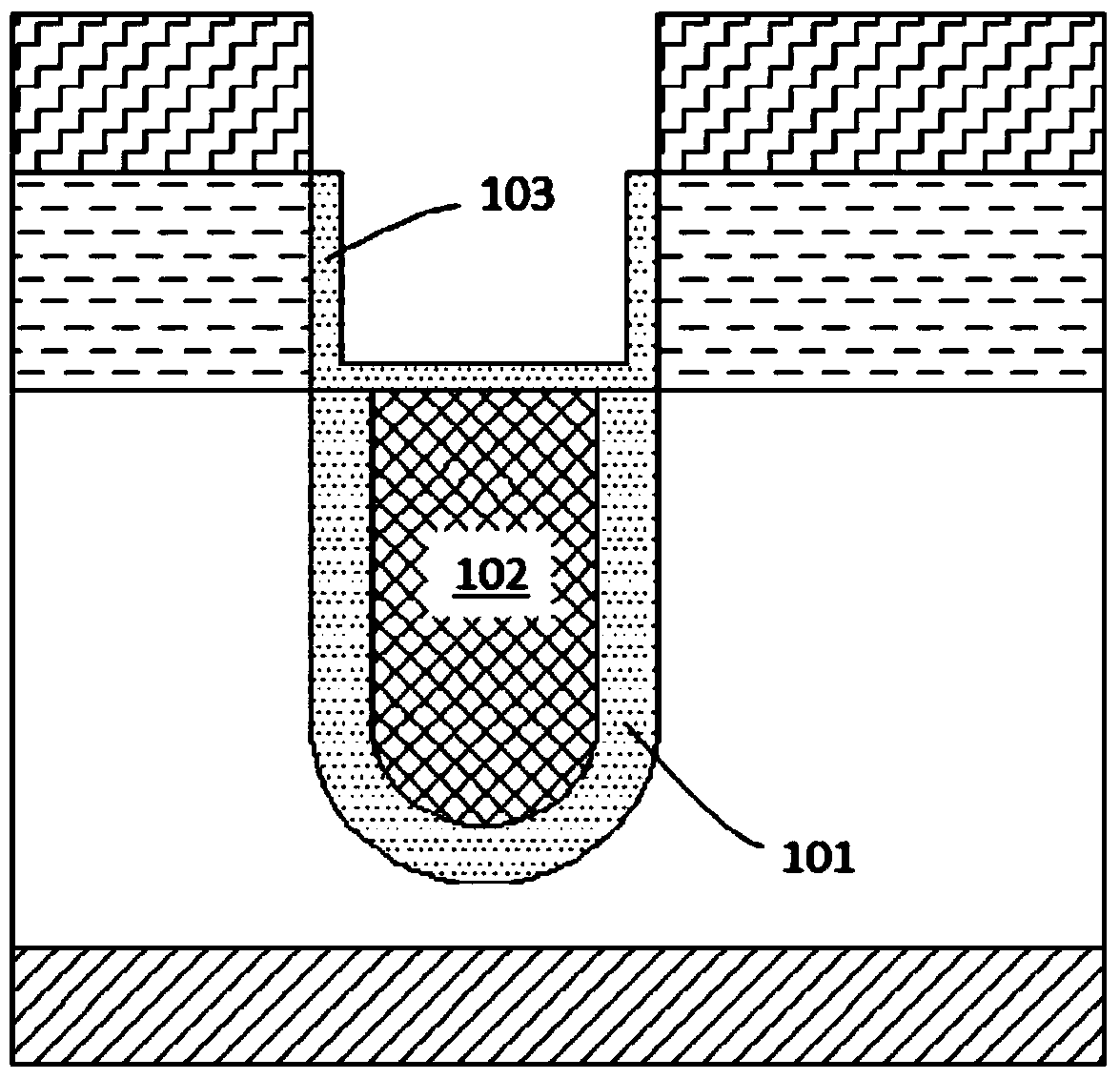

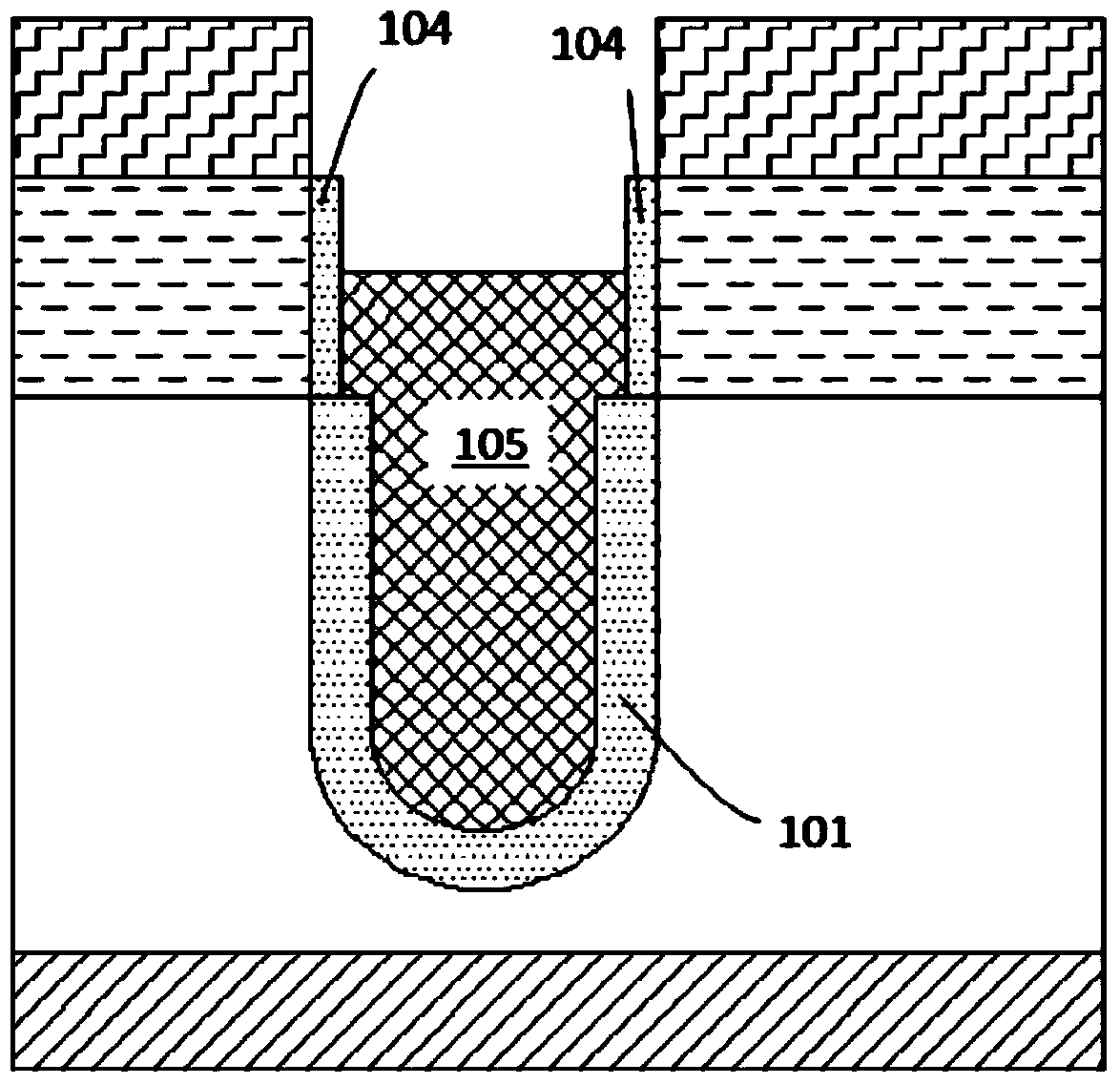

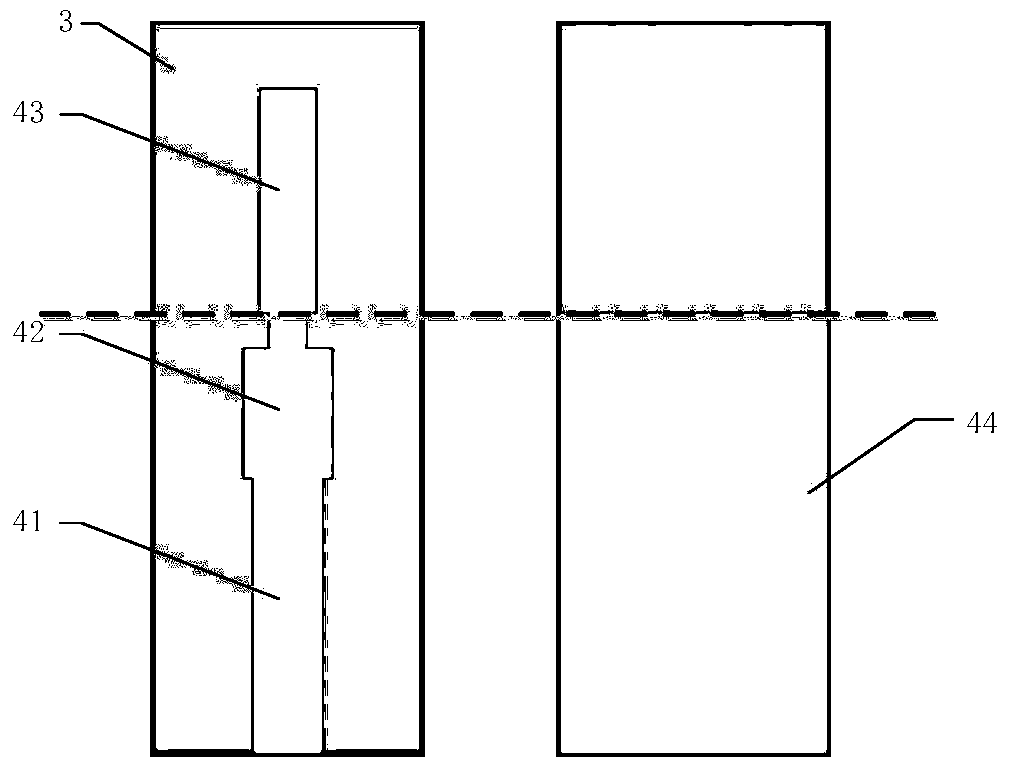

The invention discloses a thin film bulk acoustic wave resonator which comprises a substrate, a buffer layer, a piezoelectric layer and electrodes, and is characterized in that 1. A smooth concave groove and the buffer layer are arranged on the upper end surface of the substrate; the buffer layer crosses the concave groove and forms an air gap provided with a smooth upper convex edge with the substrate, and completely covers the air gap; the height of the lower top surface of the air gap is less than that of the substrate, and the air gap has flat surface and even change edge; 2. The edge of the buffer layer, which is contacted with the air gap and is close to the substrate is in smooth and outer-convex shape; the piezoelectric layer is arranged on the buffer layer; the electrodes include a bottom electrode and a top electrode; the bottom electrode is arranged in the piezoelectric layer on the buffer layer; the top electrode is arranged on the piezoelectric layer. The thin film bulk acoustic wave resonator has ingenious structure; a FBAR with stable structure and low loss can be fabricated on the substrate through the method, and the CMP process is avoided, so the thin film bulk acoustic wave resonator can be integrated into a CMOS chip conveniently.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

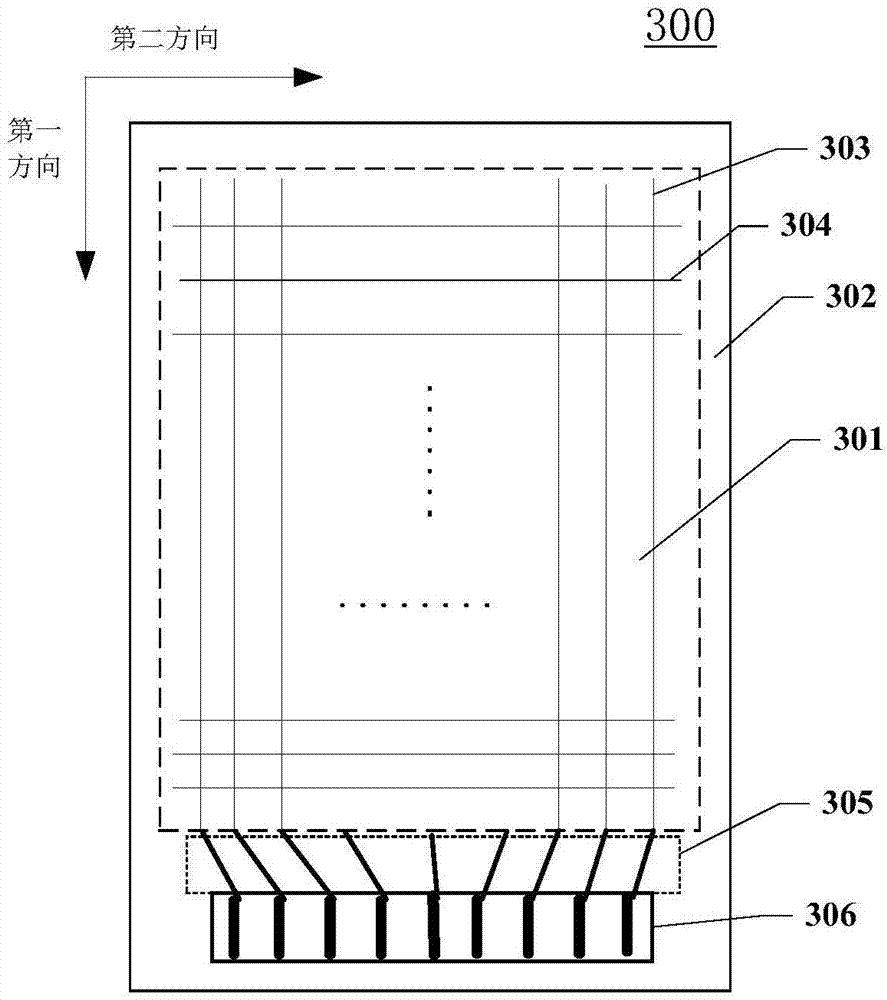

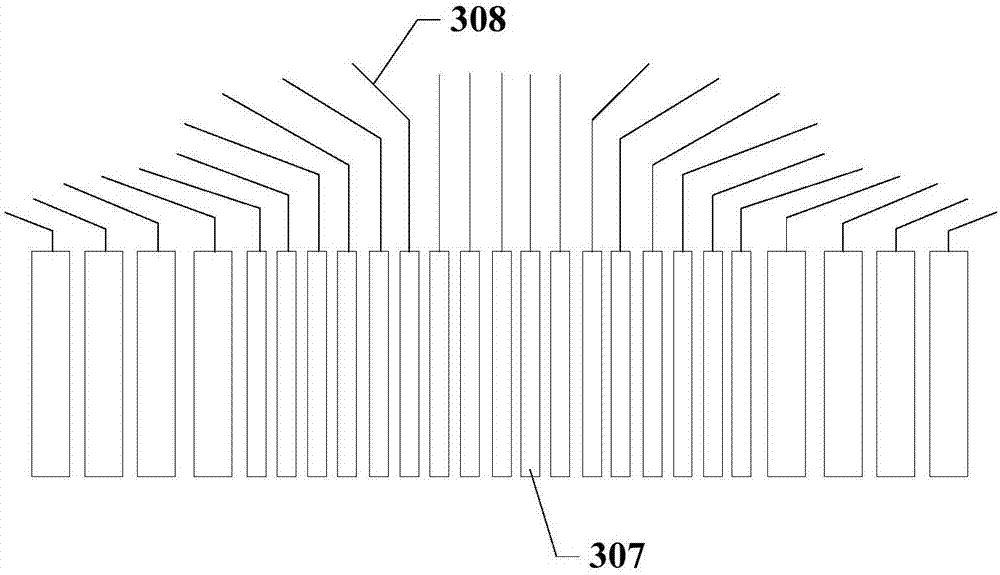

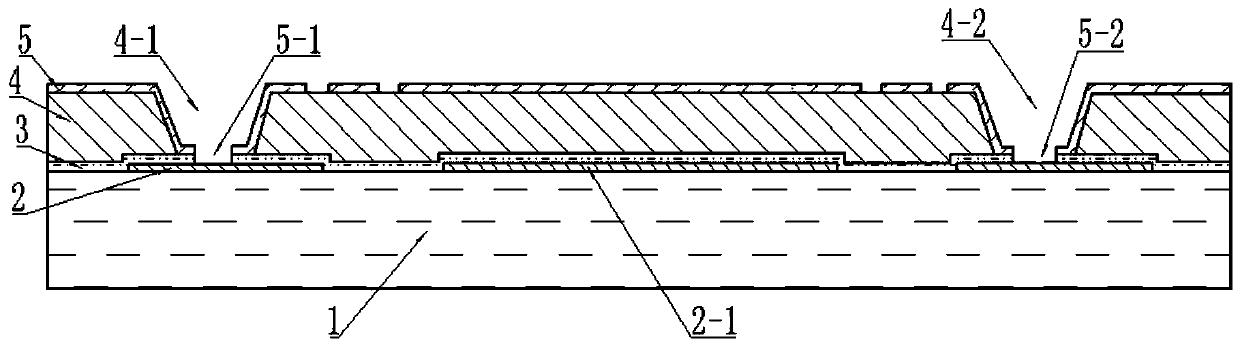

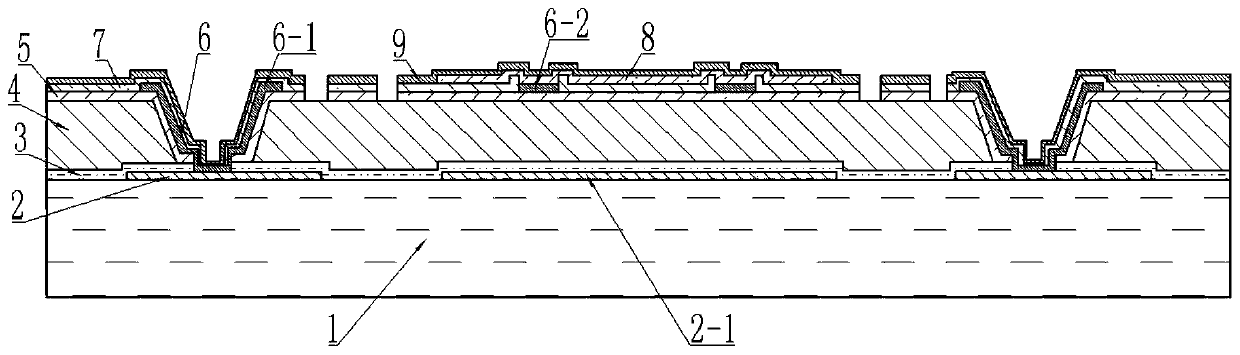

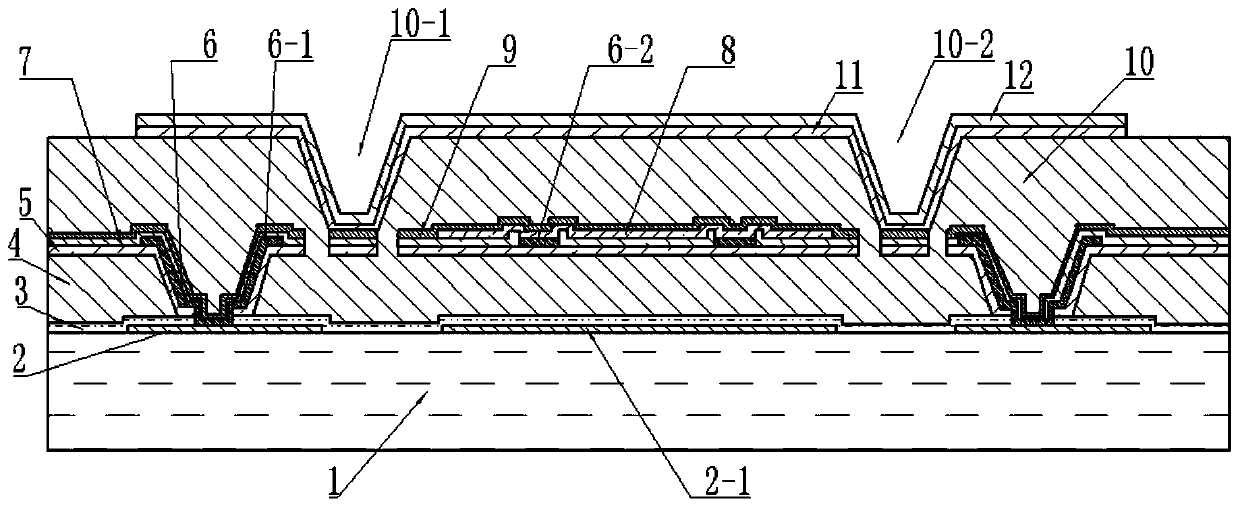

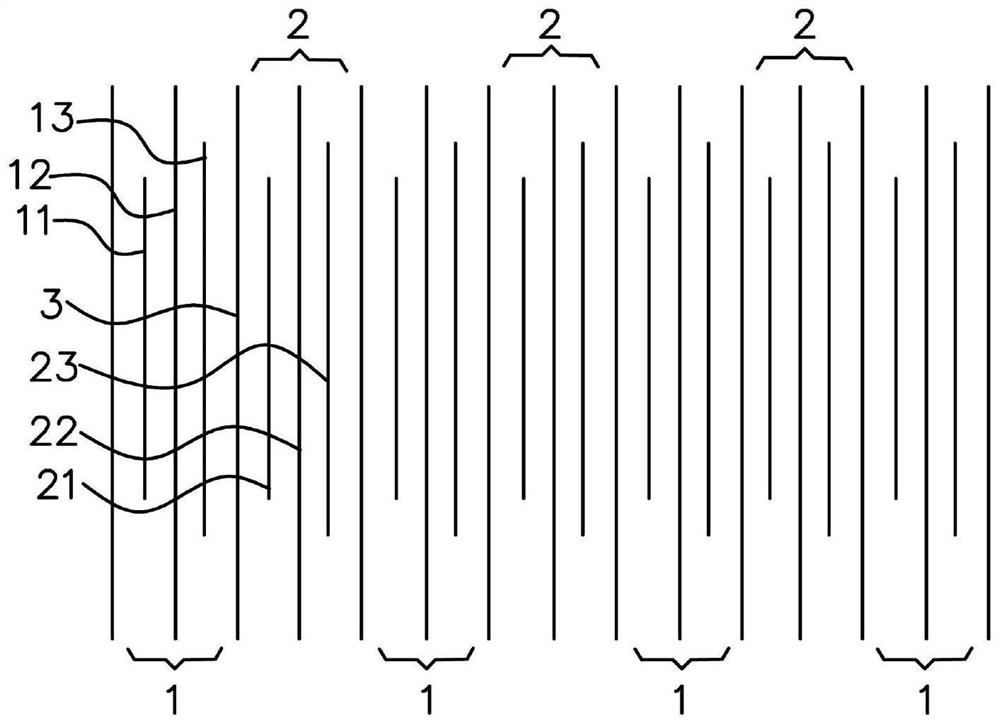

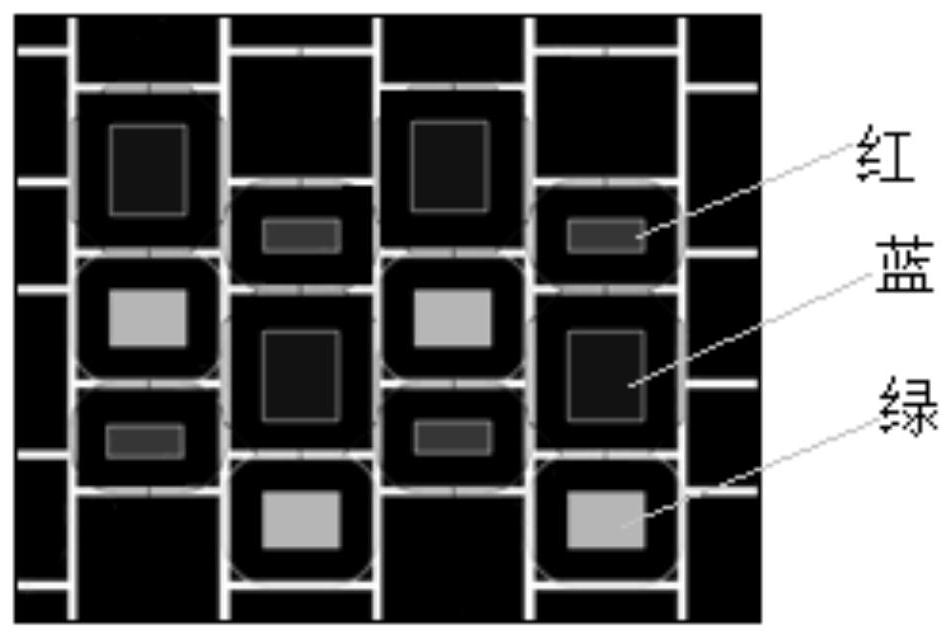

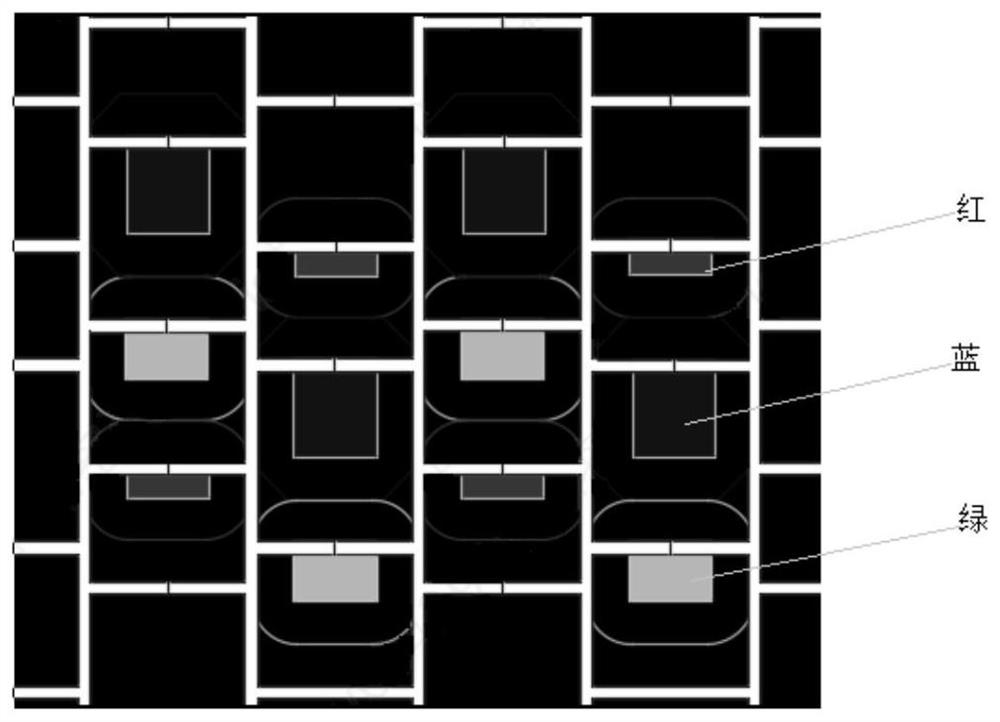

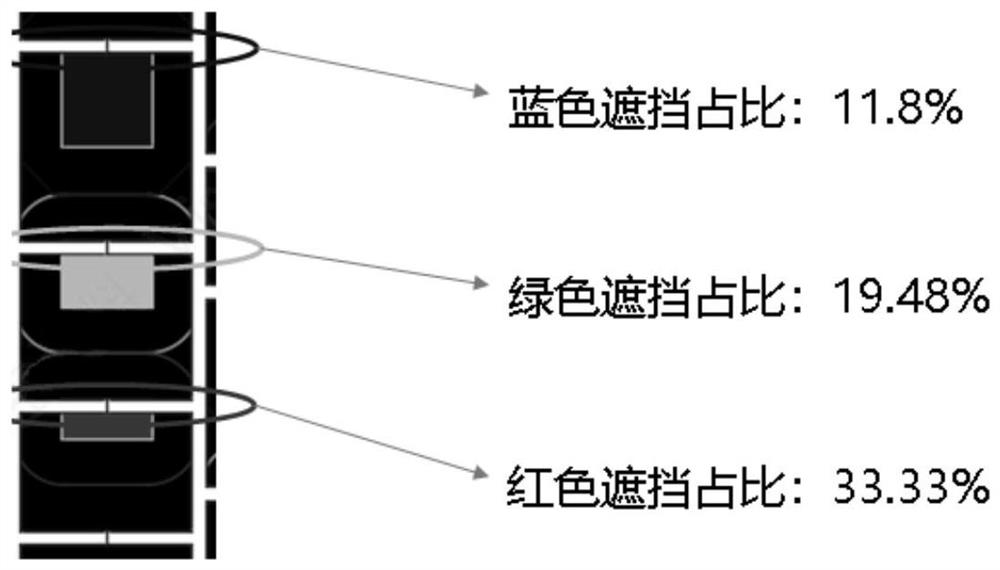

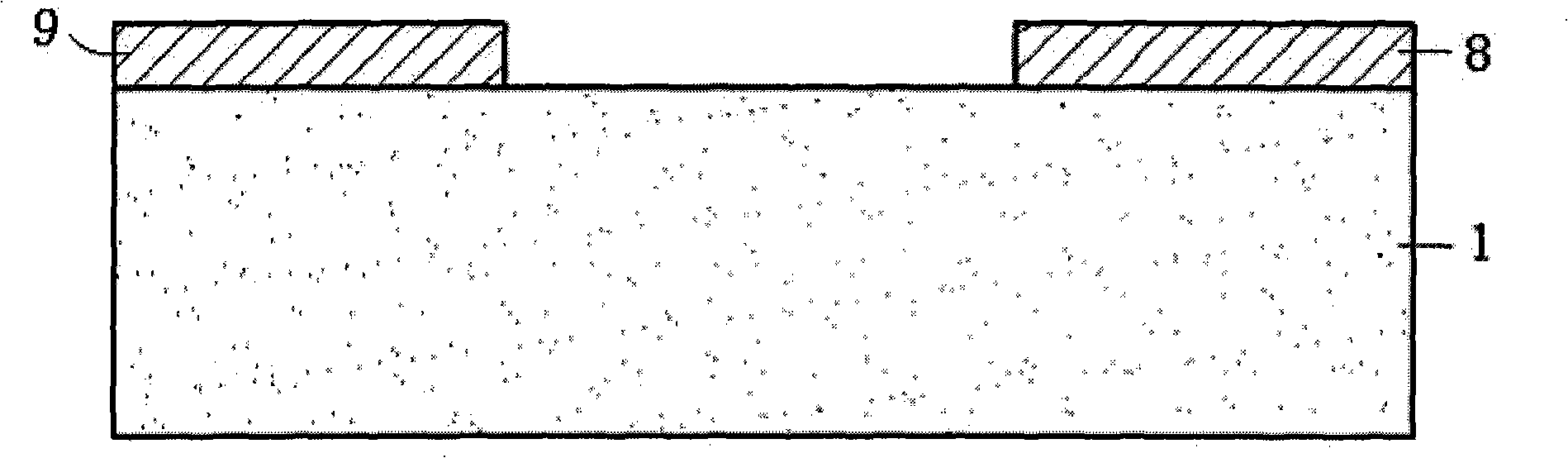

Display panel and display device

InactiveCN107300793AIncrease the proportionWill not increase the difficulty of the processStatic indicating devicesNon-linear opticsElectricityDisplay device

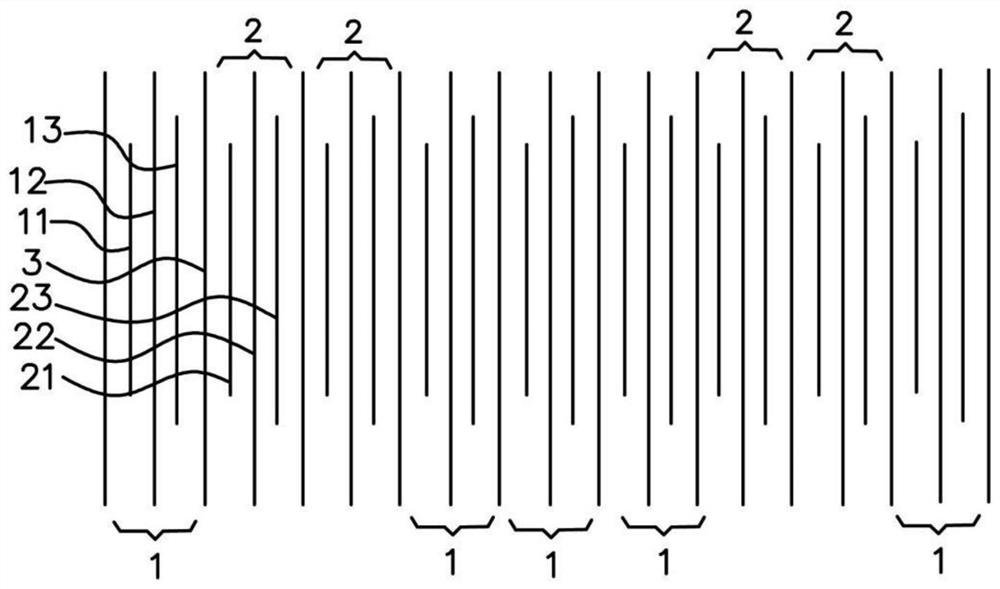

The invention discloses a display panel and a display device. The display panel comprises a first substrate, a binding area and a fan-out wiring area; the first substrate comprises a display area and a non-display area around the display area, and the display area comprises a plurality of signal leads; the binding area comprises a first conductive gasket group and a second conductive gasket group; the first conductive gasket group comprises a plurality of first conductive gaskets, and the second conductive gasket group comprises a plurality of second conductive gaskets; the fan-out wiring area comprises a plurality of first fan-out wires and a plurality of second fan-out wires; partial signal leads are electrically connected with the first conductive gaskets through the first fan-out wires, and partial signal leads are electrically connected with the second conductive gaskets through the second fan-out wires; each second fan-out wiring comprises a first wire segment and a second wire segment connected with the first wire segment, and the first wire segments and the second wire segments are located on different film layers; at least partial overlapping areas exist between the orthographic projections of the second conductive gaskets and the orthographic projections of the first wire segments which are correspondingly and electrically connected with the second conductive gaskets, wherein the orthographic projections are all on the plane where the first substrate is located. Thus, the implementation of narrow bezel design is facilitated.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

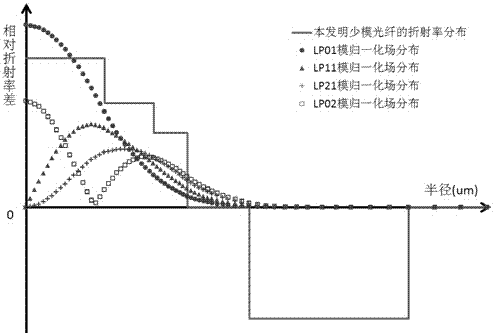

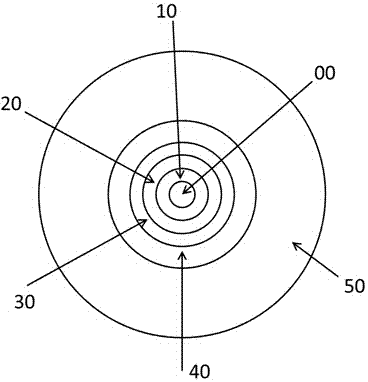

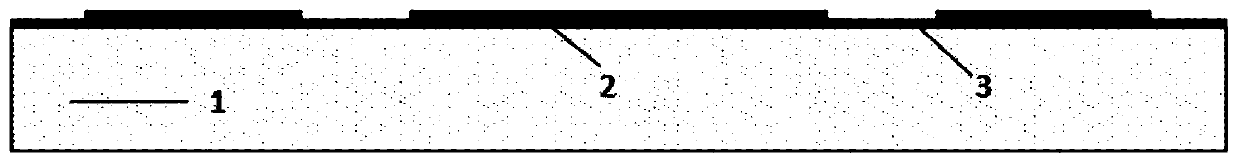

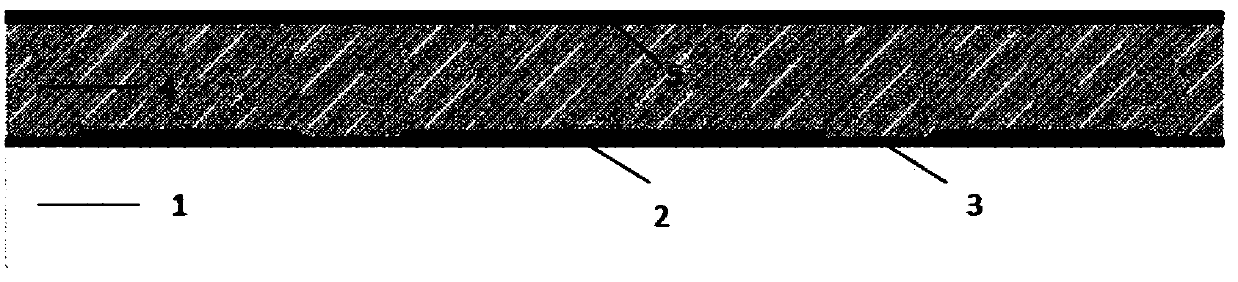

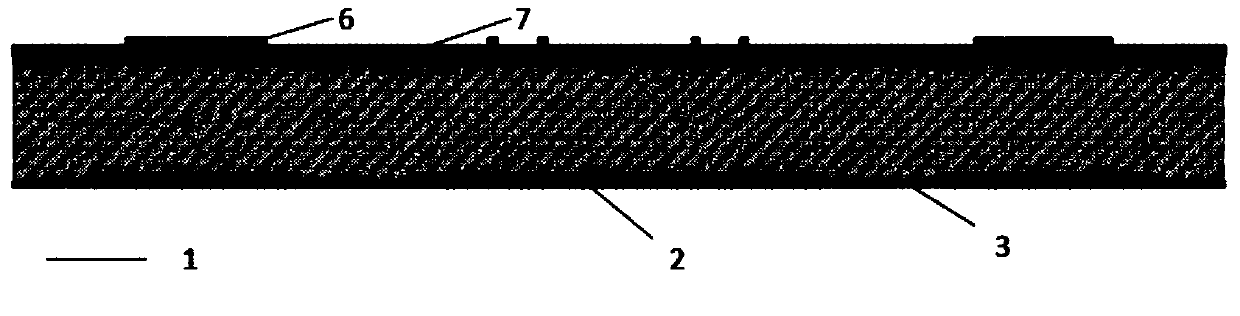

Low-attenuation and few-mode fiber

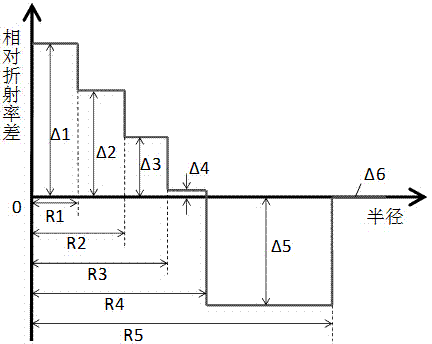

ActiveCN104714273ALow DGD valueLow refractive indexOptical fibre with multilayer core/claddingUltrasound attenuationFew mode fiber

The invention relates to a low-attenuation and few-mode fiber. A core layer has three layers and comprises three claddings from inside to outside; the relative refractive index difference delta 1 of a first core layer is 0.34%-0.45%, R1 ranges from 4.5 mu m to 7.5 mu m, the relative refractive index difference delta 2 of a second core layer is 0.20%-0.29%, R2ranges from8 mu m to 10 mu m, the relative refractive index difference delta 3 of a third core layer is 0.15%-0.24%, R3 ranges from 10 mu m to 13 mu m, the relative refractive index difference delta 4 of a first cladding is minus 0.02%-0.02%, R4 ranges from14 mu m to 18 mu m, the second cladding is a concave cladding, the relative refractive index difference delta 5 of the second cladding is minus 0.8%-minus 0.4%, R5 ranges from19 mu m to 31 mu m, and a third cladding is a pure quartz glass layer. According to the low-attenuation and few-mode fiber, four stable transmission modes are supported within 1550 nm, small DGD is provided, the process is simple, and the manufacturing is easy; at the same time, the low-attenuation and few-mode fiber has low attenuation and better bending resistance.

Owner:SHANTOU HIGH TECH ZONE AOXING OPTICAL COMM EQUIP

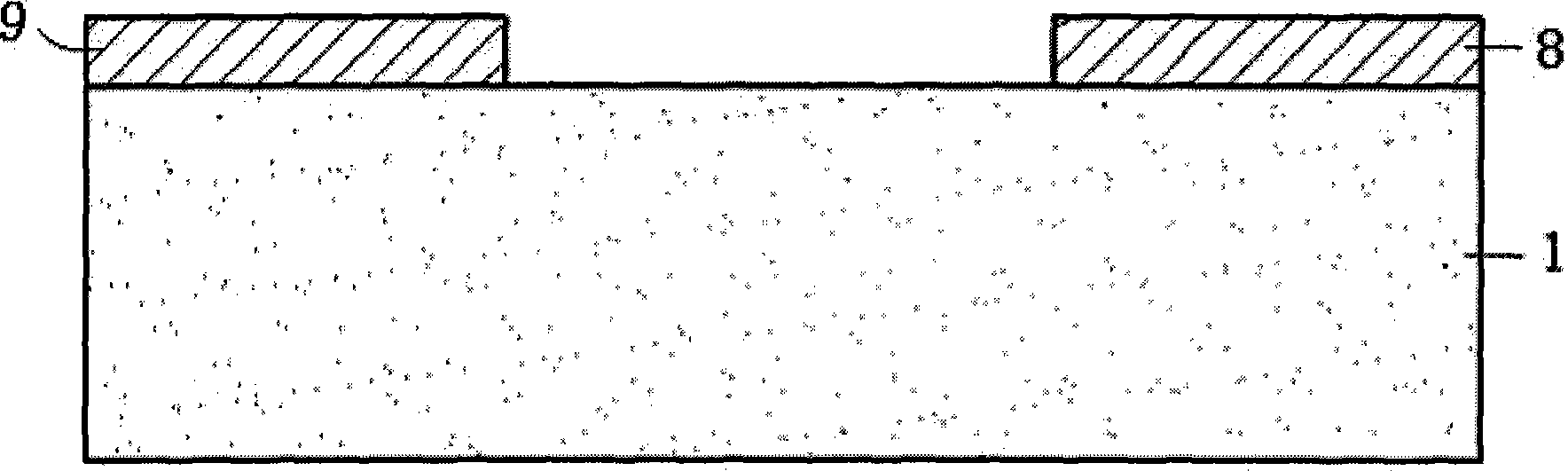

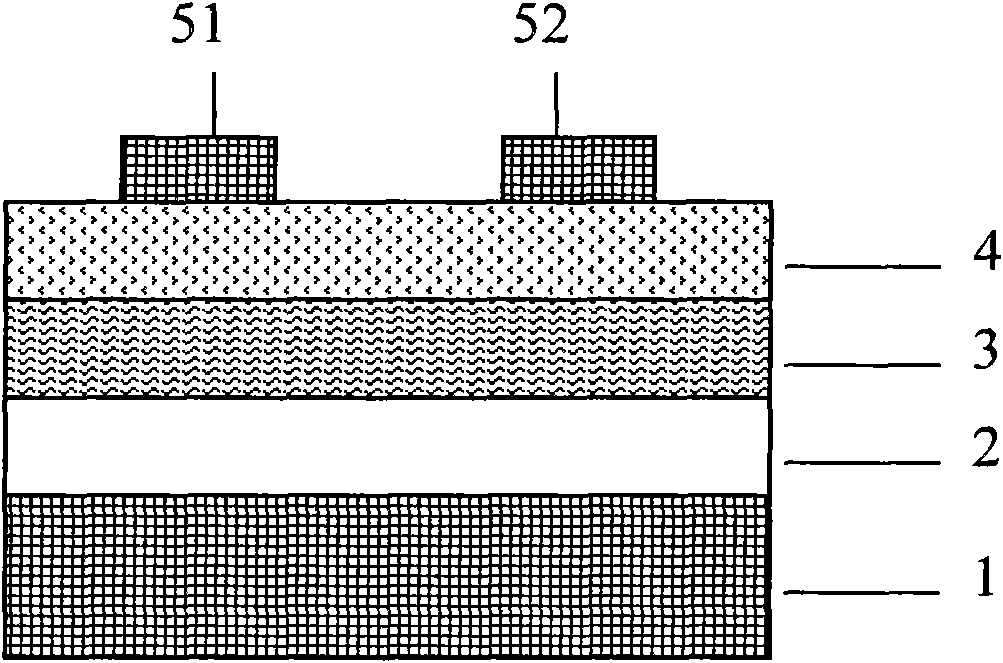

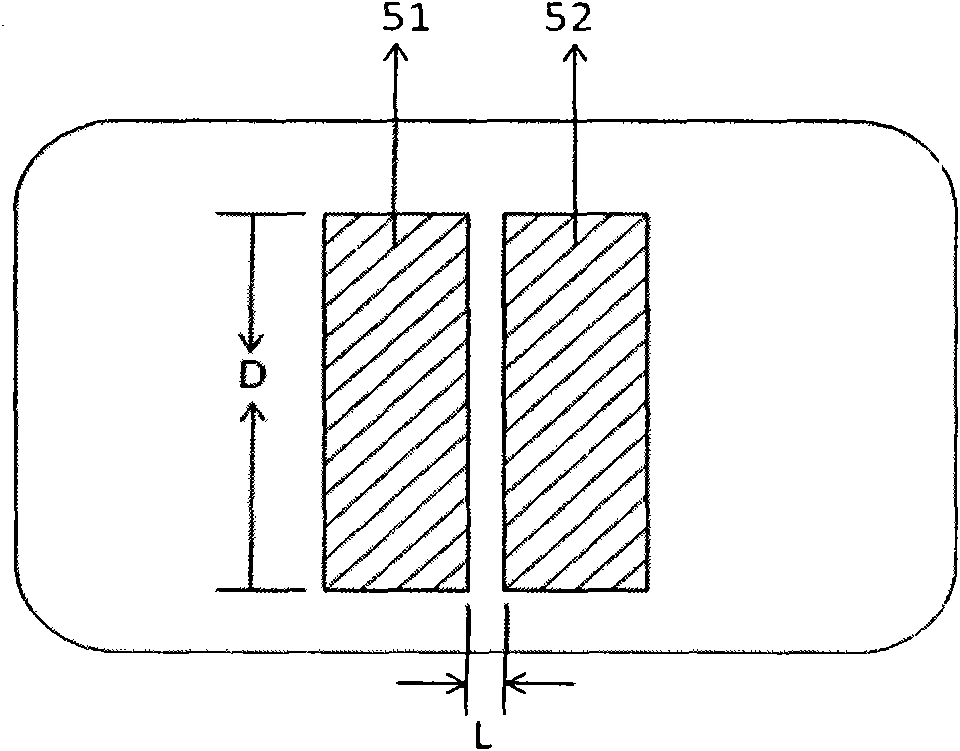

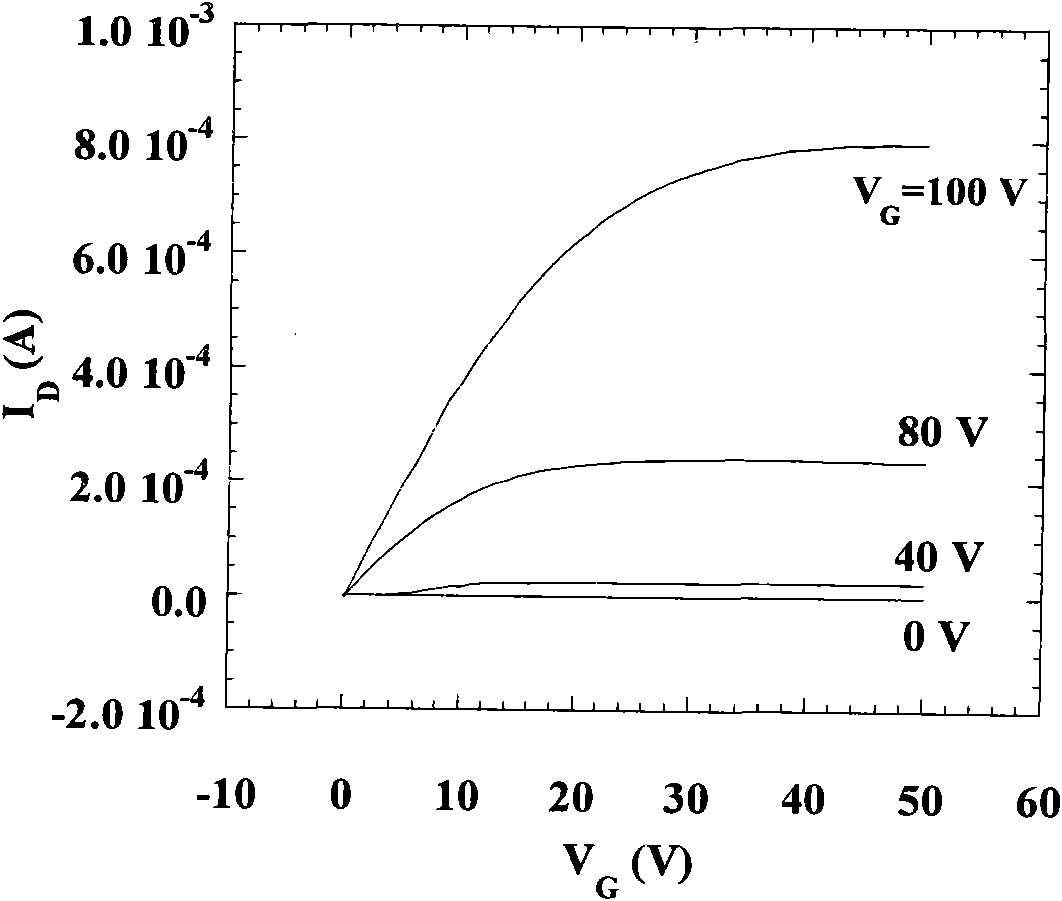

Metal oxide thin film transistor and preparation method thereof

InactiveCN101872787AReduce off-state currentImprove mobilityTransistorSemiconductor/solid-state device manufacturingElectrical stabilityOhmic contact

The invention discloses a metal oxide thin film transistor and a preparation method thereof. The metal oxide thin film transistor is composed of a grid electrode, an insulating layer, a transition layer, a semiconductor layer, a drain electrode and a source electrode, wherein the grid electrode, the insulating layer, the transition layer and the semiconductor layer are sequentially connected with each other from bottom to top; the drain electrode and the source electrode are positioned on the semiconductor layer; the transition layer and the semiconductor layer are prepared by means of sputtering with the same target being adopted in the process of sputtering, the material of the target is (In2O3)x(Ga2O3)y(ZnO)z, wherein x, y and z are not less than 0 but not more than 1, and x+y+z is equal to 1; and the transition layer and the insulating layer include excellent contact property so as to effectively lower carrier trap density between contact interfaces of the insulating layer and the transition layer as well as enhance output current of the transistor and improve electrical stability. The source electrode and the drain electrode can form outstanding ohmic contact with the semiconductor layer, thereby effectively reducing off-state current, raising on / off ratio of current and improving electronic carrier mobility.

Owner:SOUTH CHINA UNIV OF TECH

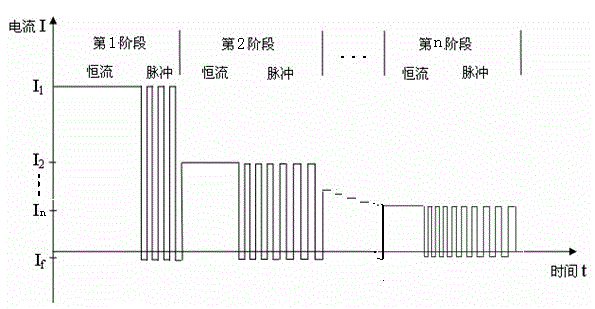

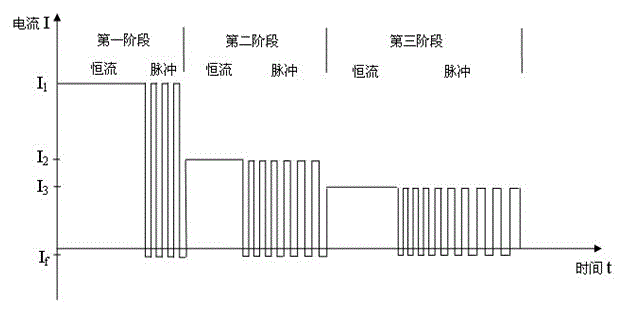

Grading constant current charging method with voltage-controlled pulse

InactiveCN102945987AShorten charging timeReduce outgassingSecondary cells charging/dischargingCharge currentLarge capacity

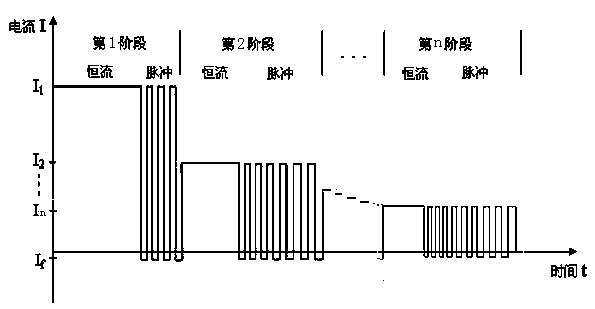

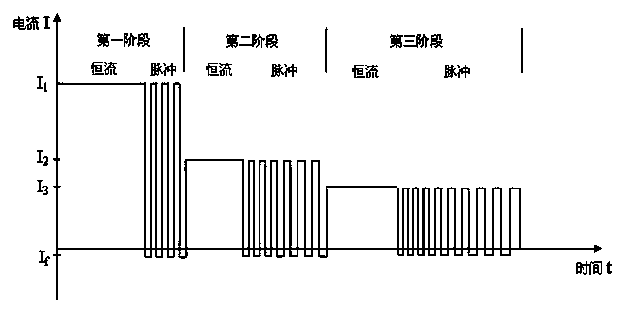

The invention relates to a grading constant current charging method with voltage-controlled pulse. A section of a pulse charging and discharging process with the depolarization function is attached when storage battery voltage rises to a gassing point at each grade of constant current charging stage. Charging current amplitude of the pulse charging and discharging process is equal to constant current amplitude at the same grade, and discharging current amplitude value is 0.5-1% of first constant current amplitude. A pulsating voltage average value of a storage battery in the pulse charging and discharging process is fixed and controlled to be a litter lower than the gassing point. Compared with a traditional grading constant current charging method used by a high-capacity lead-acid storage battery at present, the grading constant current charging method has the advantages of being short in charging time, high in charging efficiency, small in battery gassing amount, small in battery damage and the like.

Owner:中国船舶重工集团公司第七〇一研究所 +1

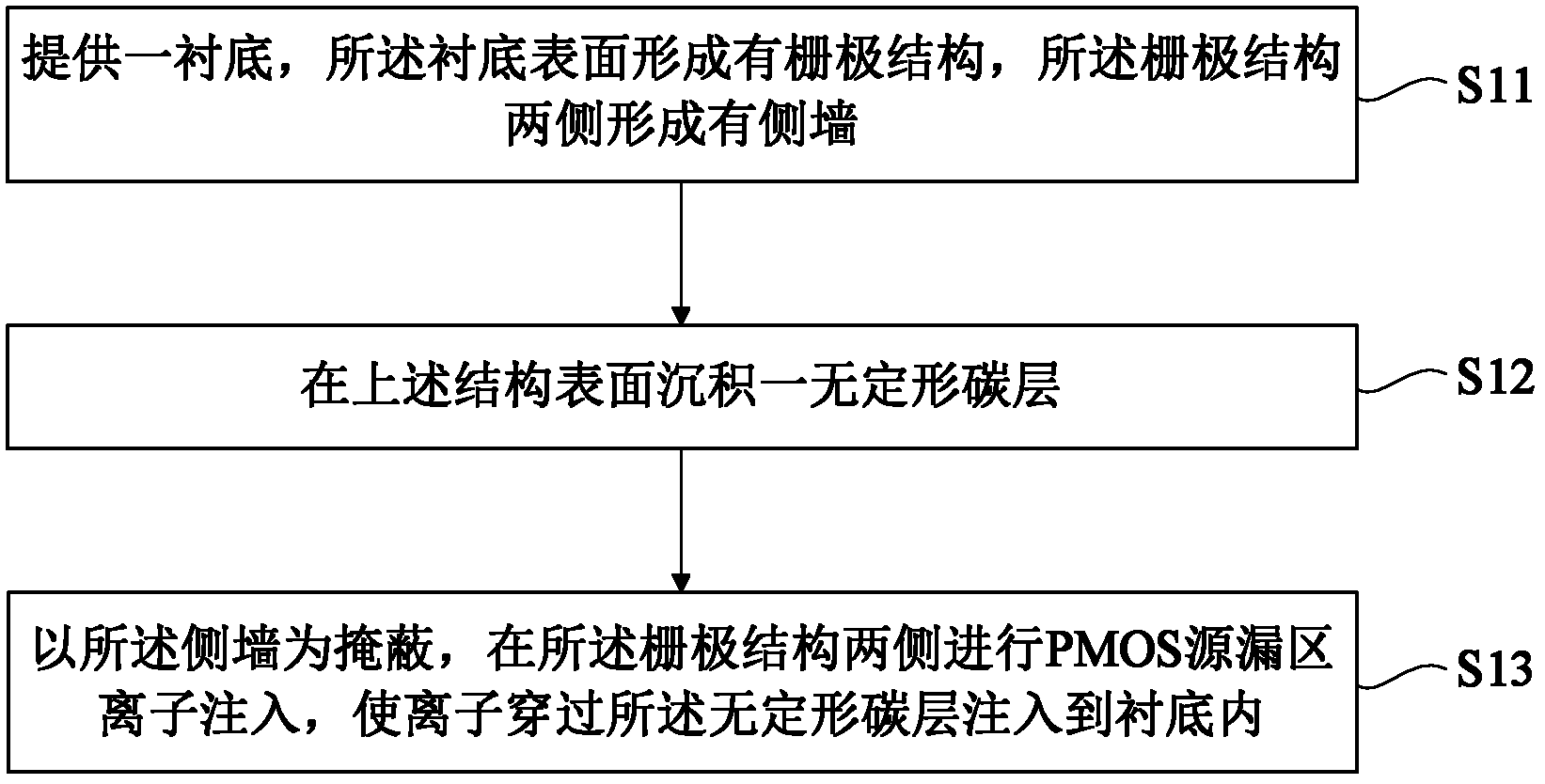

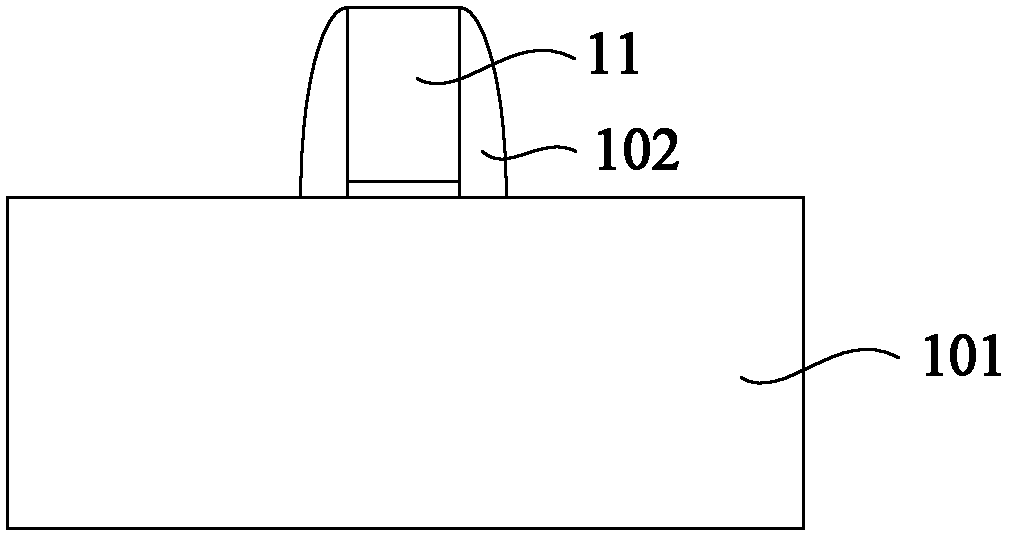

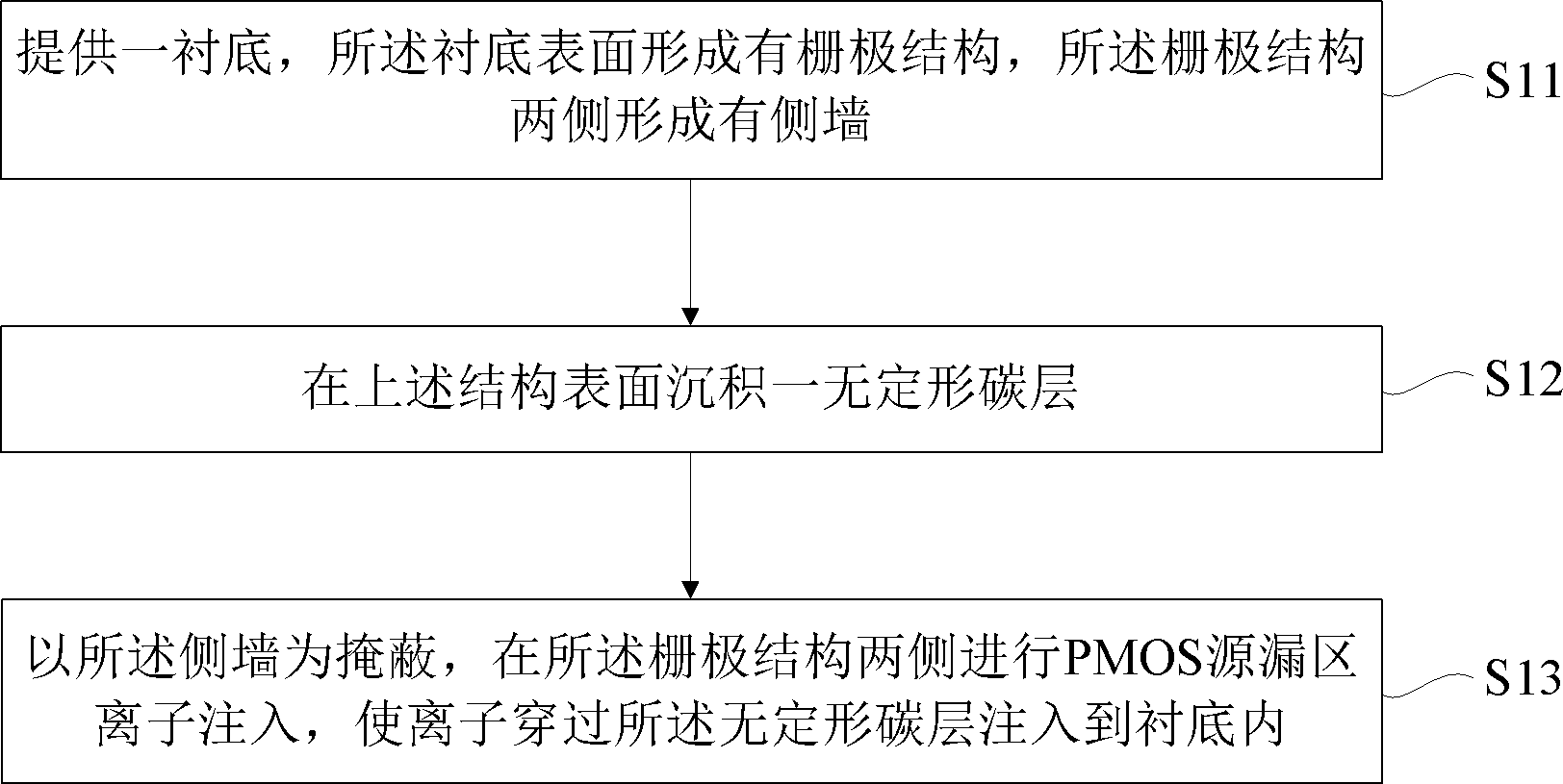

PMOS (p-channel metal-oxide-semiconductor field-effect transistor) source/drain region ion implantation method and corresponding device manufacturing method

ActiveCN102437028AReduce processing difficultyShort rangeSemiconductor/solid-state device manufacturingHigh dosesField-effect transistor

The invention discloses a PMOS (p-channel metal-oxide-semiconductor field-effect transistor) source / drain region ion implantation method and a corresponding device manufacturing method. Since an amorphous carbon layer can be completely removed without causing silicon sinking, when the amorphous carbon layer is used as a pad layer for PMOS source / drain region ion implantation, the range of implanted impurities in the silicon substrate can be reduced on the premise of basically not changing the implanted impurity distribution, thereby obtaining an ultrashallow junction which is more shallow than that obtained by a conventional method; or the implanted energy is increased on the premise of keeping the depth of the ultrashallow junction unchanged, thereby relieving the demands of technique for high-dose low-energy ion implantation to some extent, and lowering the technical difficulty of PMOS source / drain region ion implantation. The PMOS source / drain region ion implantation method and the corresponding device manufacturing method provided by the invention can be used for improving the ion implantation technique of the ultrashallow junction in the PMOS source / drain region, and lowering the technical difficulty.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

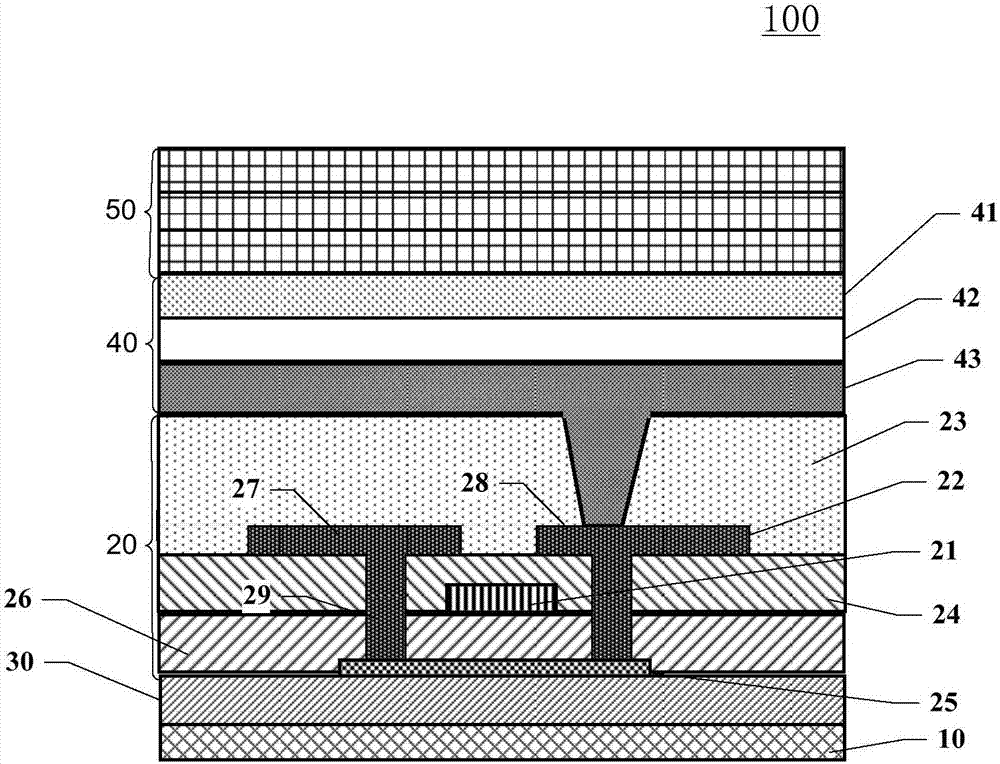

Metasurface-based uncooled infrared imaging sensor

ActiveCN110160656AWill not increase the difficulty of the processSimple processRadiation pyrometryHeat sensitiveReflective layer

The invention relates to a metasurface-based uncooled infrared imaging sensor, which comprises a double-layer uncooled infrared detector. The double-layer uncooled infrared detector comprises a semiconductor substrate and a detector body; the detector body comprises a first suspended structure layer and a second suspended structure layer; the first suspended structure layer comprises a metal reflective layer, an insulating dielectric layer, a metal electrode layer, an electrode protective layer, a first supporting layer, a heat sensitive protective layer and a heat sensitive layer; the secondsuspended structure layer comprises a metamaterial support layer and a metamaterial support protective layer; a metamaterial structure is arranged on the metamaterial support protective layer; and themetamaterial structure adopts NiCr or / and Al, and the thickness is between 12 to 30 nm. The preparation process is simple and is compatible with a CMOS process, and functions of multi-color detection, wide-band detection, narrow-spectrum detection and the like can be realized.

Owner:YANTAI RAYTRON TECH

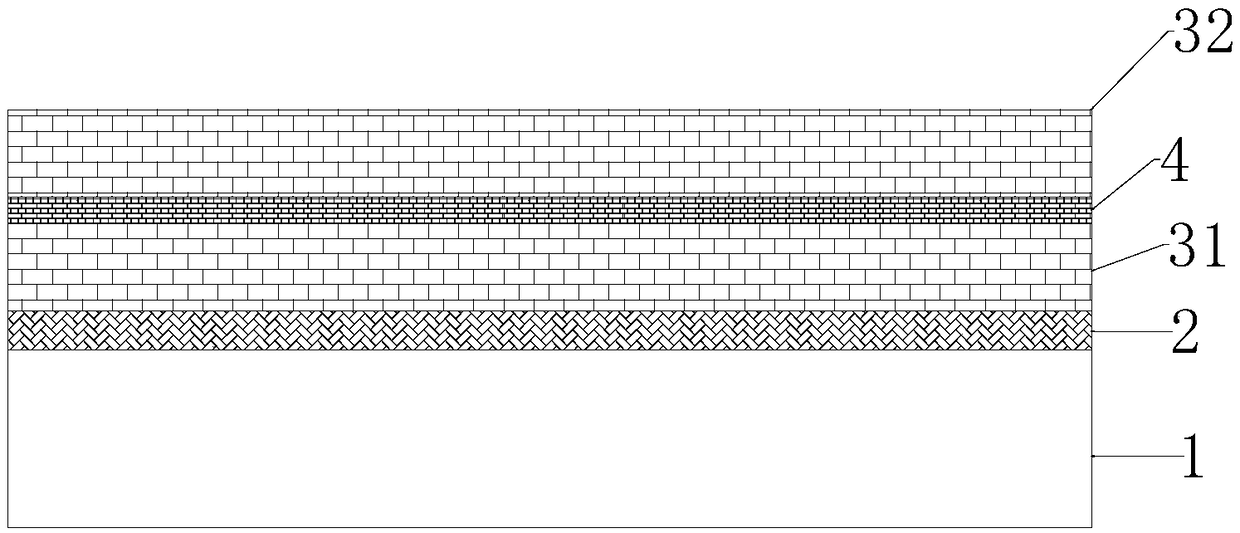

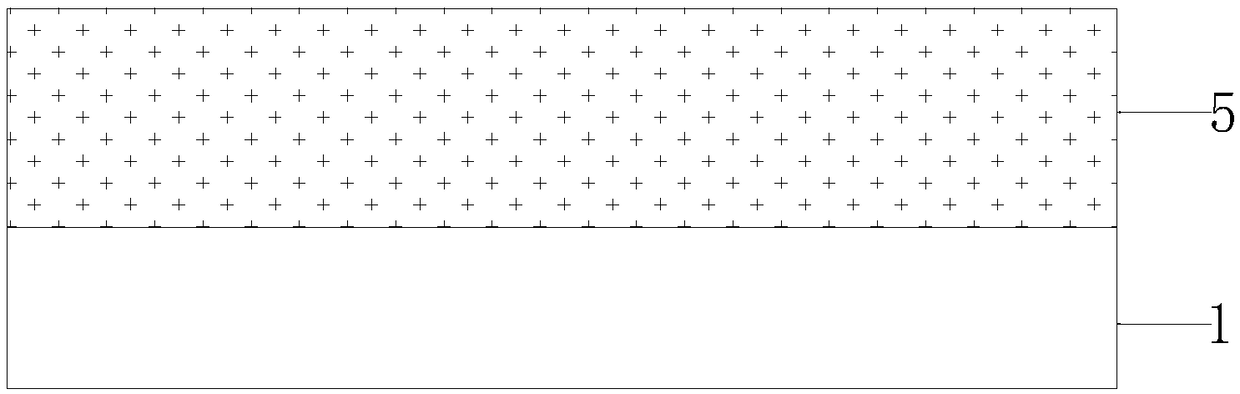

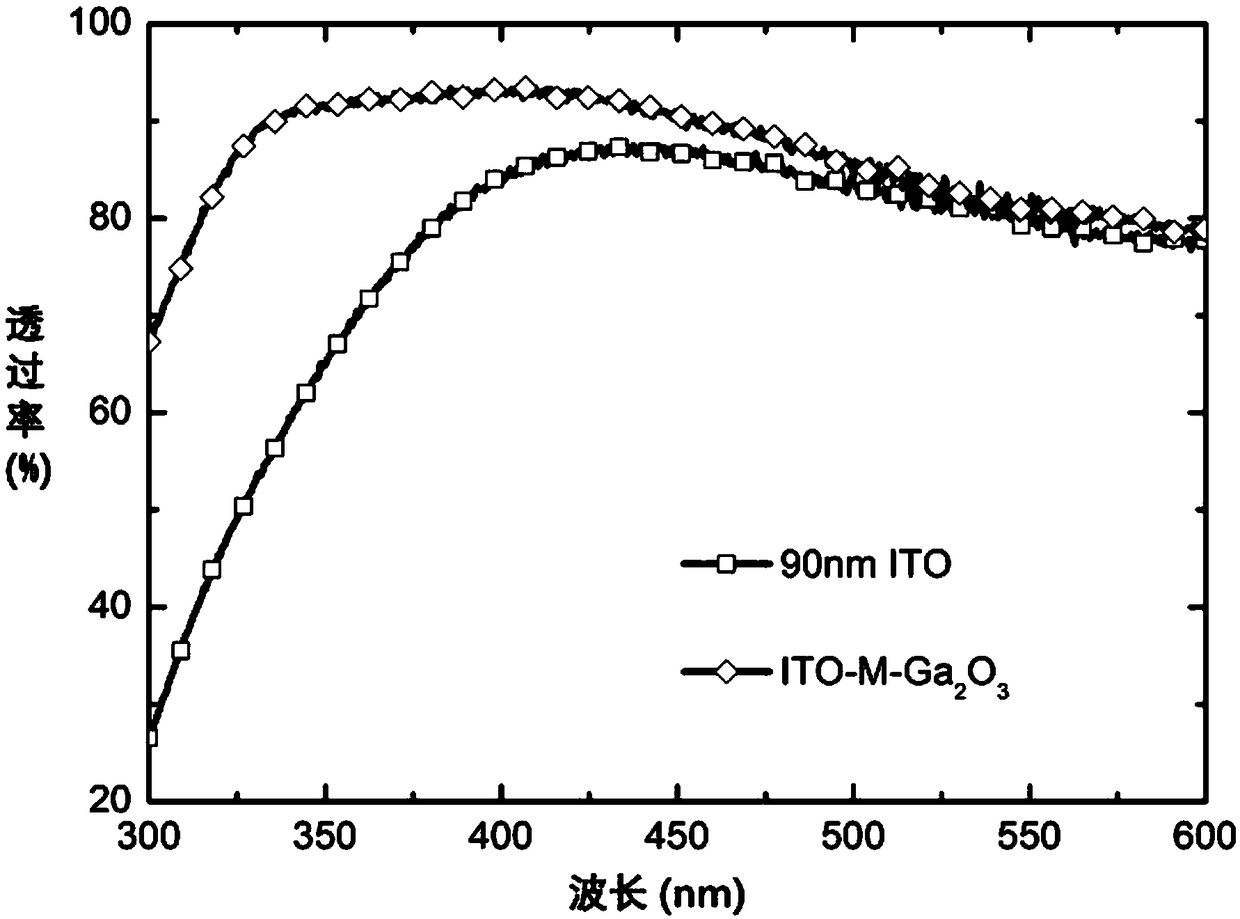

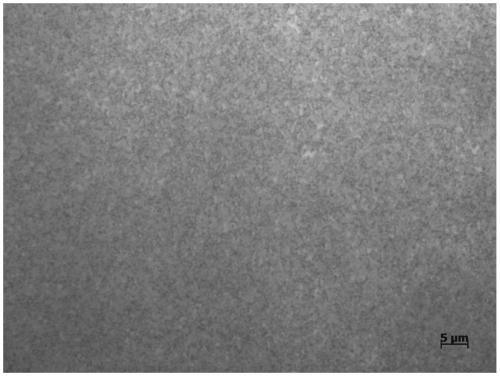

Metal gallium oxide doping transparent conductive membrane used for ultraviolet waveband and preparation method thereof

ActiveCN109136869AImprove transmittanceReduce sheet resistanceConductive layers on insulating-supportsVacuum evaporation coatingSputteringNitrogen

The invention discloses a metal gallium oxide doping transparent conductive membrane used for ultraviolet waveband and a preparation method thereof. The method comprises the steps that a layer of contact layer membrane firstly grows on a substrate, and annealing is conducted at the nitrogen-oxygen atmosphere of 400 DEG C-600 DEG C by a rapid thermal annealing furnace after the contact layer membrane grows; a first Ga2O3 membrane layer grows through sputtering under the condition of magnetic controlled argon sputtering; a doped membrane grows through sputtering under the condition of magnetic controlled argon sputtering; a second Ga2O3 membrane layer grows through sputtering under the condition of magnetic controlled argon sputtering, and annealing is conducted on completely growing membranes integrally at the nitrogen-oxygen atmosphere of 500 DEG C-600 DEG C by the rapid thermal annealing furnace, and membrane materials mutually penetrate, disperse and melt to form the metal doped Ga2O3 membrane. The transparent conductive membrane has higher membrane optical permeability and lower membrane square resistance on the basis of an ITO transparent conductive membrane.

Owner:ZHONGSHAN INST OF MODERN IND TECH SOUTH CHINA UNIV OF TECH +1

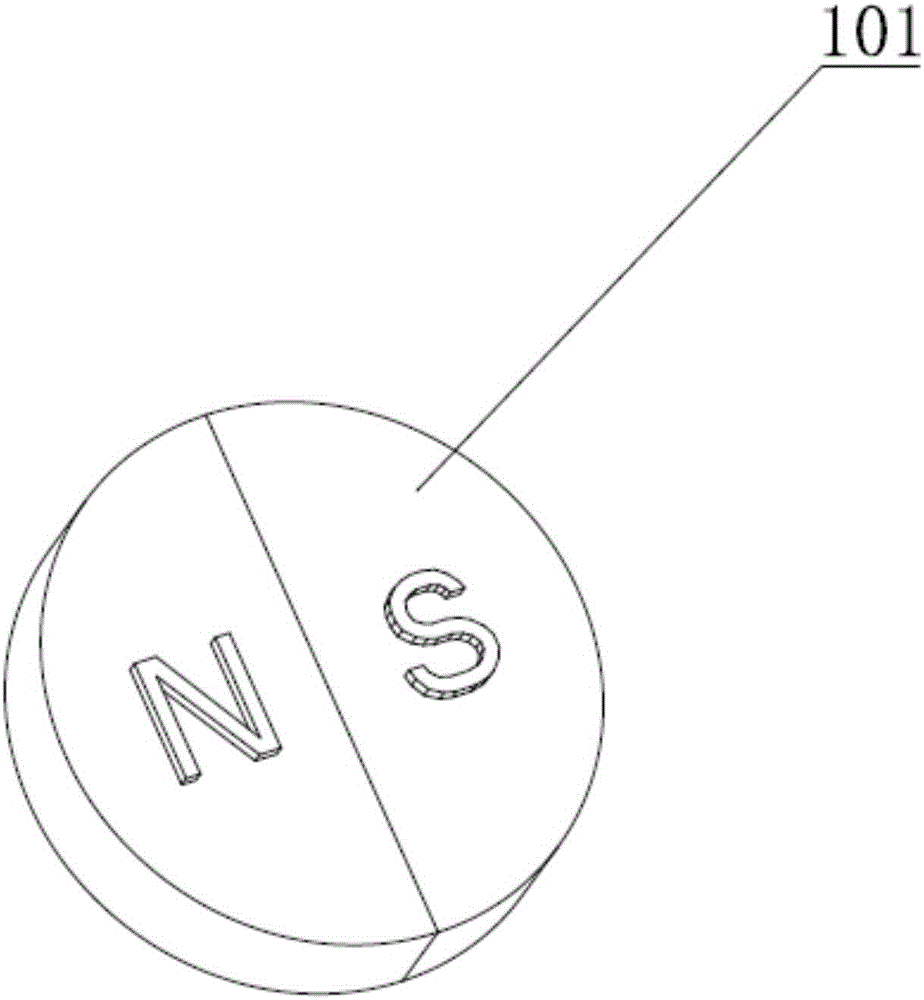

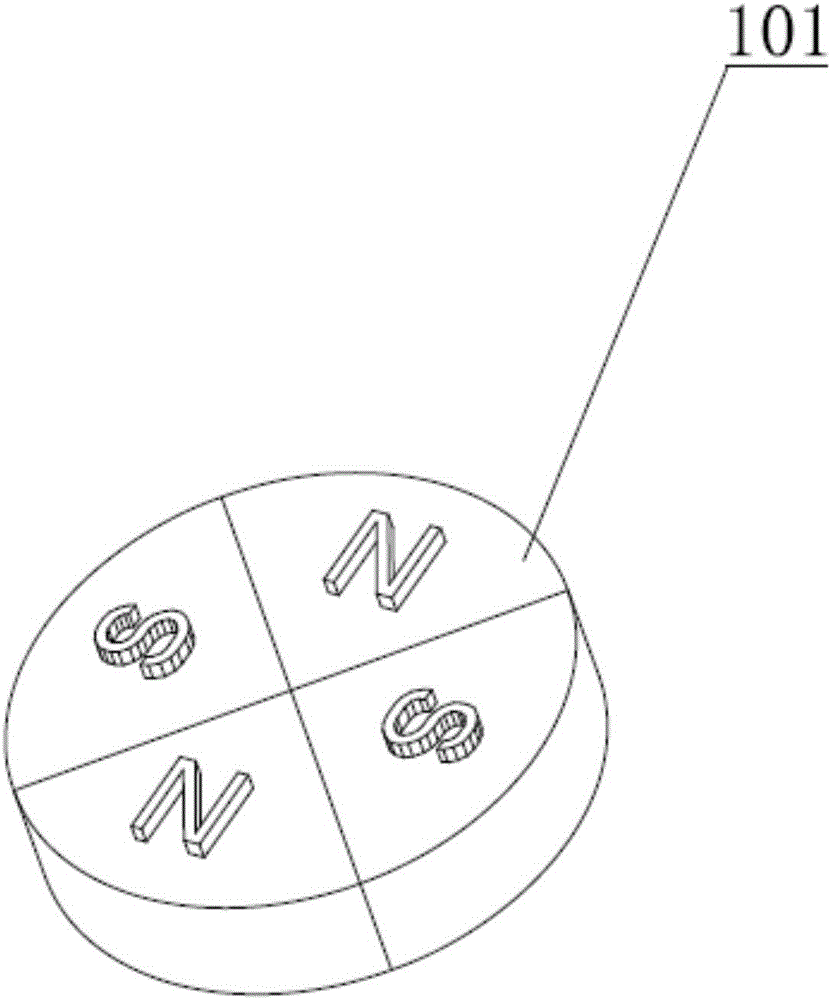

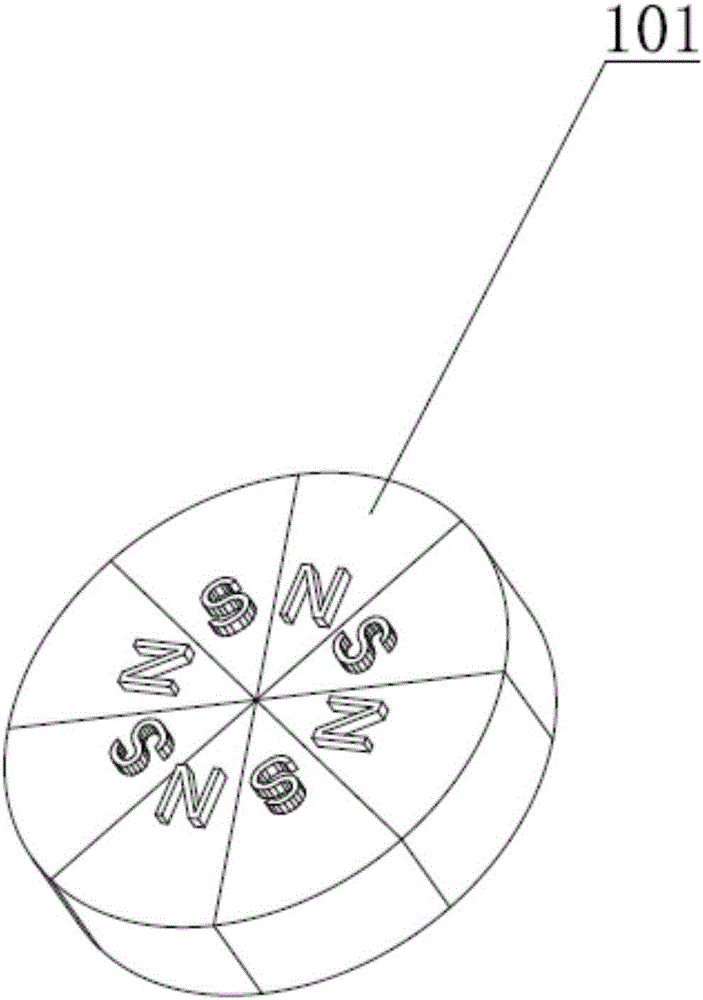

Magnetic adsorption mechanism and magnetic building block applying same

ActiveCN106098293ASimple structureAdsorption is easily achievedPermanent magnetsToysMagnetEngineering

The invention discloses a magnetic adsorption mechanism and a magnetic building block applying the same. The magnetic adsorption mechanism comprises a magnetic component and a support component supporting the magnetic component, wherein the magnetic component comprises a magnet, the magnet comprises an adsorbing surface, the adsorbing surface at least comprises an S pole and an N pole, and the magnetic component can rotate relative to the support component. When the magnetic adsorption mechanisms are used in pair, different poles located on the two adsorption mechanisms produce adsorption force through rotation, and accordingly, the two adsorption mechanisms are easily adsorbed together; the distance between the adsorbing surfaces is shorter, so that the adsorbing force is larger under the condition that magnets with equal-strength magnetic force are adopted. The magnetic building block applying the magnetic adsorption mechanism comprises a main building block body, wherein a cavity is formed in the main building block body, and the magnetic adsorption mechanism is arranged in the cavity. The magnetic building block is simple in structure and simple and convenient to assemble and disassemble and the use experience is good.

Owner:深圳市美高途实业有限公司

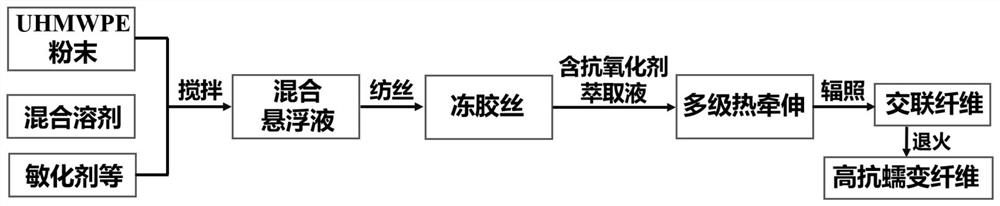

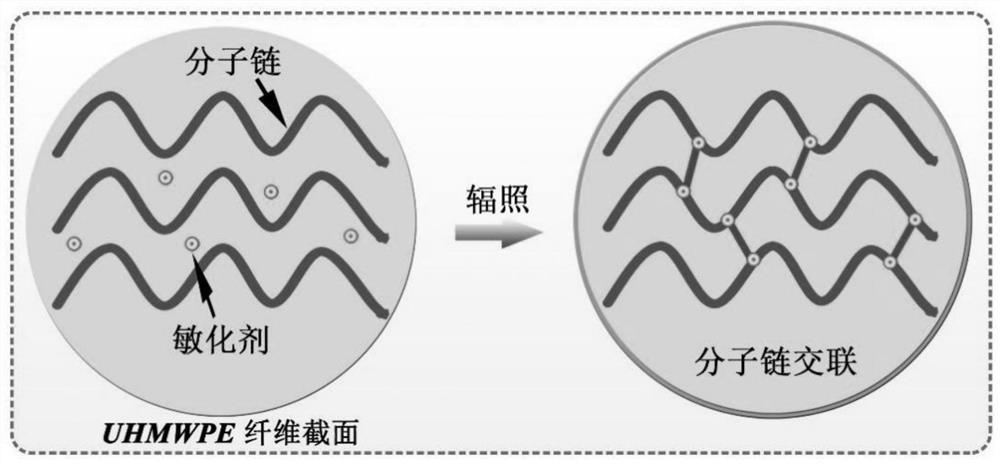

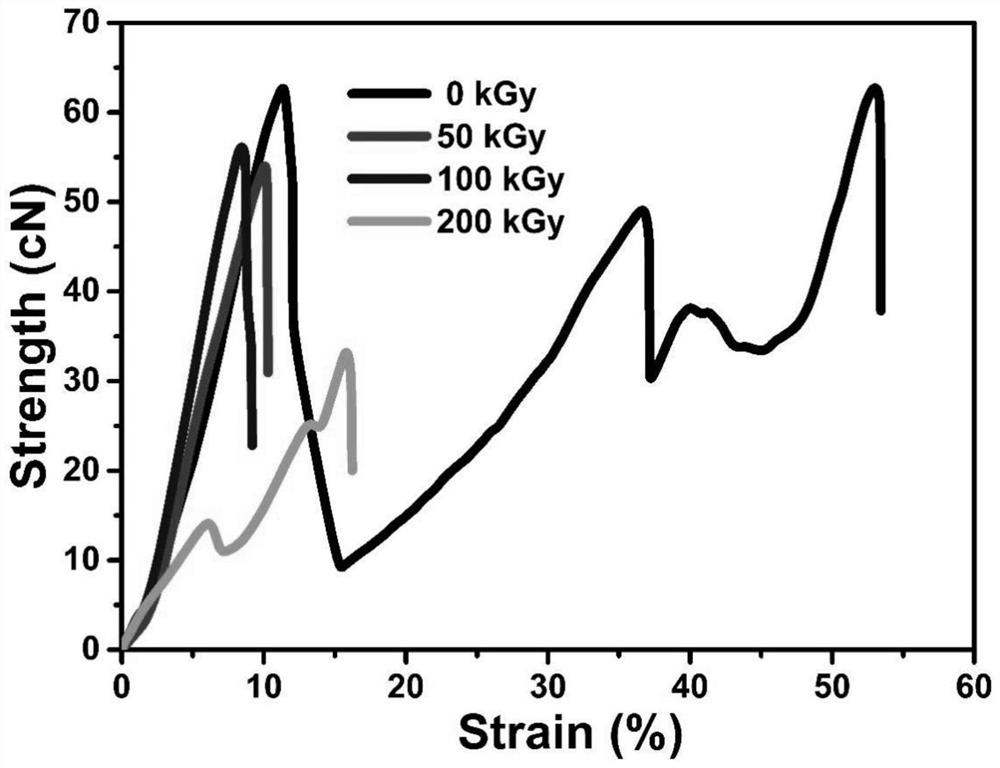

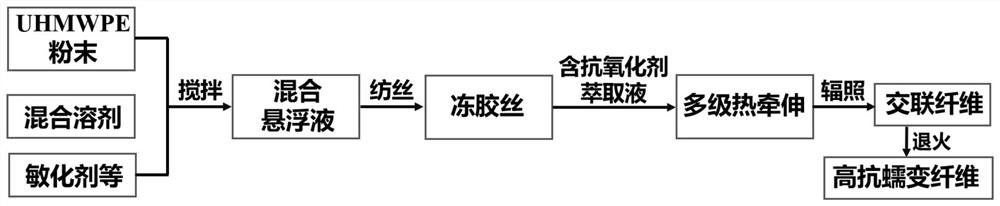

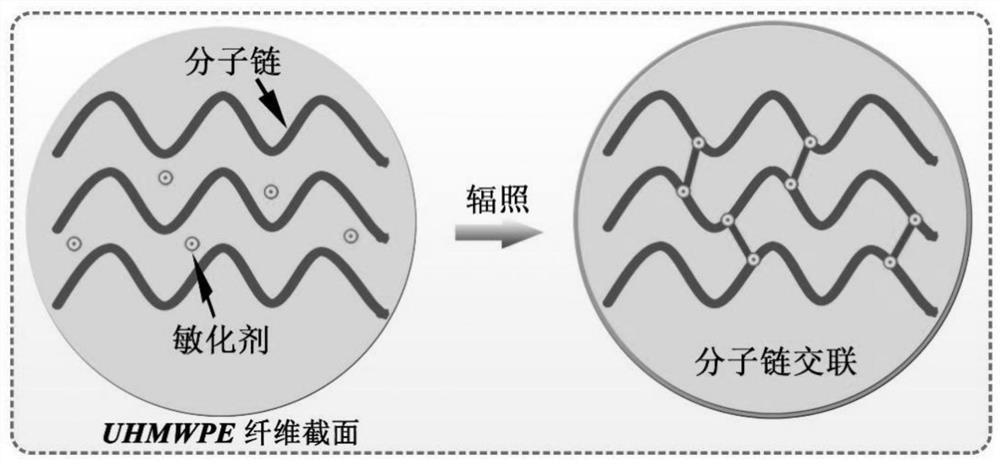

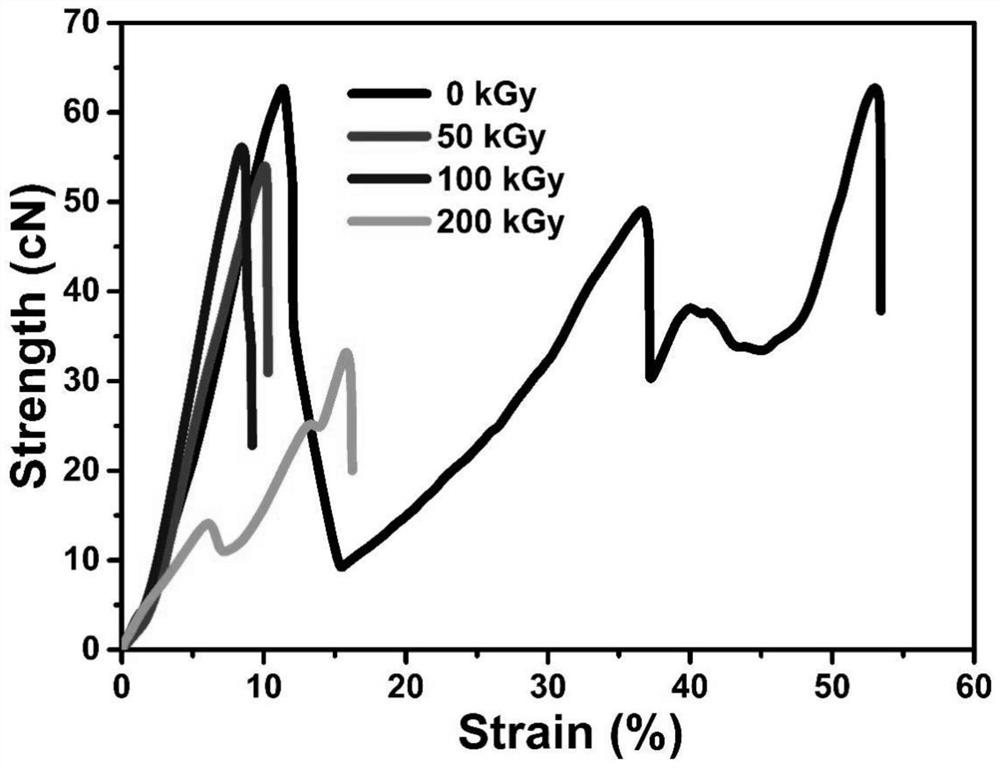

High-creep-resistance ultra-high molecular weight polyethylene fiber and preparation method thereof

ActiveCN113502556AReduce oxidationPrevent oxidationRadioactive element fibre treatmentMonocomponent polyolefin artificial filamentFiberPolymer science

The invention provides high-creep-resistance ultra-high molecular weight polyethylene fiber and a preparation method thereof. The preparation method comprises the following steps of S1, mixing ultra-high molecular weight polyethylene powder, a mixed solvent, an antioxidant and a sensitizer according to a preset proportion, and performing stirring to obtain a uniform mixed suspension; S2, putting the mixed suspension into a double-screw extruder for spinning treatment, then obtaining primary gel filament through a cooling water bath, extracting the primary gel filament through a mixed extraction solution containing the antioxidant, performing drying, and then obtaining a primary fiber product through multi-stage hot drafting and multi-stage drying in a drying oven; and S3, performing irradiation crosslinking: performing irradiation treatment of a predetermined dose on the primary fiber product, and finally performing annealing treatment under a nitrogen condition to obtain the high-creep-resistance ultra-high molecular weight polyethylene fiber. Compared with conventional ultra-high molecular weight polyethylene fiber, the creep elongation of the high-creep-resistance ultra-high molecular weight polyethylene fiber prepared by the invention is reduced by 50% or above.

Owner:WUHAN TEXTILE UNIV +2

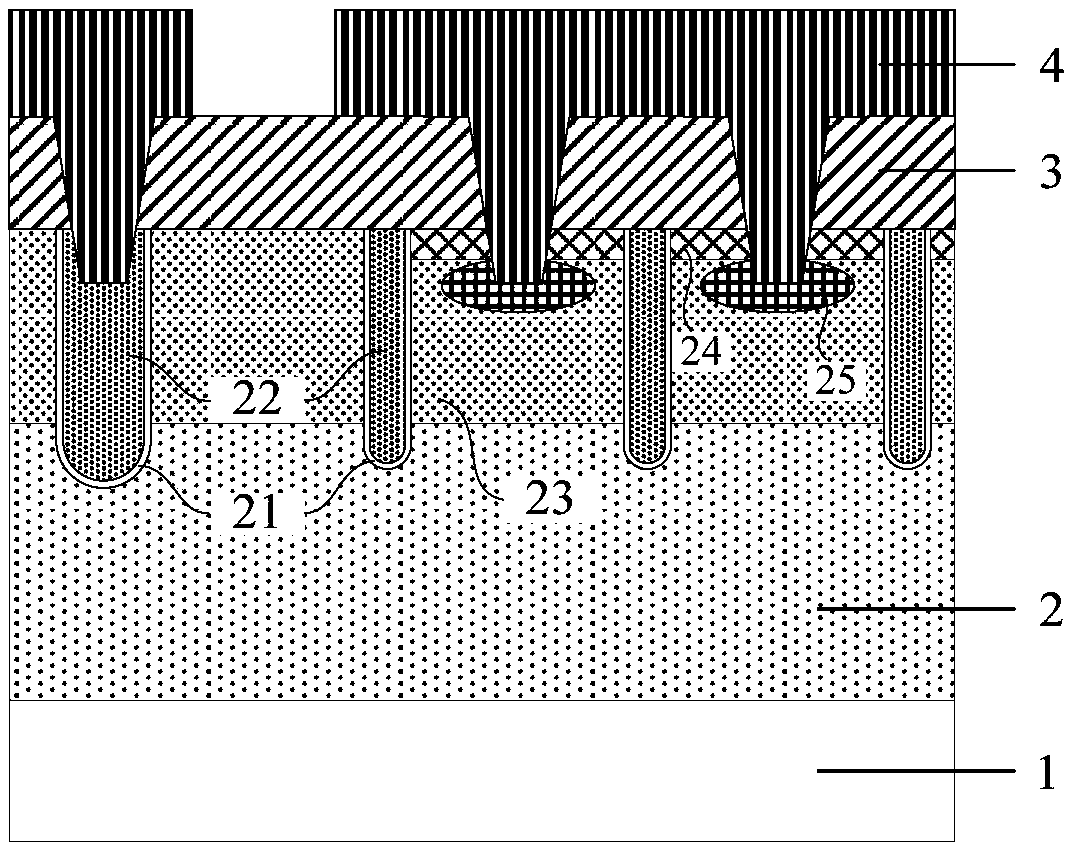

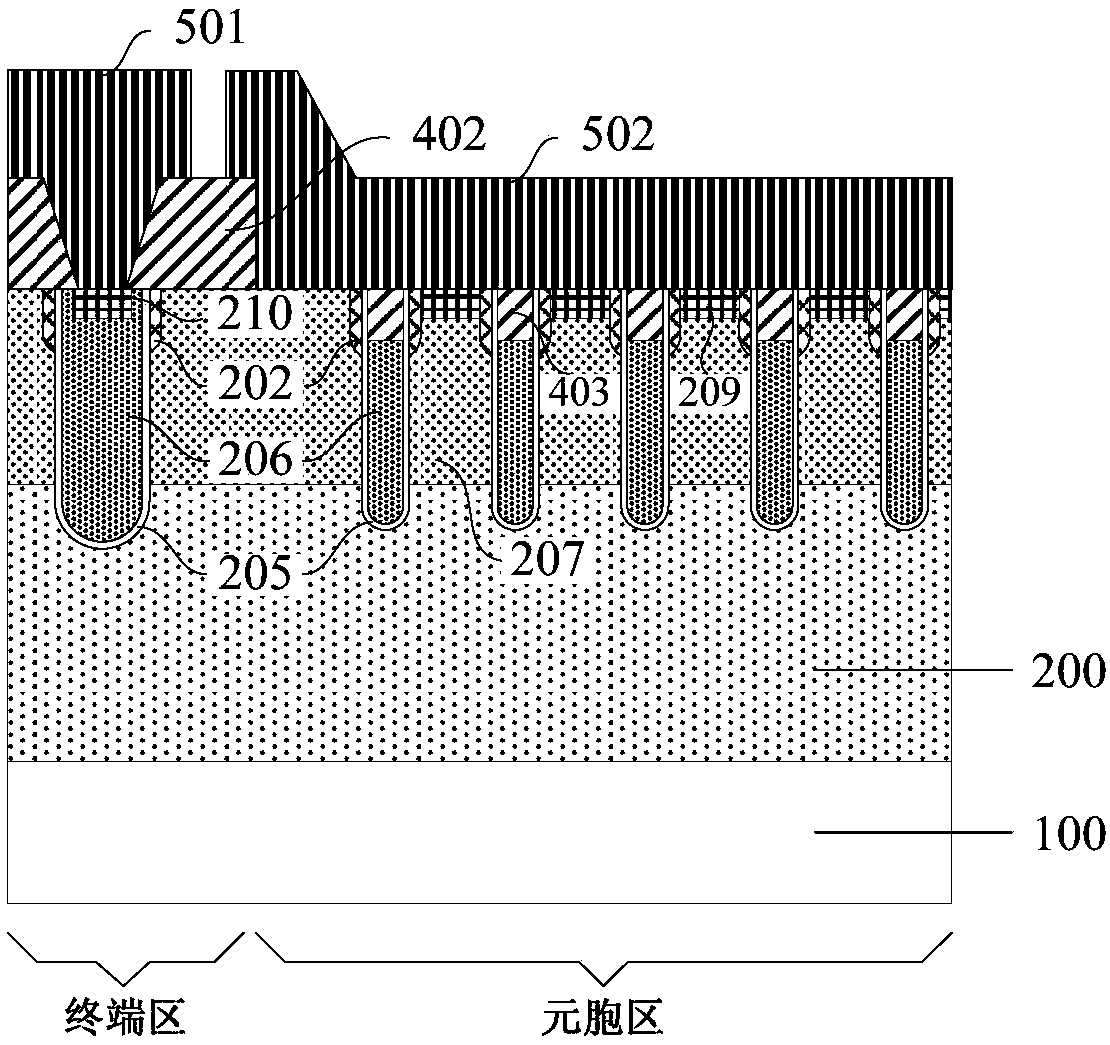

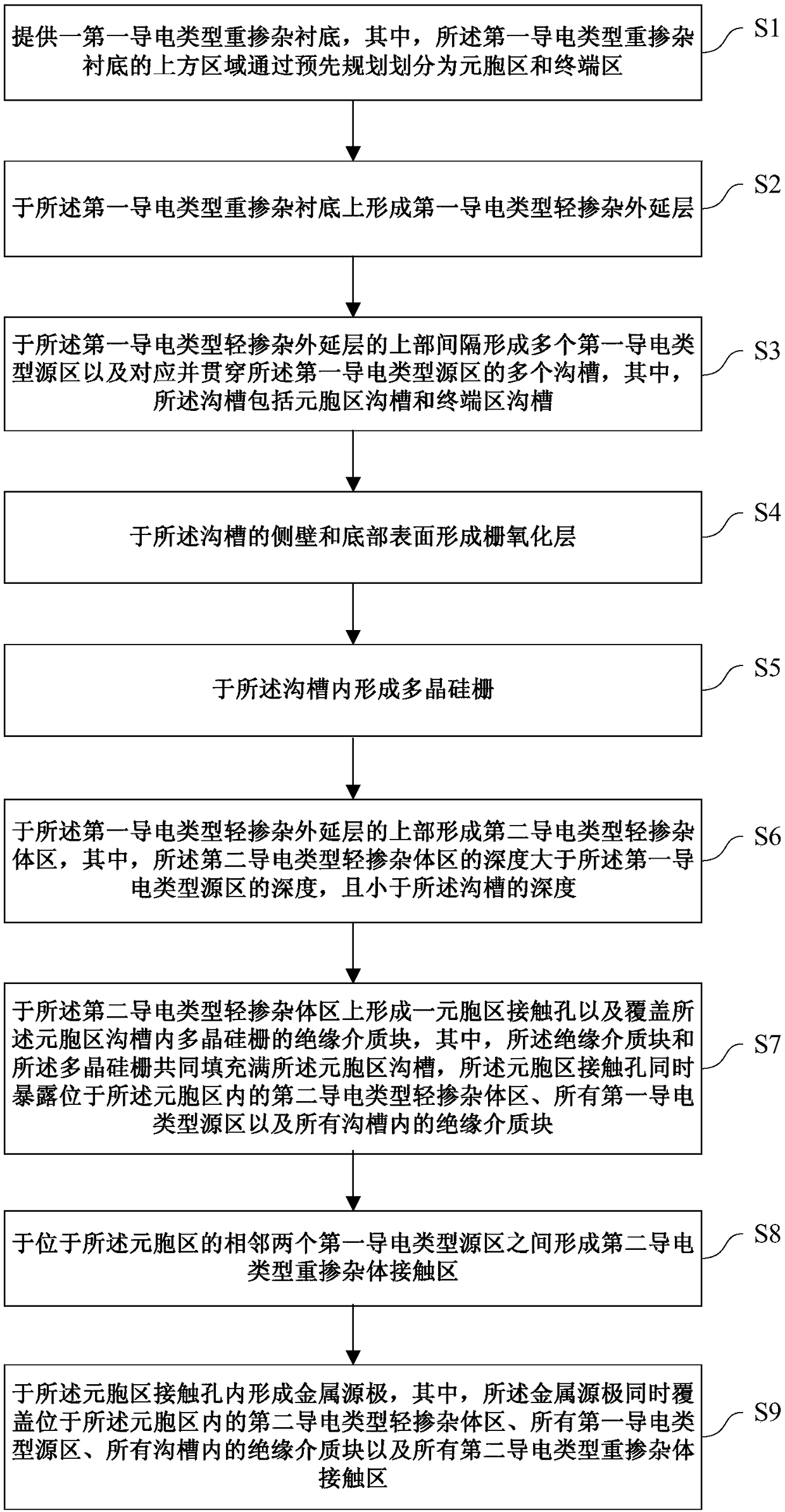

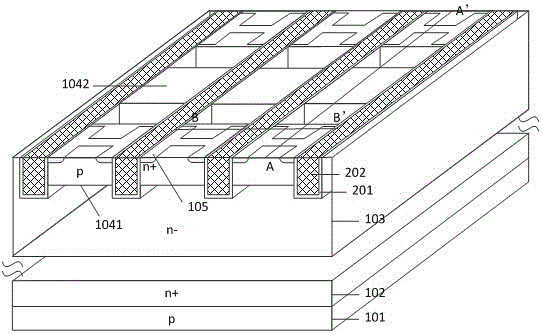

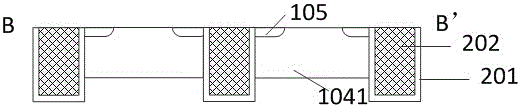

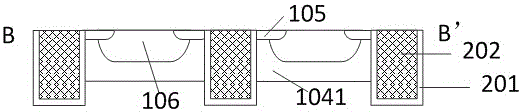

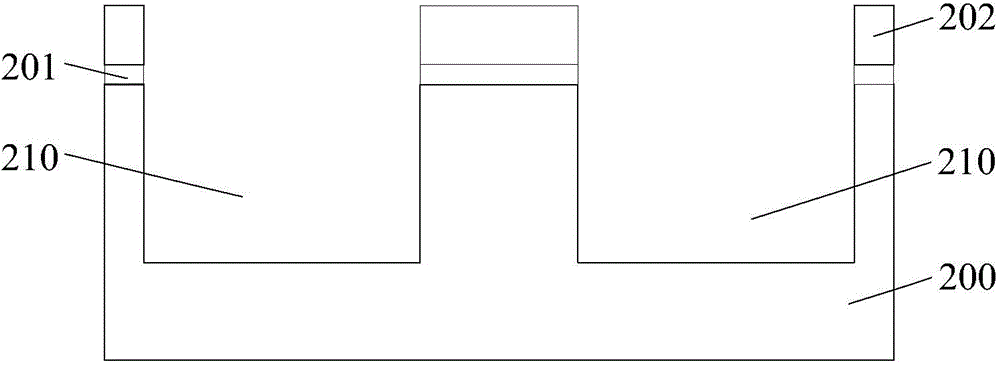

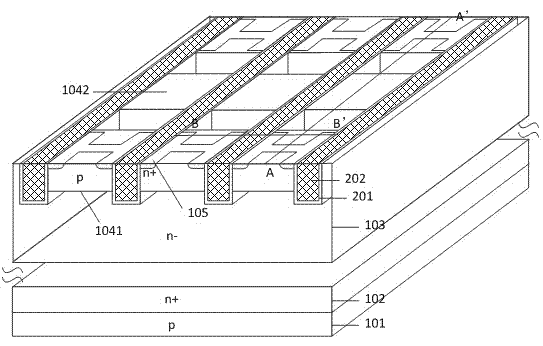

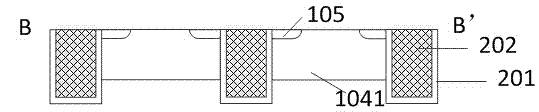

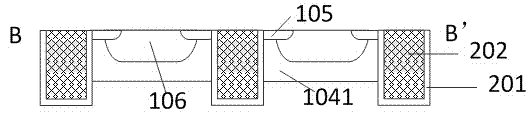

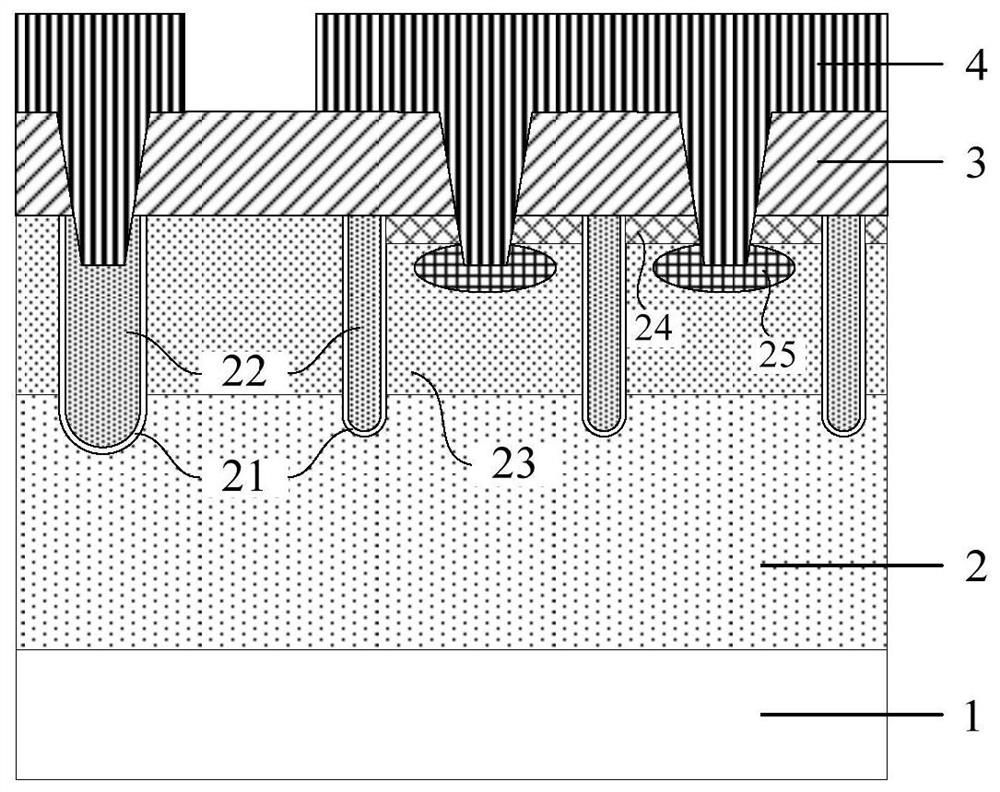

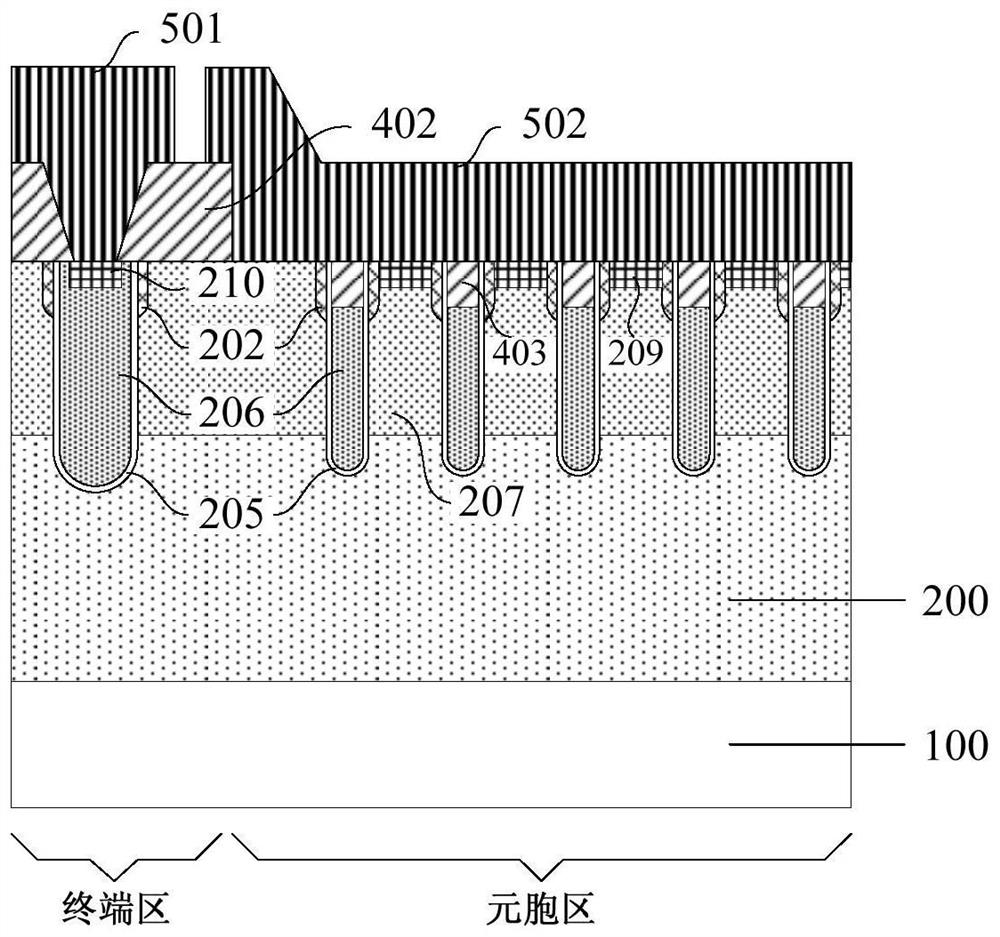

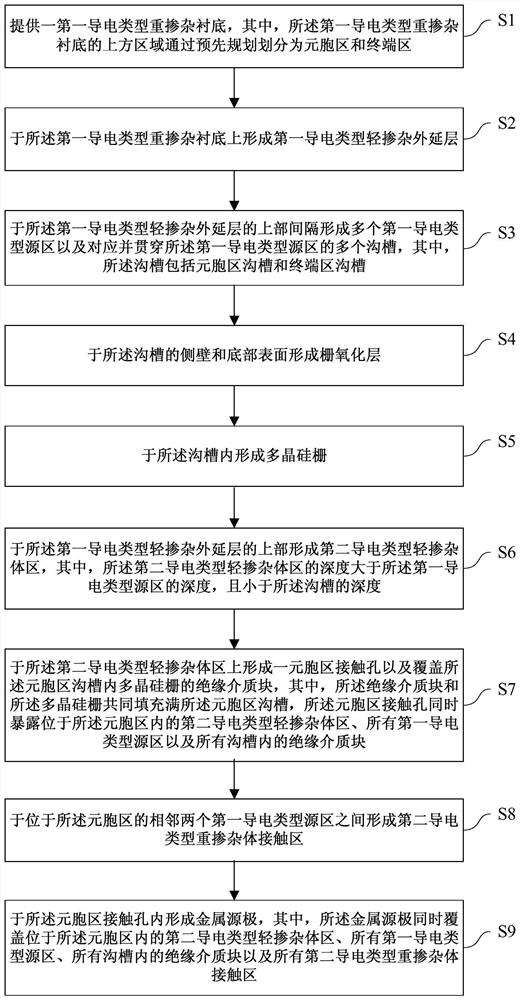

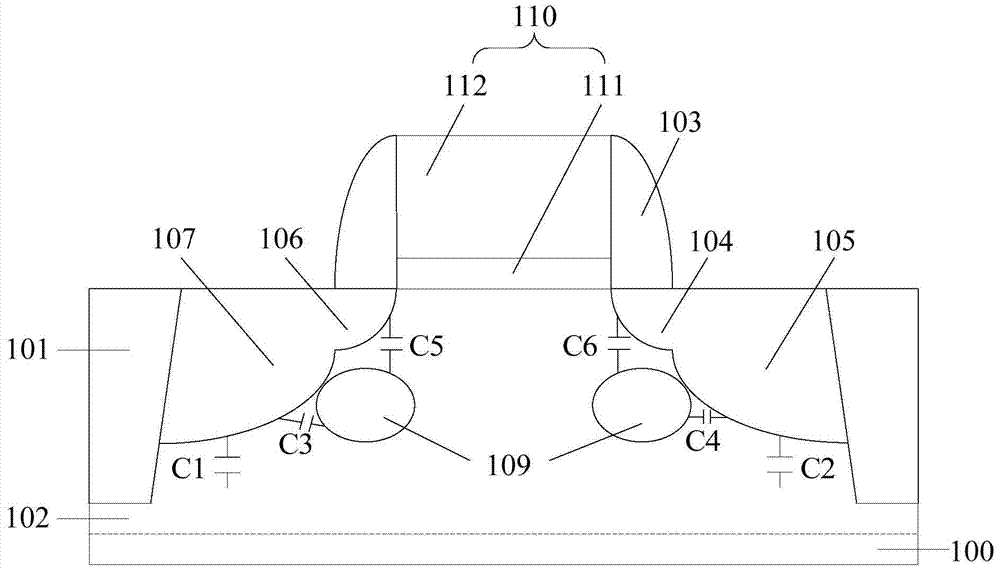

Groove-type MOS device and manufacturing method thereof

ActiveCN108962989AGuaranteed stabilityImprove device densitySemiconductor/solid-state device manufacturingSemiconductor devicesBody regionOxide semiconductor

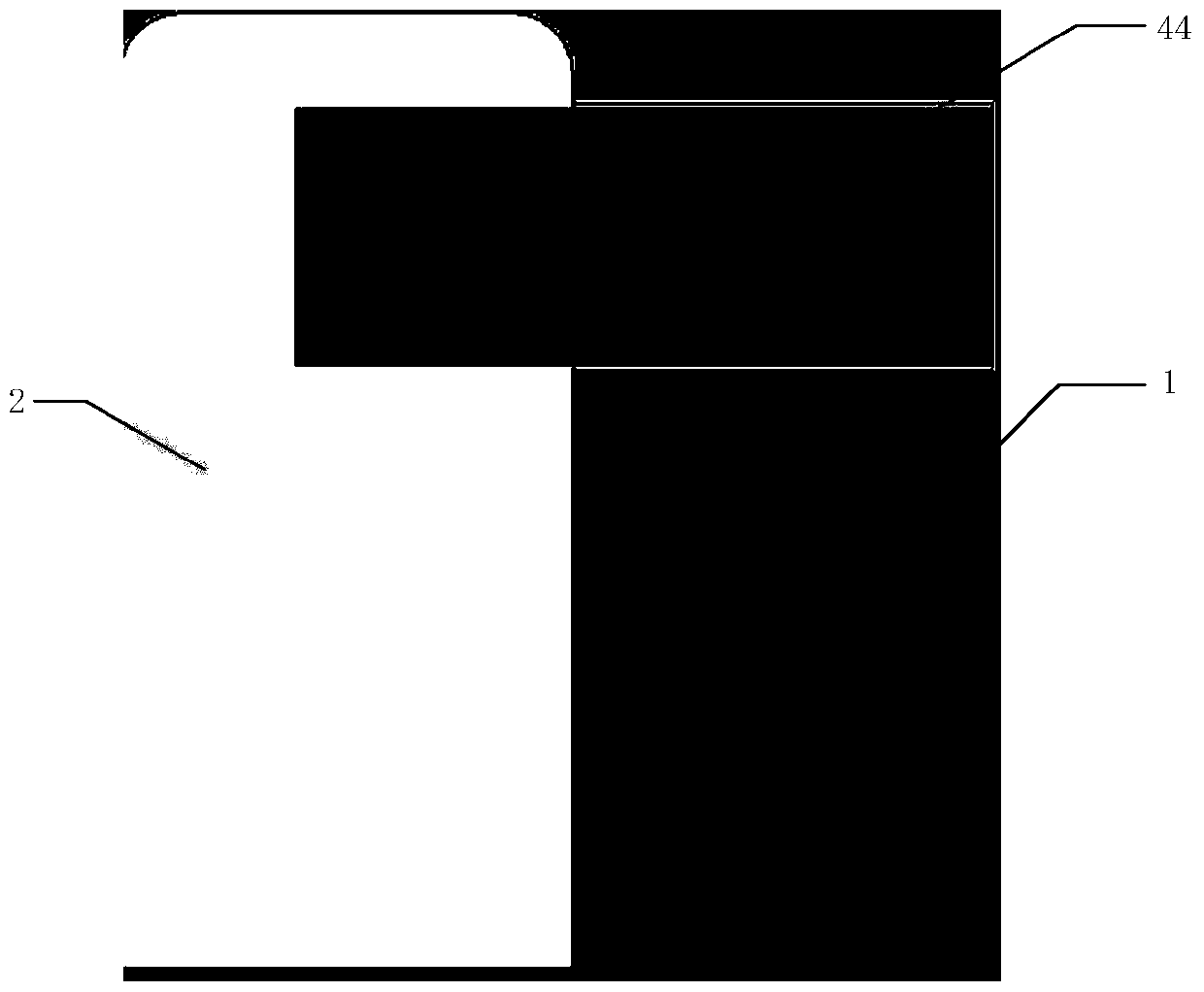

The invention provides a groove-type MOS (Metal-Oxide-Semiconductor) device and a manufacturing method thereof. The groove-type MOS device at least includes a first conductive heavily doped substrate,a first conductive lightly doped epitaxial layer on the first conductive heavily doped substrate, a plurality of first conductive source regions, a plurality of grooves, a gate oxide layer and a polysilicon gate which are formed in the each groove, a second conductive lightly doped body region formed on the upper portion of the first conductive lightly doped epitaxial layer, a cellular region contact hole formed in the second conductive lightly doped body region, an insulating dielectric block covering the polysilicon gate in the groove of the cellular region, a second conductive heavily doped body contact region formed between two adjacent first conductive source regions of the cellular region, and a metal source electrode formed in the contact hole of the cellular region, wherein the plurality of first conductive source regions and the plurality of grooves are formed on the upper portion of the first conductive lightly doped epitaxial layer at intervals. The groove-type MOS device can guarantee stability of the device while improving the device density and reducing the conduction resistance.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

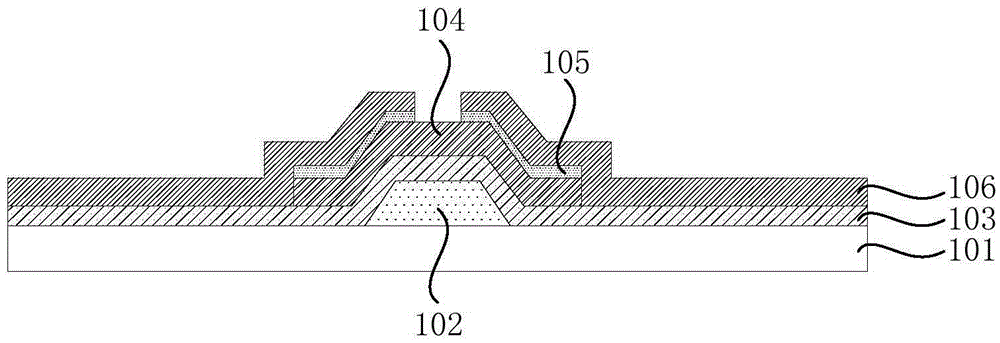

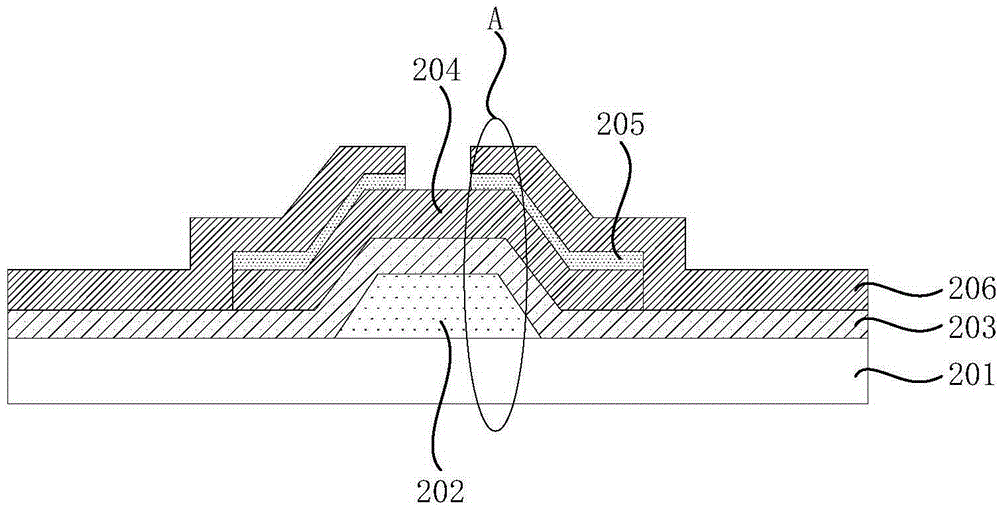

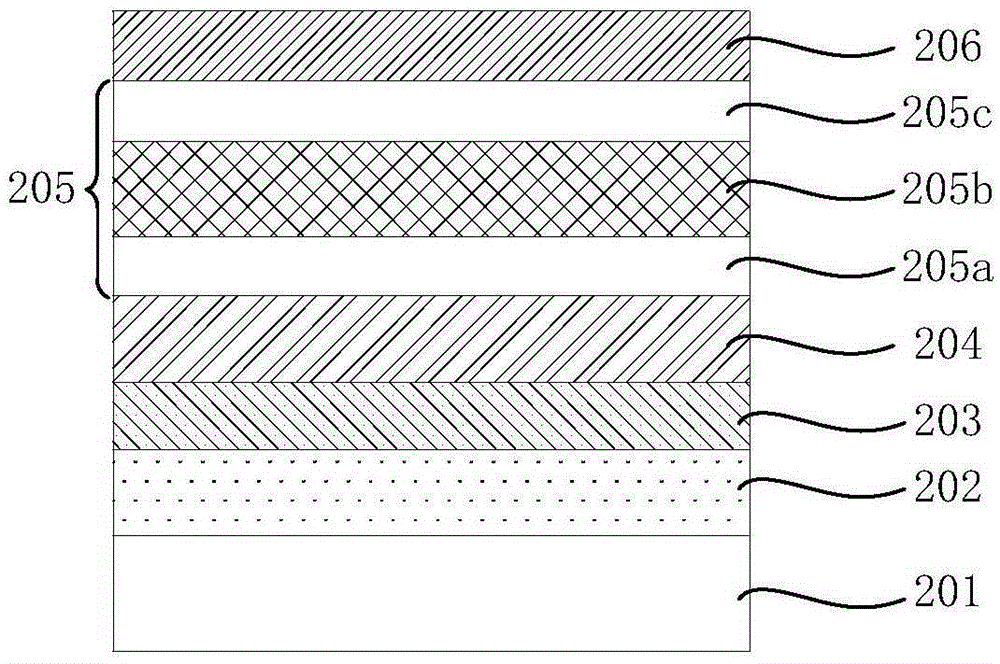

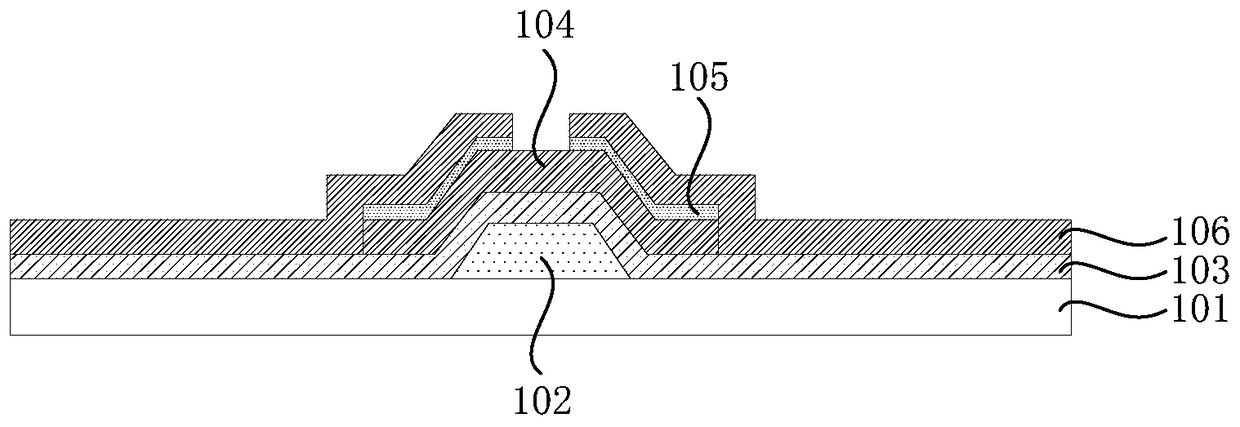

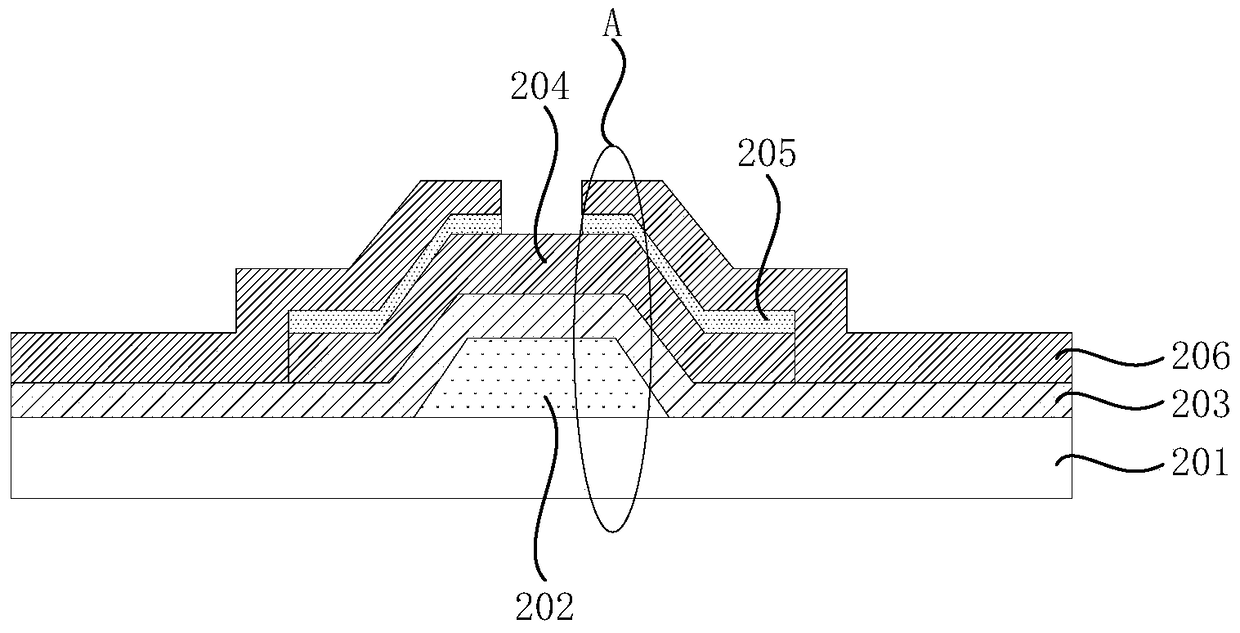

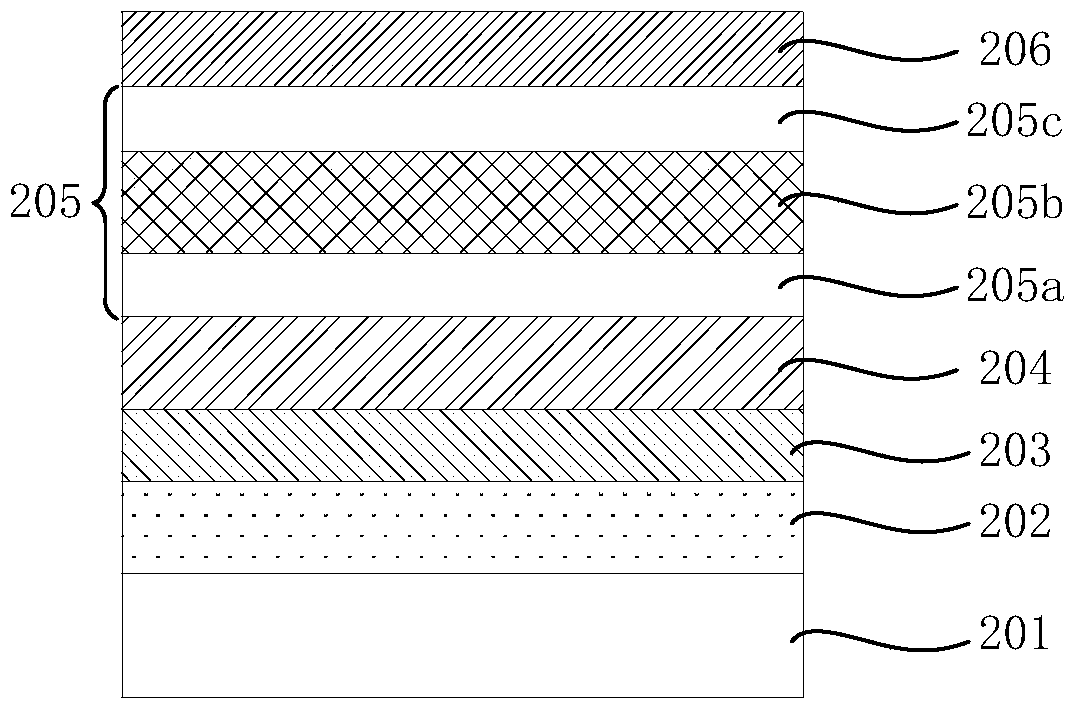

Thin film transistor and array substrate

ActiveCN105405892AReduce leakage currentImprove afterimage problemTransistorSolid-state devicesPhysicsHigh impedance

The invention discloses a thin film transistor and an array substrate. The thin film transistor comprises a grid electrode, a grid electrode insulation layer, an active layer, a first material layer and a source / drain electrode, wherein the grid electrode insulation layer is formed on the grid electrode and covers the grid electrode; the active layer is formed on the grid electrode insulation layer; the first material layer is formed on the active layer; the source / drain electrode is formed on the first material layer; the first material layer comprises a first Ohmic contact layer, a second Ohmic contact layer and a high-impedance inclusion layer, wherein the high-impedance inclusion layer is formed between the first Ohmic contact layer and the second Ohmic contact layer; and the impedance of the high-impedance inclusion layer is greater than the impedance of the first Ohmic contact layer and the second Ohmic contact layer. The thin film transistor can effectively lower leakage current which is in the presence between the source / drain electrode and the active layer and has a simple manufacture technology.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Battery cell structure, secondary battery, battery pack and power utilization device

PendingCN114784362AImprove securityReduce low temperature and low SOCCell electrodesSecondary cellsHigh energyBattery cell

The invention belongs to the technical field of secondary batteries, and particularly relates to a battery cell structure, a secondary battery, a battery pack and a power utilization device, and the battery cell structure comprises a first battery cell unit which comprises a first positive plate; the second battery cell unit comprises a second positive plate; the unit diaphragm is arranged between the first battery cell unit and the second battery cell unit; wherein the first positive plate and the second positive plate are respectively made of different positive active materials. The battery cell structure and the secondary battery have the advantages of high specific capacity, high energy density, excellent cycle performance and good needling and overcharge performance.

Owner:JIANGSU ZENIO NEW ENERGY BATTERY TECH CO LTD

Grading constant current charging method with voltage-controlled pulse

InactiveCN102945987BShorten charging timeReduce outgassingSecondary cells charging/dischargingElectrical batteryEngineering

The invention relates to a grading constant current charging method with voltage-controlled pulse. A section of a pulse charging and discharging process with the depolarization function is attached when storage battery voltage rises to a gassing point at each grade of constant current charging stage. Charging current amplitude of the pulse charging and discharging process is equal to constant current amplitude at the same grade, and discharging current amplitude value is 0.5-1% of first constant current amplitude. A pulsating voltage average value of a storage battery in the pulse charging and discharging process is fixed and controlled to be a litter lower than the gassing point. Compared with a traditional grading constant current charging method used by a high-capacity lead-acid storage battery at present, the grading constant current charging method has the advantages of being short in charging time, high in charging efficiency, small in battery gassing amount, small in battery damage and the like.

Owner:中国船舶重工集团公司第七〇一研究所 +1

Manufacturing method of groove power device

InactiveCN104008976AThe spin-coating process is easy to controlLow costSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoresistPolysilicon gate

The invention belongs to the technical field of manufacturing of semiconductor power devices, and particularly relates to a manufacturing method of a groove power device. The manufacturing method includes the steps that after a field oxide layer is formed in a U-shaped groove of the device, photoresist is adopted as a sacrificial dielectric layer, the developed photoresist is reserved only in the U-shaped groove by controlling the exposure time and the development time of the photoresist, then the exposed portions of the field oxide layer are etched away, then the photoresist is stripped, then a gate oxide layer is oxidized, a polycrystalline silicon grid electrode is deposited, and finally source electrode metal making contact with a source area and a channel doping area is formed. The manufacturing method has the advantages of being simple and reliable in technical process, easy to control and the like, the production cost of the groove power device can be lowered, and yield of the groove power device can be improved.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

A Realization Method of Waveguide-Microstrip Transition Structure in Millimeter Wave Band

ActiveCN104934676BWill not increase the difficulty of the processPrecise positioningWaveguide type devicesMicrowaveAdhesive

The invention provides a method for realizing a waveguide-microstrip transition structure in the millimeter wave frequency band. The steps of the method include: 1. opening a narrow groove on the wide wall on one side of the waveguide; Metal thin film pattern sputtering is carried out on both sides, 50 ohm microstrip transmission line, microstrip impedance transformation line, positioning mark circuit and probe circuit are formed on the front side, and a metal layer with an extension part is formed on the back side, and the probe circuit is formed by traditional suspension The stripline is improved to a combined form of a microstrip line and a suspended stripline; 3. The back of the dielectric substrate is bonded in the narrow slot with conductive glue, and the probe circuit is vertically suspended in the waveguide. The waveguide-probe circuit transition structure obtained by this method is suitable for microwave products in the millimeter wave or even higher frequency bands. On the premise of ensuring the excellent performance of the transition structure, it greatly reduces the uncertainty caused by manual assembly and ensures Consistency of product assembly.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

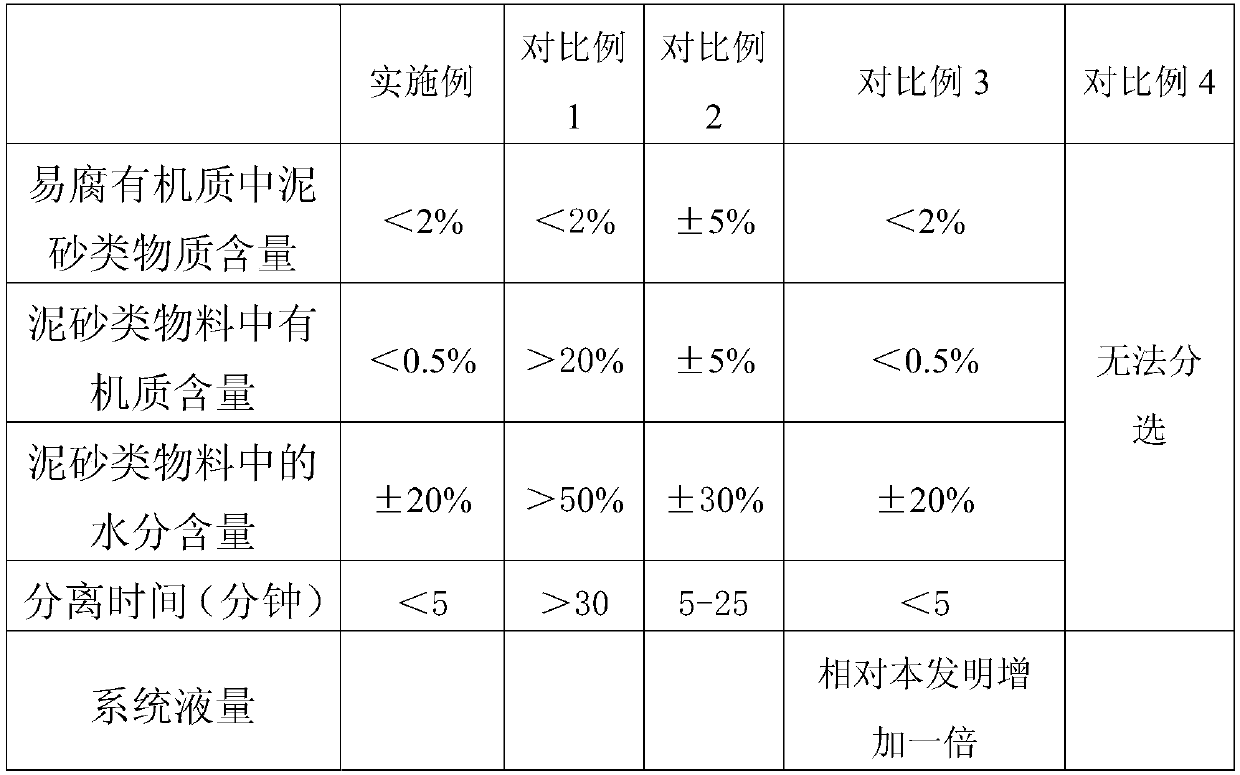

System process method for fertilizer making through perishable garbage fermentation

ActiveCN110590420AIncrease moisture contentMoisture content will not increaseBio-organic fraction processingOrganic fertiliser preparationSlurryWaste treatment

The invention relates to the technical field of solid waste treatment, in particular to a system process method for fertilizer making through perishable garbage fermentation. The system process methodcomprises the steps: to-be-treated garbage is crushed and separated firstly, and refractory organic matter is removed; and then water is added to adjust the solid content of the garbage, slurry is prepared, and micron bubbles are introduced into the slurry. The refractory organic matter such as plastic and fabrics and imputrescible inorganic matter such as glass, ceramic, gravel and metal are removed to the greatest extent; the content of the heavy metal in garbage derived fertilizer can be effectively decreased and stably controlled, the uncertainty of the content of the heavy metal in the garbage derived fertilizer is eliminated, and convenience is provided for application of the garbage derived fertilizer; and the content of the organic matter and the content of the water in sinking and separated muddy sand materials with the large specific gravity are low, and the sinking and separated muddy sand materials with the large specific gravity meet the requirements of being subjected todirect landfill and used as raw materials of building materials.

Owner:中原环资科技有限公司

High-temperature alloy machining tool and application thereof

InactiveCN111286661AGood metallurgical performanceWill not increase the difficulty of the processMilling cuttersSuperalloyMachine tool

The invention discloses a high-temperature alloy machining tool and application thereof. The tool comprises a substrate, and the substrate comprises the following chemical components of, in percentageby weight, 10 %-13 % of cobalt (Co), 0.4 %-1.3 % of chromium (Cr), 84 %-89 % of tungsten carbide (WC) and 0.2 %-1.5 % of rare metal elements. The high-temperature alloy machining tool has excellent cutting performance, strong high-temperature hardness and long service life; and the actual cutting result shows that the substrate with the above components has better performance than an existing known cutting tool for high-temperature alloy machining, and has better performance in the aspects of semi-finish machining and finish machining after being matched with a coating.

Owner:GANZHOU ACHTECK TOOL TECH

Injection Enhanced Insulated Gate Bipolar Transistor

ActiveCN104332497BIncrease the carrier concentrationReduce conduction voltage dropSemiconductor devicesPower semiconductor deviceCharge carrier

Owner:中国东方电气集团有限公司

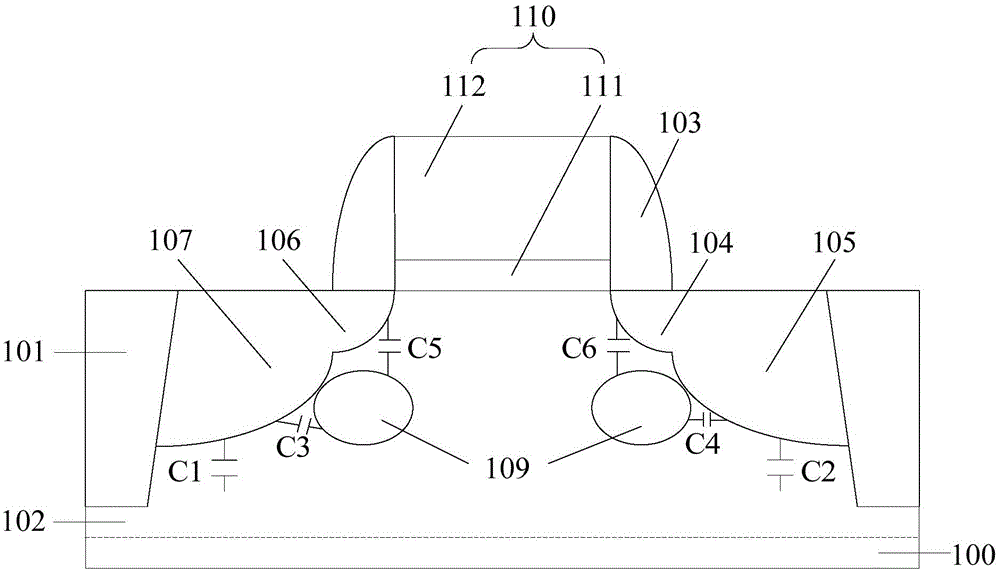

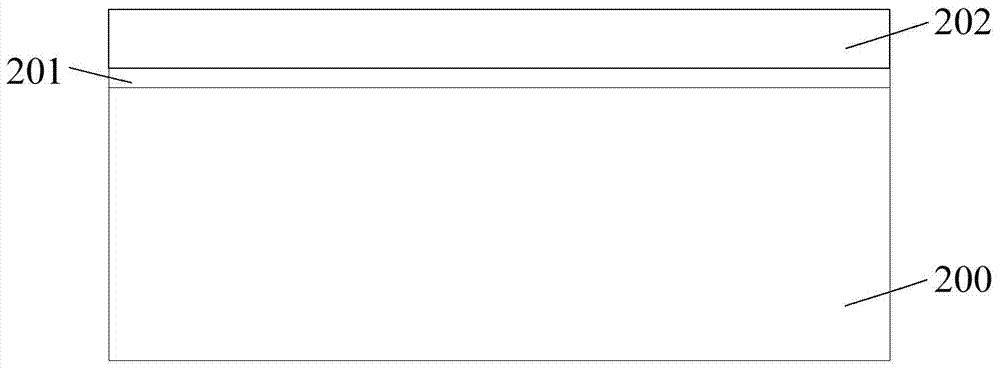

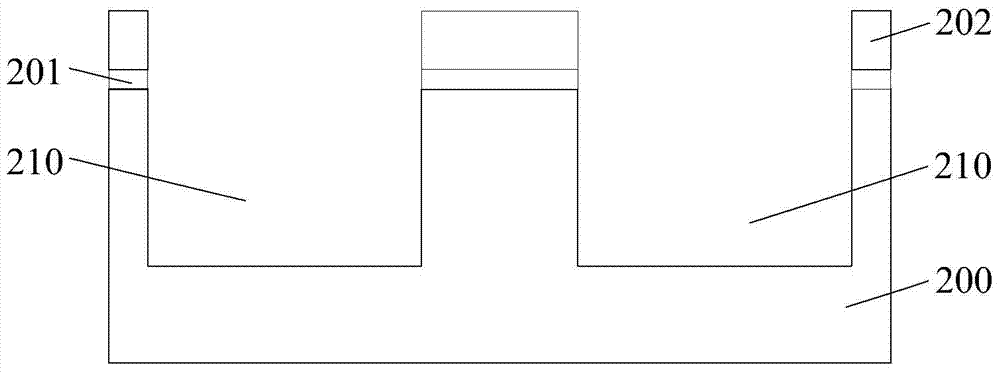

Transistor and transistor forming method

ActiveCN104425604AReduce RC delayRun fastTransistorSemiconductor/solid-state device manufacturingInsulation layerGate dielectric

The invention relates to a transistor and a transistor forming method, wherein the transistor forming method comprises the following steps that a semiconductor substrate is provided; at least two grooves are formed in the semiconductor substrate; insulation layers filling the grooves are formed in the grooves, and in addition, the tops of the insulation layers are set to be lower than the surface of the semiconductor substrate; epitaxial layers are formed on the surface and the side wall of the semiconductor substrate higher than the tops of the isolation layers, and in addition, the epitaxial layers are enabled to cover the partial isolation layers arranged at the two sides of the semiconductor substrate; a well region is formed in the semiconductor substrate and the epitaxial layers; a gate electrode structure is formed on the surface of each epitaxial layer, wherein each gate electrode structure comprises a gate dielectric layer covering the surface of the corresponding epitaxial layer and a gate conducting layer positioned on the top of the grate dielectric layer; light doping regions are formed in the epitaxial layers arranged at the two sides of the grate conducting layers; a heavy doping region is formed in each light doping region, and in addition, the heavy doping regions and the well region are isolated by the light doping regions and the isolation layers. The transistor formed by the method provided by the invention has low power consumption, the operation speed is high, the groove dimension is small, and in addition, the warping effect can be effectively eliminated.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Injection reinforced bipolar transistor of insulated gate

ActiveCN104332497AIncrease the carrier concentrationReduce conduction voltage dropSemiconductor devicesPower semiconductor deviceVoltage drop

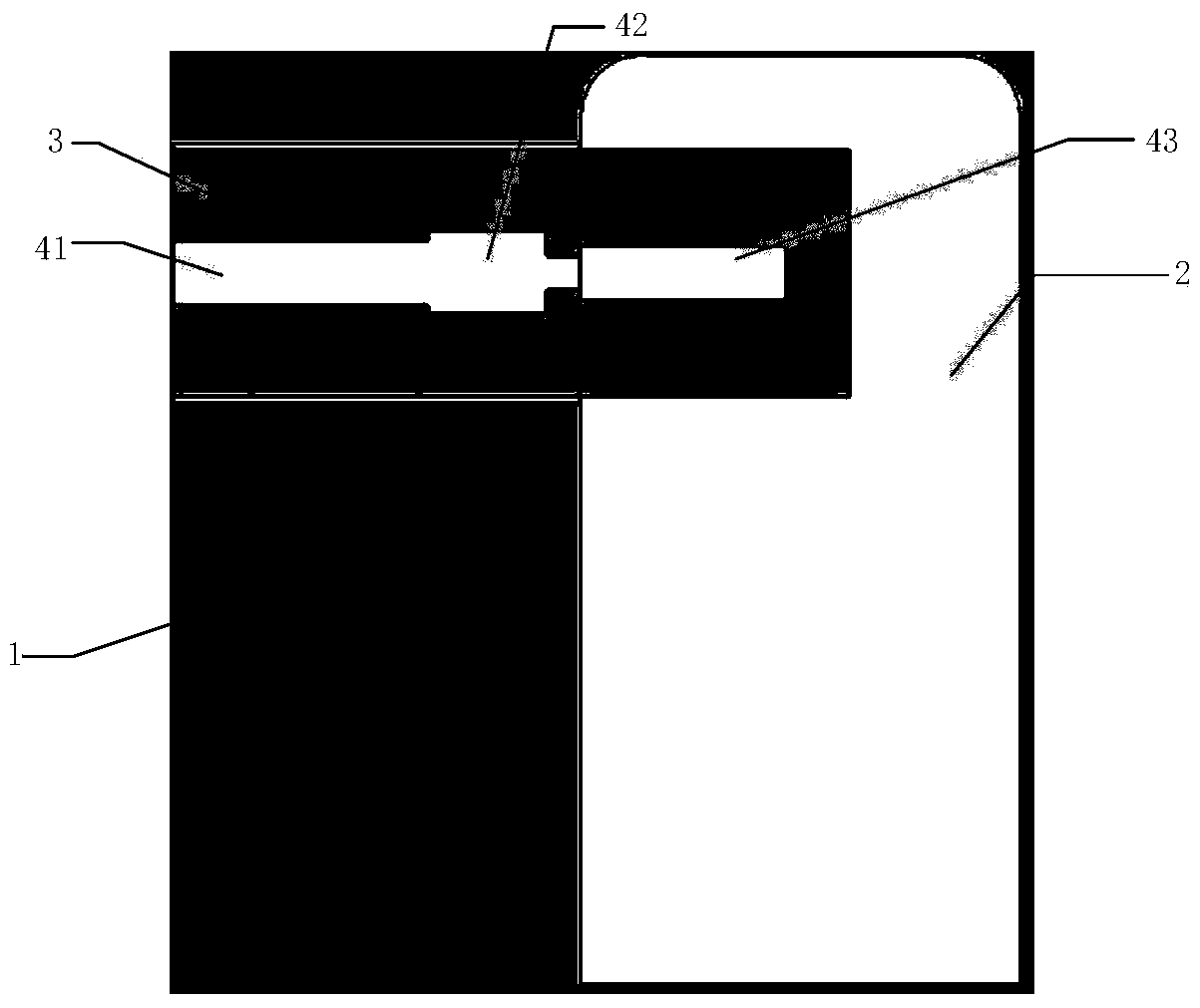

The invention relates to the field of power semiconductor devices, in particular to an injection reinforced bipolar transistor of an insulated gate. The injection reinforced bipolar transistor comprises a p-type collector electrode, wherein a carrier diffusion layer is arranged on the p-type collector electrode. A plurality of grooves are longitudinally arranged on the carrier diffusion layer. A plurality of rows of p-type active zones and a plurality of rows of p-type non-active zones are transversely arranged on the carrier diffusion layer and form a strip-shaped p-type base region. The injection reinforced bipolar transistor is provided with strip-shaped periodic separate cell structures, emitting electrodes are correspondingly in separate shapes, accordingly holes generate the accumulative effect in the zones not covered by the emitting electrodes, further the carrier concentration of the zones close to the grooves is improved, and the on-state voltage drop is reduced.

Owner:中国东方电气集团有限公司

A trench type MOS device and its manufacturing method

ActiveCN108962989BGuaranteed stabilityHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesPolysilicon gateBody region

The invention provides a groove-type MOS (Metal-Oxide-Semiconductor) device and a manufacturing method thereof. The groove-type MOS device at least includes a first conductive heavily doped substrate,a first conductive lightly doped epitaxial layer on the first conductive heavily doped substrate, a plurality of first conductive source regions, a plurality of grooves, a gate oxide layer and a polysilicon gate which are formed in the each groove, a second conductive lightly doped body region formed on the upper portion of the first conductive lightly doped epitaxial layer, a cellular region contact hole formed in the second conductive lightly doped body region, an insulating dielectric block covering the polysilicon gate in the groove of the cellular region, a second conductive heavily doped body contact region formed between two adjacent first conductive source regions of the cellular region, and a metal source electrode formed in the contact hole of the cellular region, wherein the plurality of first conductive source regions and the plurality of grooves are formed on the upper portion of the first conductive lightly doped epitaxial layer at intervals. The groove-type MOS device can guarantee stability of the device while improving the device density and reducing the conduction resistance.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

PMOS (p-channel metal-oxide-semiconductor field-effect transistor) source/drain region ion implantation method and corresponding device manufacturing method

ActiveCN102437028BReduce processing difficultyShort rangeSemiconductor/solid-state device manufacturingHigh dosesField-effect transistor

The invention discloses a PMOS (p-channel metal-oxide-semiconductor field-effect transistor) source / drain region ion implantation method and a corresponding device manufacturing method. Since an amorphous carbon layer can be completely removed without causing silicon sinking, when the amorphous carbon layer is used as a pad layer for PMOS source / drain region ion implantation, the range of implanted impurities in the silicon substrate can be reduced on the premise of basically not changing the implanted impurity distribution, thereby obtaining an ultrashallow junction which is more shallow than that obtained by a conventional method; or the implanted energy is increased on the premise of keeping the depth of the ultrashallow junction unchanged, thereby relieving the demands of technique for high-dose low-energy ion implantation to some extent, and lowering the technical difficulty of PMOS source / drain region ion implantation. The PMOS source / drain region ion implantation method and the corresponding device manufacturing method provided by the invention can be used for improving the ion implantation technique of the ultrashallow junction in the PMOS source / drain region, and lowering the technical difficulty.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

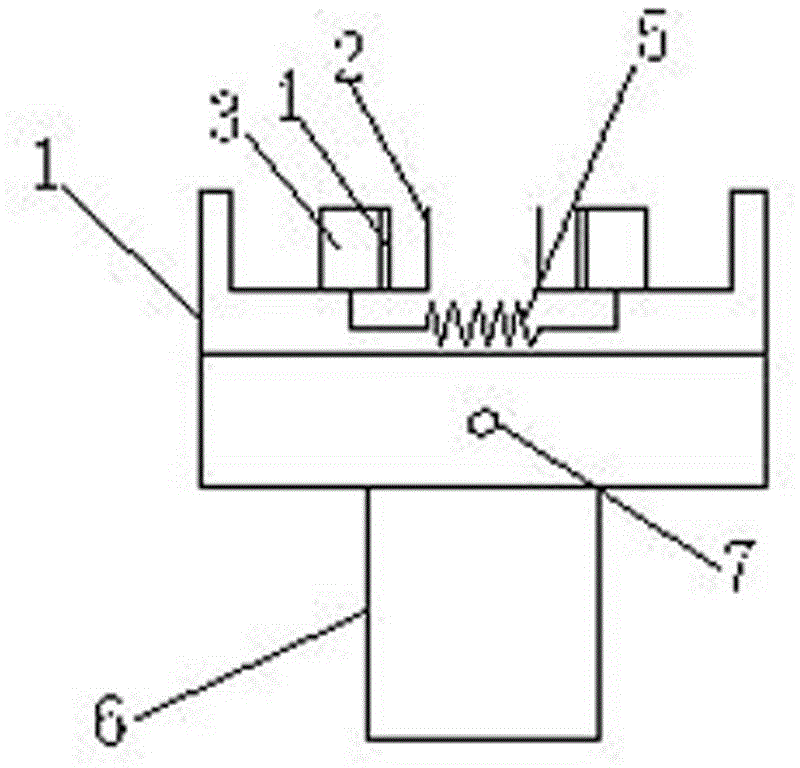

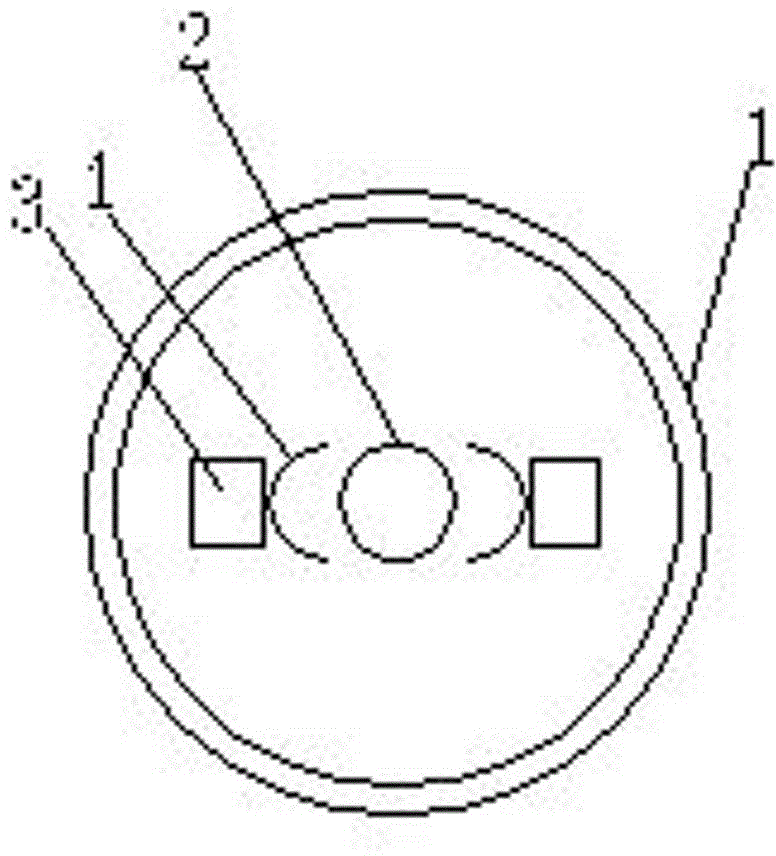

Bottle preform carrier based on spring fastening, and bottle blowing machine

The invention discloses a bottle preform carrier based on spring fastening. The top of the bottle preform carrier is provided with a bottle preform fixing column; slide blocks are respectively arranged at left and right sides of the bottle preform fixing column; the sides, close to the bottle preform fixing column, of the slide blocks are provided with arc catches matching with the shape of the bottle preform fixing column; a spring is arranged below the bottle preform fixing column; and two sides of the bottle preform fixing column are respectively connected with the slide blocks. The invention also discloses a bottle blowing machine. The bottle blowing machine can fix a bottle preform through the spring without other electrical control, enables a produced bottle to be conveniently taken off, is simple in structure, does not increase process difficulty and improves work efficiency.

Owner:XIAN TAIHUI ELECTRONICS TECH CO LTD

Display screen design method and device

ActiveCN112434455AThickness unchangedImprove color castSolid-state devicesDesign optimisation/simulationComputer hardwareComputer graphics (images)

The invention provides a display screen design method and device, and the method comprises the steps: determining a first grid line disposed between a first pixel and a second pixel in a target display screen, enabling the area of the first pixel to be larger than that of the second pixel, enabling the first pixel to be adjacent to the second pixel, and according to a first preset shielding view angle, determining a first interval between the first pixel and the first grid line, the first interval being smaller than a second interval between the second pixel and the first grid line, and then determining the position of the first grid line between the two pixels according to the first interval, i.e., adjusting the position of the first grid line, so that the grid line is close to the pixelwith a larger area, and the pixel with a larger area is obtained. The grid lines are separated from the pixels with smaller areas, so that the shielding of the grid lines to the pixels with differentsizes is approximately consistent, the color cast phenomenon of a large viewing angle is improved, the thickness of the packaging layer is not changed, the product performance is not reduced, the width of the grid lines is not changed, and the process difficulty is not increased.

Owner:HEFEI VISIONOX TECH CO LTD

Film bulk acoustic wave resonator and preparation method thereof

InactiveCN101465628BHigh application frequencyReduce the requirements of the manufacturing process for equipmentImpedence networksThin-film bulk acoustic resonatorBulk acoustic wave

The invention discloses a thin film bulk acoustic wave resonator which comprises a substrate, a buffer layer, a piezoelectric layer and electrodes, and is characterized in that 1. A smooth concave groove and the buffer layer are arranged on the upper end surface of the substrate; the buffer layer crosses the concave groove and forms an air gap provided with a smooth upper convex edge with the substrate, and completely covers the air gap; the height of the lower top surface of the air gap is less than that of the substrate, and the air gap has flat surface and even change edge; 2. The edge of the buffer layer, which is contacted with the air gap and is close to the substrate is in smooth and outer-convex shape; the piezoelectric layer is arranged on the buffer layer; the electrodes includea bottom electrode and a top electrode; the bottom electrode is arranged in the piezoelectric layer on the buffer layer; the top electrode is arranged on the piezoelectric layer. The thin film bulk acoustic wave resonator has ingenious structure; a FBAR with stable structure and low loss can be fabricated on the substrate through the method, and the CMP process is avoided, so the thin film bulk acoustic wave resonator can be integrated into a CMOS chip conveniently.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A kind of high creep resistance ultra-high molecular weight polyethylene fiber and preparation method thereof

ActiveCN113502556BReduce oxidationPrevent oxidationRadioactive element fibre treatmentMonocomponent polyolefin artificial filamentFiberPolymer science

Owner:WUHAN TEXTILE UNIV +2

Transistor and method for forming the transistor

ActiveCN104425604BReduce RC delayRun fastTransistorSemiconductor/solid-state device manufacturingInsulation layerGate dielectric

Owner:SEMICON MFG INT (SHANGHAI) CORP

A microbolometer with high filling factor and its preparation method

ActiveCN106124066BSimple preparation processSimple manufacturing processPyrometry using electric radation detectorsRadiometerElectrical connection

Owner:YANTAI RAYTRON TECH

A kind of thin film transistor and array substrate

ActiveCN105405892BReduce leakage currentImprove afterimage problemTransistorSolid-state devicesInsulation layerOhmic contact

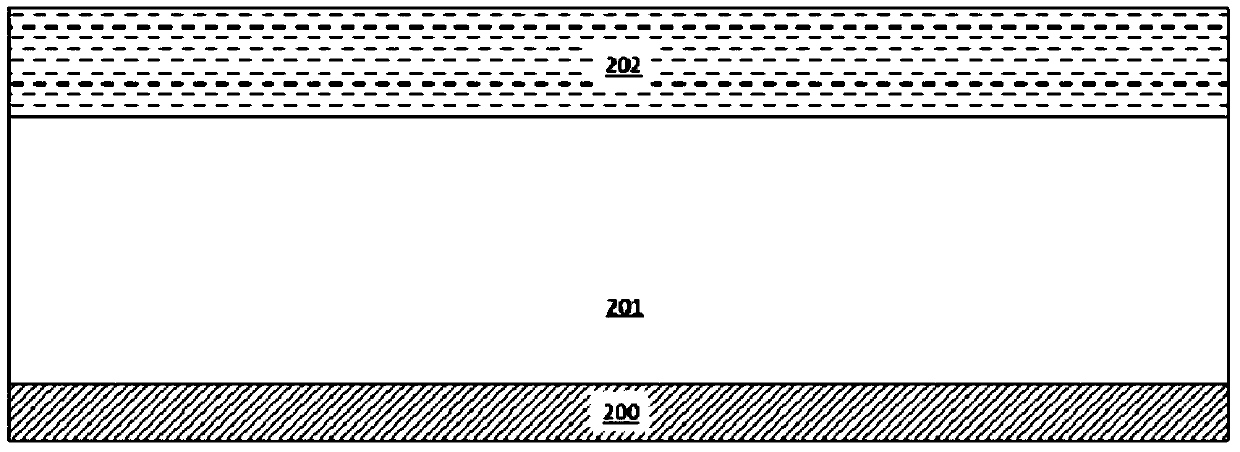

A thin film transistor and an array substrate. The thin film transistor comprises: a gate electrode (202); a gate electrode insulation layer (203) formed on the gate electrode and covering the gate electrode; an active layer (204) formed on the gate electrode insulation layer; a first material layer (205) formed on the active layer; and a source / drain electrode (206) formed on the first material layer. The first material layer comprises: a first ohmic contact layer (205a), a second ohmic contact layer (205c) and a high impedance interlayer (205b). The high impedance interlayer is formed between the first ohmic contact layer and the second ohmic contact layer, and an impedance thereof is greater than impedances of the first ohmic contact layer and the second ohmic contact layer. By means of the thin film transistor, a leakage current existing between a source / drain electrode and an active layer can be effectively reduced, and the manufacturing process therefor is simple.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com