Patents

Literature

66results about How to "Improve afterimage problem" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

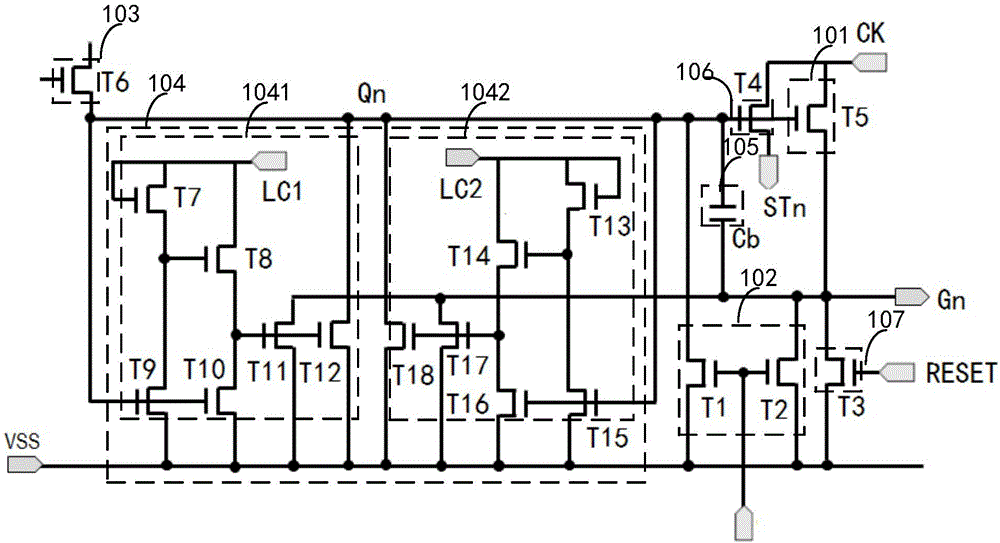

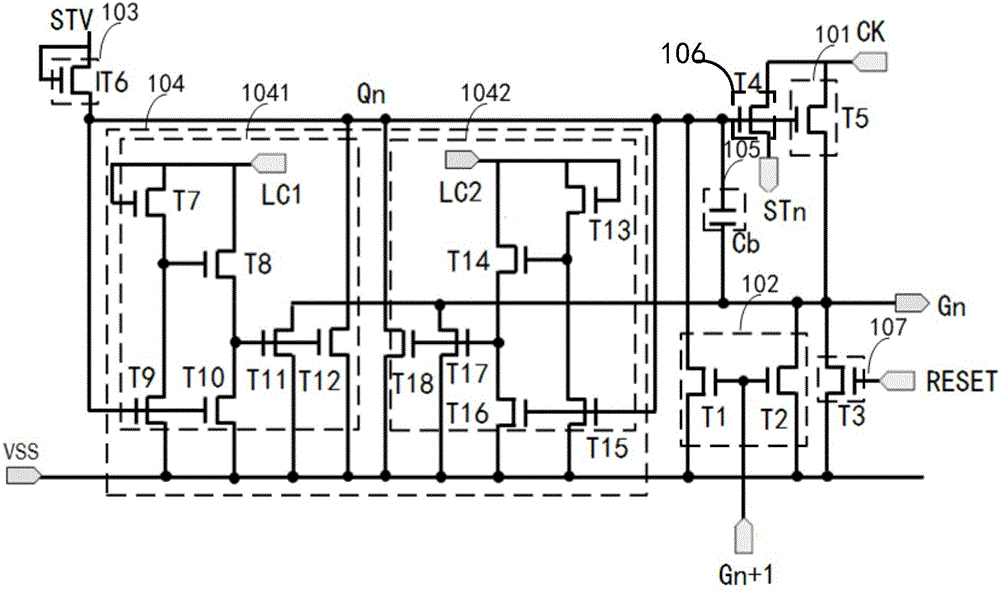

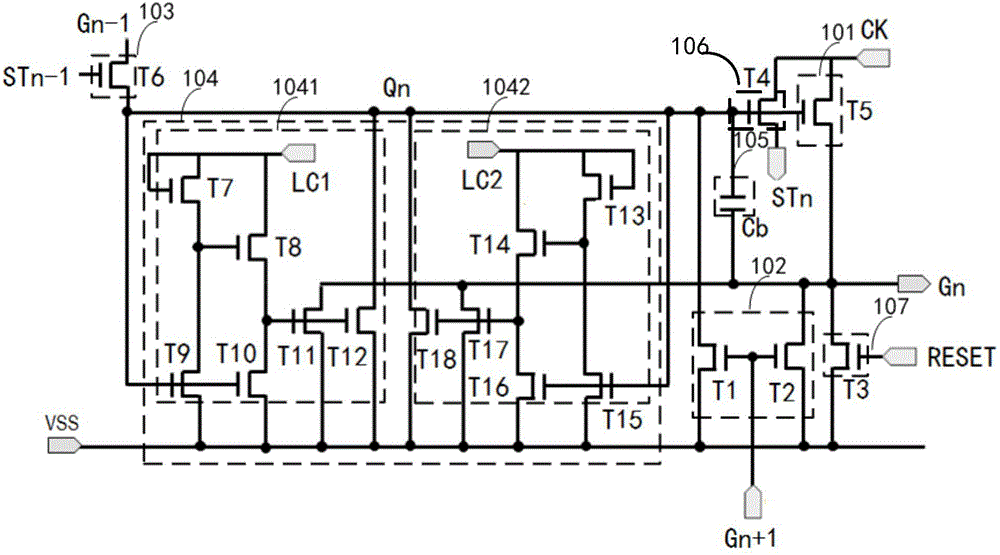

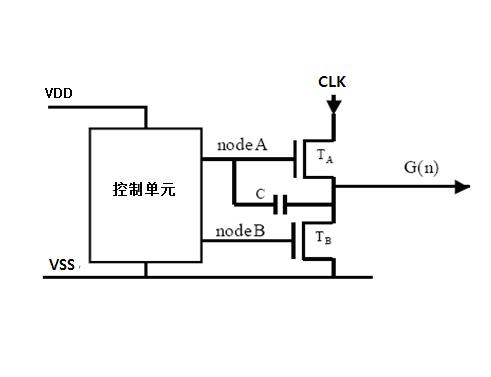

GOA drive circuit and liquid crystal display device

InactiveCN106328084AImprove afterimage problemStatic indicating devicesCapacitanceLiquid-crystal display

The invention discloses a GOA drive circuit and liquid crystal display device,which comprises a plurality of cascaded GOA units outputting the gate-drive signals to the Nth horizontal scanning line according to the Nth GOA units;the Nth GOA units comprise a pull-up module,a pull-down module,a pull-up control module,a pull-down maintenance module,a bootstrap capacitor module and a reset module;the pull-up module,the pull-down module,the pull-down maintenance module and the the bootstrap capacitor module respectively are connected to the Nth level gate signal point Qn and the Nth horizontal scanning line;the pull-up control module is connected to the Nth gate signal point Qn;the reset module comprises a first end,a second end,and a control end and the first end is connected to horizontal scanning line Gn.The invention can remove the blur when the liquid crystal display device is turned off.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

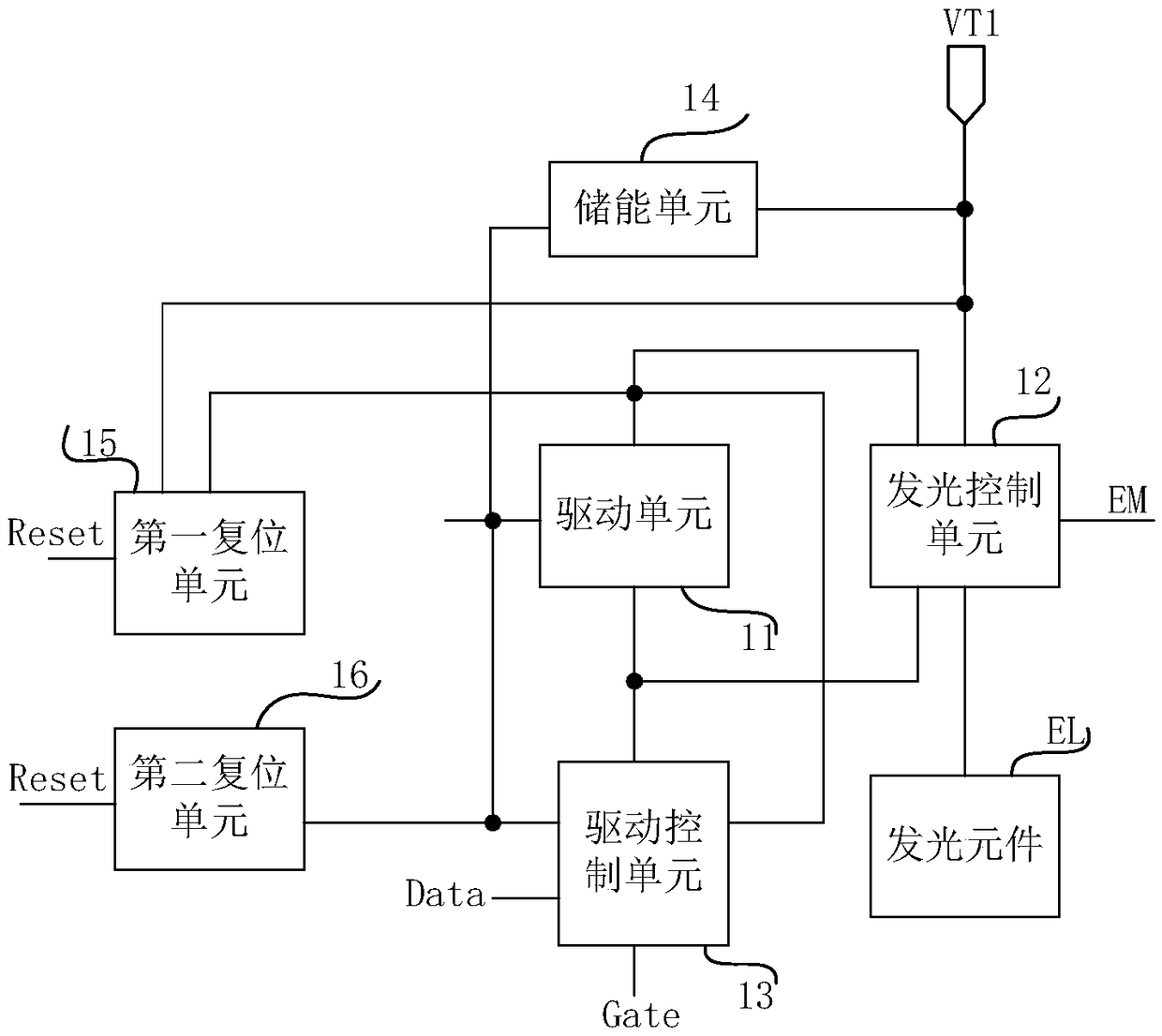

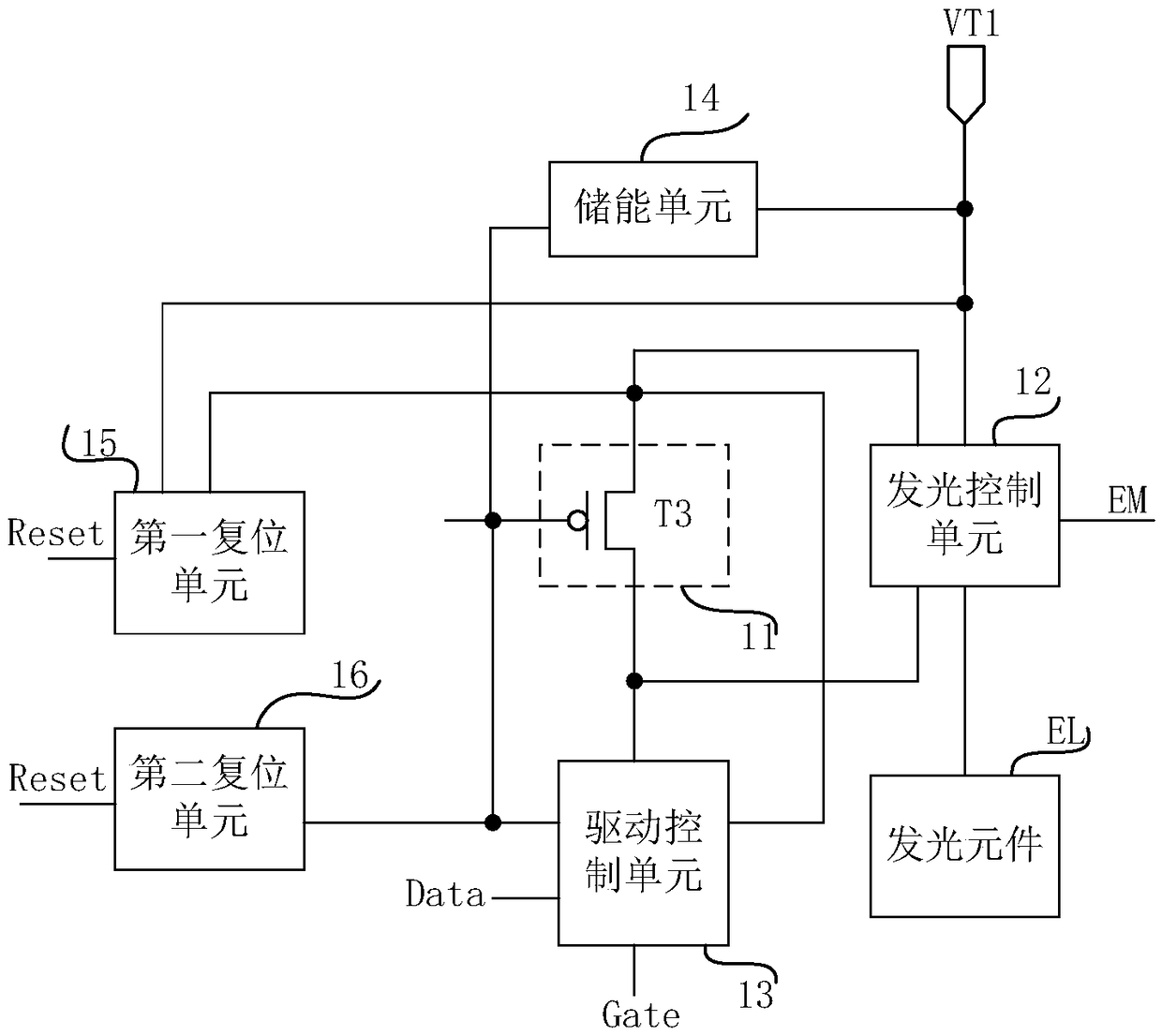

Pixel circuit, pixel drive method and display device

InactiveCN109256094AReduce hysteresisImprove afterimage problemStatic indicating devicesControl lineDisplay device

The invention provides a pixel circuit, a pixel drive method and a display device. The pixel circuit comprises a light-emitting element, a drive unit, a light emitting control unit, a drive control unit, an energy storage unit, a first reset unit and a second reset unit, wherein the first reset unit is used for controlling first voltage output by a first voltage line to be written into a first endof the drive unit under the control of a rest control line; the second reset unit is used for controlling initial voltage output by an initial voltage line to be written into a control end of the drive unit under the control of the rest control line; and the drive unit is used for driving the light-emitting element to emit light under the control of the control end of the drive unit. With the pixel circuit, the pixel drive method and the display device, the problem of residual image display caused by the retardation effect of a drive transistor of the drive unknit in the prior art is solved.

Owner:BOE TECH GRP CO LTD +1

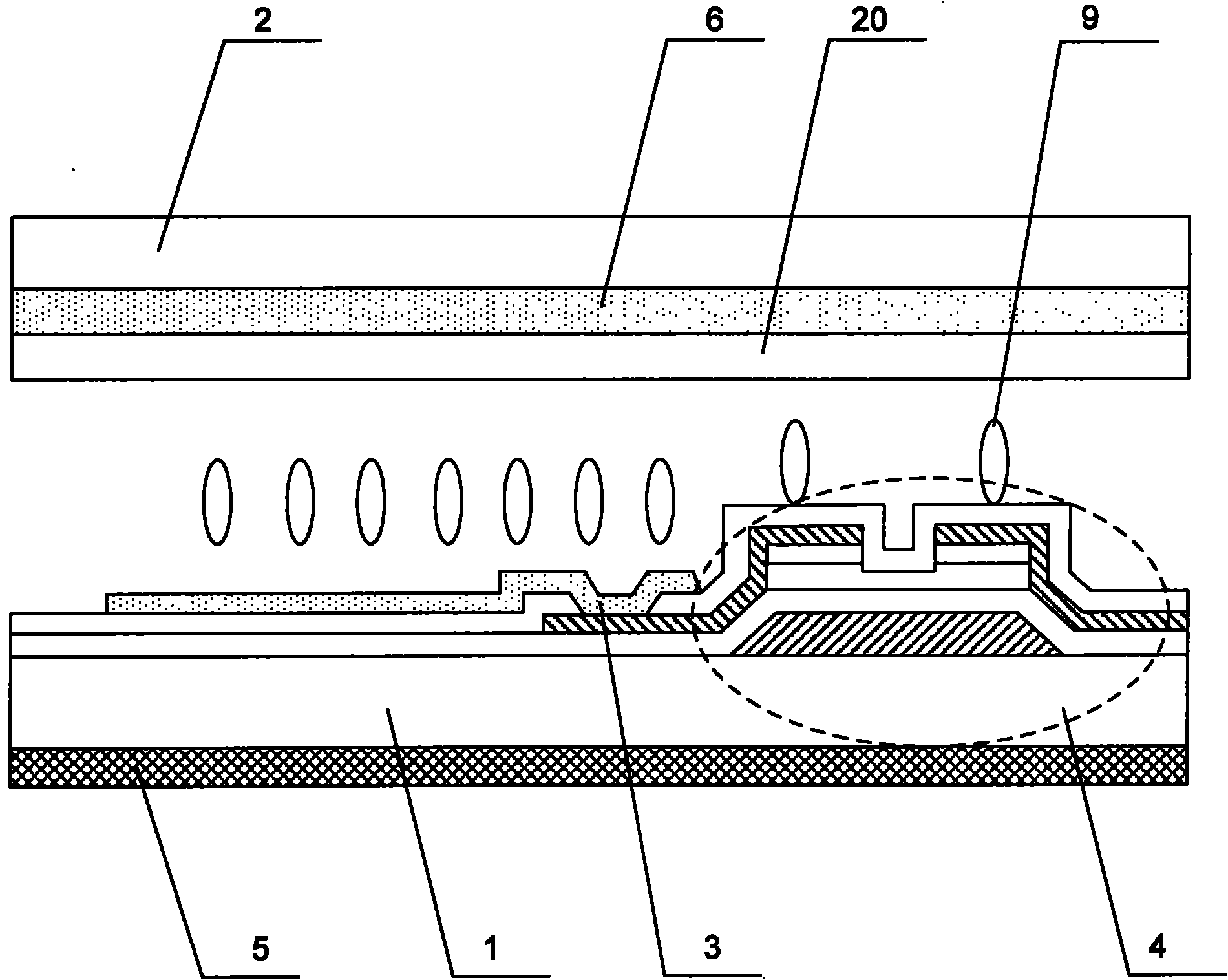

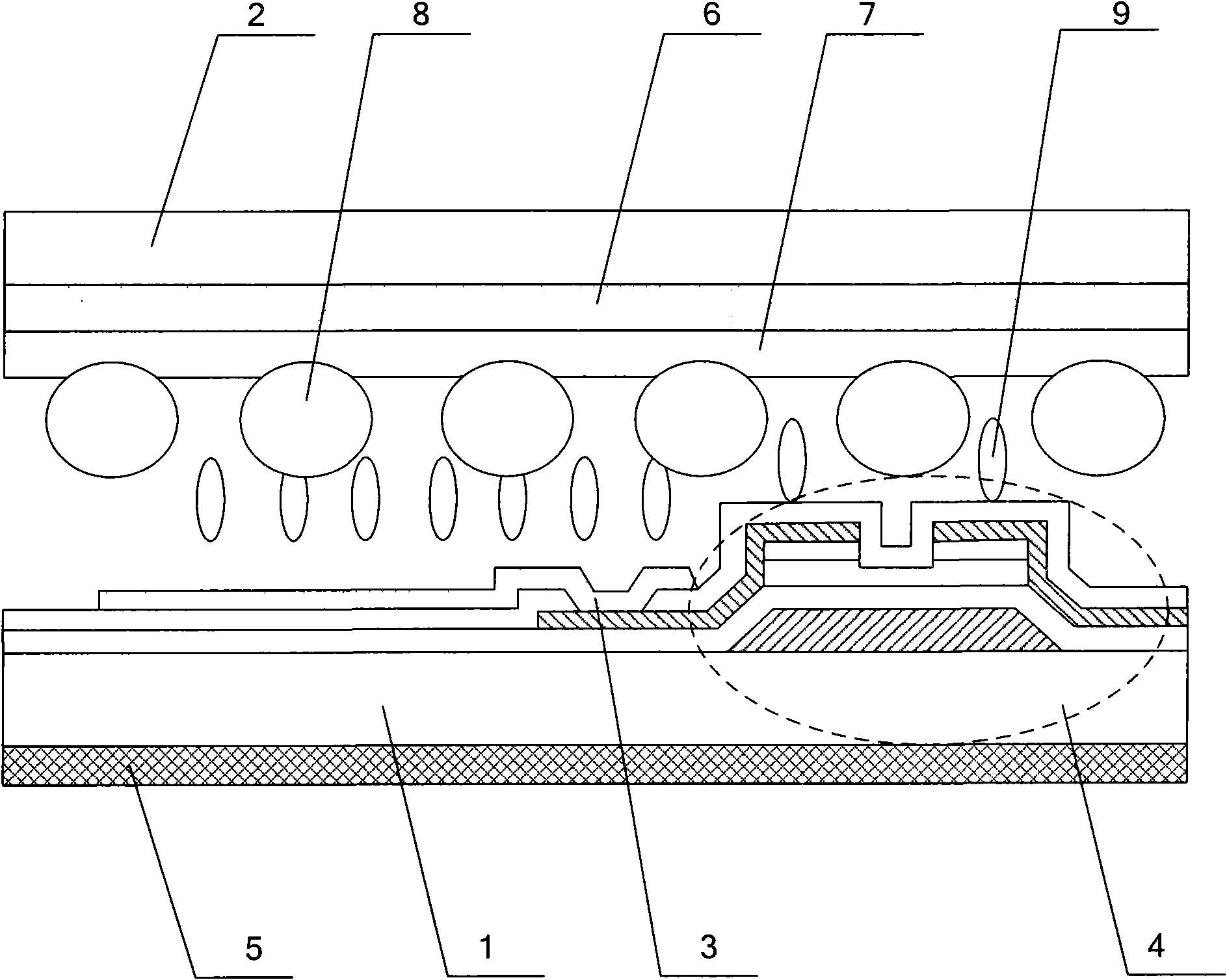

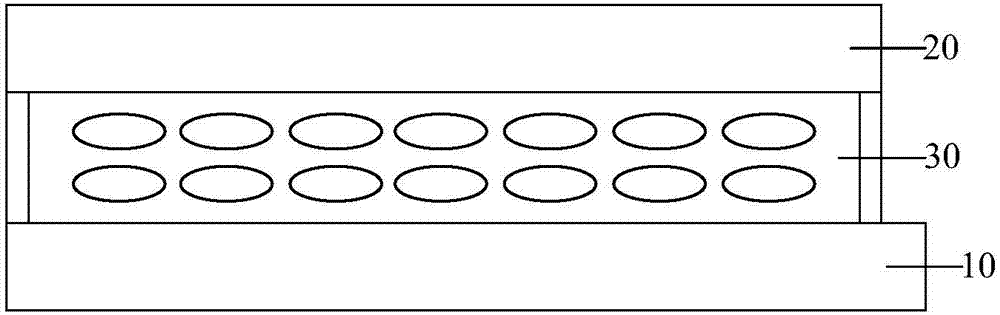

Total-reflection liquid crystal display

ActiveCN101852942AImprove efficiencyTake advantage ofNon-linear opticsRefractive indexReflective layer

The invention relates to a total-reflection liquid crystal display, comprising a first substrate and a second substrate of which cassettes are mutually opposite to each other, wherein liquid crystal molecules are clamped between the first substrate and the second substrate; the first substrate comprises a light adsorbing layer for adsorbing ray; the second substrate comprises a transparent electrode and a reflecting layer, wherein the transparent electrode is formed on the second substrate for forming voltage difference between the transparent electrode and the pixel electrode to control liquid crystal inversion, the reflecting layer is arranged between the transparent electrode and the liquid crystal, and the refractive index of the reflecting layer is between the ordinary light refractive index and the abnormal light refractive index of the liquid crystal. The total-reflection liquid crystal display of the invention has high illumination and contrast ratio. Compared with the liquid crystal display adopting the electronic ink technology in the prior art, the invention improves incidental images caused by electrostatic adhesion.

Owner:BOE TECH GRP CO LTD +1

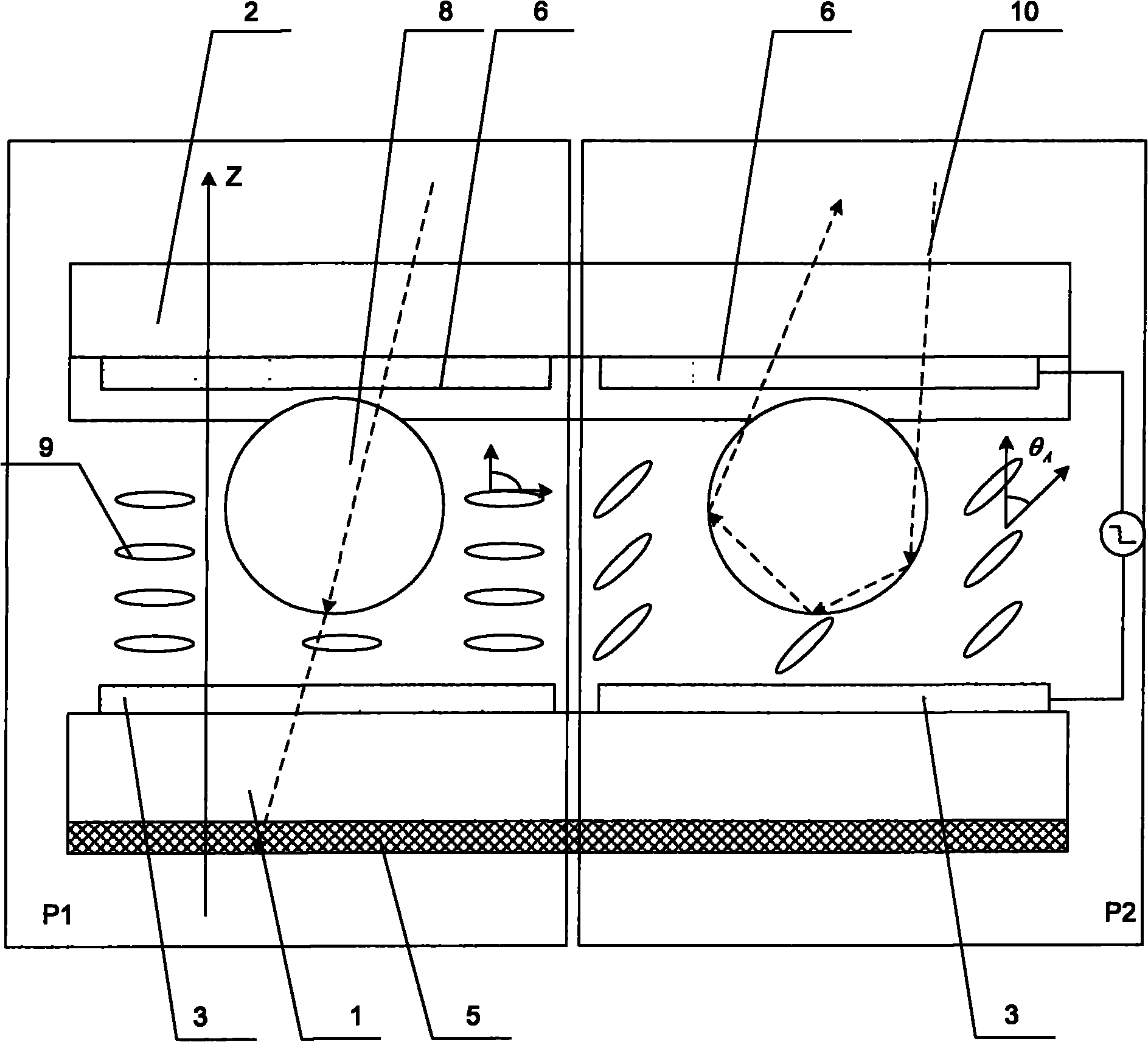

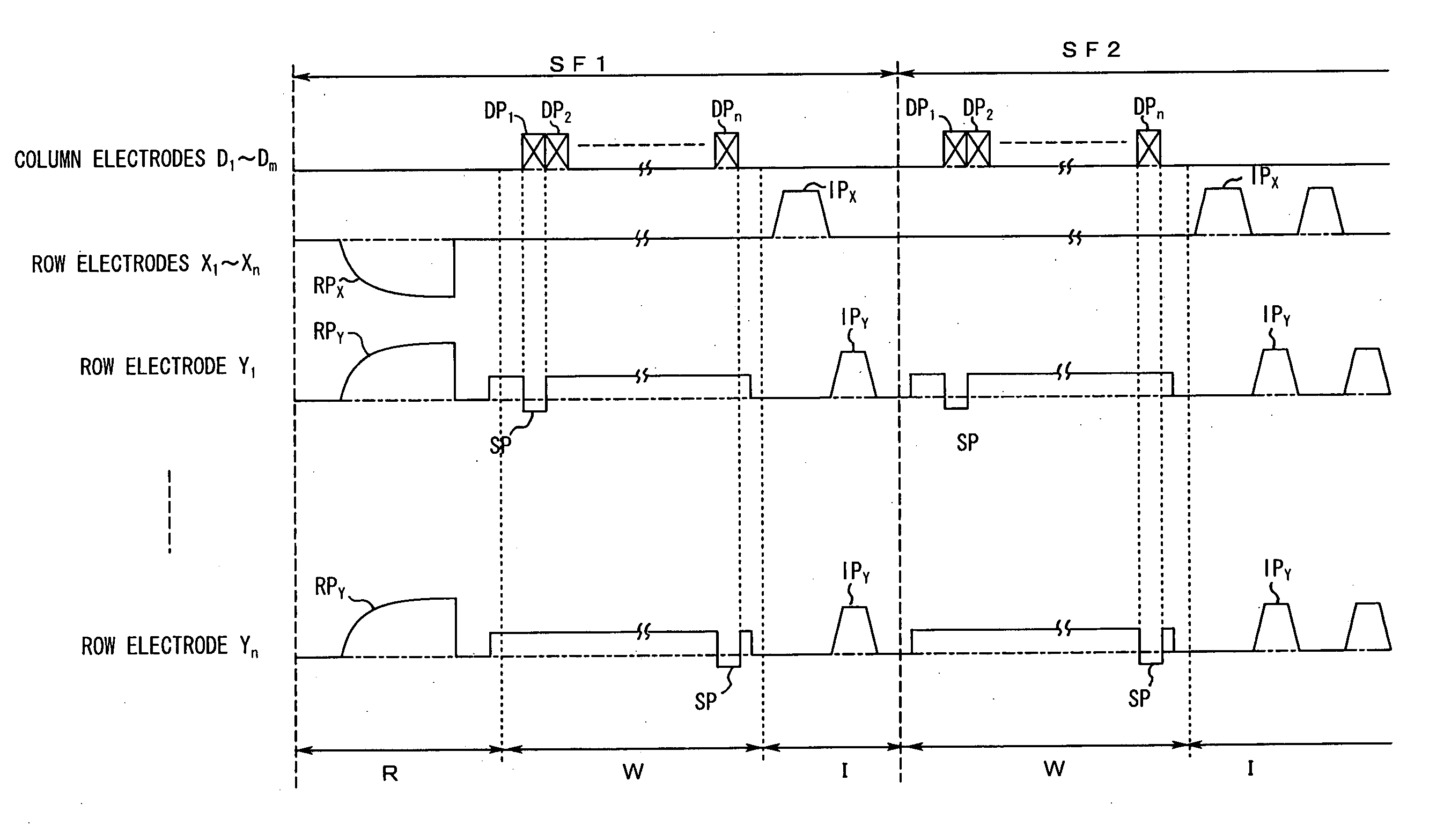

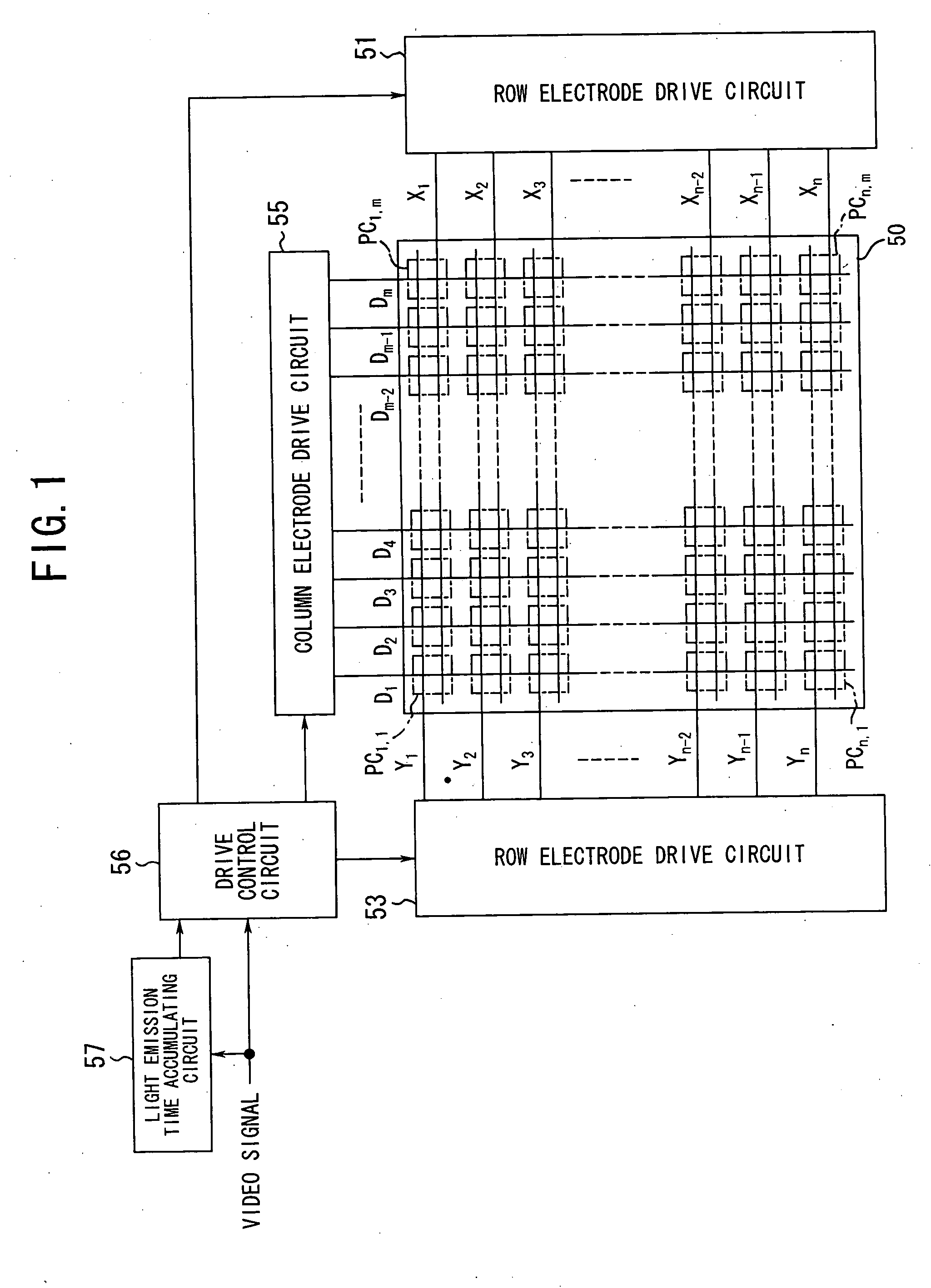

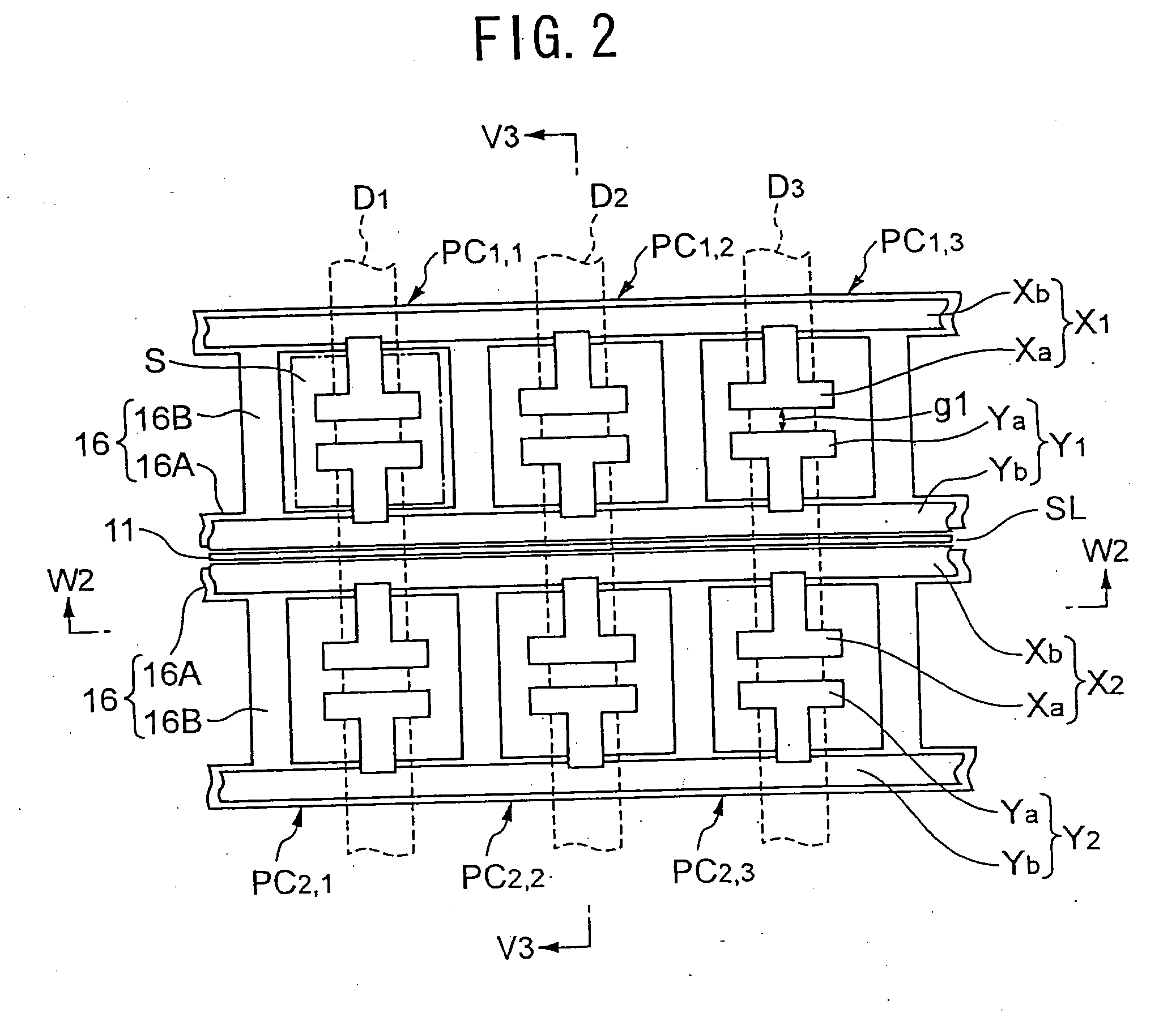

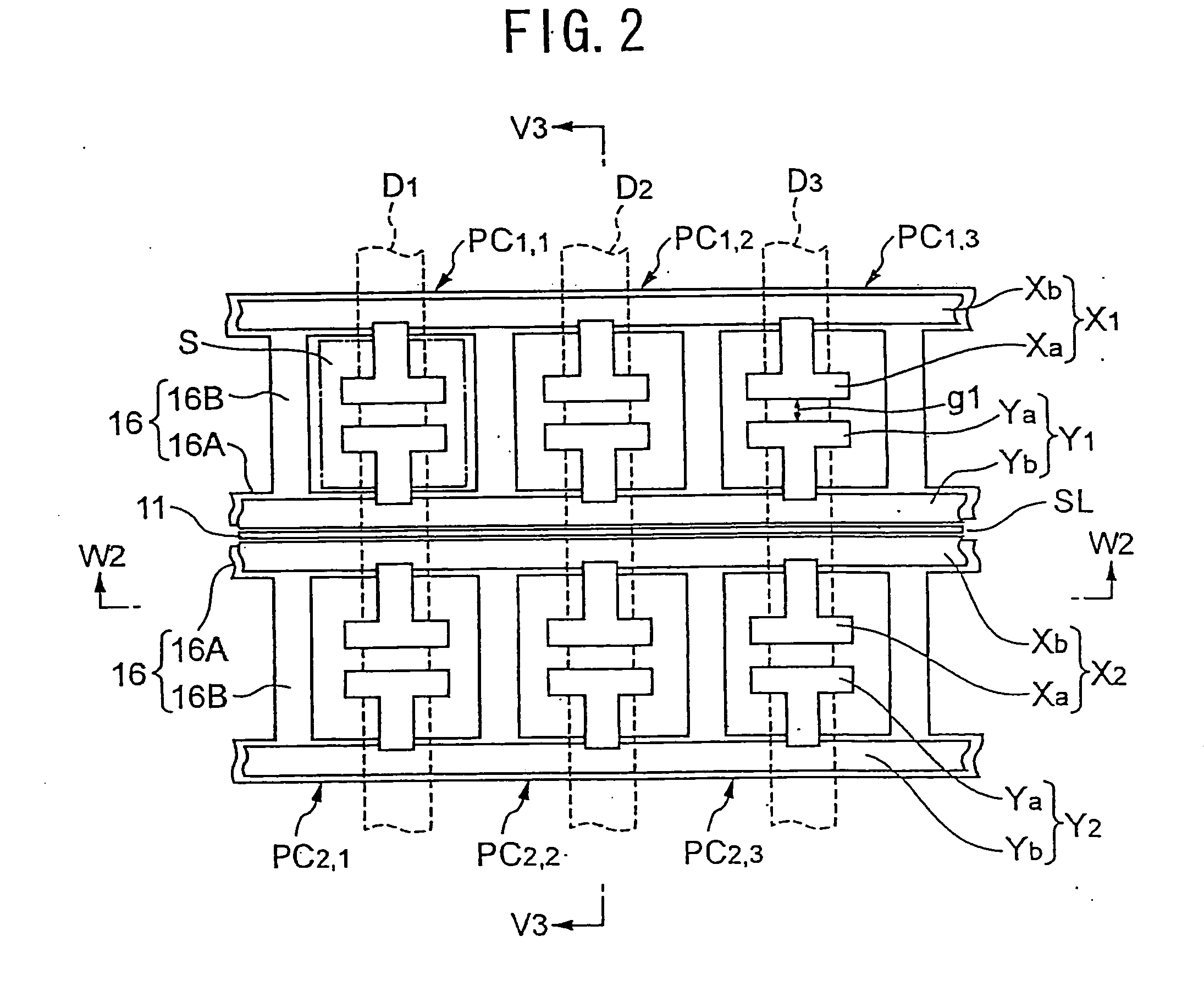

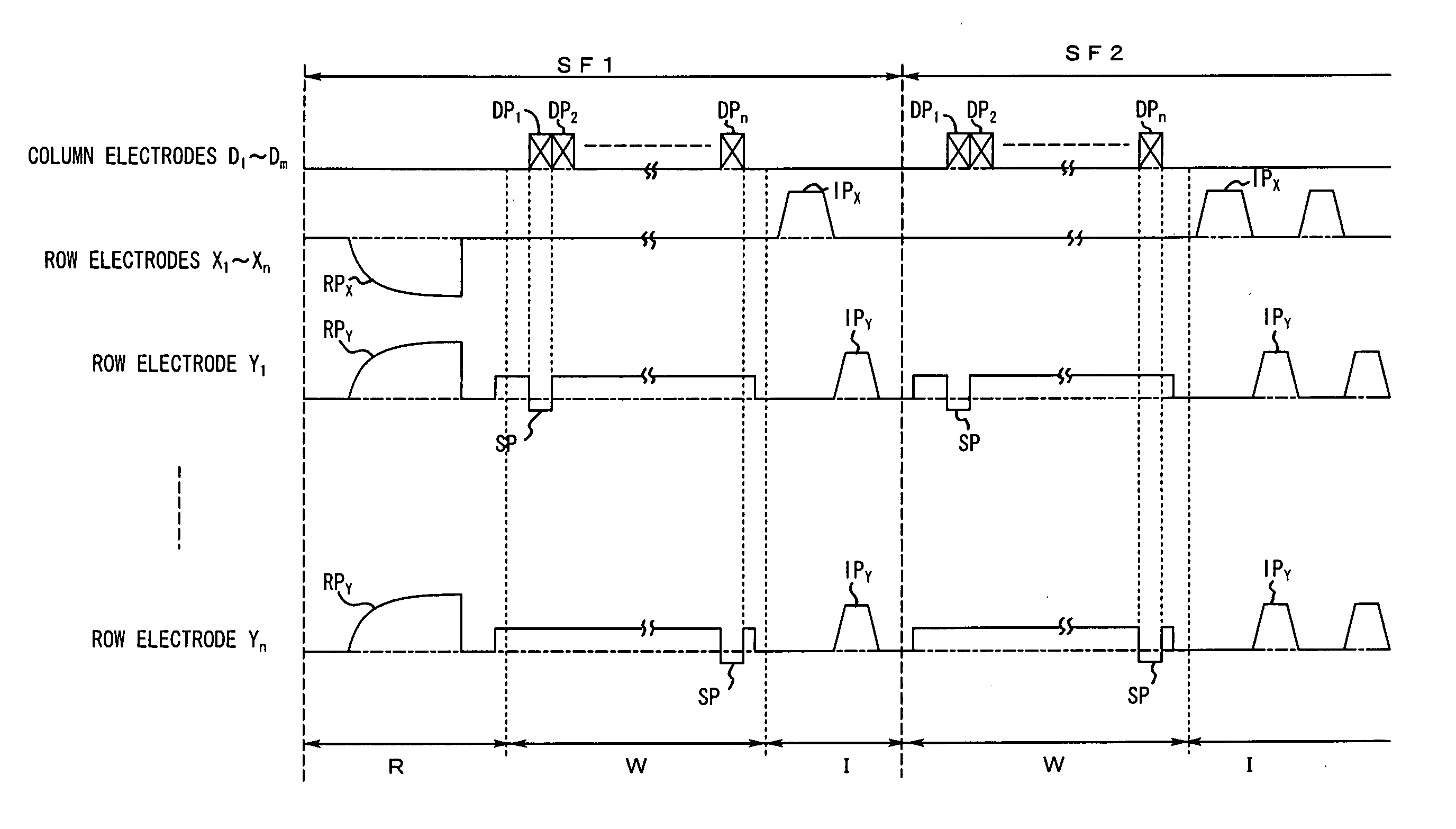

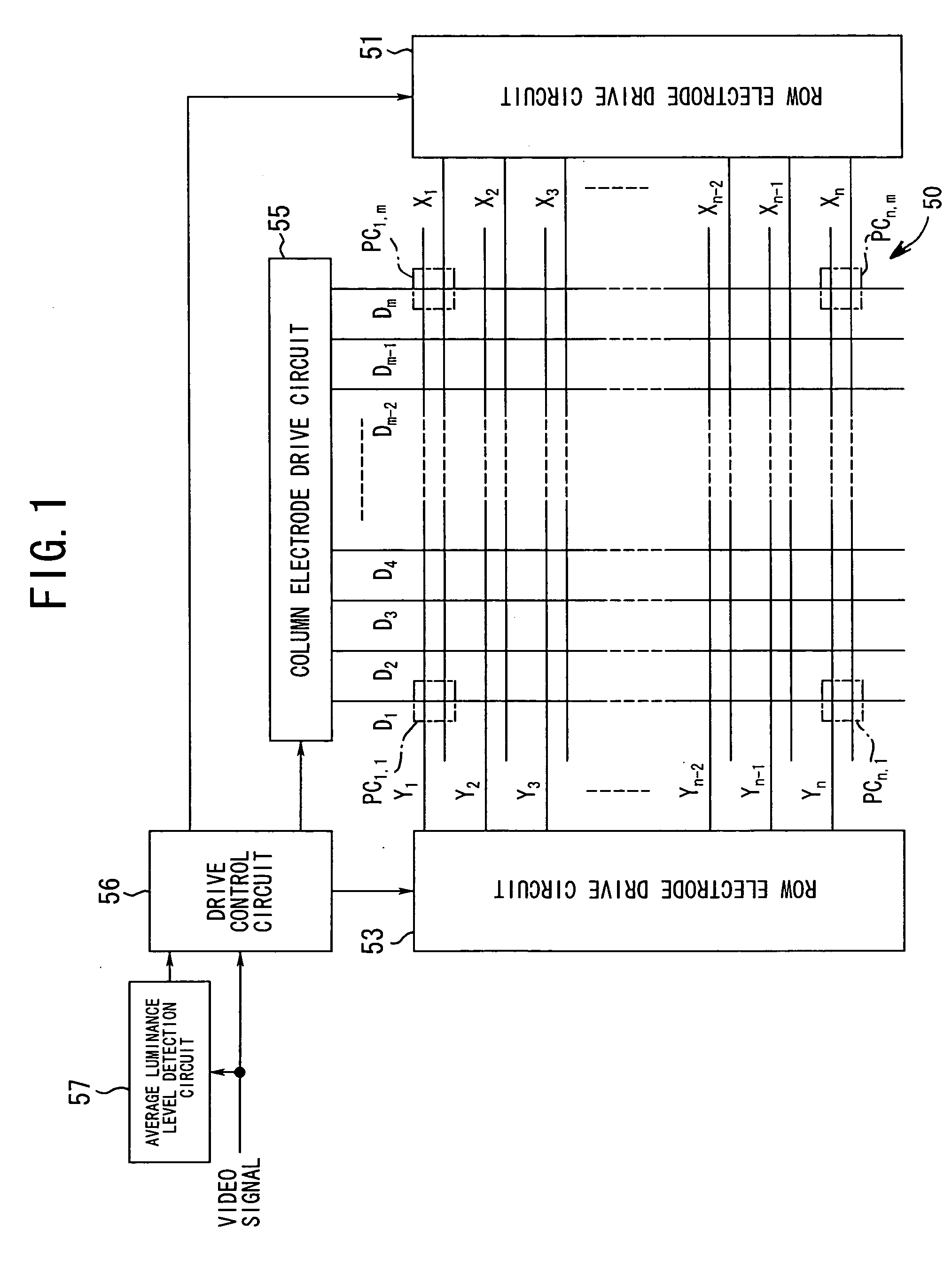

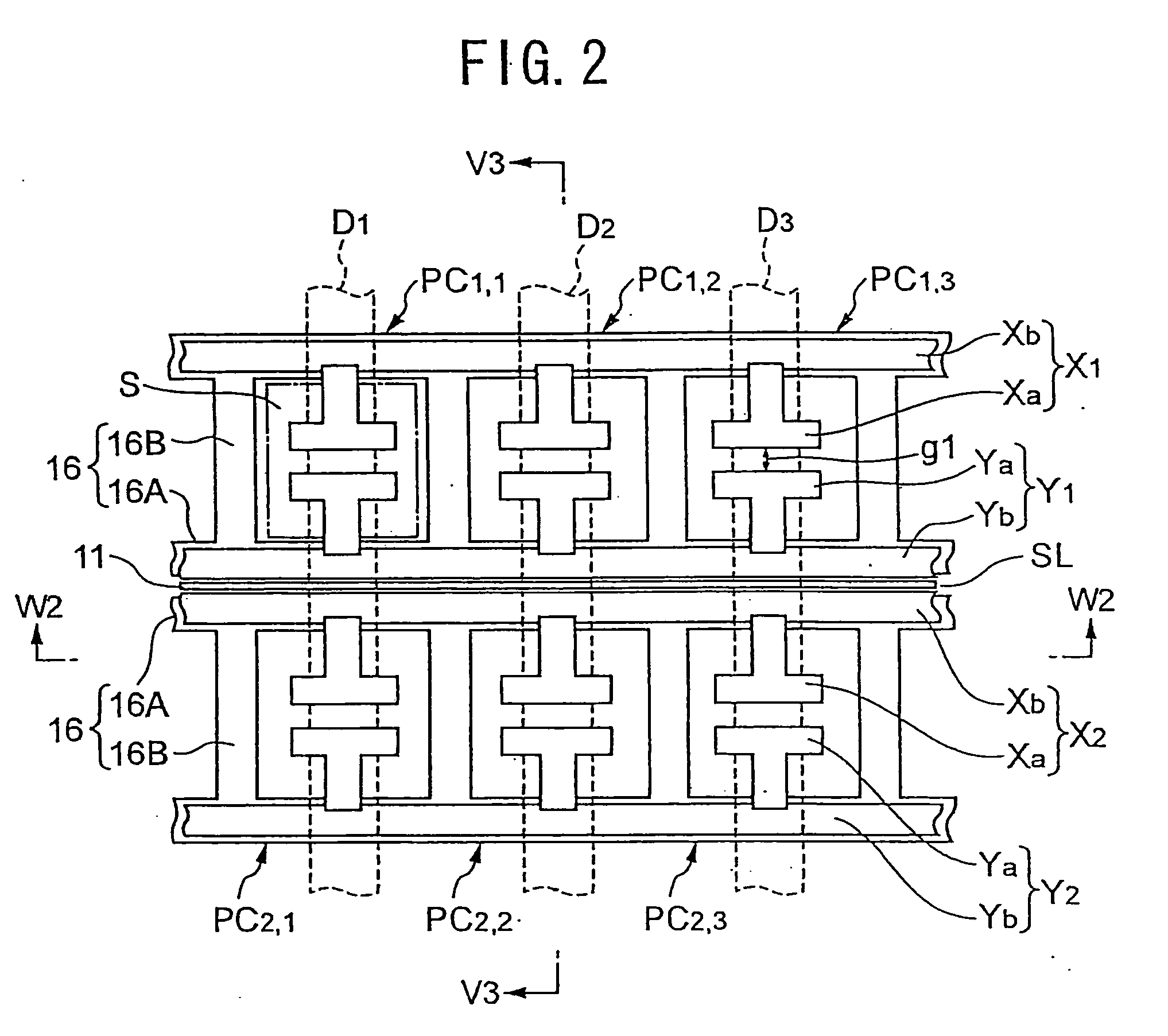

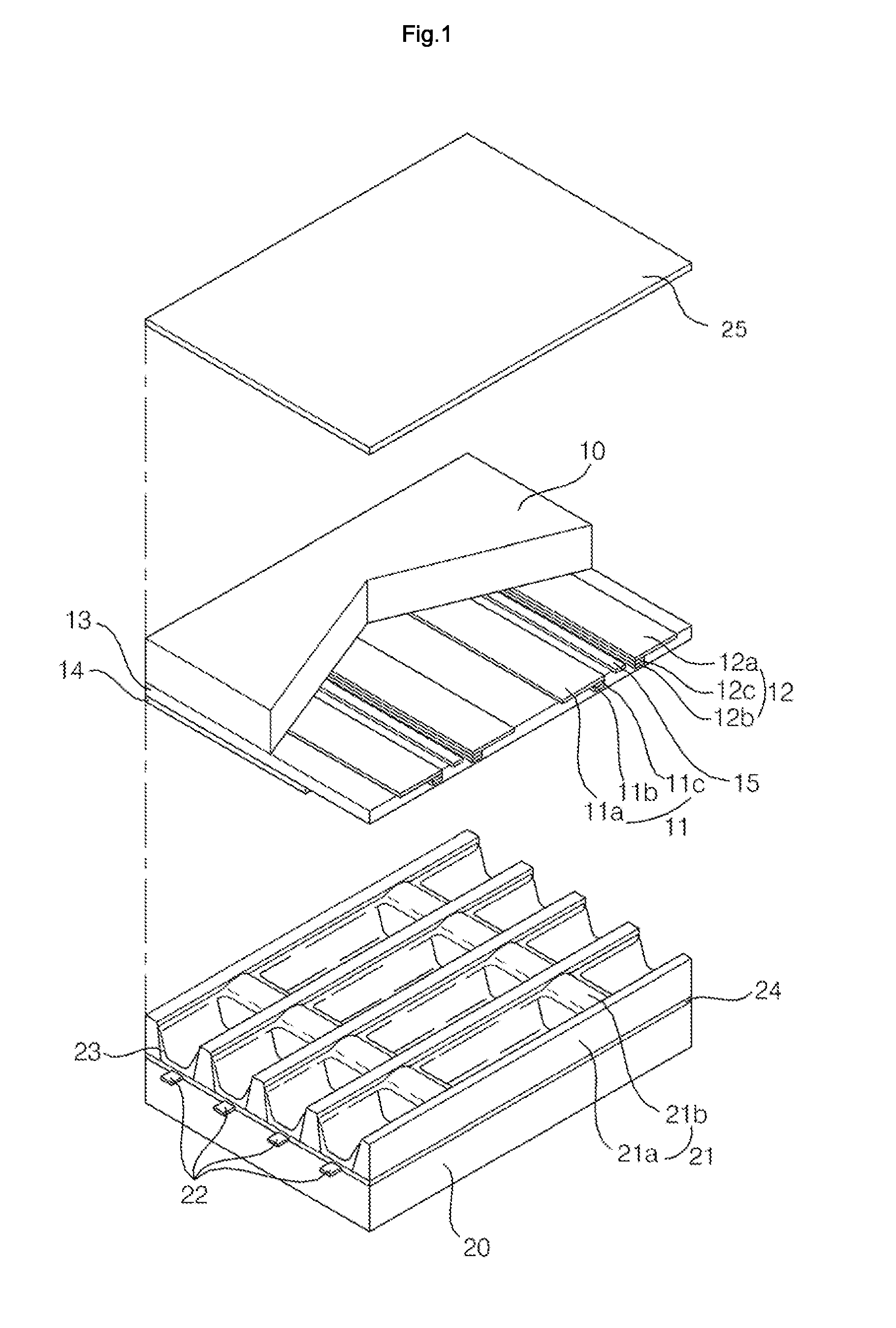

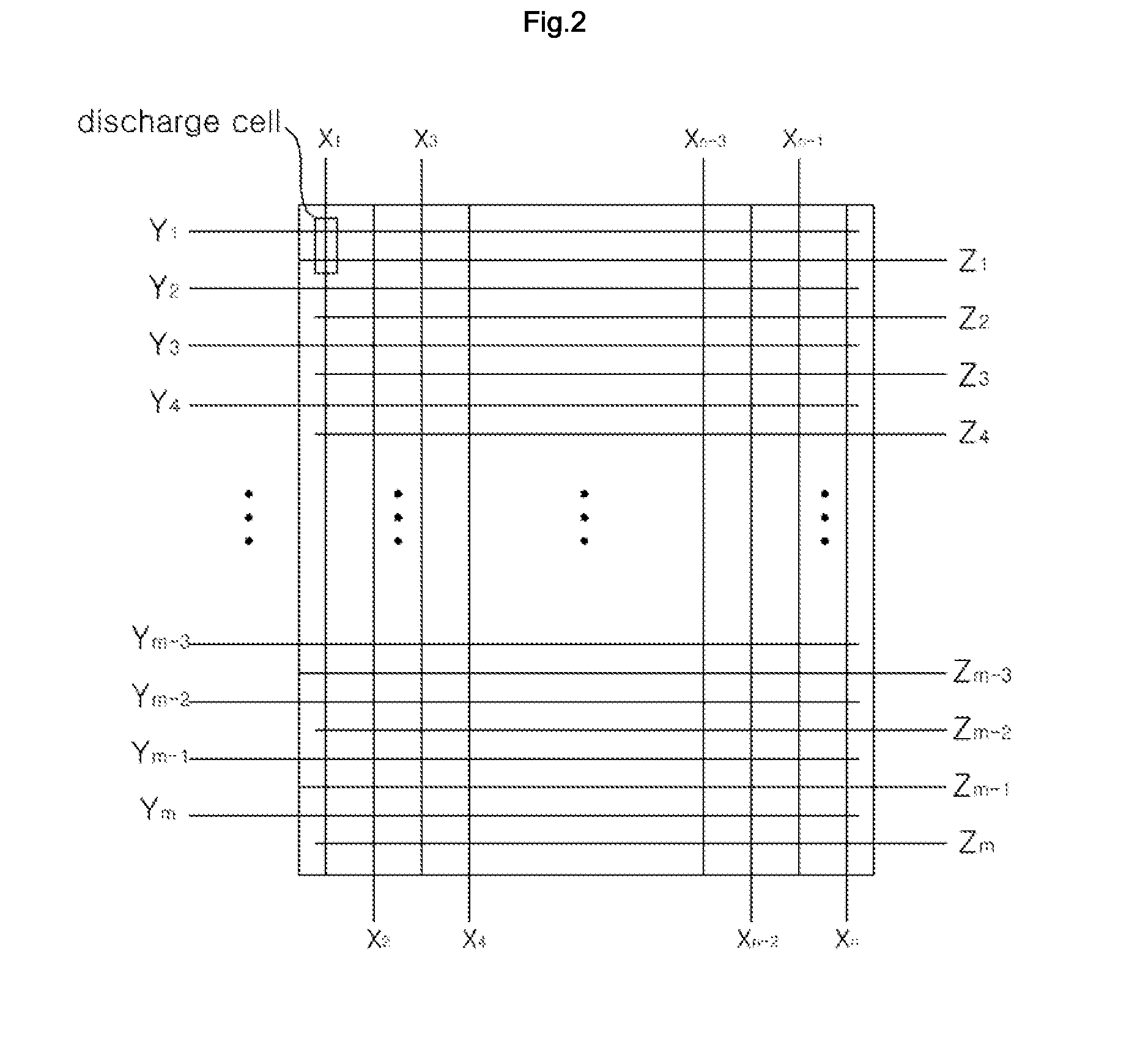

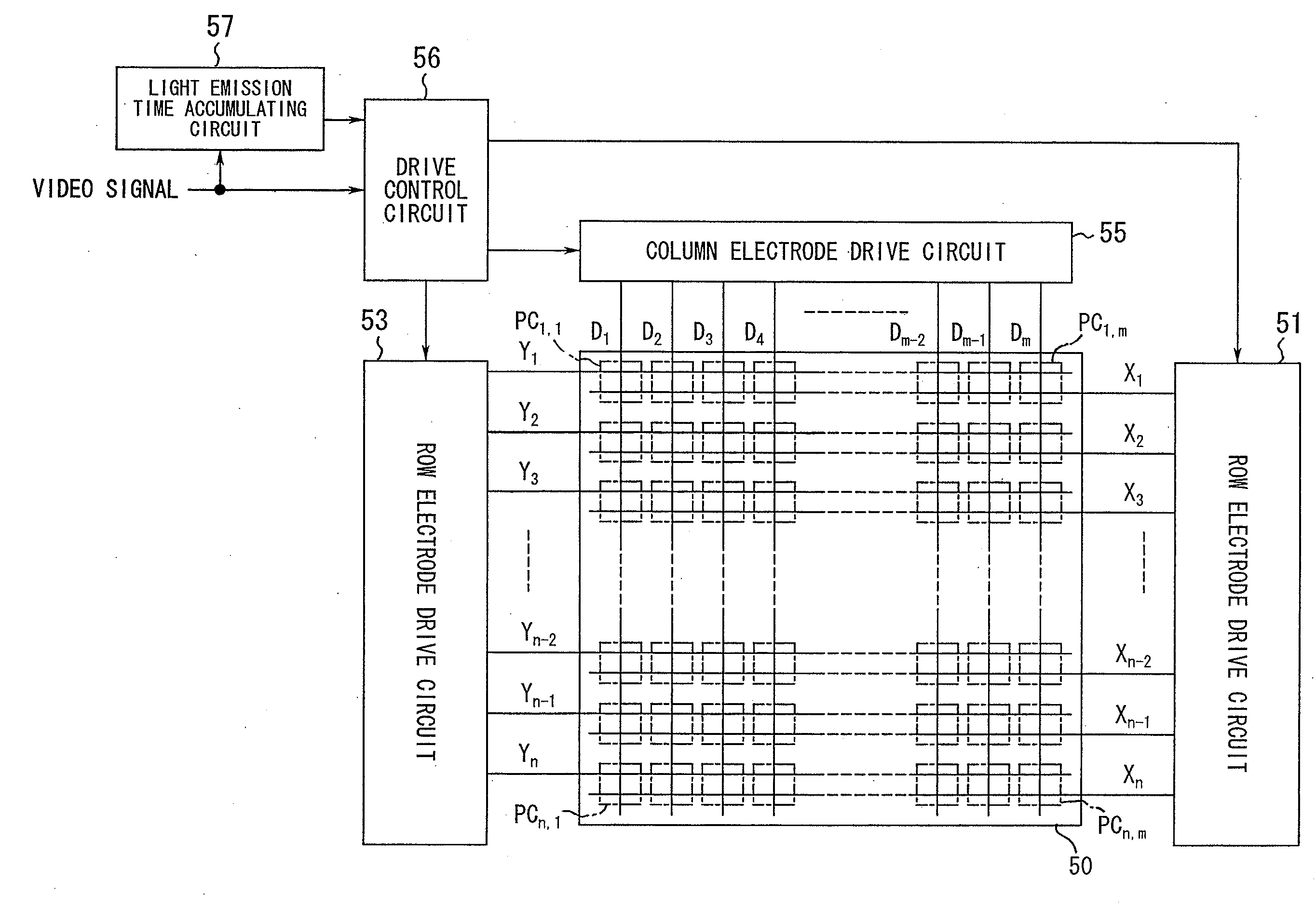

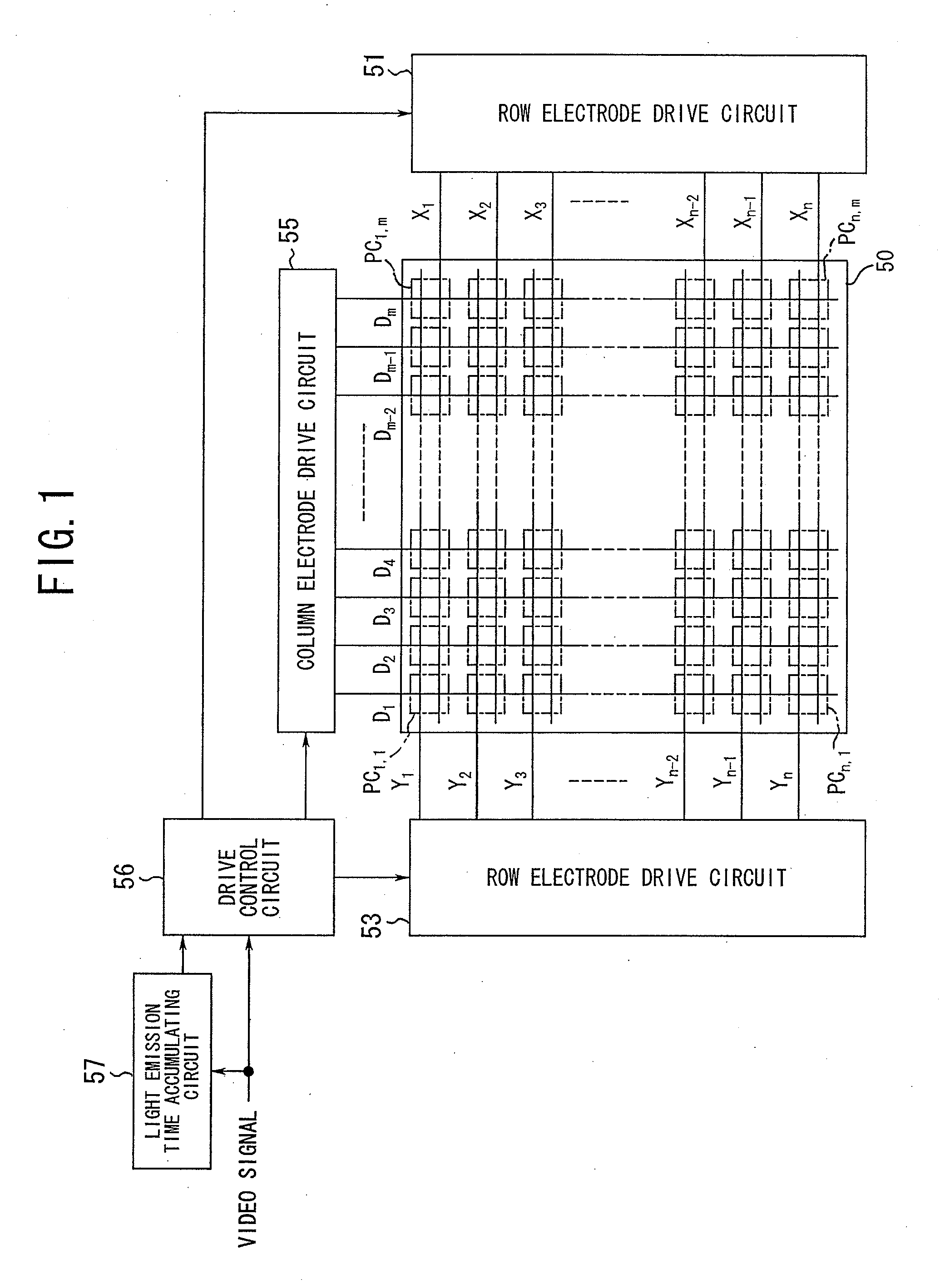

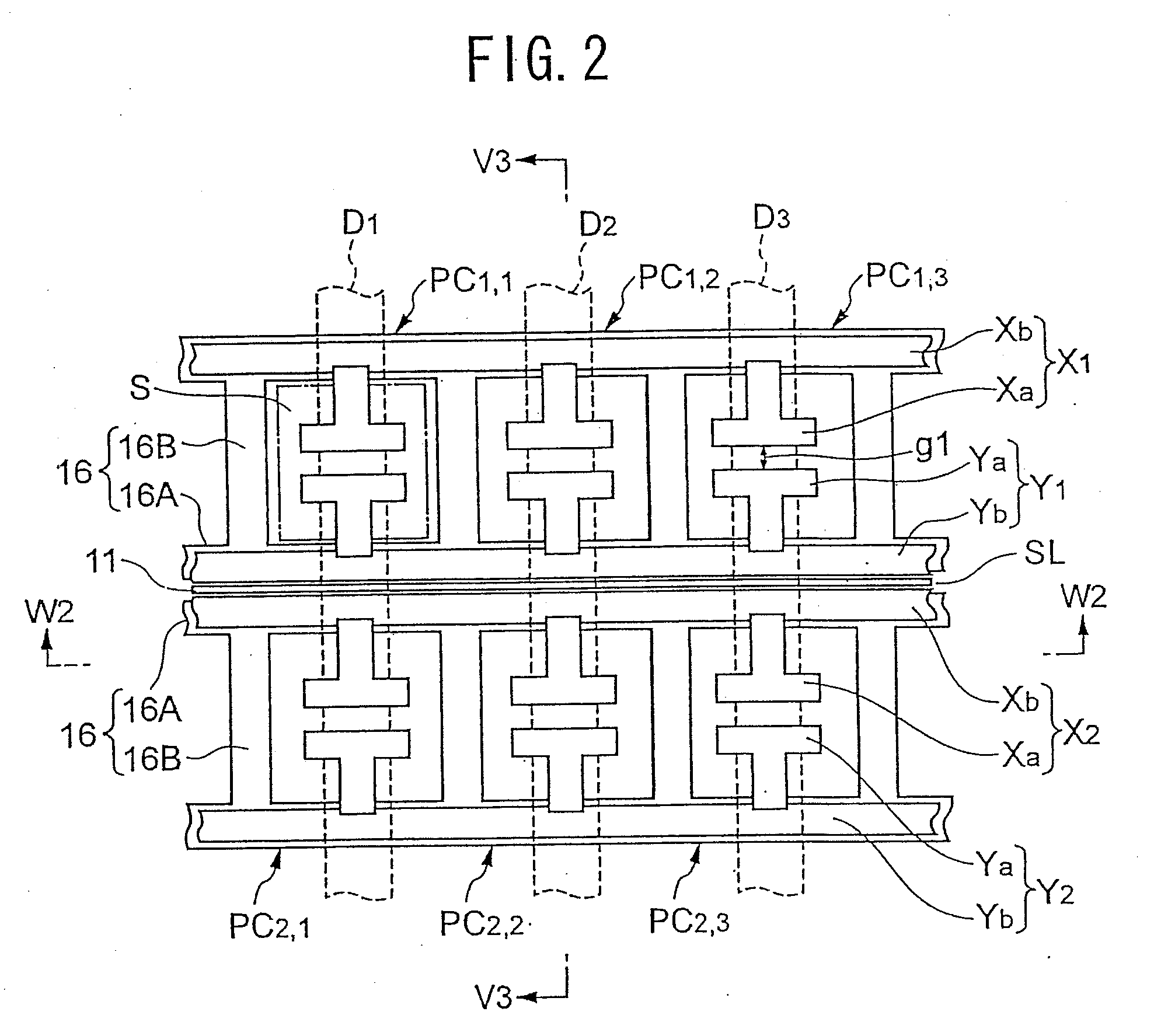

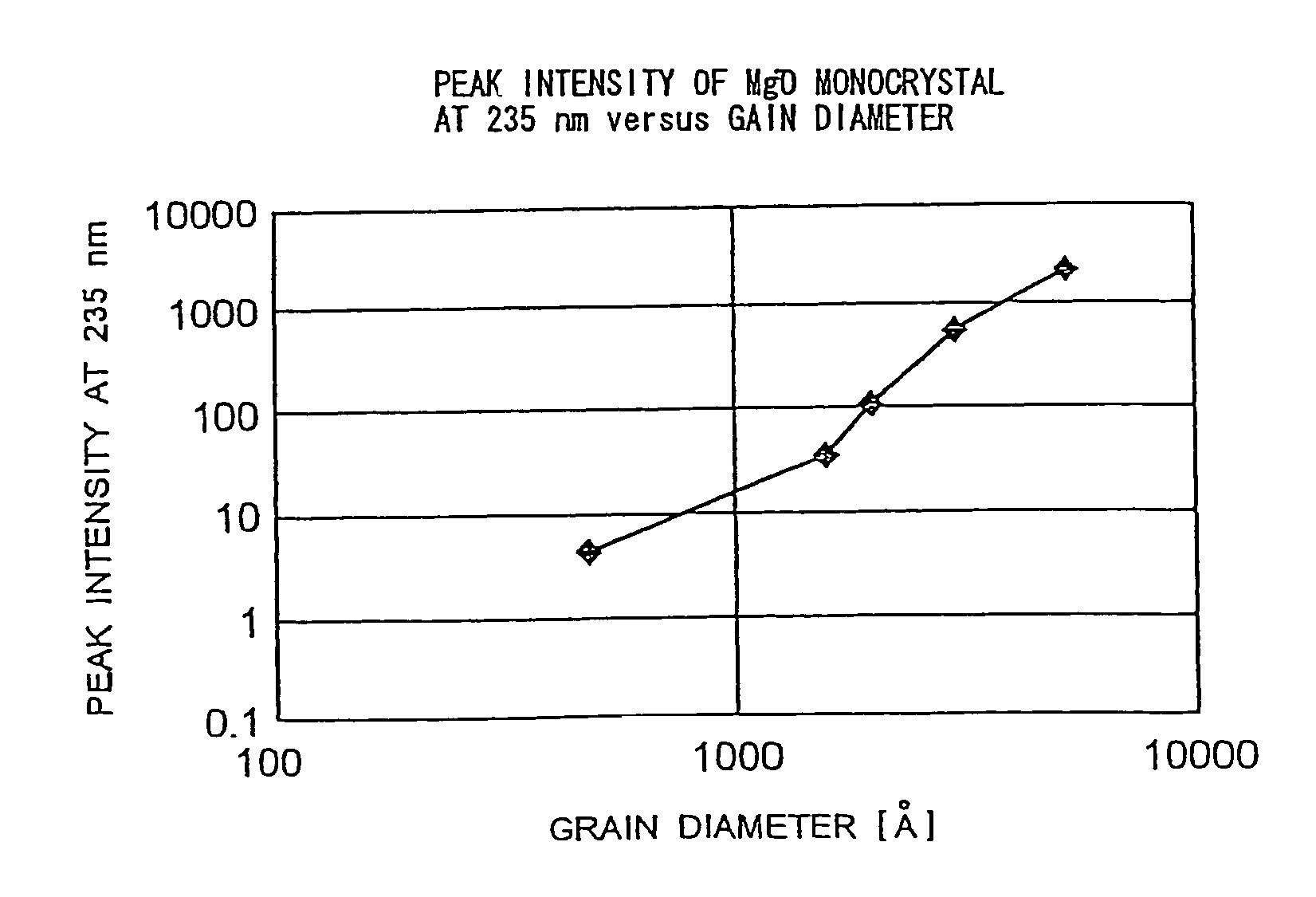

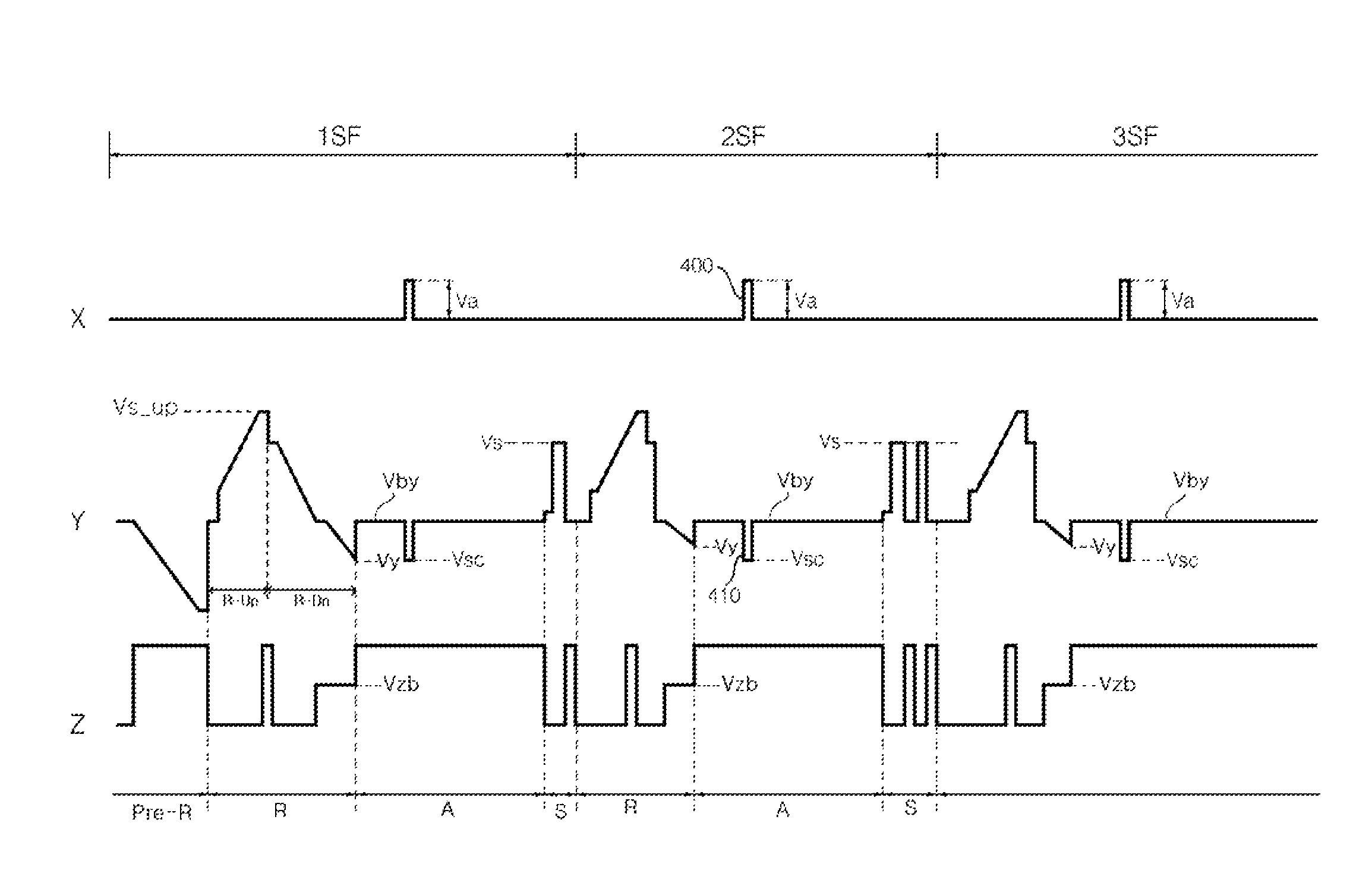

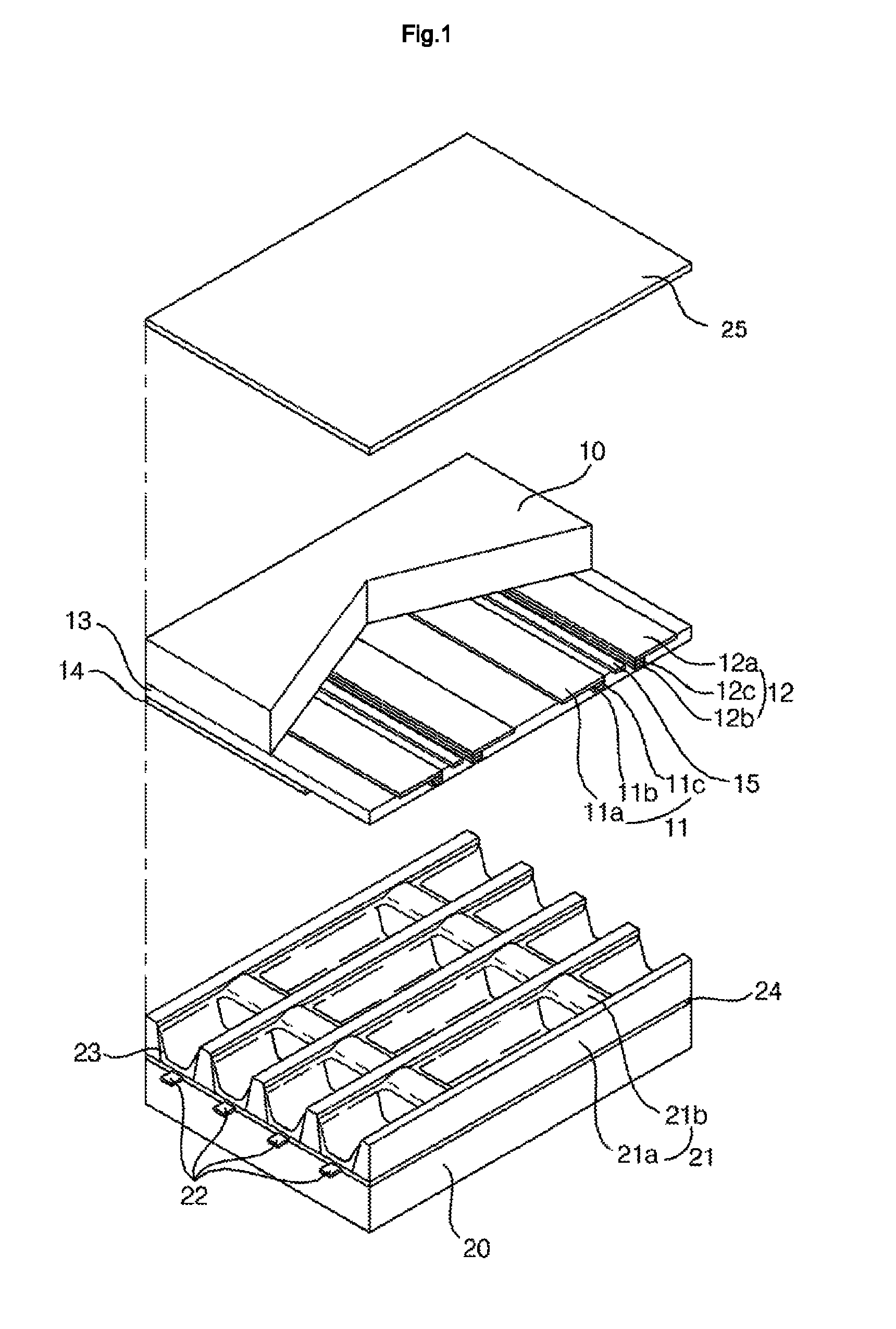

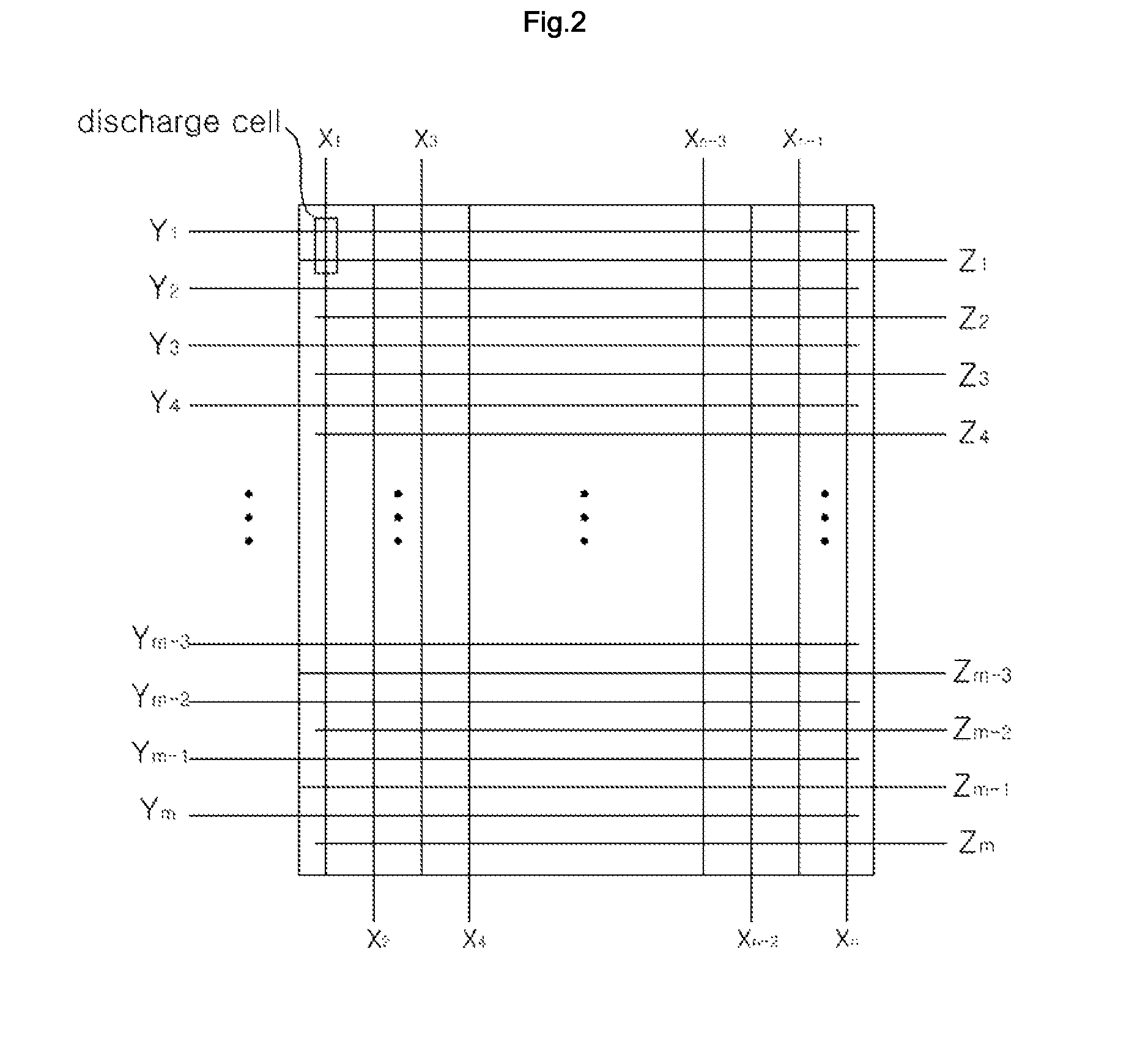

Plasma display device

InactiveUS20070103395A1Preventing variation in discharge intensityImprove afterimage problemAddress electrodesSustain/scan electrodesElectrode pairLight emission

A plasma display device in which a sustain pulse having a leading period is applied between row electrodes forming each row electrode pair by a number of times previously determined for each subfield, in a sustain period, and a length of the leading period of the sustain pulse is set in accordance with an accumulated light emission time or an accumulated use time of the plasma display panel.

Owner:PANASONIC CORP

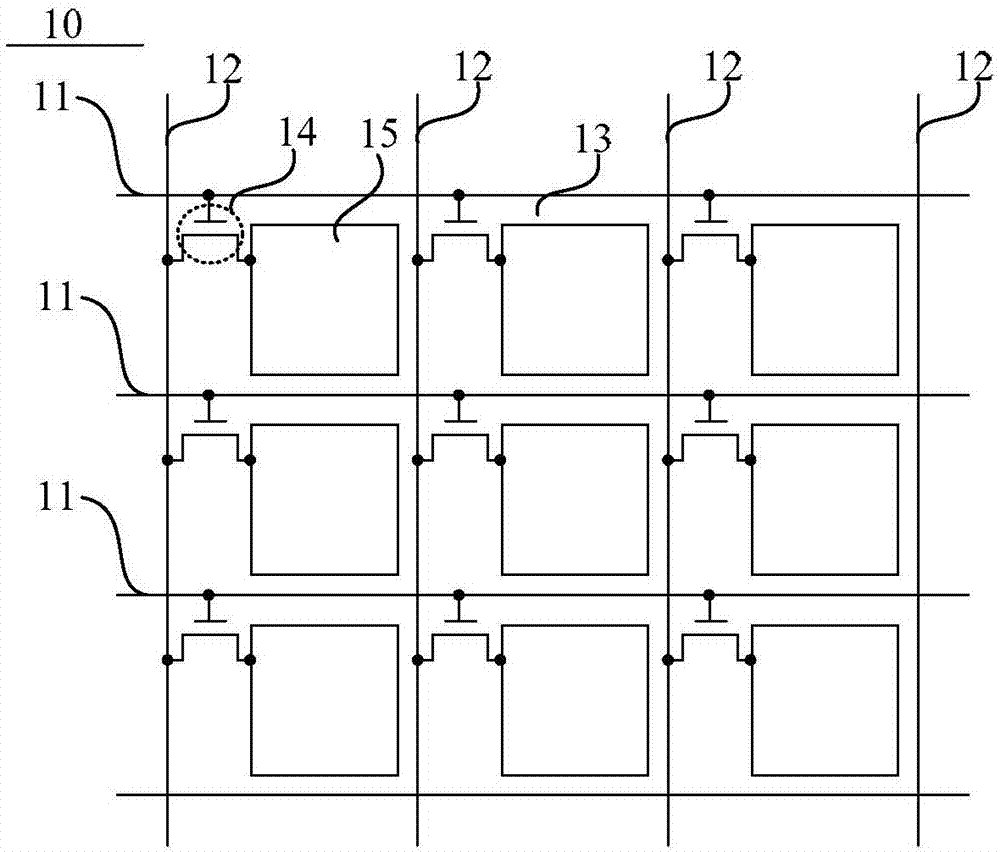

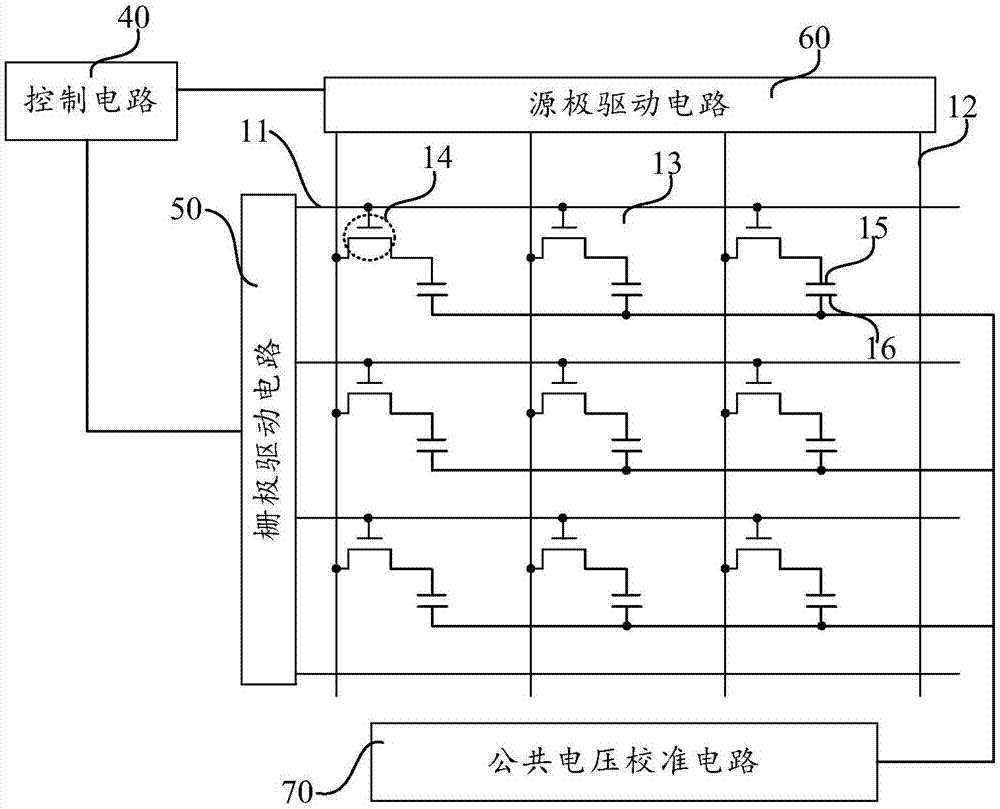

Common voltage calibration circuit, circuit board and display device

ActiveCN107578752AAchieve precision controlImprove stabilityStatic indicating devicesDisplay deviceEngineering

The embodiment of the invention discloses a common voltage calibration circuit, a circuit board and a display device and relates to the technical field of display. The precision and stability degree of common voltage which is actually input to a common electrode can be improved. The common voltage calibration circuit comprises a differencing module, an integral module, a compensation module and asummation module; the input end of the differencing module is connected with the input end of the common voltage and the feedback end of the common voltage, the differencing module is used for acquiring a voltage difference value of the input end of the common voltage and the feedback end of the common voltage, and the voltage difference value is output through the output end; the input end of theintegral module is connected with the output end of the differencing module, the output end of the integral module is connected with the input end of the summation module, and the integral module isused for controlling the precision of the common voltage; the input end of the compensation module is connected with the output end of the differencing module, the output end of the compensation module is connected with the input end of the summation module, and the compensation module is used for compensating the common voltage; the output end of the summation module is connected with the outputend of the common voltage, and the summation module is used for overlapping and outputting results output by the integral module and the compensation module.

Owner:BOE TECH GRP CO LTD +1

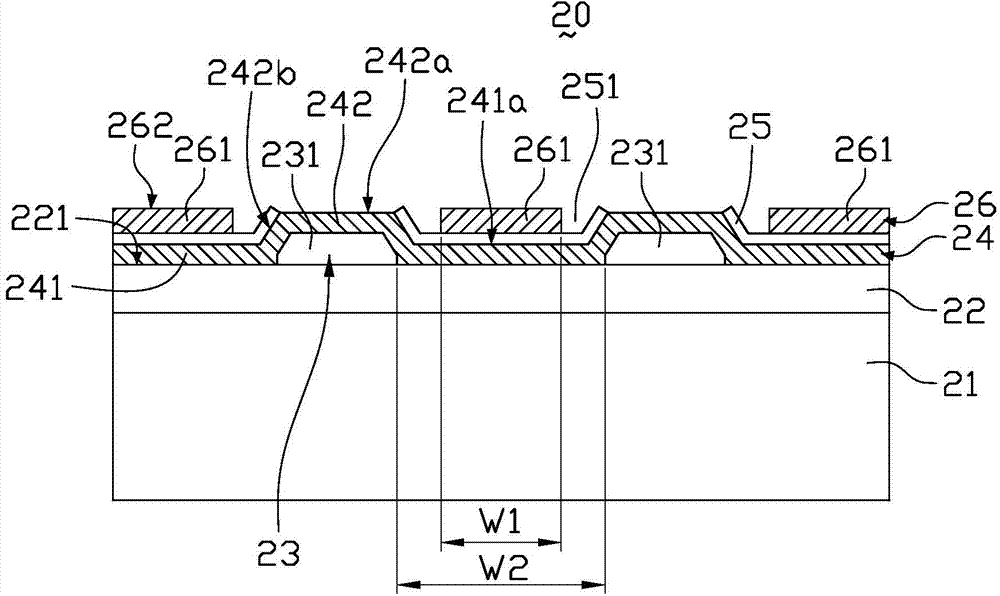

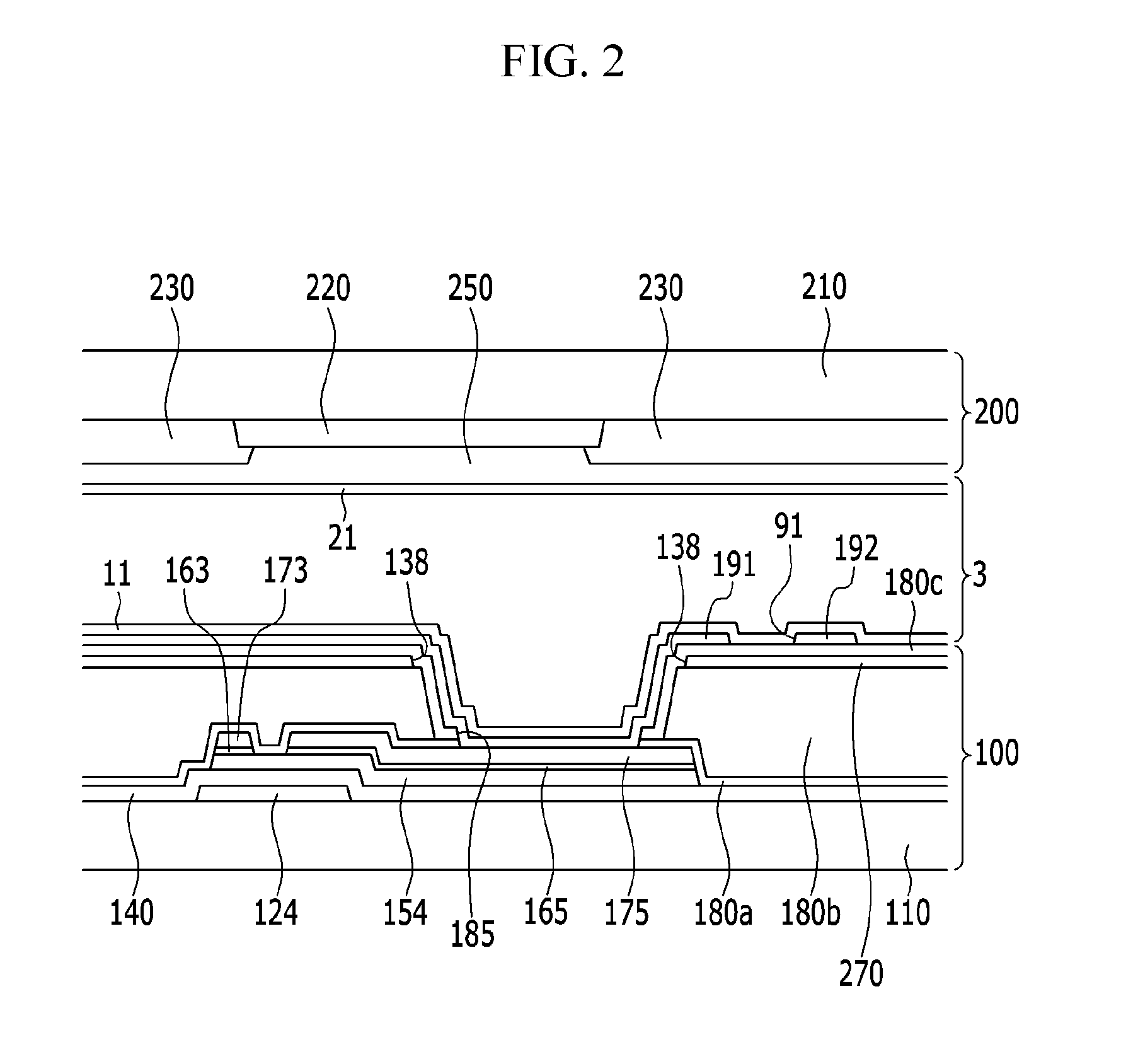

Fringe-field switching mode thin film transistor array substrate and manufacturing method thereof

ActiveCN104714343AReduce distanceReduce the driving voltageSemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsTransistor

The invention discloses a fringe-field switching mode thin film transistor array substrate and a manufacturing method thereof. The array substrate comprises a first insulating layer formed on a transparent substrate, a second insulating layer formed on the first insulating layer, a first electrode layer formed on the second insulating layer, a third insulating layer formed on the first electrode layer and a second electrode layer formed on the third insulating layer, wherein the second insulating layer comprises multiple insulating protrusive portions arranged at intervals; the multiple insulating protrusive portions protrude out of the surface of the first insulating layer; the first electrode layer comprises multiple electrode flat portions and multiple electrode convex portions; the multiple electrode flat portions cover the surface, not provided with the insulating protrusive portions, of the first insulating layer; the multiple electrode convex portions cover the multiple insulating protrusion portions respectively; the upper surfaces of the electrode convex portions are not covered with the third insulating layer and exposed; the second electrode layer comprises multiple electrode portions arranged at intervals; the multiple electrode portions are located above the multiple electrode flat portions respectively; the electrode portions and the electrode convex portions are arranged in a staggered and alternate mode.

Owner:KUSN INFOVISION OPTOELECTRONICS

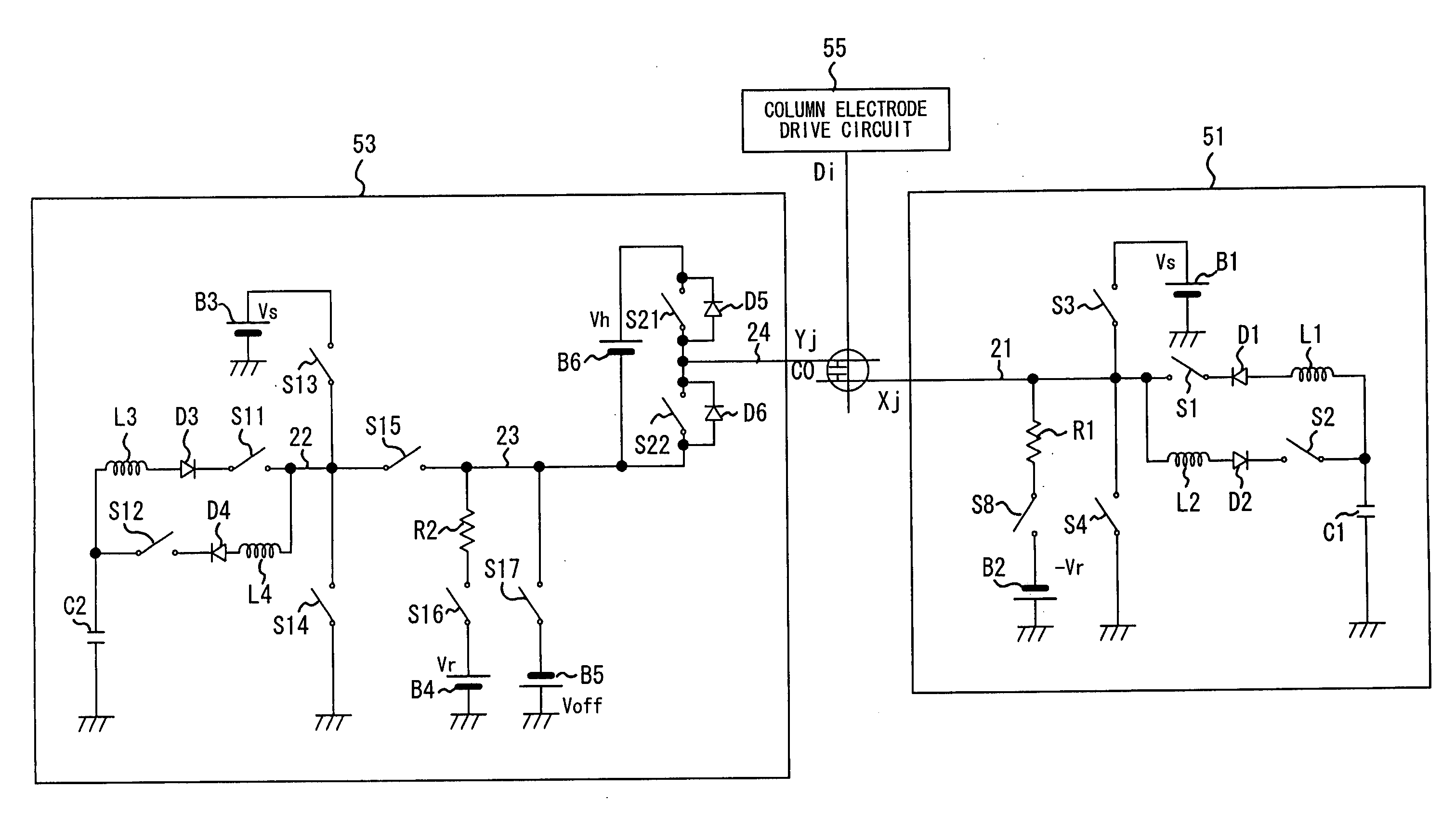

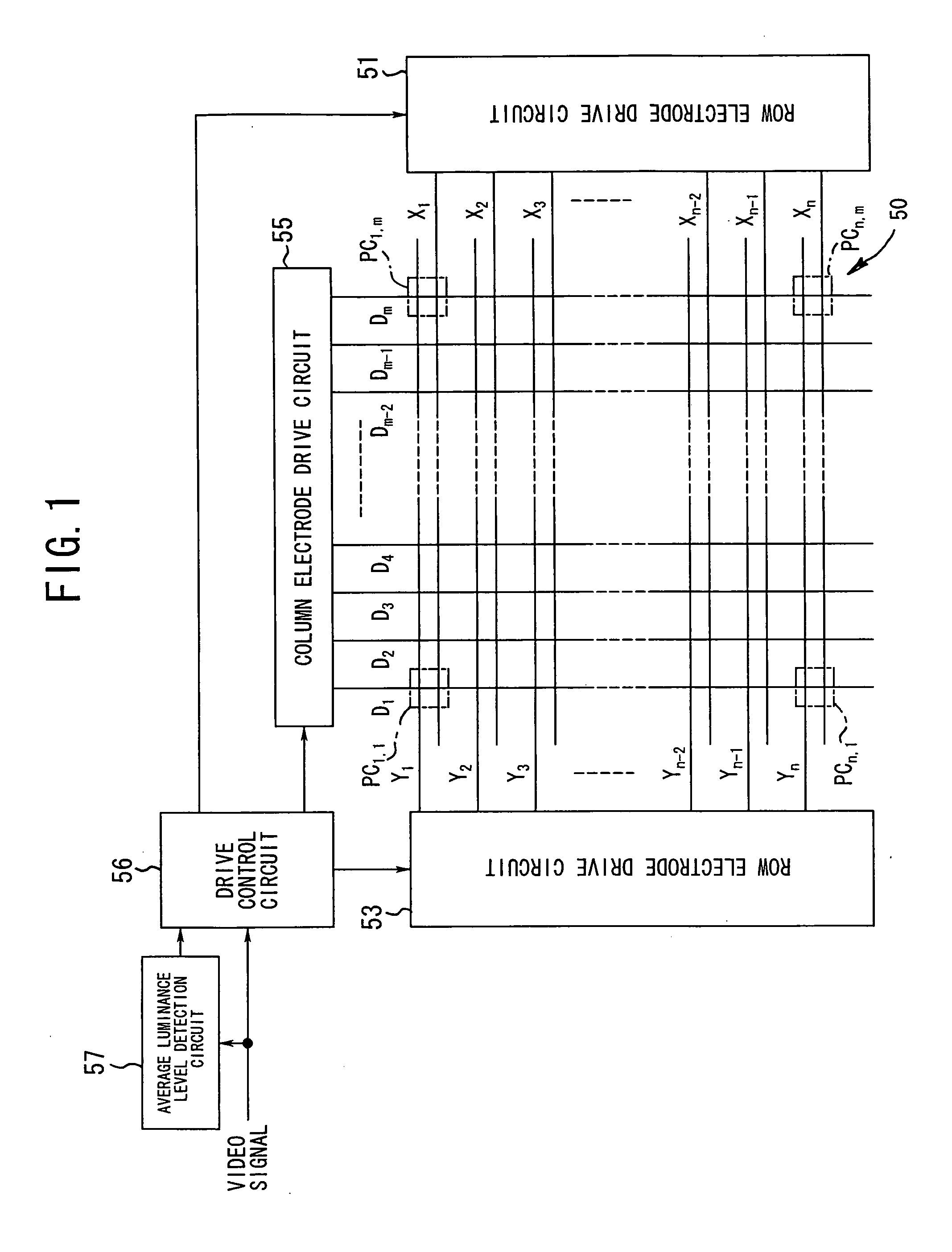

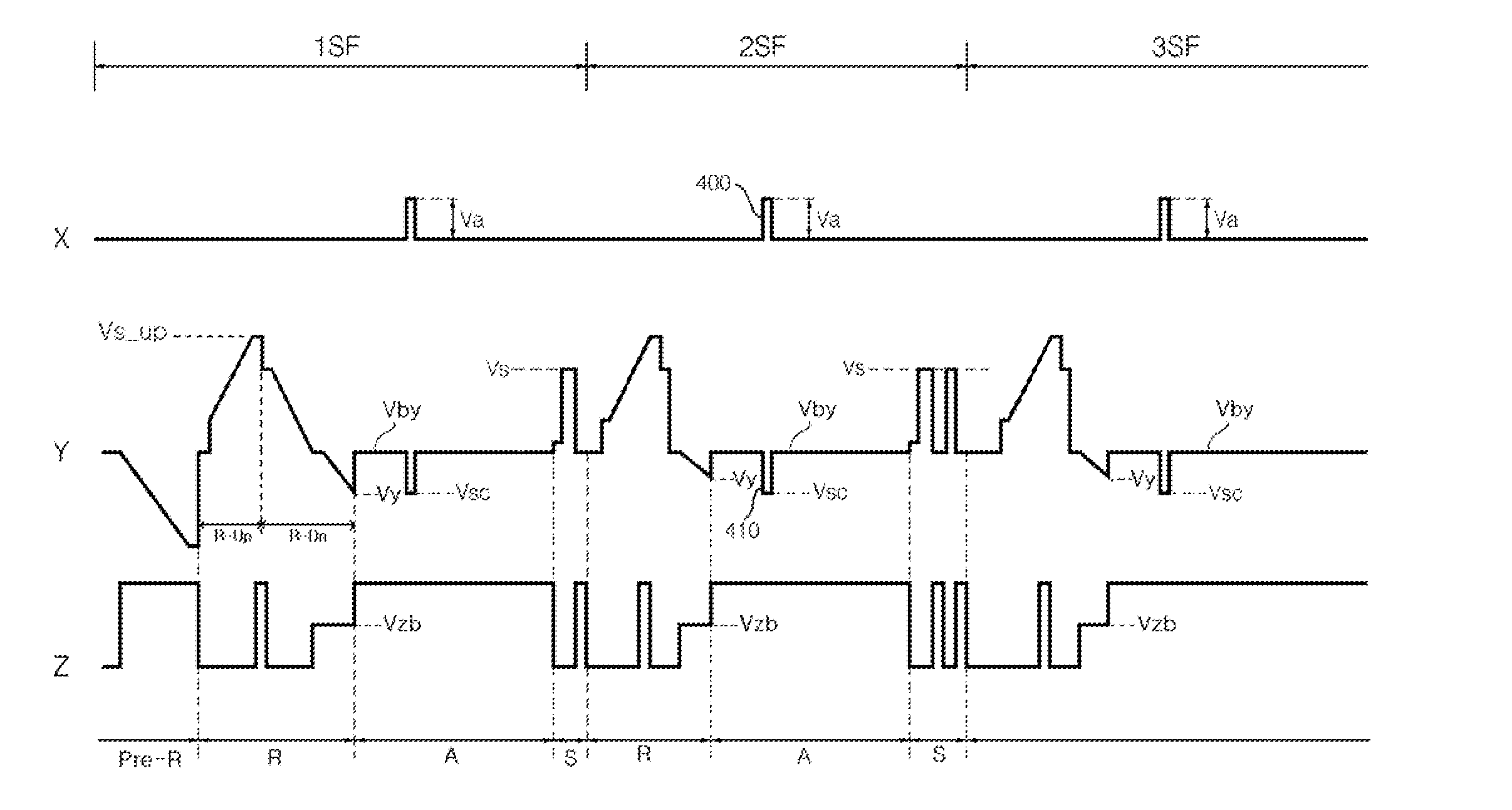

Plasma display device

InactiveUS20070052630A1Preventing variation in discharge intensityImprove afterimage problemStatic indicating devicesElectrode pairPlasma display

A plasma display device in which at least one of a first sustain pulse having a first leading period and a second sustain pulse having a second leading period shorter than the first leading period is applied between row electrodes forming each row electrode pair by a number of times previously determined for each subfield, in a sustain period, and an application ratio between the first sustain pulse and the second sustain pulse in the sustain period of each subfield is changed in accordance with a luminance level of a video signal.

Owner:PANASONIC CORP

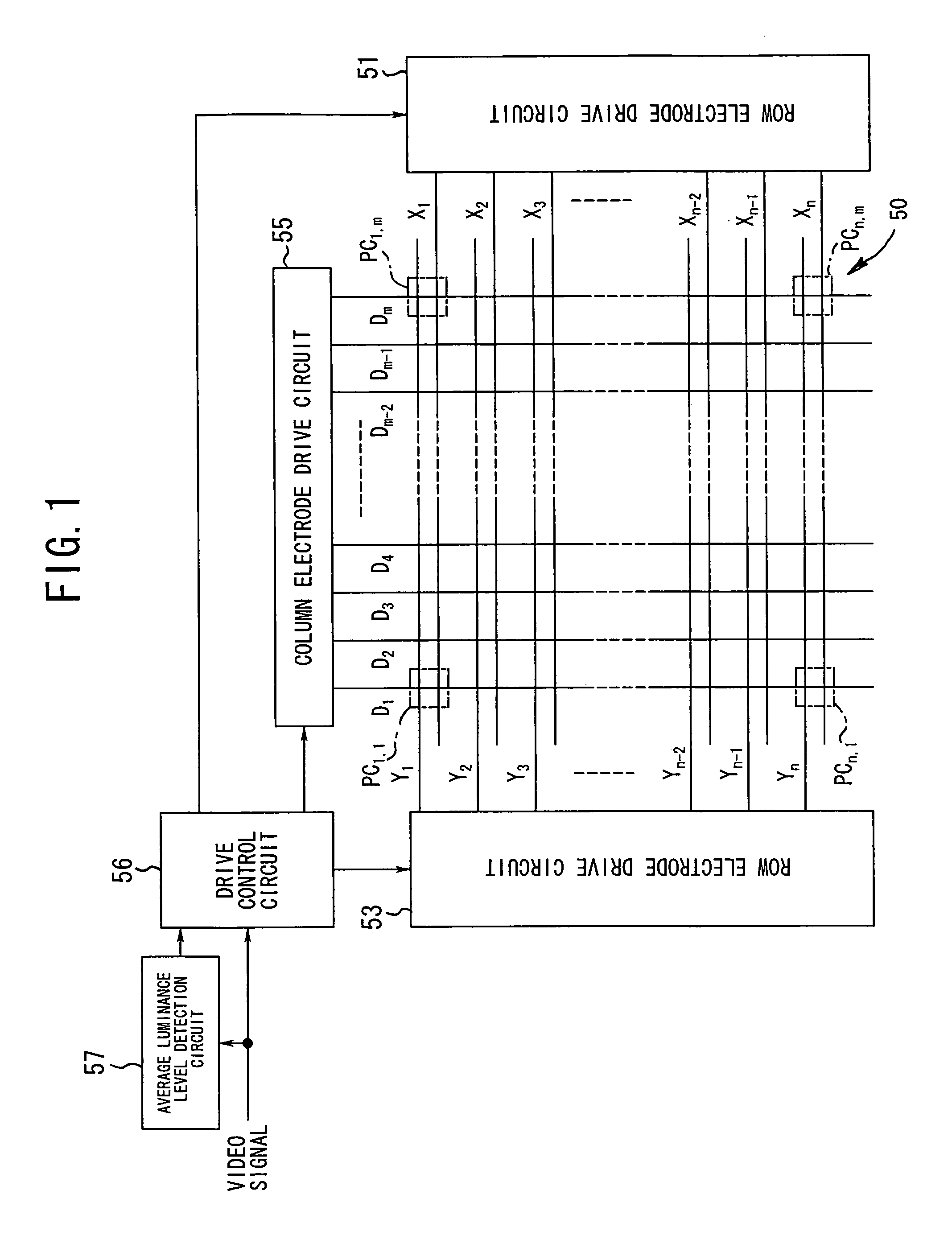

Plasma display device

InactiveUS20070057871A1Improve afterimage problemPreventing variation in discharge intensityTelevision system detailsAddress electrodesPlasma displayPhysics

A plasma display device which changes, in accordance with an average luminance level of a video signal, the length of a pause period between a sustain pulse application end point at which one sustain pulse is applied in a sustain period of each of subfields and a sustain pulse application starting point at which the next sustain pulse is applied.

Owner:PANASONIC CORP

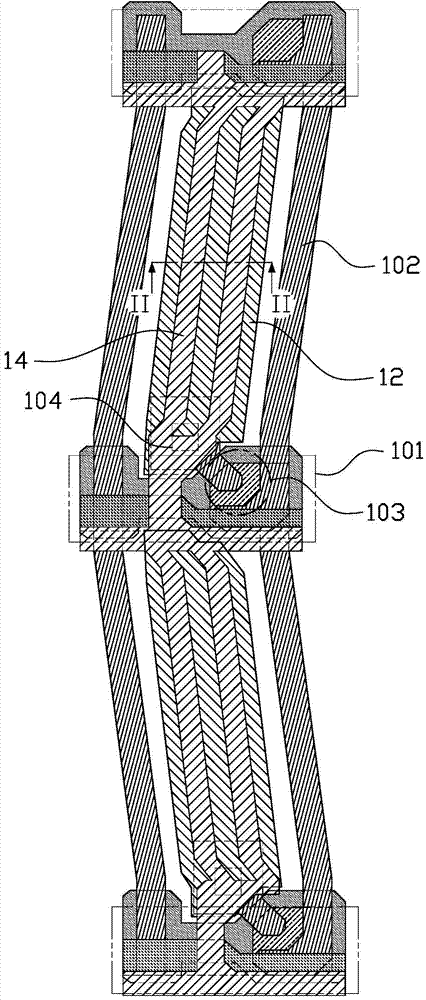

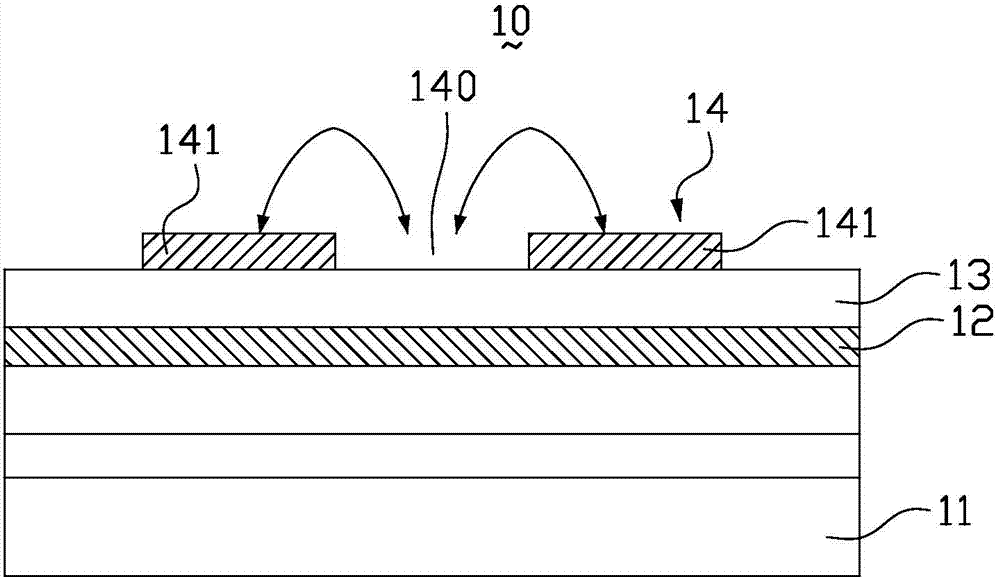

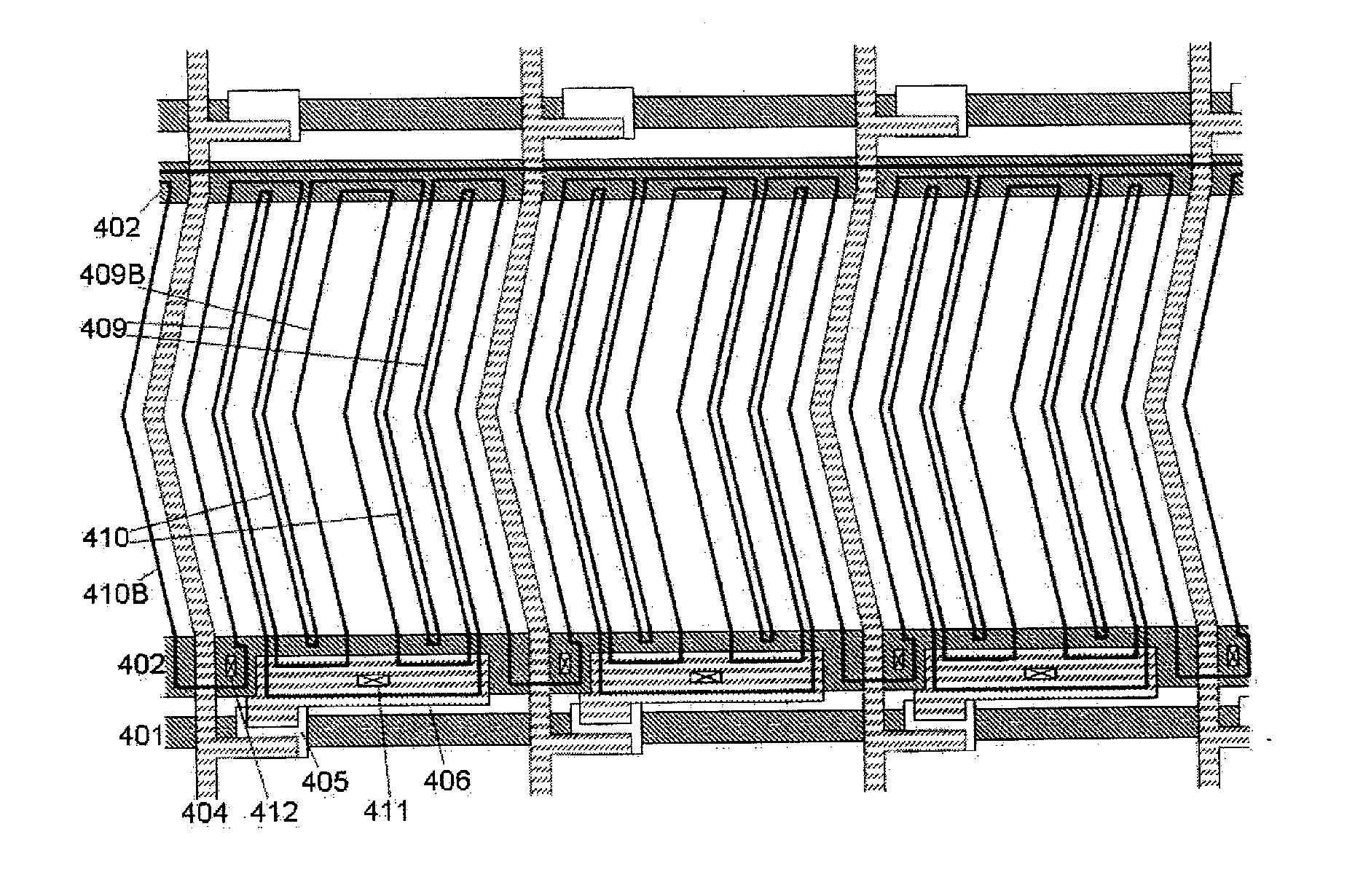

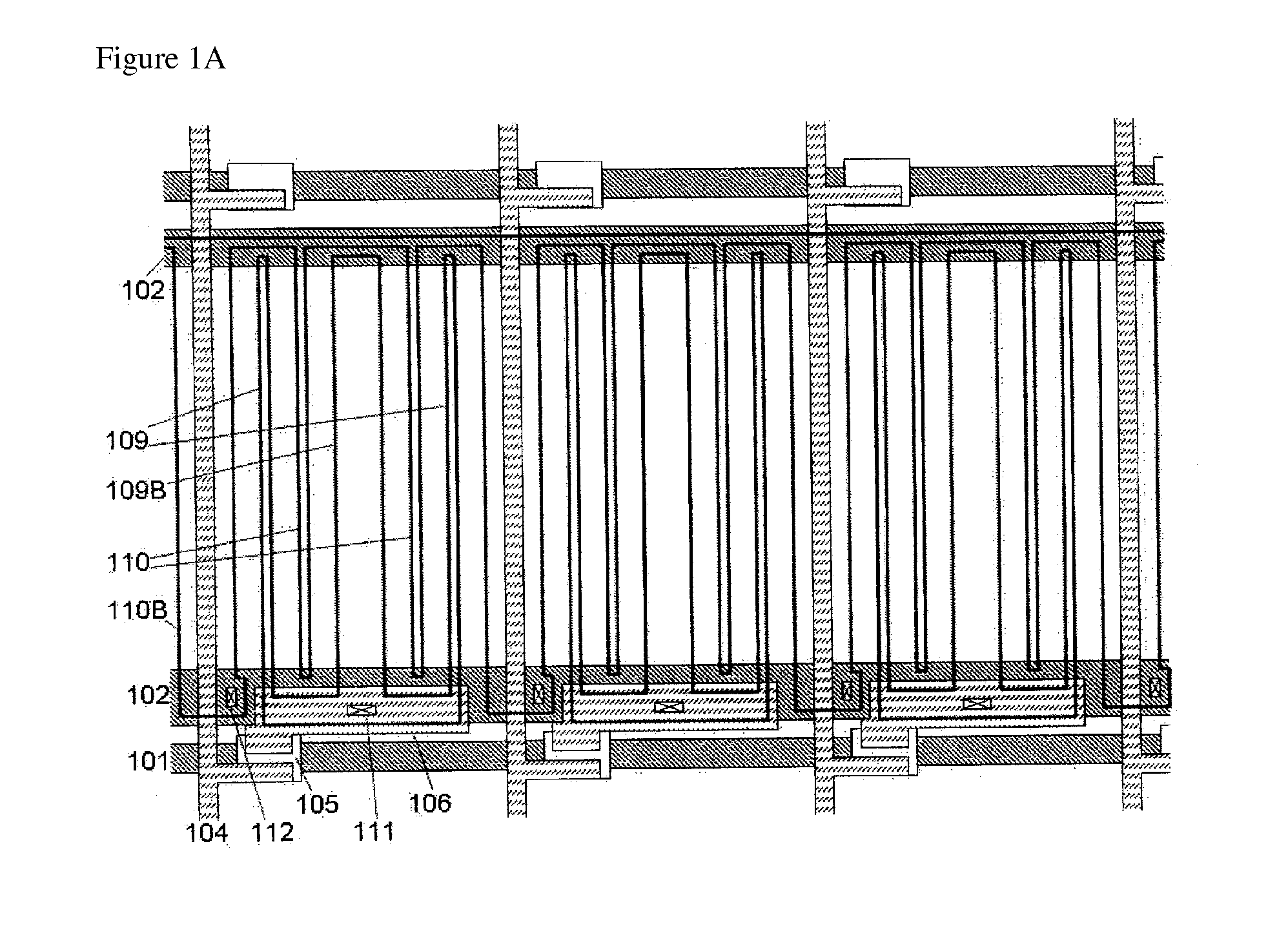

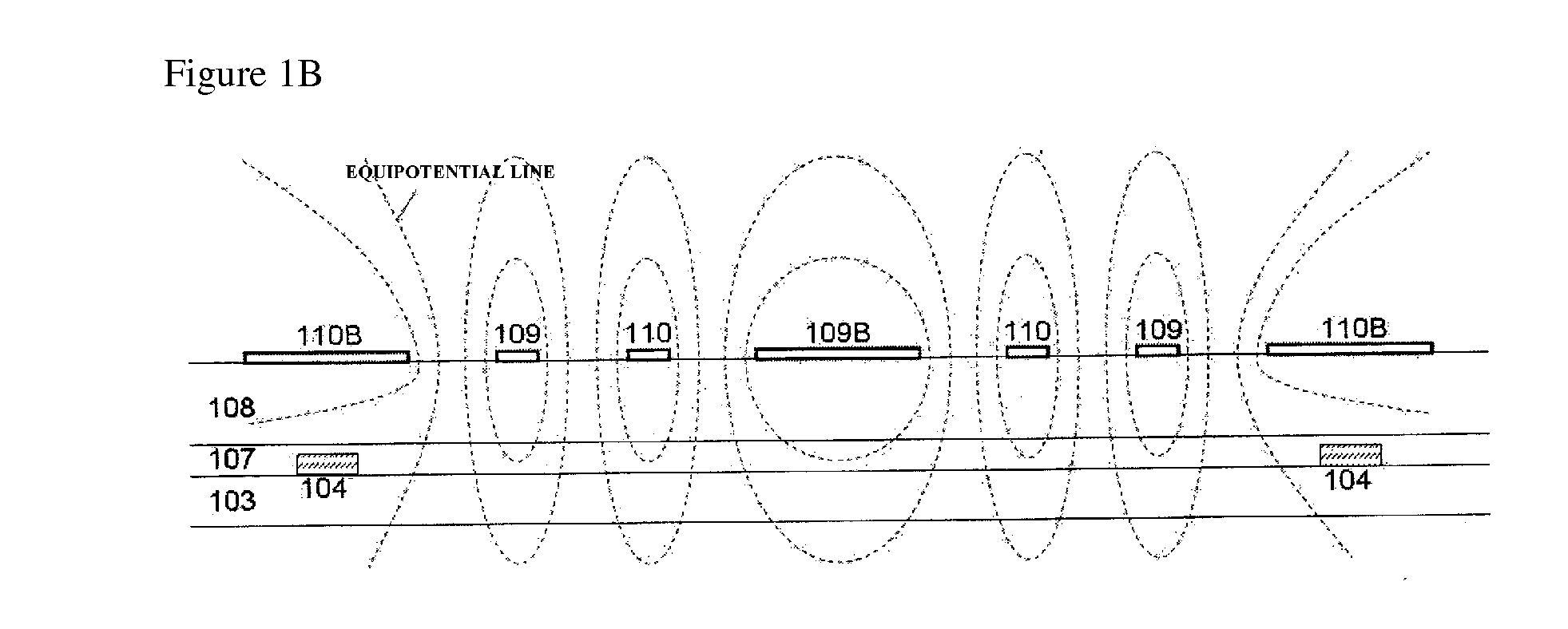

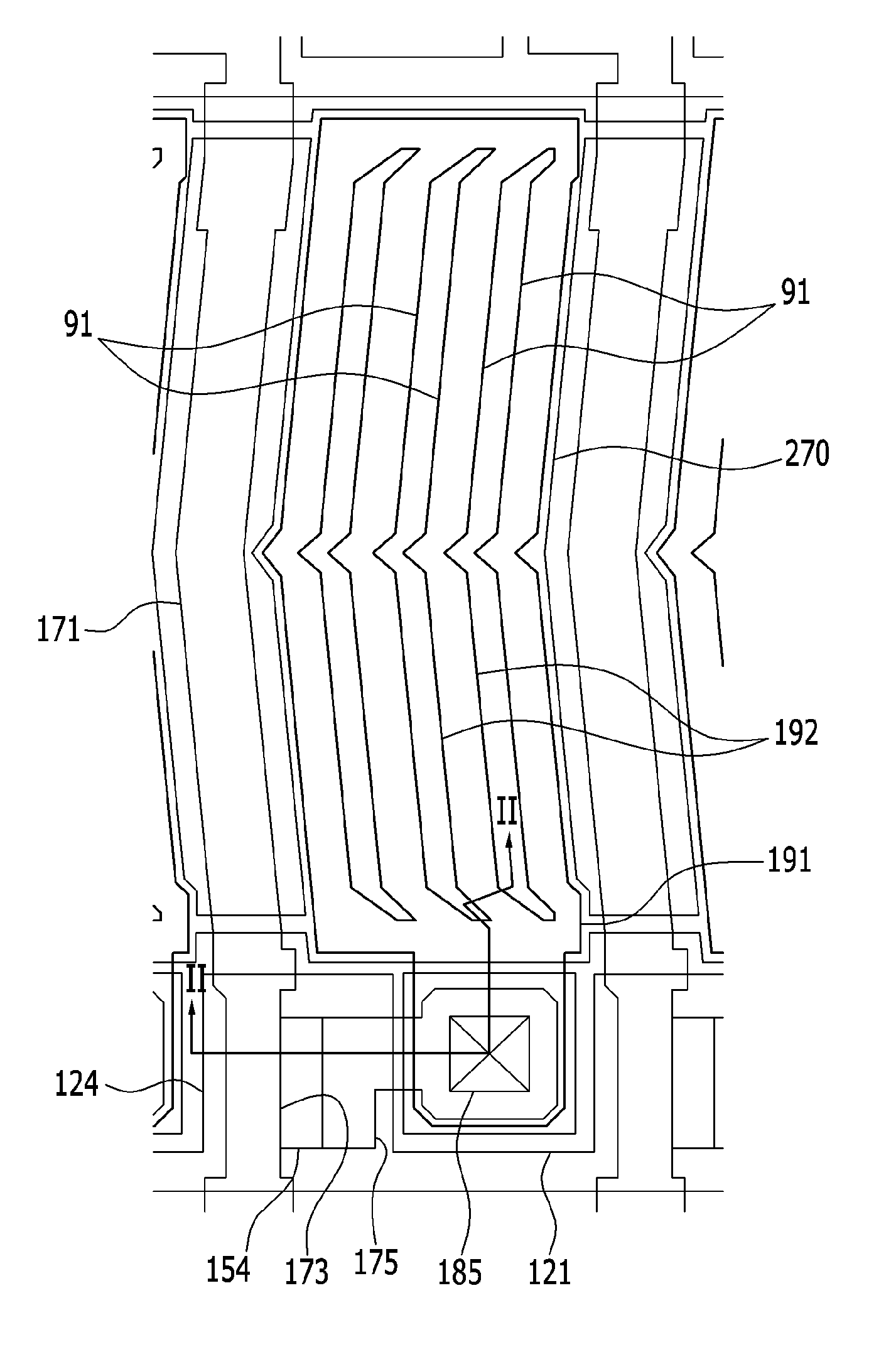

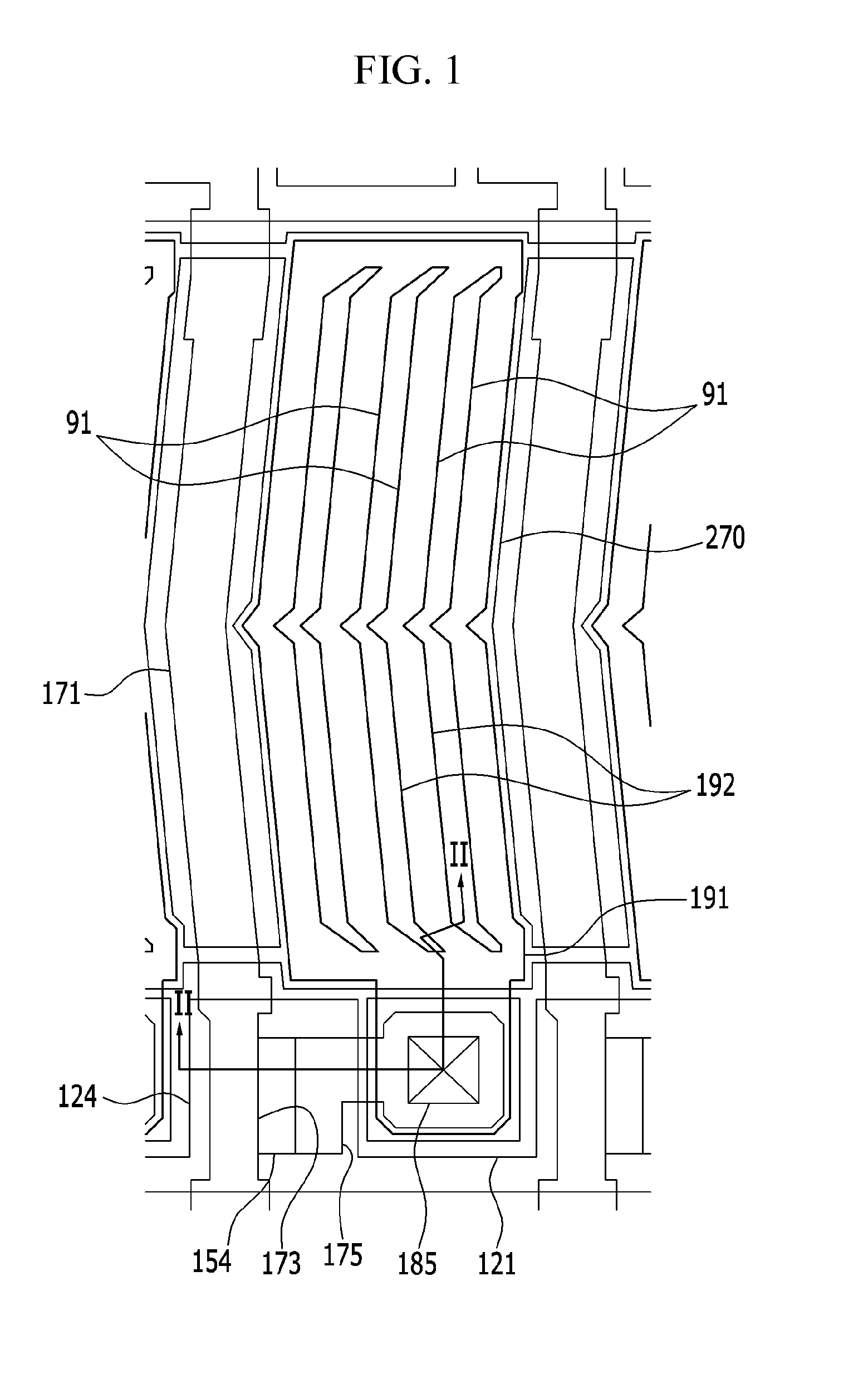

Liquid-crystal display device

ActiveUS20150185564A1Improve afterimage problemNon-linear opticsActive-matrix liquid-crystal displayLiquid-crystal display

Provided is a lateral-electric-field mode active matrix liquid crystal display device in which an afterimage can be improved. The width of one pixel comb electrode 109B of a plurality of pixel comb electrodes 109 is larger than each of the widths of the other pixel comb electrodes 109 and common comb electrodes 110 and is equivalent to the width of a common shield electrode 110B that covers an image signal wiring line 104 via a second insulating film. A display region is divided into two subregions by the wide pixel comb electrode 109B. In each subregion, the number of pixel comb electrodes 109 is equal to that of common comb electrodes 110. In addition, the width of the common shield electrode 110B is equivalent to that of the wide pixel comb electrode 109B, and the concentration of an electric field in the vicinity of each pixel comb electrode is reduced. Since structural symmetry is achieved, an electric potential distribution becomes symmetrical, and the asymmetry of the manners of emitting light between frames is reduced. As a result, the DC offset component of an image signal after flicker adjustment is reduced to improve an afterimage.

Owner:TIANMA MICRO ELECTRONICS CO LTD

Plasma Display Apparatus

InactiveUS20070152916A1Prevent misdischargeImprove afterimage problemStatic indicating devicesLow voltageEngineering

Provided is a plasma display apparatus. The plasma display apparatus includes a first electrode and a second electrode formed in parallel on an upper substrate, and a third electrode formed on a lower substrate to intersect with the first electrode and the second electrode. A driving signal is applied to the first electrode, the second electrode, and the third electrode in a reset period, an address period, and a sustain period per one subfield. The reset period comprises a setdown period. A difference between a setdown lowest voltage of the driving signal applied to the first electrode and a voltage applied to the second electrode in the setdown period is 1.2 times to 1.5 times of a sustain voltage.

Owner:LG ELECTRONICS INC

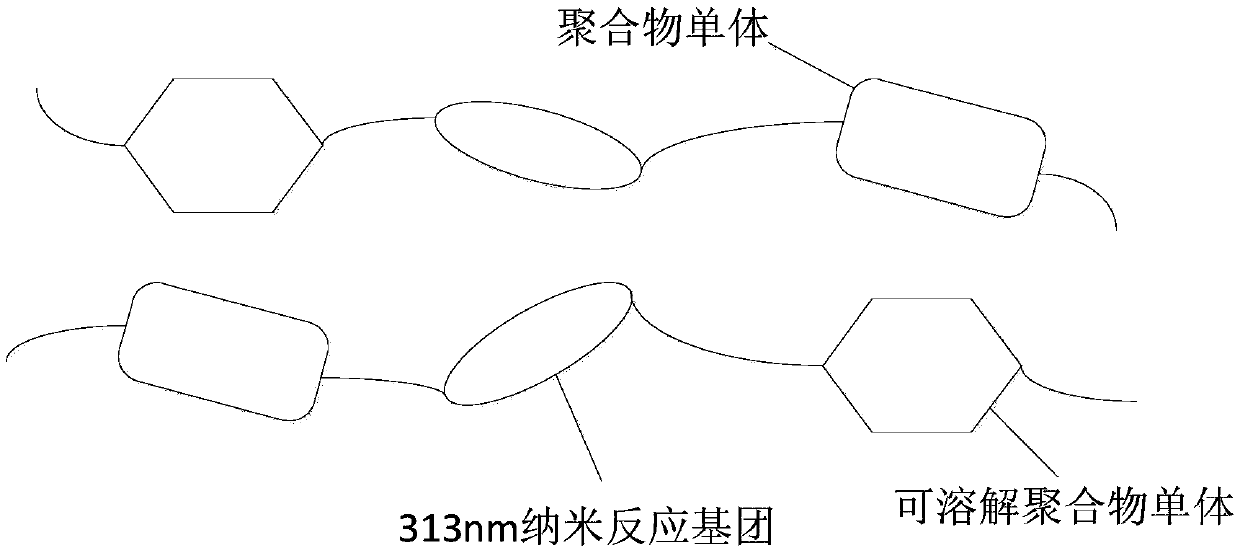

Photoalignment agent, liquid crystal display device including the same, and method of manufacturing the same

ActiveUS20150241739A1Improve afterimage problemSemiconductor/solid-state device manufacturingCoatingsLiquid-crystal displayDiamine

A photoalignment agent is provided. The photoalignment agent includes a copolymer of at least one of a cyclobutanedianhydride (CBDA) and a cyclobutanedianhydride (CBDA) derivative, and a realignment property diamine, wherein two or more aromatic rings in the realignment property diamine are connected by an ester group.

Owner:SAMSUNG DISPLAY CO LTD

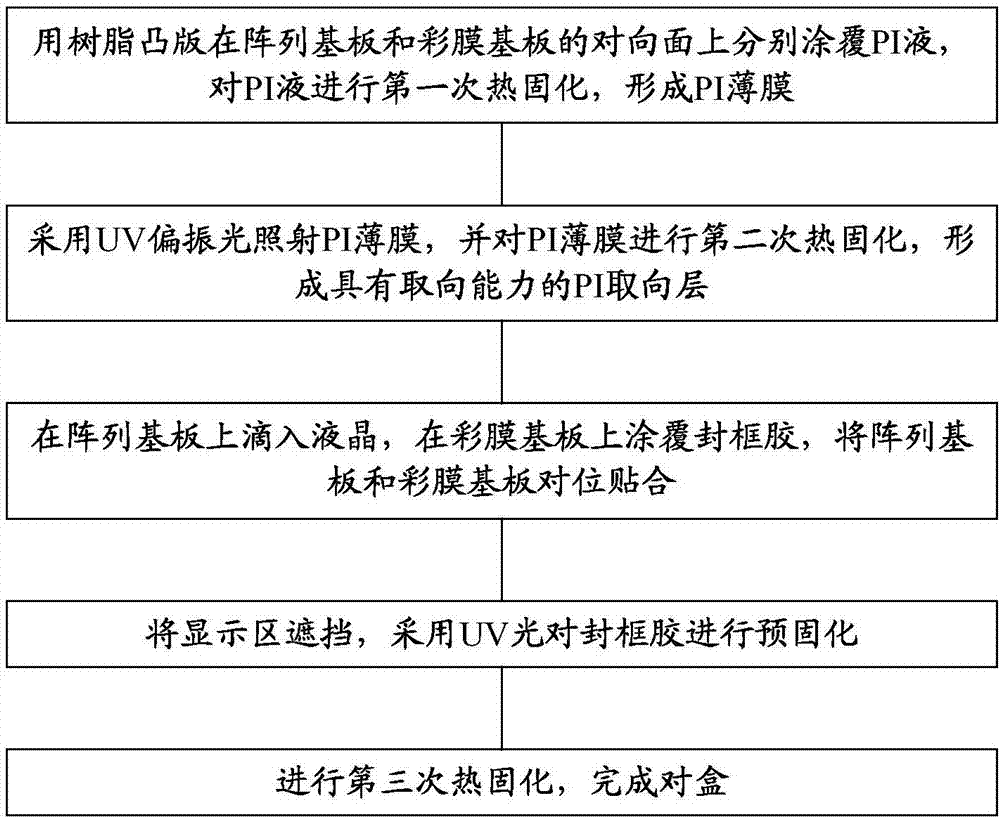

Liquid crystal display panel manufacturing method

InactiveCN105116621AImprove reliabilityStrong penetrating powerNon-linear opticsArray data structureLiquid-crystal display

The invention discloses a liquid crystal display panel manufacturing method. The method includes the steps that an array substrate and a color film substrate are provided, the array substrate comprises first electrodes and a second electrode, and each first electrode is provided with a plurality of trenches; a first light alignment film is coated on the array substrate, first irradiation processing is conducted on the first light alignment film, and the first light alignment film is made to have a first pretilt angle; a second light alignment film is coated on the color film substrate, second irradiation processing is conducted on the second light alignment film, the second light alignment film is made to have a second pretilt angle, and the second pretilt angle is antiparallel to the first pretilt angle; liquid crystal molecular and photopolymerization monomers are arranged between the first alignment film and the second alignment film in a sealed mode, and a liquid crystal display panel is formed; third irradiation processing is conducted on the liquid crystal display panel, and the photopolymerization monomers are made to conduct a polymerization reaction.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

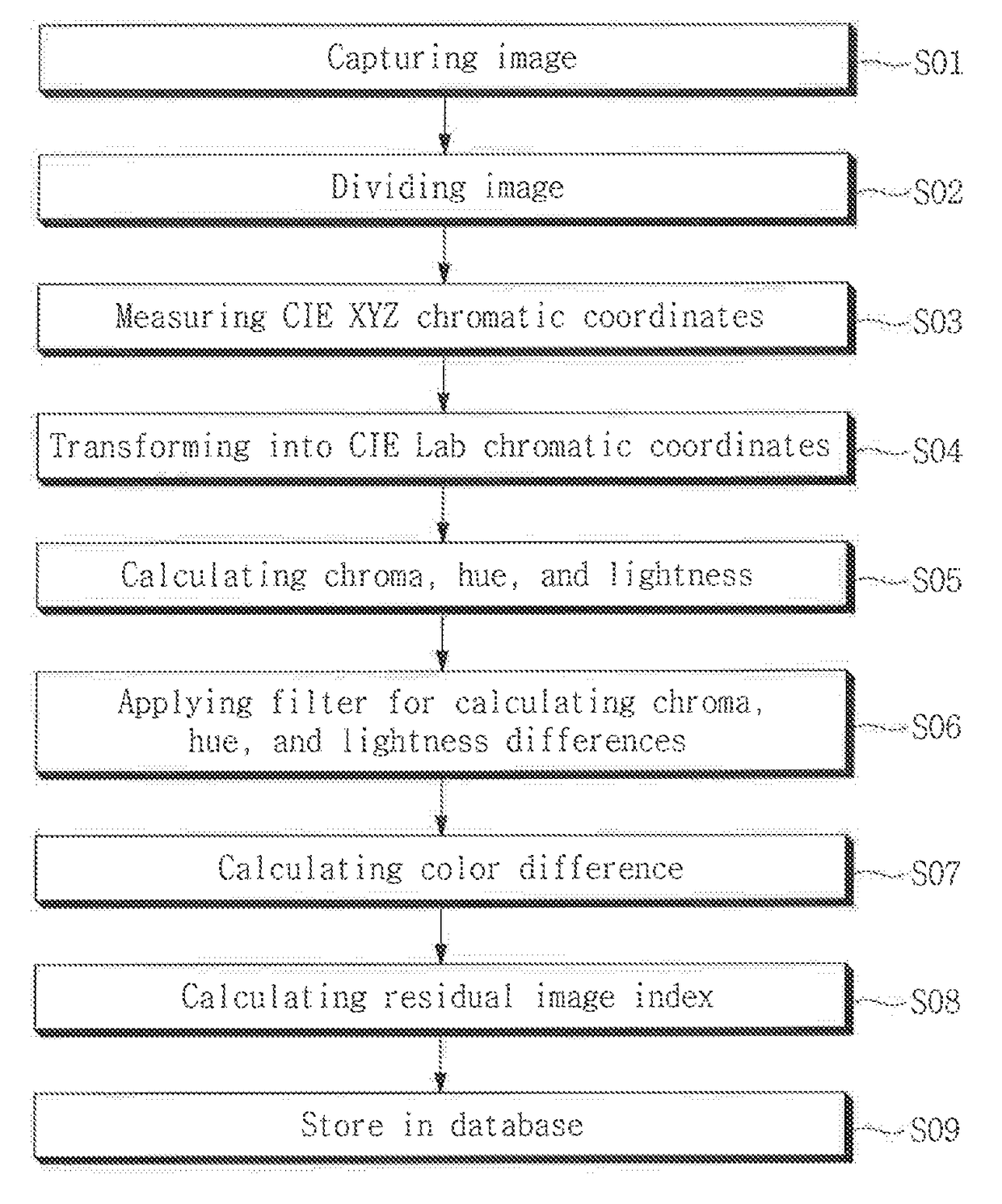

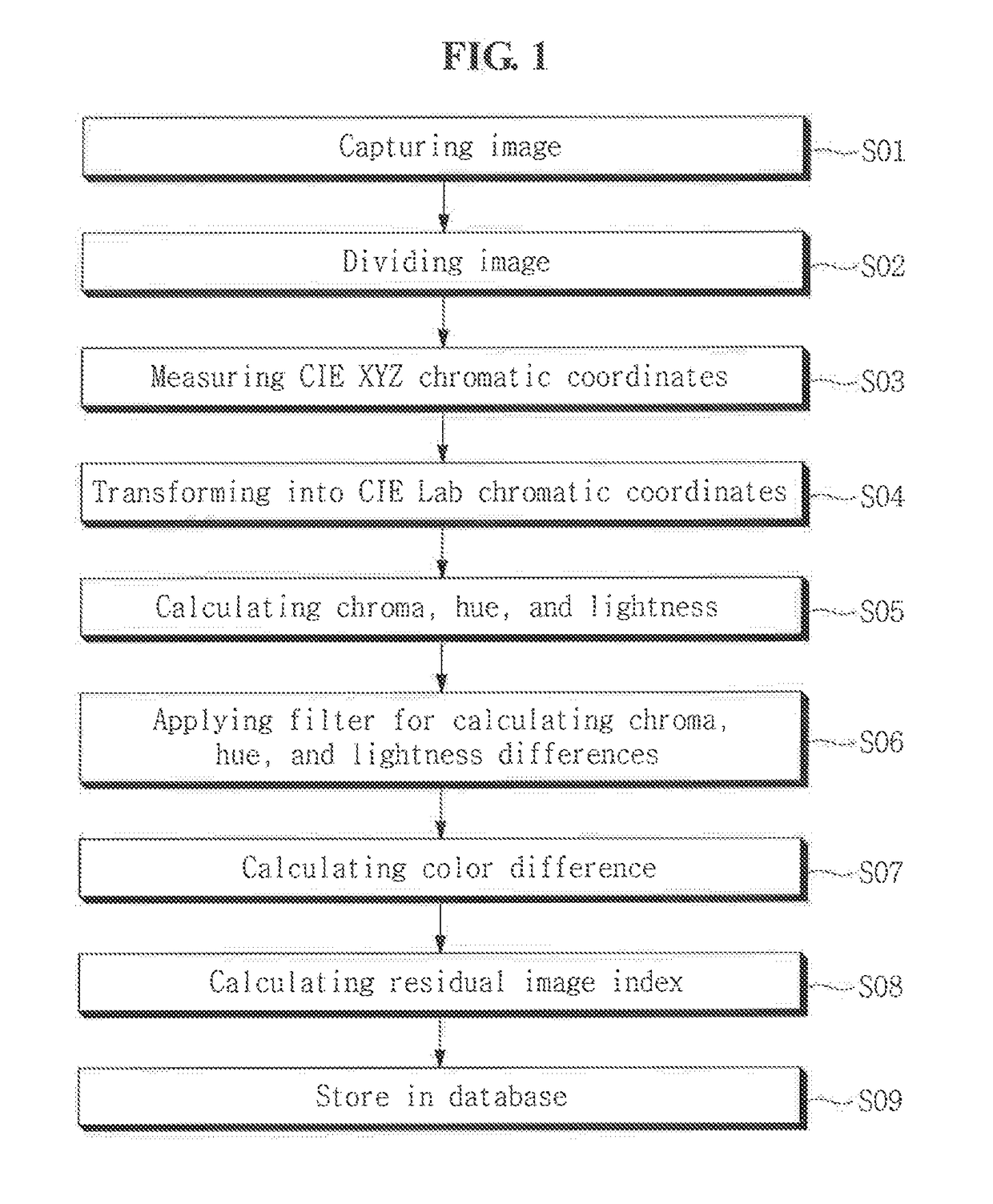

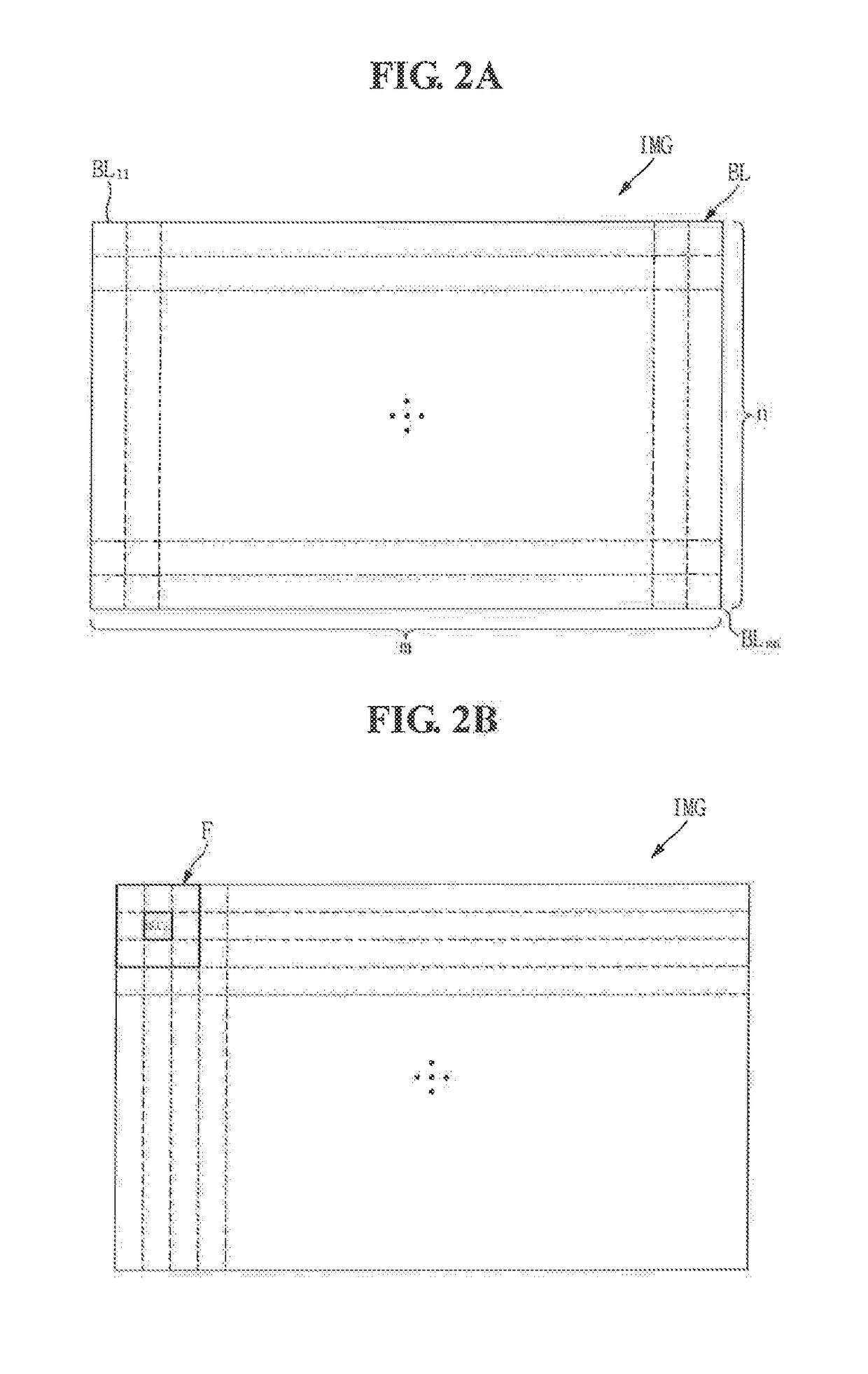

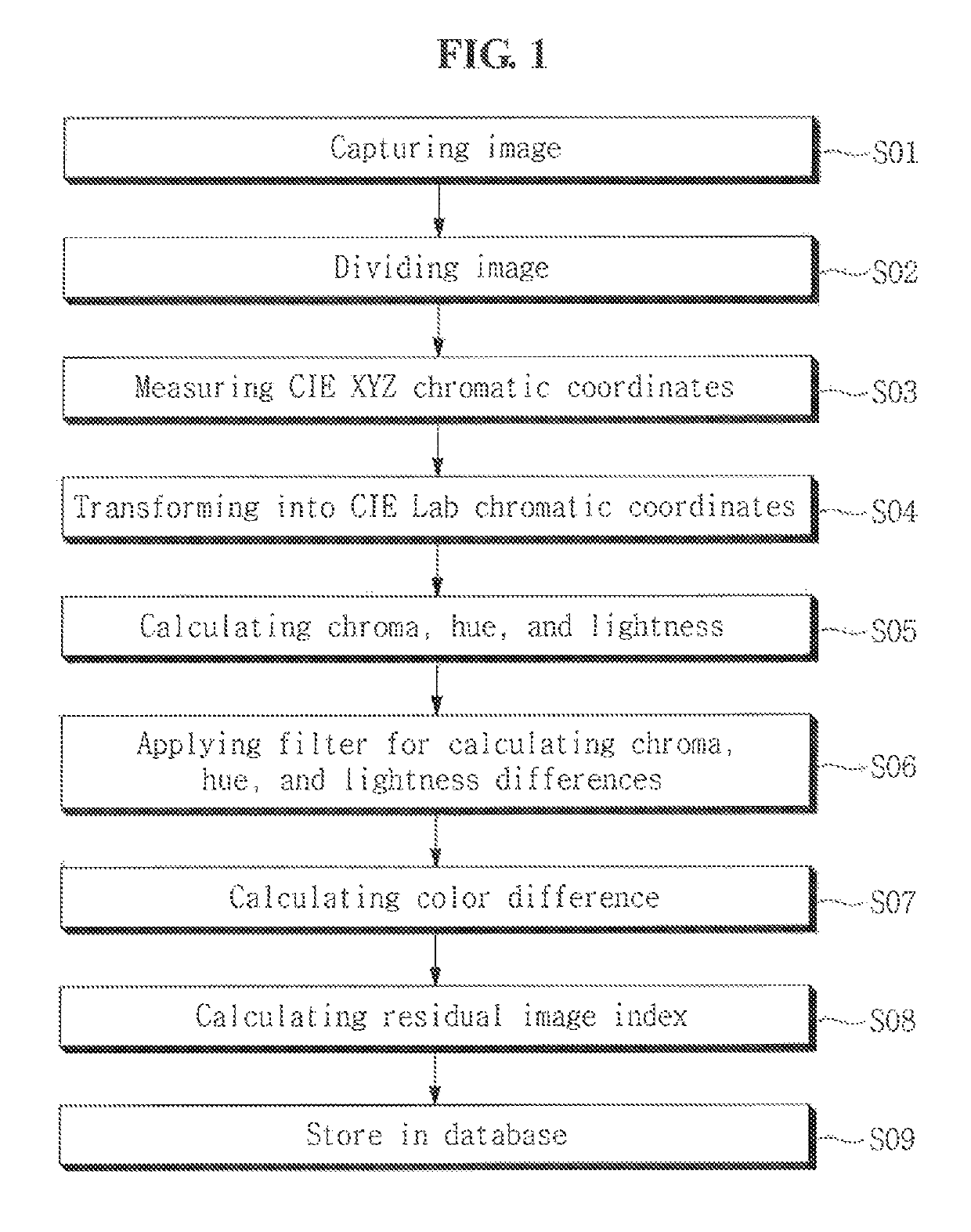

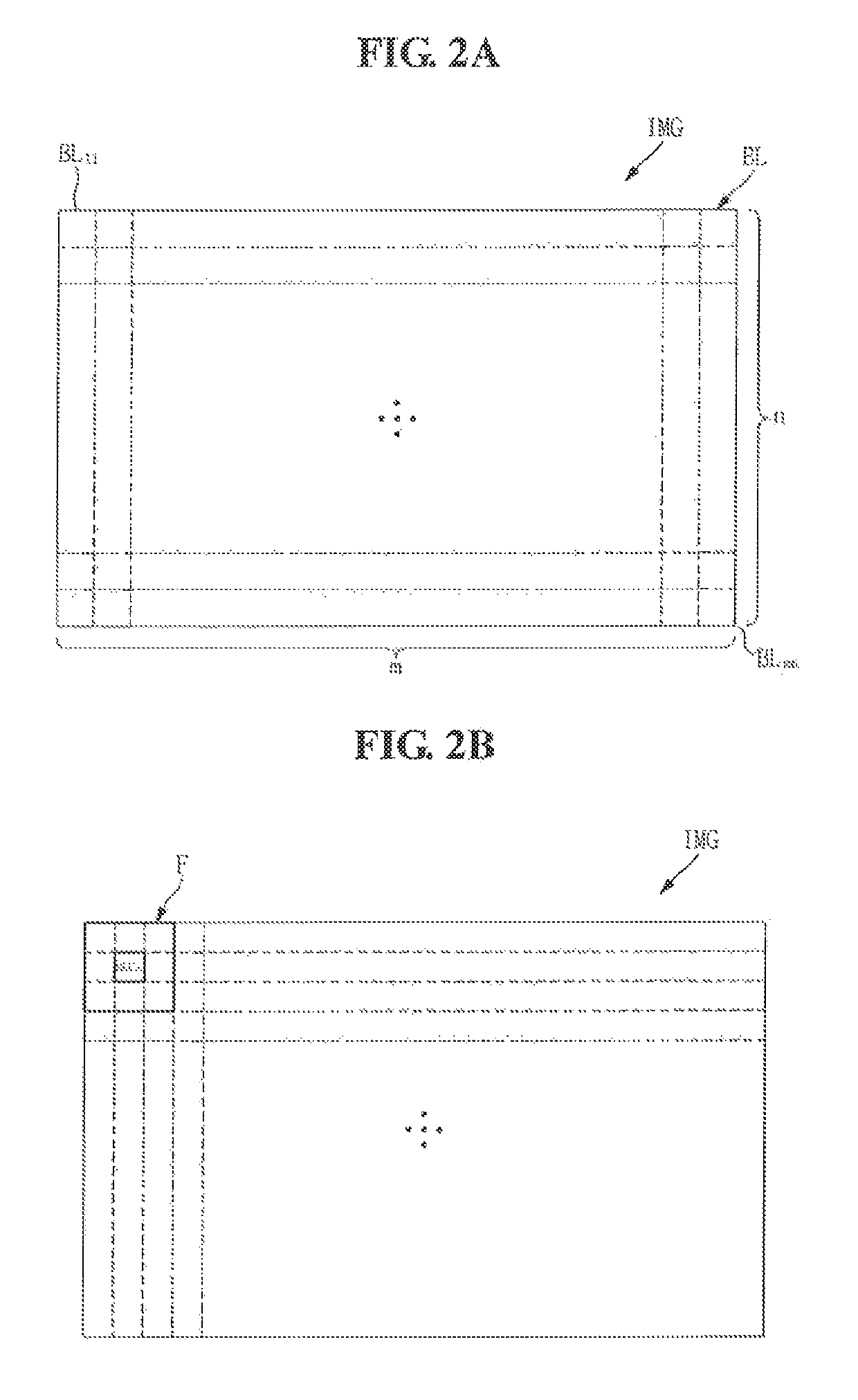

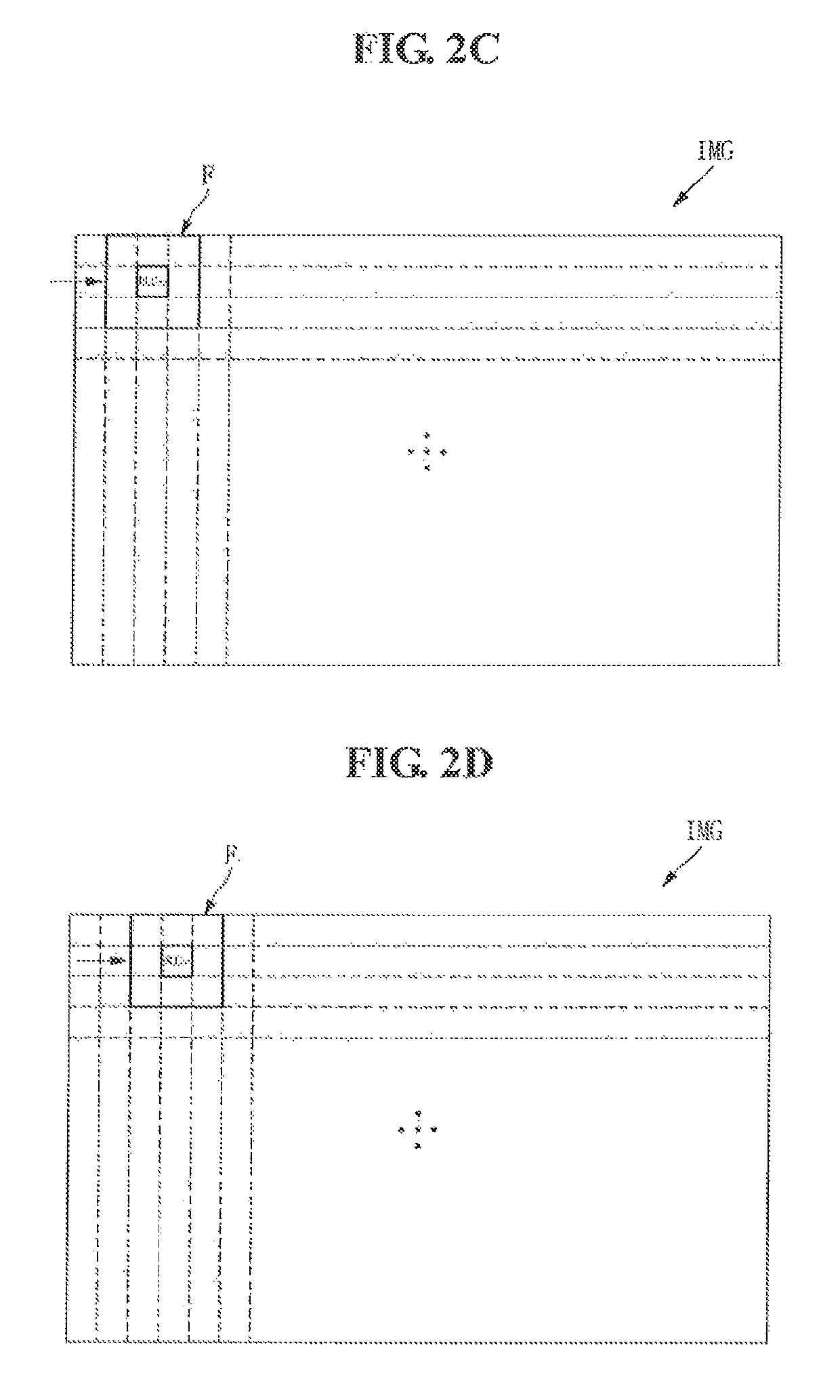

Device for determining residual image of display device and method for determining residual image of display device

ActiveUS20180295356A1Improve afterimage problemStatic indicating devicesTelevision systemsPattern recognitionDisplay device

Owner:SAMSUNG DISPLAY CO LTD

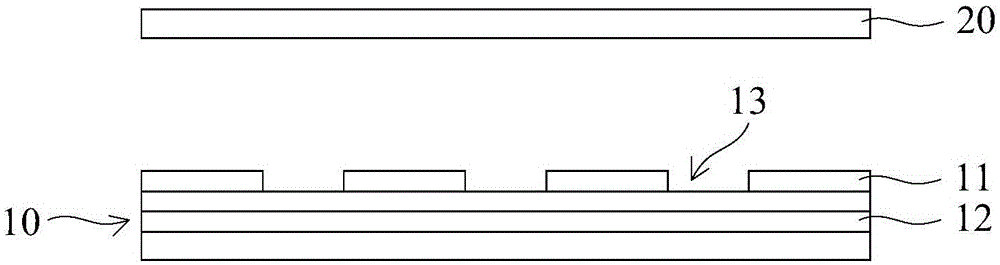

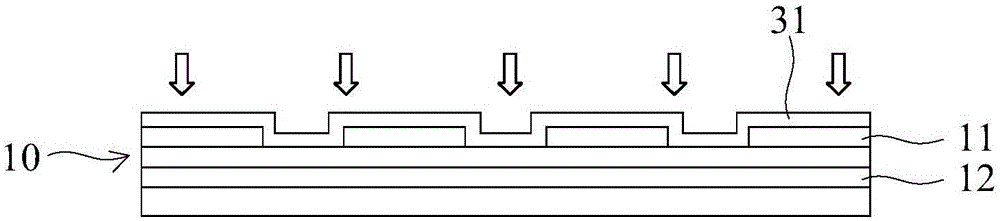

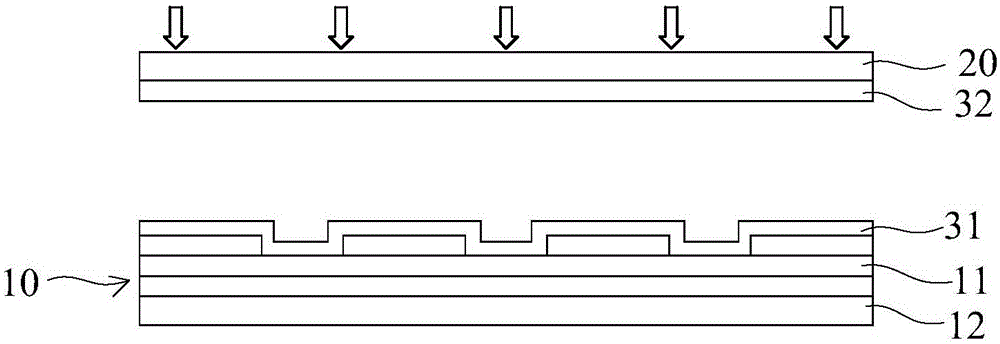

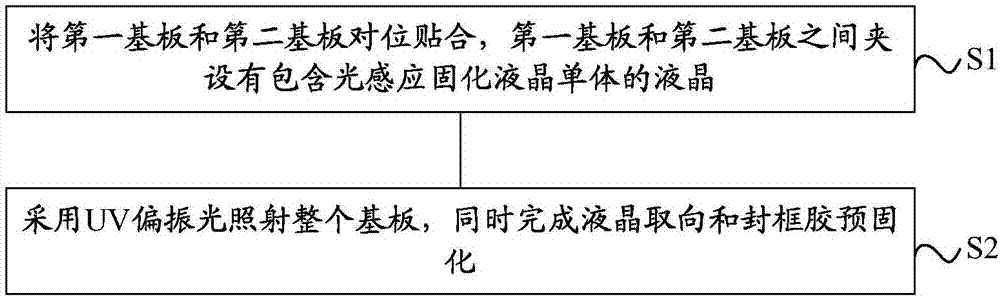

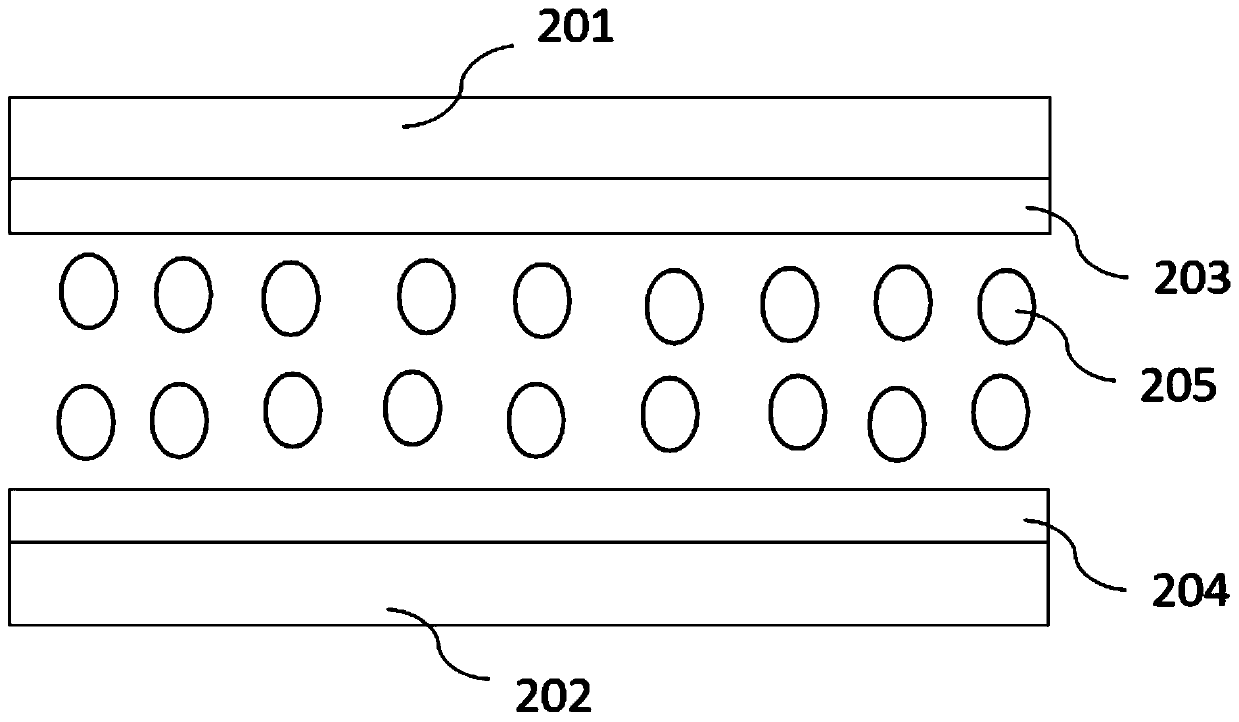

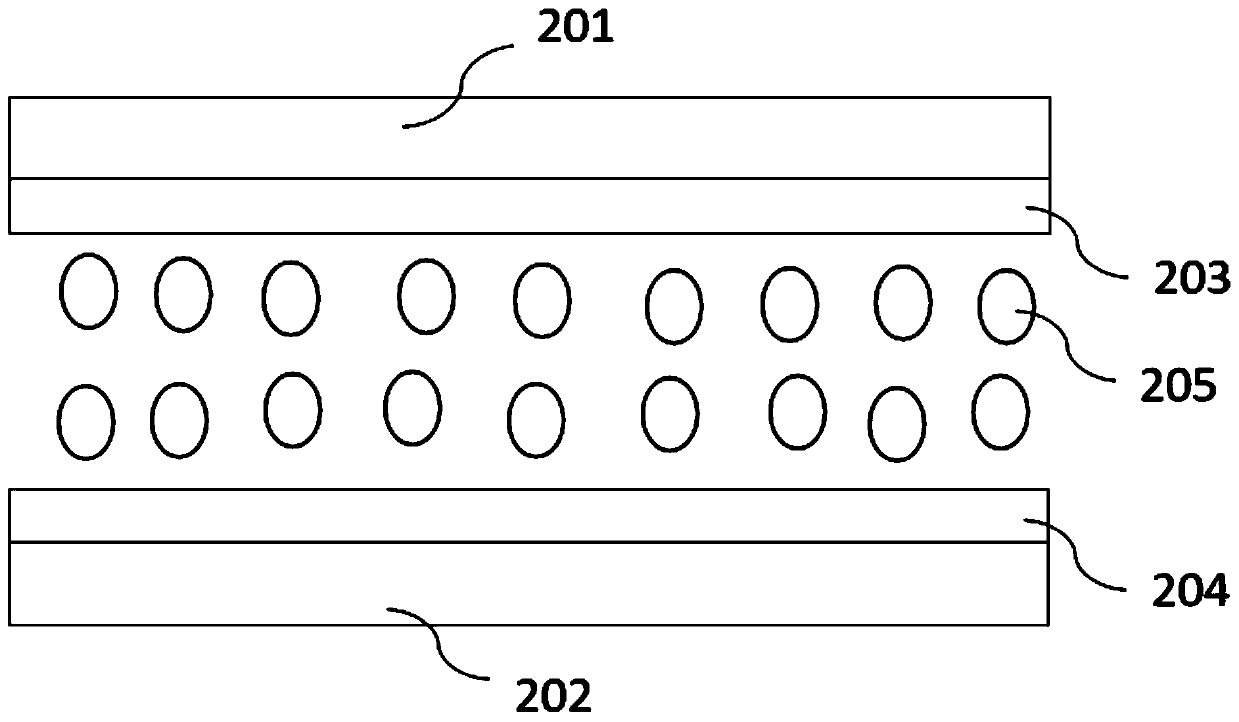

Display panel, preparation method of display panel, and display device

ActiveCN107402477AImprove afterimage problemImprove afterimageNon-linear opticsDisplay deviceUltraviolet

The invention discloses a display panel, a preparation method of the display panel, and a display device, and belongs to the technical field of display. The preparation method of the display panel comprises the steps of binding a first substrate and a second substrate in a contraposition manner, arranging liquid crystal comprising a photosensitive curing liquid crystal monomer between the first substrate and the second substrate in a clamping manner, irradiating the whole substrate by UV (ultraviolet) polarized light, and completing liquid crystal orientation and frame seal glue precuring. The method simplifies a preparation technology process of the display panel, lowers the cost, and improves the productive capacity. When the whole substrate is irradiated by the UV polarized light, the photosensitive curing liquid crystal monomer forms a polymer grid on the surface of an orientation layer under irradiation of the UV polarized light, so that a surface anchorage force of the orientation layer is increased, and a residual image and a residual shadow of the display panel are improved. The embodiment of the invention further provides the display panel prepared by the preparation method and the display device comprising the display panel.

Owner:BOE TECH GRP CO LTD +1

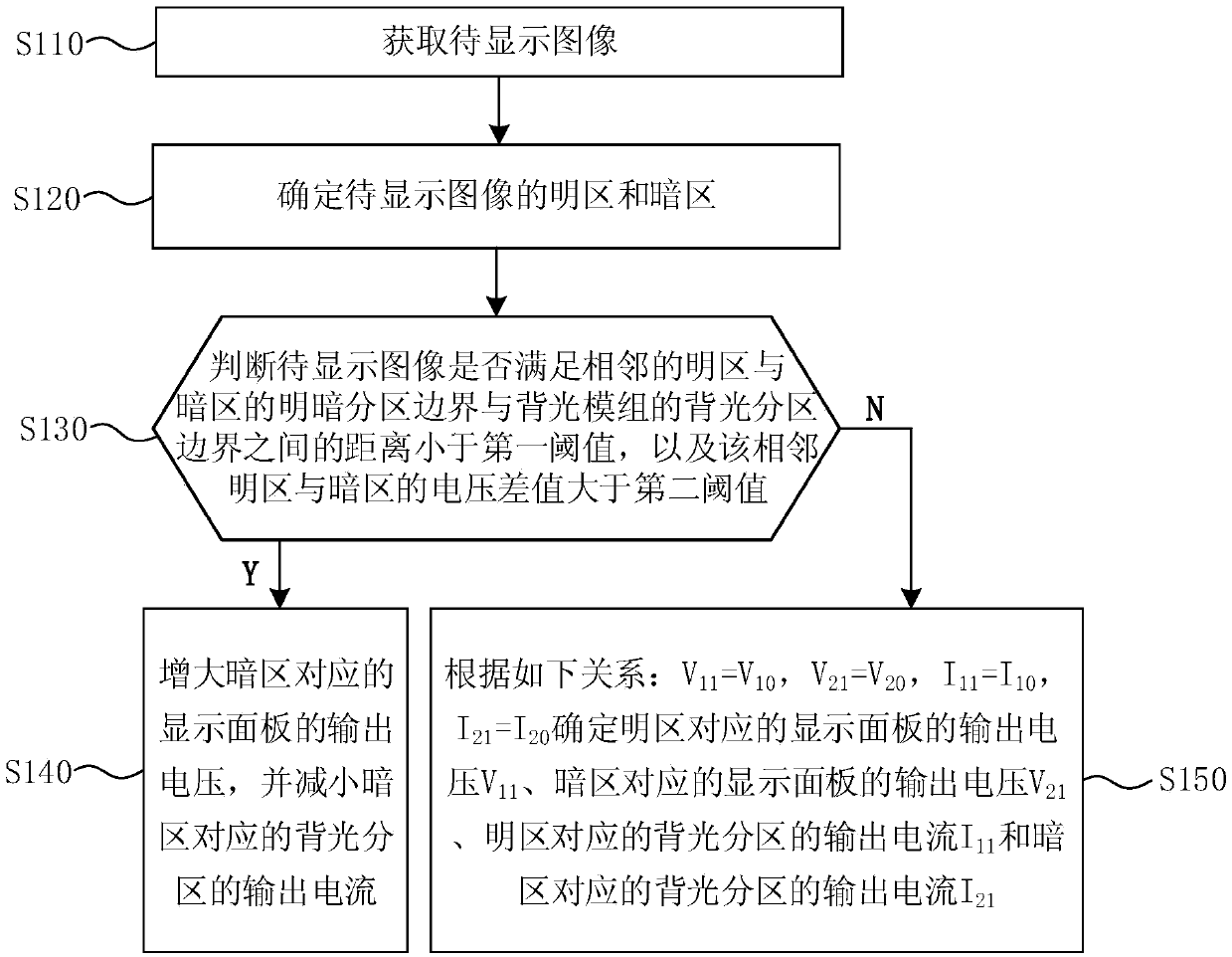

Display method of display device and display device

ActiveCN109686324AIncrease the output voltageReduce voltage differenceStatic indicating devicesPower flowDisplay device

The embodiment of the invention discloses a display method of a display device and the display device. The display method includes the following steps: acquiring a to-be-displayed image; determining bright areas and dark areas of the to-be-displayed image; judging whether the to-be-displayed image meets the requirements that the distance between the bright and dark partition boundary of the adjacent bright area and dark area and the backlight partition boundary of a backlight module is less than a first threshold, and the voltage difference between the adjacent bright area and dark area is greater than a second threshold; if the requirements are met, increasing the output voltage of a display panel corresponding to the dark areas, and reducing the output current of a backlight partition corresponding to the dark areas; and if the requirements are not met, adopting an initial output scheme to determine the output voltage of the display panel and the output current of the corresponding backlight partition. According to the display method of the display device provided by the embodiment of the invention, the difference between the output voltages of the adjacent bright area and dark area can be reduced, the working temperature of the backlight partition can be lowered, and the problem of residual images can be further improved on the premise of ensuring normal image display.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

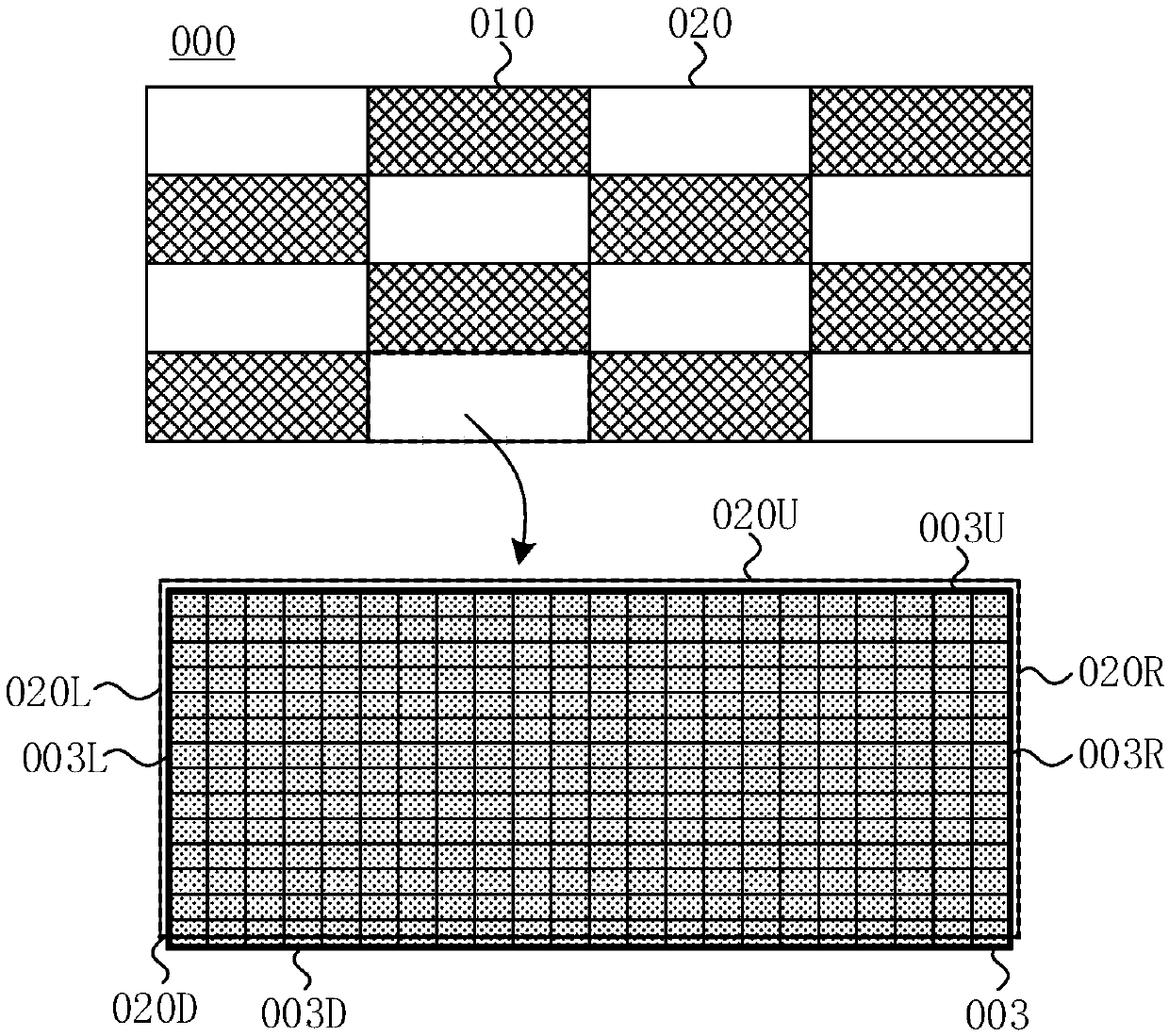

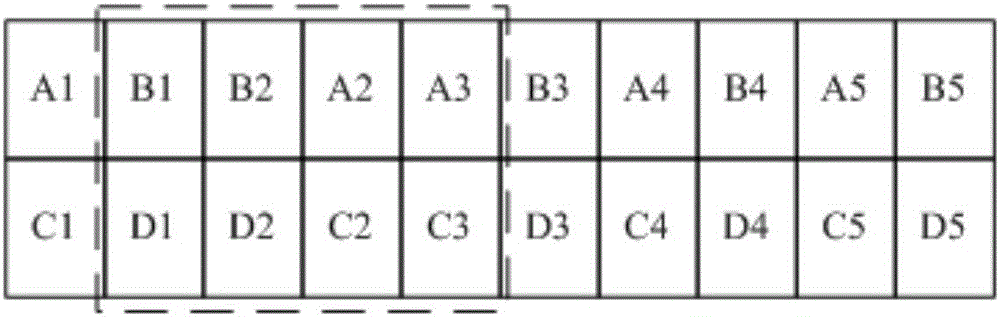

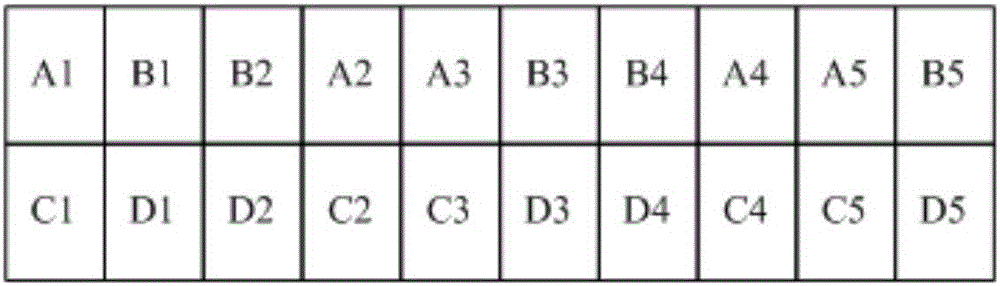

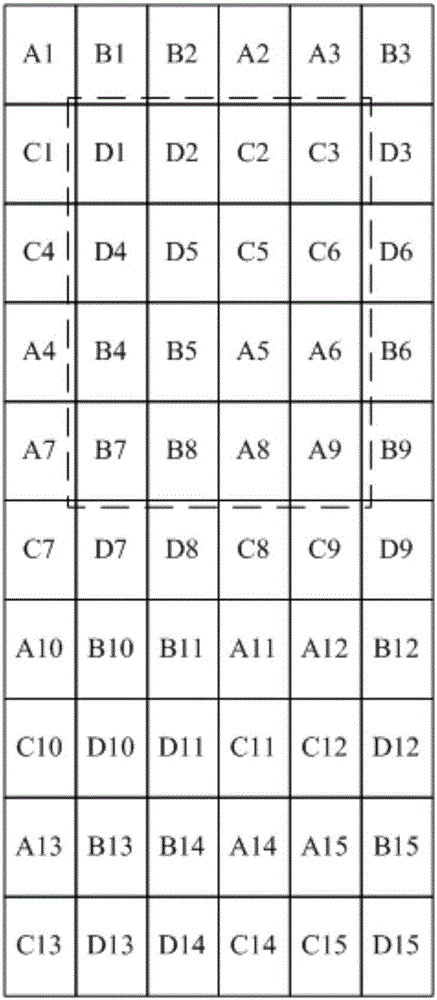

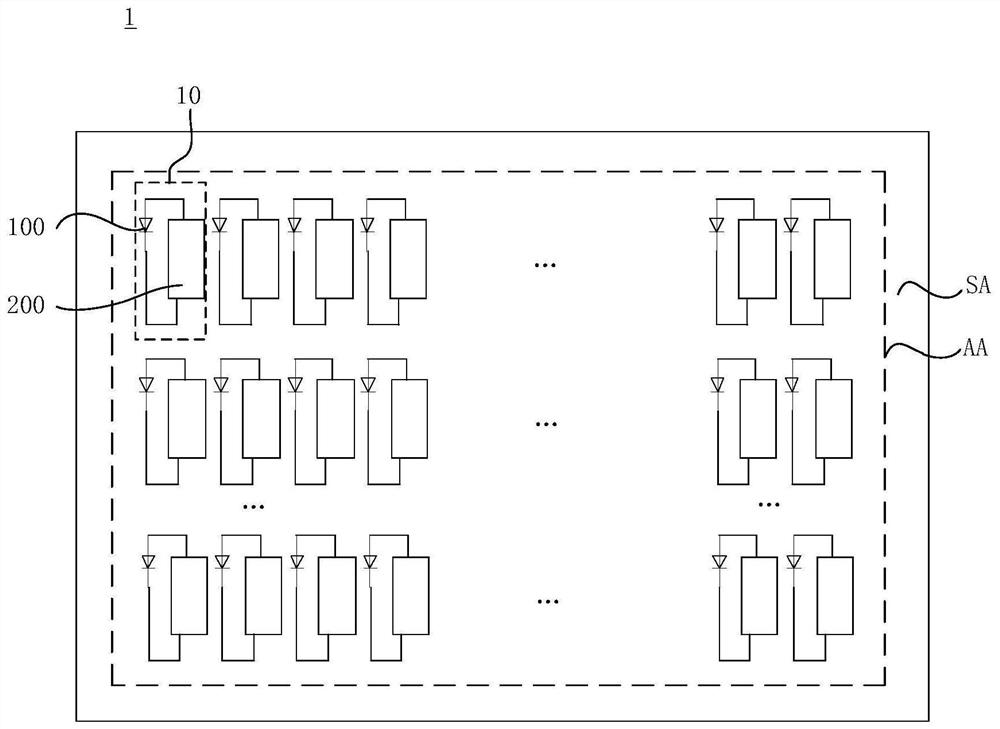

Array substrate, driving method, organic electroluminescence display panel and display device

InactiveCN106024829AImprove afterimage problemStatic indicating devicesSolid-state devicesDisplay deviceOrganic electroluminescence

The invention discloses an array substrate, a driving method, an organic electroluminescence display panel and a display device. A color resistance arrangement method of all sub pixels in adjacent-row pixels in at least one group of three adjacent rows of pixels in the array substrate is changed to enable the color resistance colors of two adjacent-row sub pixels belonging to two different pixels to be identical. Therefore, in each row of pixels in each group of pixels, assumed that two sub pixels with same adjacent-row color resistance color form a sub pixel unit and four sub pixel units with different color resistance colors form a pixel unit, in each pixel unit, the number of the sub pixels with the same color resistance color is two, and when a static image is displayed for a long time in a preset region of the organic electroluminescence display panel, each sub pixel in the region can have restoring time by driving the two sub pixels with the same color resistance color in each pixel unit in turns, so that the problem of residual image in the preset region of the organic electroluminescence display panel can be improved.

Owner:BOE TECH GRP CO LTD

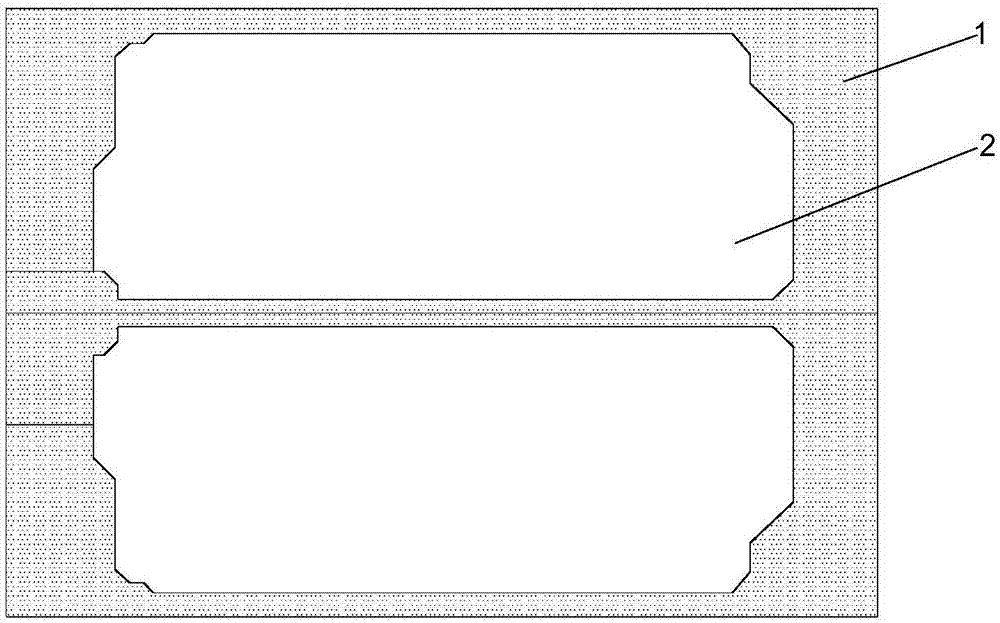

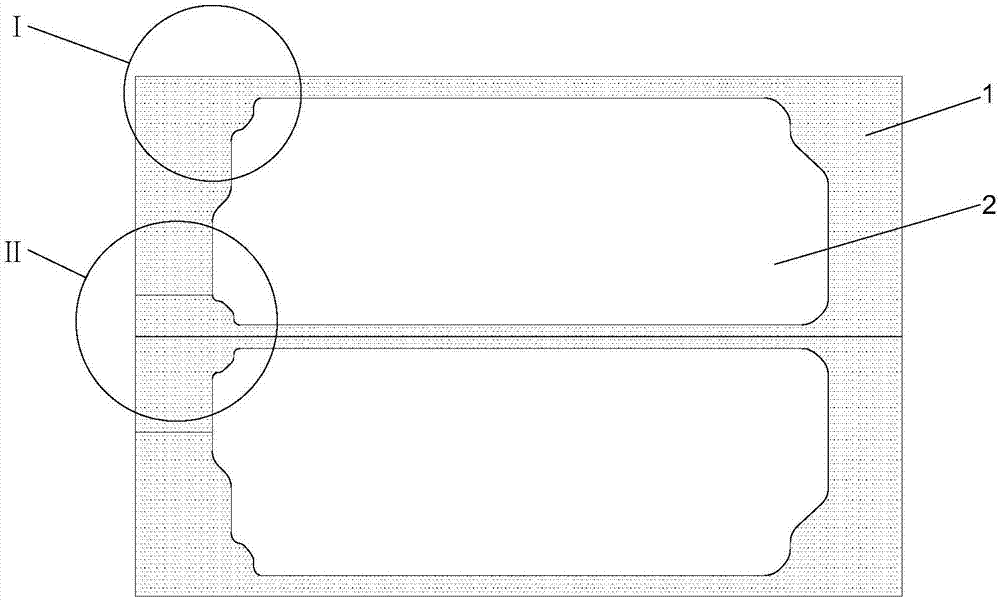

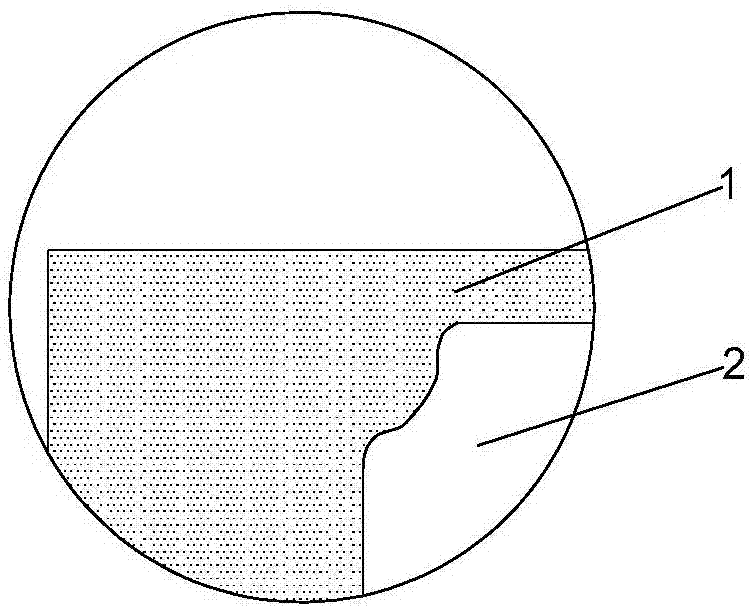

Mask plate, substrate and display device

InactiveCN106997147AImprove afterimage problemRestore clarityOriginals for photomechanical treatmentDisplay deviceResidual charge

The invention relates to the technical field of display device preparation and discloses a mask plate, a substrate and a display device. The mask plate is applied to display device preparation and comprises a panel, wherein a plurality of openings corresponding to pixel units on the display device in a one-to-one mode are formed in the panel, and every two adjacent edges in a corner of each opening are in smooth transition. When the mask plate is matched with a high-resolution exposure machine to perform picture composition, a pattern of the mask plate can be more clearly and accurately restored; furthermore, two adjacent edges at a corner of an opening area of the pattern are in smooth transition, so that electric charges are not prone to being gathered, and washing of residual charged particles is facilitated; thus, the display device prepared from the mask plate disclosed by the invention has an effect of improving residual images.

Owner:BOE TECH GRP CO LTD +1

Plasma display device

InactiveUS20100245303A1Preventing variation in discharge intensityImprove afterimage problemAddress electrodesSustain/scan electrodesDisplay deviceElectrode pair

Owner:PANASONIC CORP

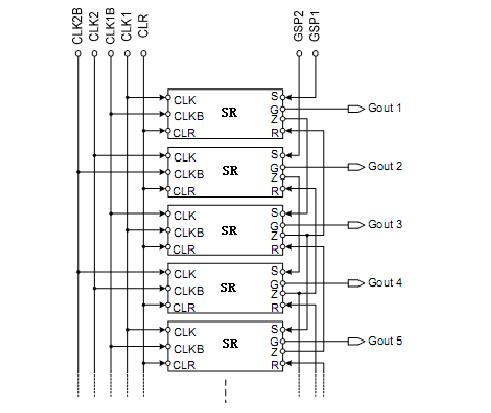

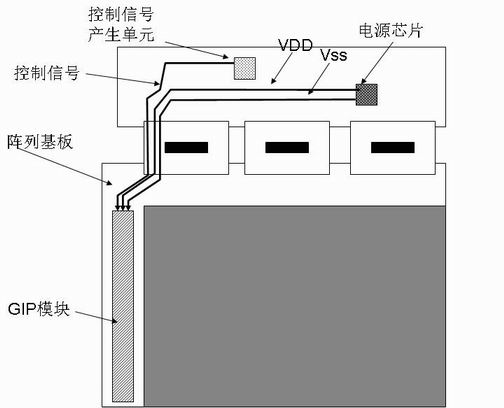

Method for improving picture quality of GIP (Gate-in-Panel) liquid crystal display panel

InactiveCN101968952AImprove afterimage problemSolve the problem of afterimage after shutdownStatic indicating devicesLiquid-crystal displayRadiometer

The invention relates to a method for improving the picture quality of a GIP (Gate-in-Panel) liquid crystal display panel, which is characterized in that a changeover switch is additionally arranged between a TFT (Thin Film Transistor) power-on voltage VDD and a TFT power-off voltage Vss of a GIP unit on a printed circuit board, so that the voltage of VDD is switched to a conducting wire of Vss and is output to the GIP unit when the liquid crystal display panel is powered off, and each scan line outputs the TFT power-on voltage VDD, the Vss voltage is equal to the VDD voltage and is input to each SR (Scanning Radiometer) unit through an array substrate to neutralize the voltage of pixels. The voltage value supplied to the conducting wire of Vss is switched to VDD by controlling the switch unit between VDD and Vss, so that the voltages input to all scan lines during power-off are VDD to turn on all TFT, and the purpose of improving a residual image is achieved without changing the design of the array substrate.

Owner:NANJING CEC PANDA LCD TECH

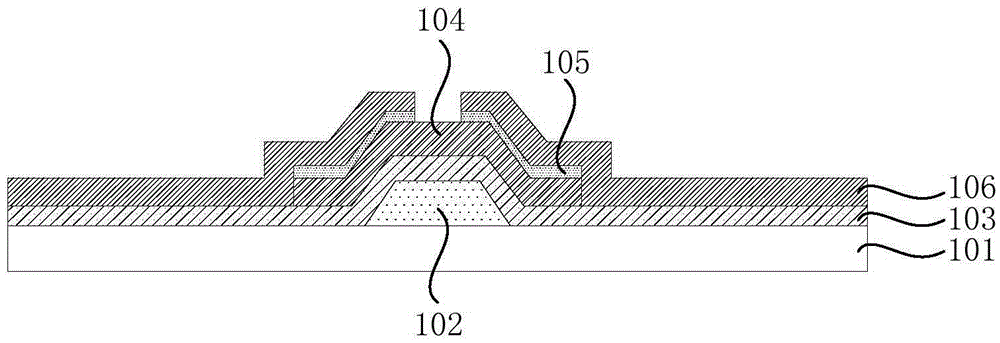

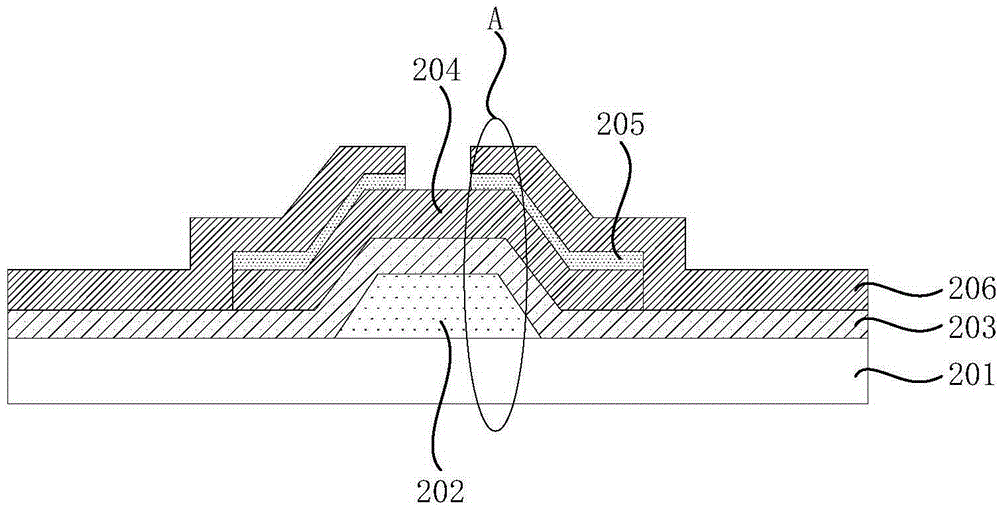

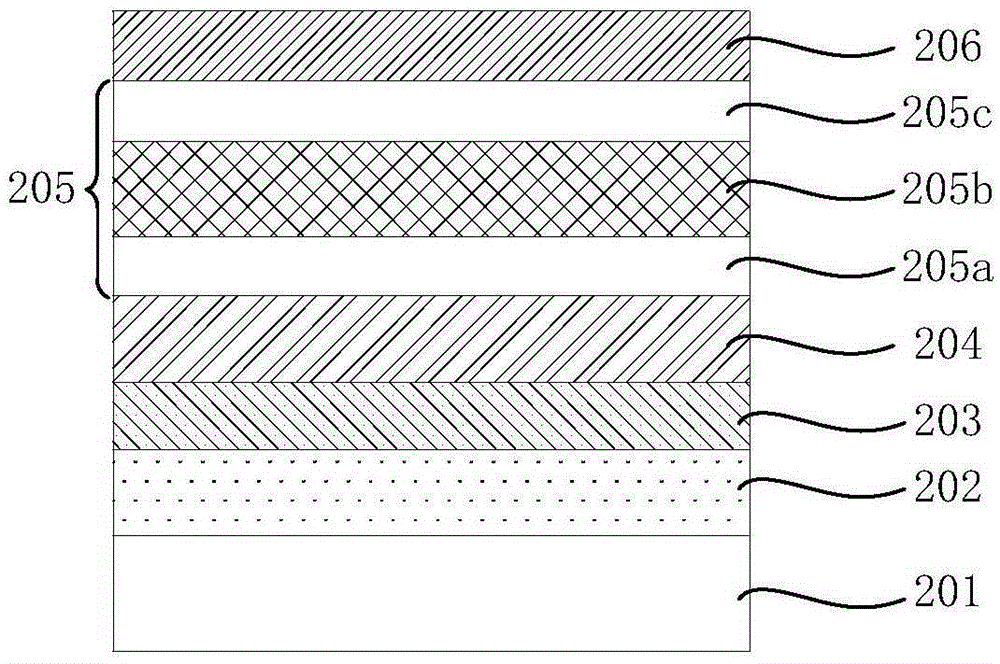

Thin film transistor and array substrate

ActiveCN105405892AReduce leakage currentImprove afterimage problemTransistorSolid-state devicesPhysicsHigh impedance

The invention discloses a thin film transistor and an array substrate. The thin film transistor comprises a grid electrode, a grid electrode insulation layer, an active layer, a first material layer and a source / drain electrode, wherein the grid electrode insulation layer is formed on the grid electrode and covers the grid electrode; the active layer is formed on the grid electrode insulation layer; the first material layer is formed on the active layer; the source / drain electrode is formed on the first material layer; the first material layer comprises a first Ohmic contact layer, a second Ohmic contact layer and a high-impedance inclusion layer, wherein the high-impedance inclusion layer is formed between the first Ohmic contact layer and the second Ohmic contact layer; and the impedance of the high-impedance inclusion layer is greater than the impedance of the first Ohmic contact layer and the second Ohmic contact layer. The thin film transistor can effectively lower leakage current which is in the presence between the source / drain electrode and the active layer and has a simple manufacture technology.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

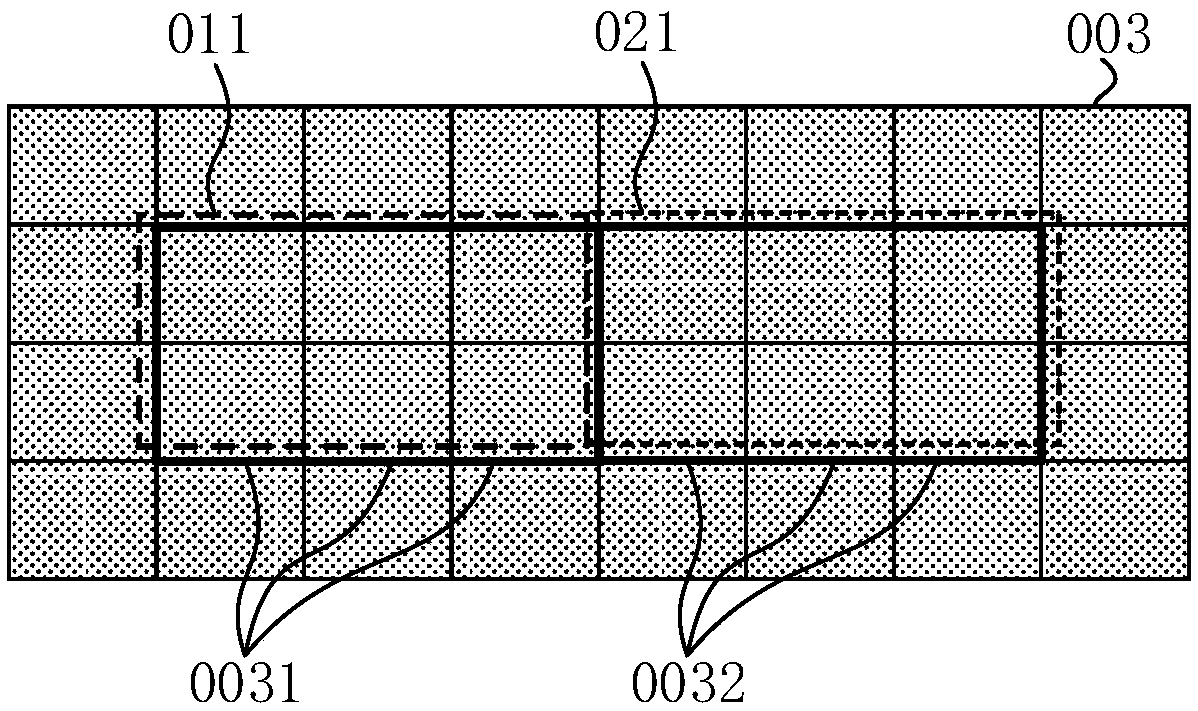

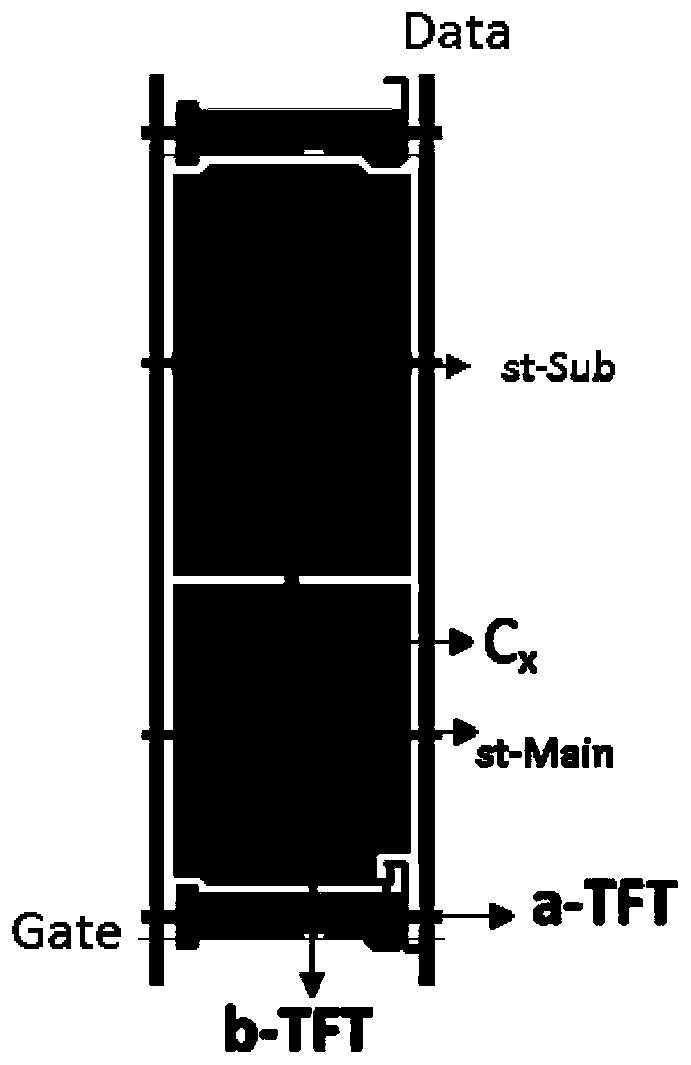

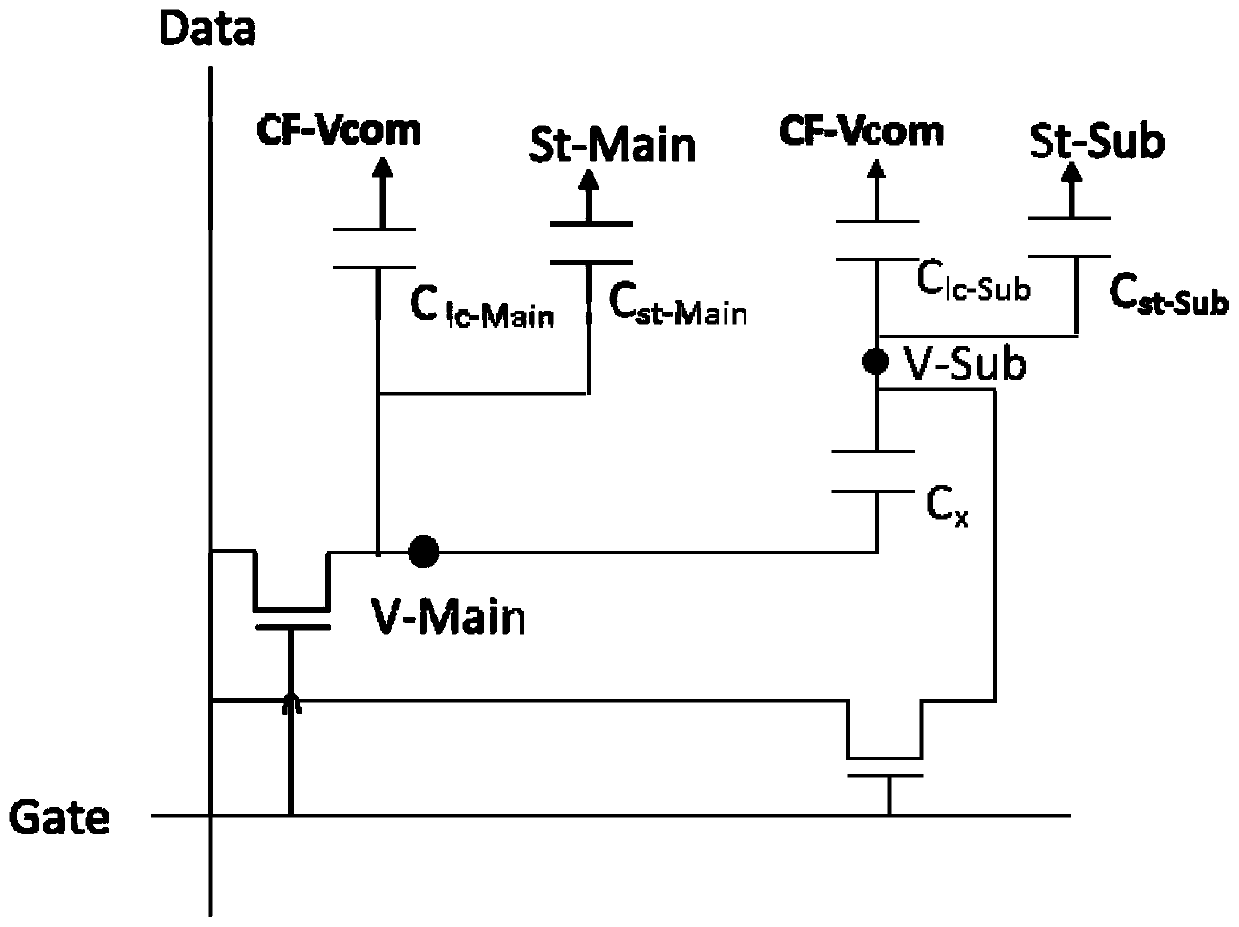

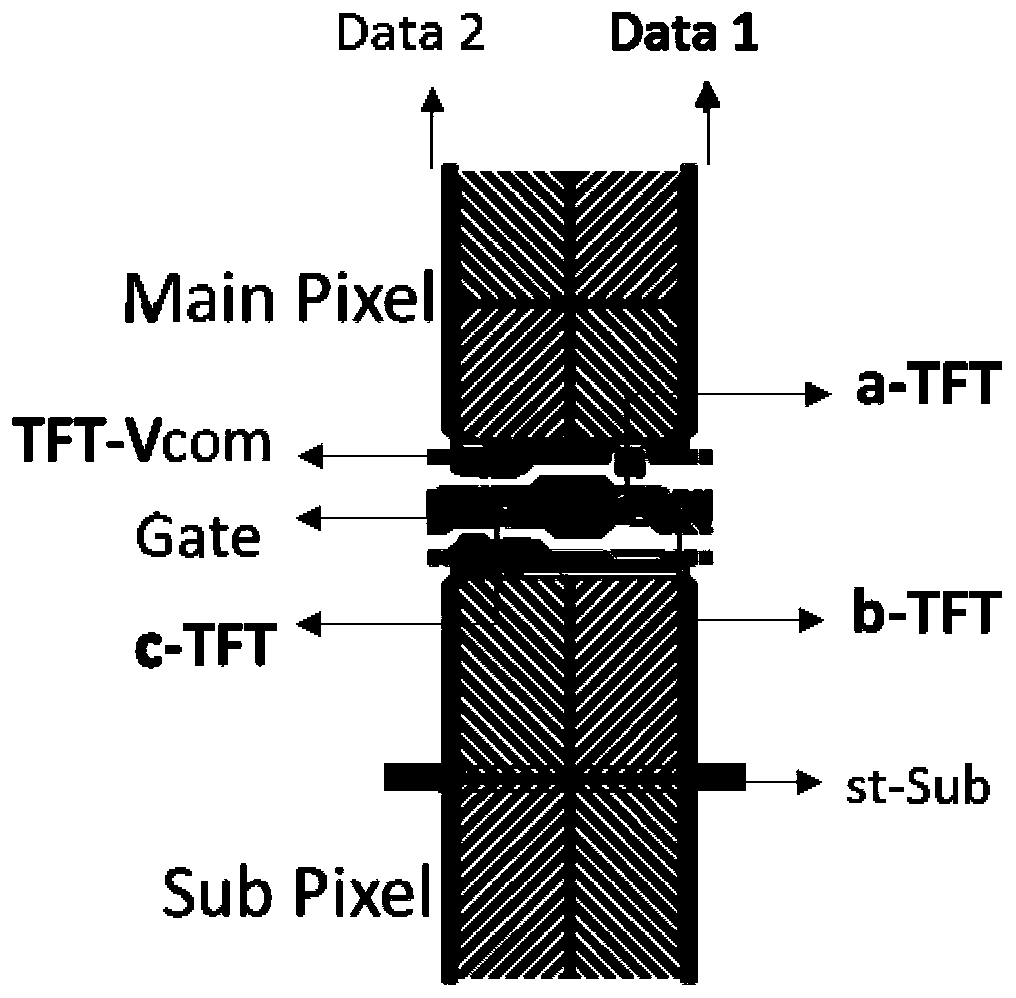

Pixel unit, pixel array and liquid crystal panel thereof

ActiveCN111381406AFast charging and dischargingEnhanced charge release abilityNon-linear opticsScan lineEngineering

The invention relates to a pixel unit, a pixel array and a liquid crystal panel thereof; each pixel unit comprises a first switch, a second switch and a third switch; the first switch and the second switch are electrically connected with the same data line and the same scanning line, the third switch is connected with the second switch in parallel, and the third switch is electrically connected with the same scanning line; the main pixel electrode is electrically connected with the first switch; the sub-pixel electrode is electrically connected with the second switch and the third switch; thecoupling electrode is electrically connected with the second switch and the third switch; and the third switch is also electrically connected with the common line. By adding the third switch and connecting the third switch and the second switch in parallel, the charge and discharge speed of the second storage capacitor is increased, the charge release capacity of the second storage capacitor is enhanced, and residual images can be improved.

Owner:XIANYANG CAIHONG OPTOELECTRONICS TECH CO LTD

Plasma display device

InactiveUS7852296B2Improve afterimage problemPreventing variation in discharge intensityStatic indicating devicesDisplay deviceElectrode pair

Owner:PANASONIC CORP

Liquid crystal composition, and liquid crystal display including the same

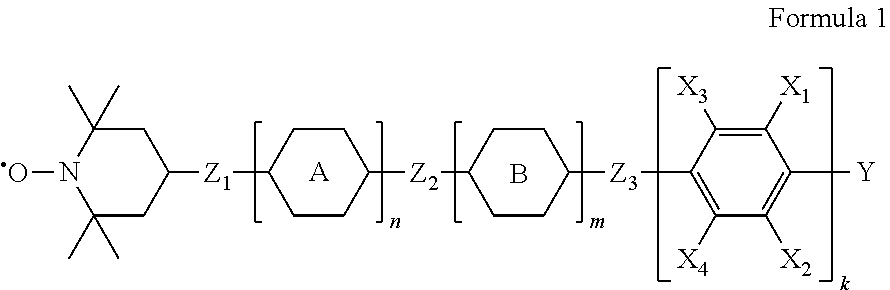

InactiveUS20160230091A1Improve advancedHigh-rate response characteristicLiquid crystal compositionsNon-linear opticsHalogenSingle bond

Disclosed is a liquid crystal composition. The liquid crystal composition includes liquid crystal molecules including at least one of a liquid crystal compound having an alkenyl group and a liquid crystal compound having an alkoxy group, and a first stabilizer including a compound having a structure represented by Formula 1:where n is 0 or 1; m is 0 or 1; k is 0 or 1; Z1, Z2, and Z3 are each independently a single bond, —C═C—, —OCO—, —COO—, —CF2O—, or a C1 to C5 alkylene group; X1, X2, X3, and X4 are each independently hydrogen or halogen; Y is hydrogen, an alkylene group, an alkoxy group, a hydroxyl group, —NHCOCH3, or ═O; and A and B are cyclic compounds.

Owner:SAMSUNG DISPLAY CO LTD

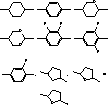

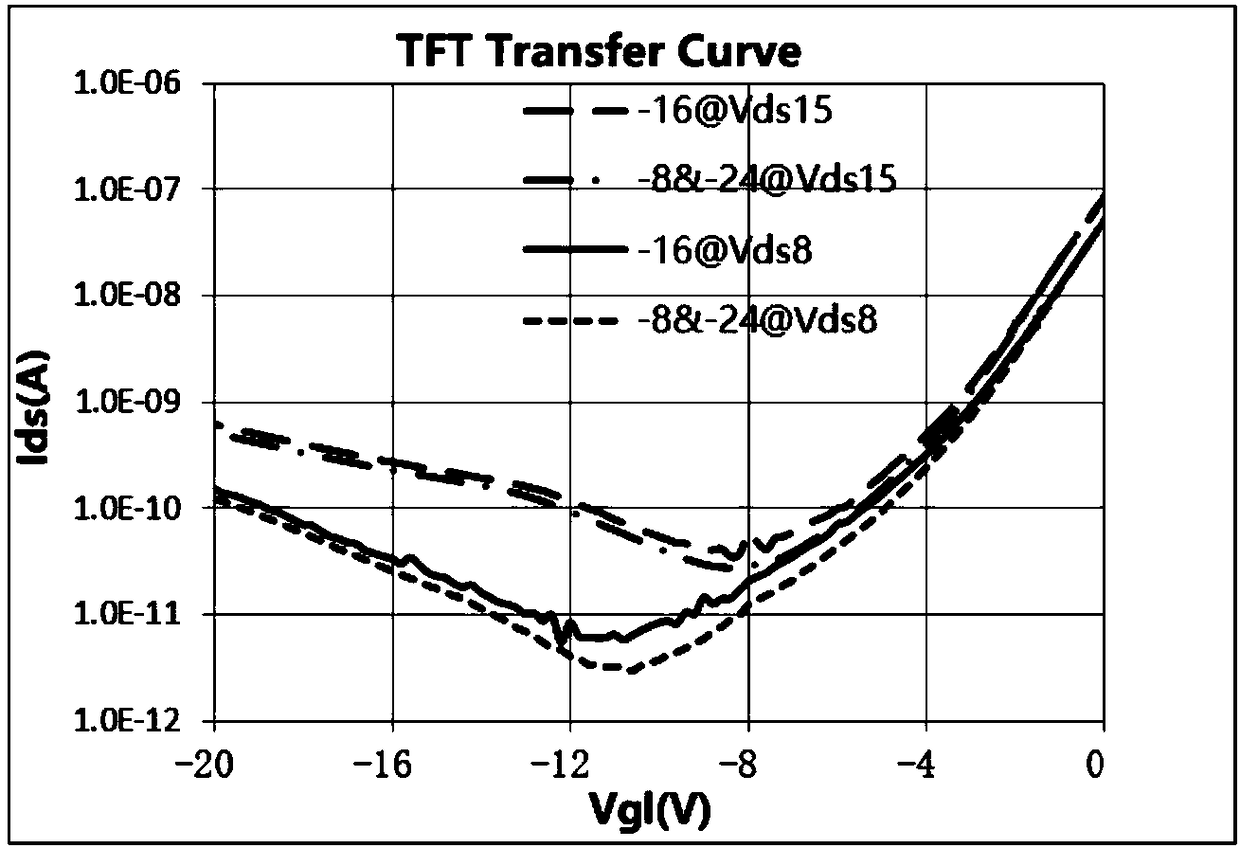

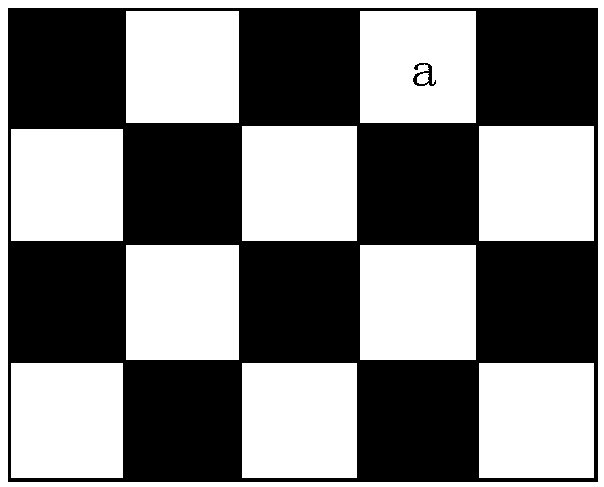

Trifluoromethoxy-containing liquid crystal composition and applications thereof

ActiveCN109722252AGood for afterimage recoveryImprove afterimage problemLiquid crystal compositionsLiquid-crystal displayDisplay device

The invention relates to a liquid crystal material and application fields thereof, particularly to a trifluoromethoxy-containing liquid crystal composition and applications thereof, wherein the liquidcrystal composition comprises compounds represented by general formulas I, II and III. According to the present invention, the liquid crystal composition has large elastic constant, easily achieves the afterimage recovery of liquid crystal display devices, can improve the afterimage problem of liquid crystal display devices and improve the quality of liquid crystal display devices, can particularly improve the display effects in TN, IPS or FFS mode display devices, and is especially suitable for IPS and FFS mode liquid crystal display devices. The formulas I, II and III are defined in the specification.

Owner:BEIJING BAYI SPACE LCD MATERIALS TECH

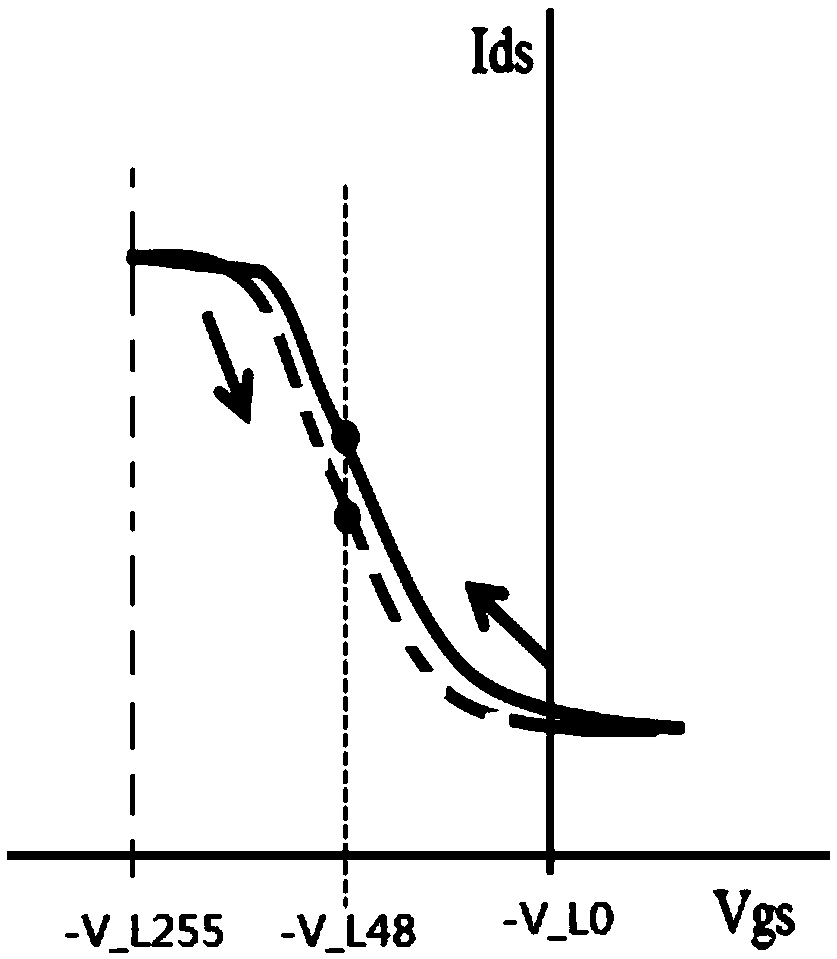

Display control method and display apparatus

InactiveCN108305591AIncrease the number ofReduce driftStatic indicating devicesEngineeringAfterimage

Embodiments of the invention provide a display control method and a display apparatus. The method includes: setting a current driving voltage of a thin film transistor TFT as an initial driving voltage; detecting a continuous display time of a current frame image; determining a target driving voltage corresponding to the continuous display time; and adjusting the current driving voltage accordingto the target driving voltage. According to the method, the change of the continuous display time of the current frame image is detected, the corresponding target driving voltage is determined, the current driving voltage of the TFT is further adjusted according to the target driving voltage, the number of the current driving voltages can be increased, and the drift of the TFT and the afterimage caused thereby can be reduced.

Owner:BOE TECH GRP CO LTD +1

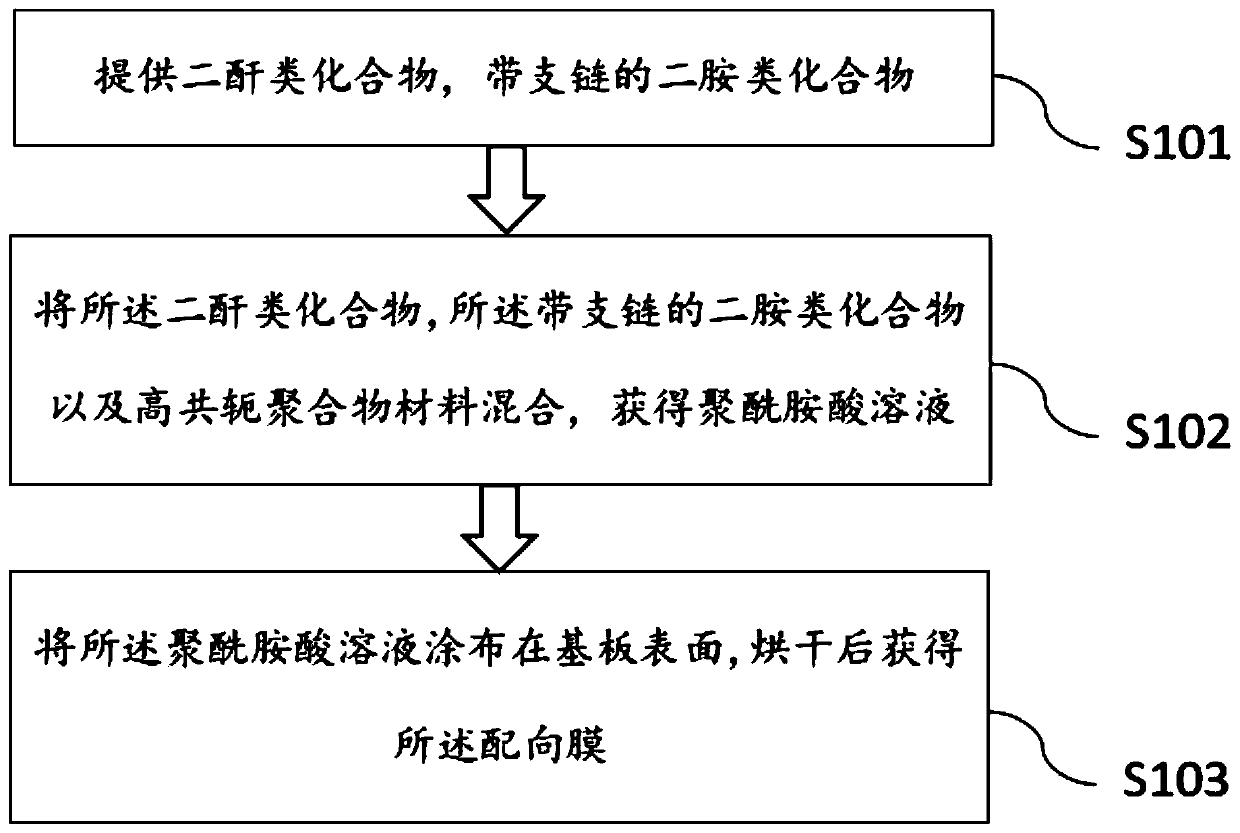

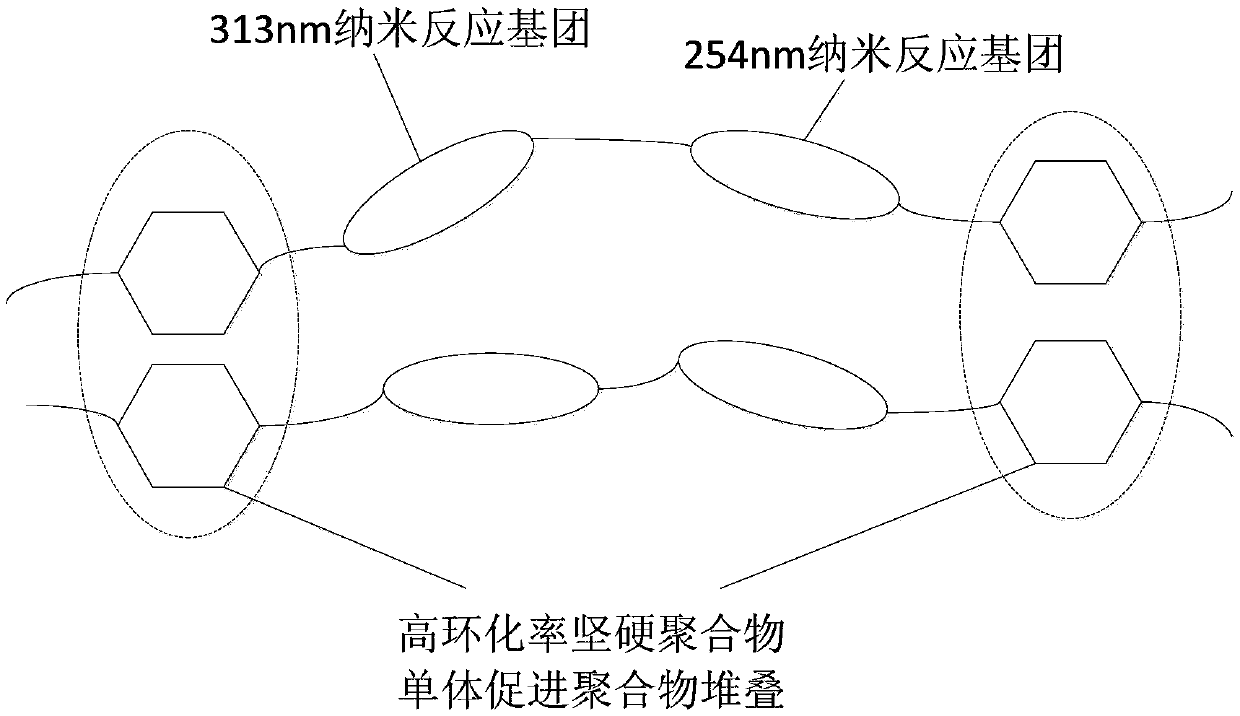

Alignment film, preparation method thereof and display panel

InactiveCN111117666ALower bulk resistanceQuick releaseLiquid crystal compositionsNon-linear opticsFilm materialDiamine

The invention provides an alignment film. The alignment film is obtained by reacting a dianhydride compound, a diamine compound with a branched chain and a highly conjugated polymer material. By doping the highly conjugated polymer material into a conventional alignment film material, the body resistance of the alignment film material can be reduced, so that the residual direct-current bias voltage in a liquid crystal panel can be quickly released, and the technical effect of improving residual images is achieved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Plasma display apparatus

InactiveUS7755575B2Prevent misdischargeImprove afterimage problemStatic indicating devicesLow voltageEngineering

Provided is a plasma display apparatus. The plasma display apparatus includes a first electrode and a second electrode formed in parallel on an upper substrate, and a third electrode formed on a lower substrate to intersect with the first electrode and the second electrode. A driving signal is applied to the first electrode, the second electrode, and the third electrode in a reset period, an address period, and a sustain period per one subfield. The reset period comprises a setdown period. A difference between a setdown lowest voltage of the driving signal applied to the first electrode and a voltage applied to the second electrode in the setdown period is 1.2 times to 1.5 times of a sustain voltage.

Owner:LG ELECTRONICS INC

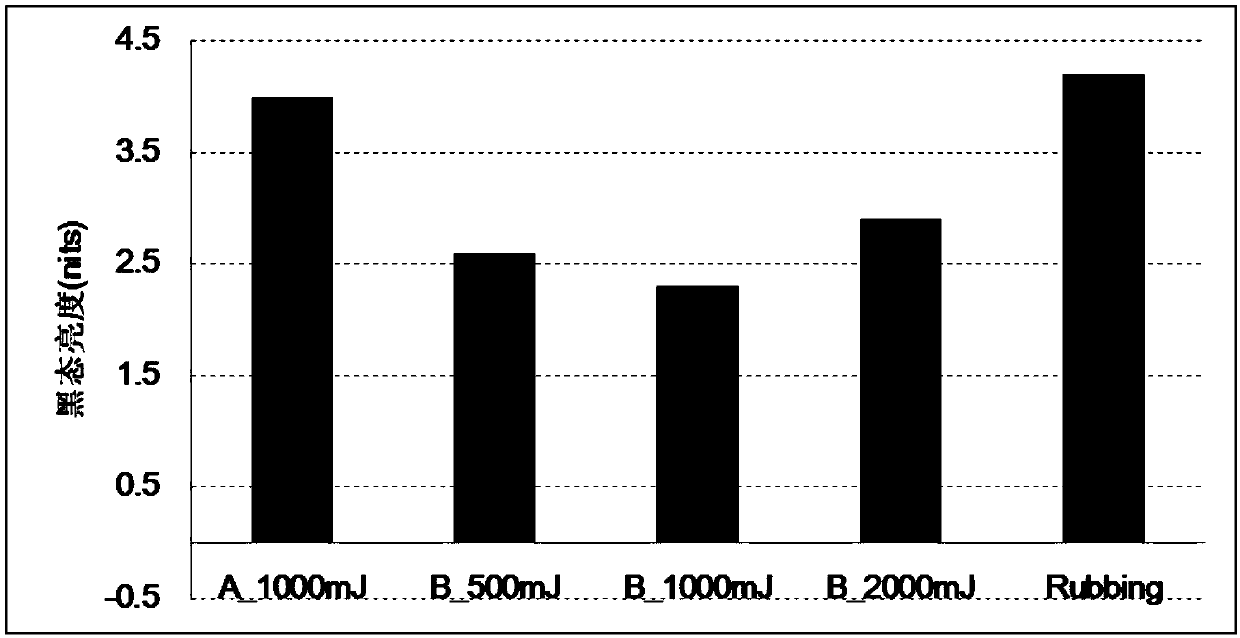

Liquid crystal aligning agent, liquid crystal aligning film and manufacturing method thereof, and panel and device comprising same

ActiveCN106544043BReduce the amount of DoseEasy alignmentLiquid crystal compositionsNon-linear opticsCrystallographyAfterimage

The invention relates to a liquid crystal alignment agent, a liquid crystal alignment film, a making method of the film, a panel including the film, and a device including the film. The above compound has multi-waveband ultraviolet photosensitivity, is sensitive to two wavebands, reduces the Dose amount of illumination, and can complete orientation only by 500-1000 mJ, so energy is saved, and the productivity is improved; and addition of a rigid group to the compound increases the orientation of AC voltage and improves the contrast and the afterimage.

Owner:XIAMEN TIANMA MICRO ELECTRONICS +1

Device for determining residual image of display device and method for determining residual image of display device

ActiveUS10291908B2Improve afterimage problemColor measuring devicesStatic indicating devicesPattern recognitionDisplay device

A method for determining residual images of a display device includes: dividing an image into a plurality of unit blocks; calculating a chroma, a hue, and a lightness of each unit block; applying a filter to the plurality of unit blocks to calculate a chroma difference, a hue difference, and a lightness difference; calculating a plurality of color difference based on the chroma, hue and lightness differences between the unit block and unit blocks adjacent to the unit block, a chroma weight constant, a hue weight constant, and a lightness weight constant; and calculating residual image indices for each unit block, where a residual image index is a maximum value of the plurality of color differences between the unit block and unit blocks adjacent to the unit block. The lightness weight constant is less than the chroma weight constant and the hue weight constant.

Owner:SAMSUNG DISPLAY CO LTD

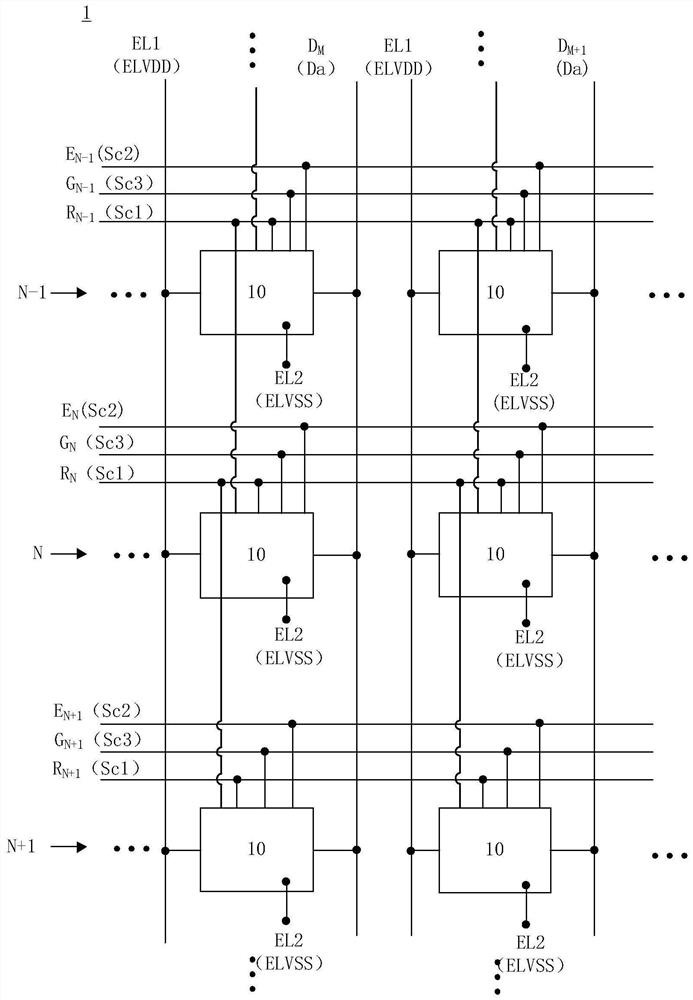

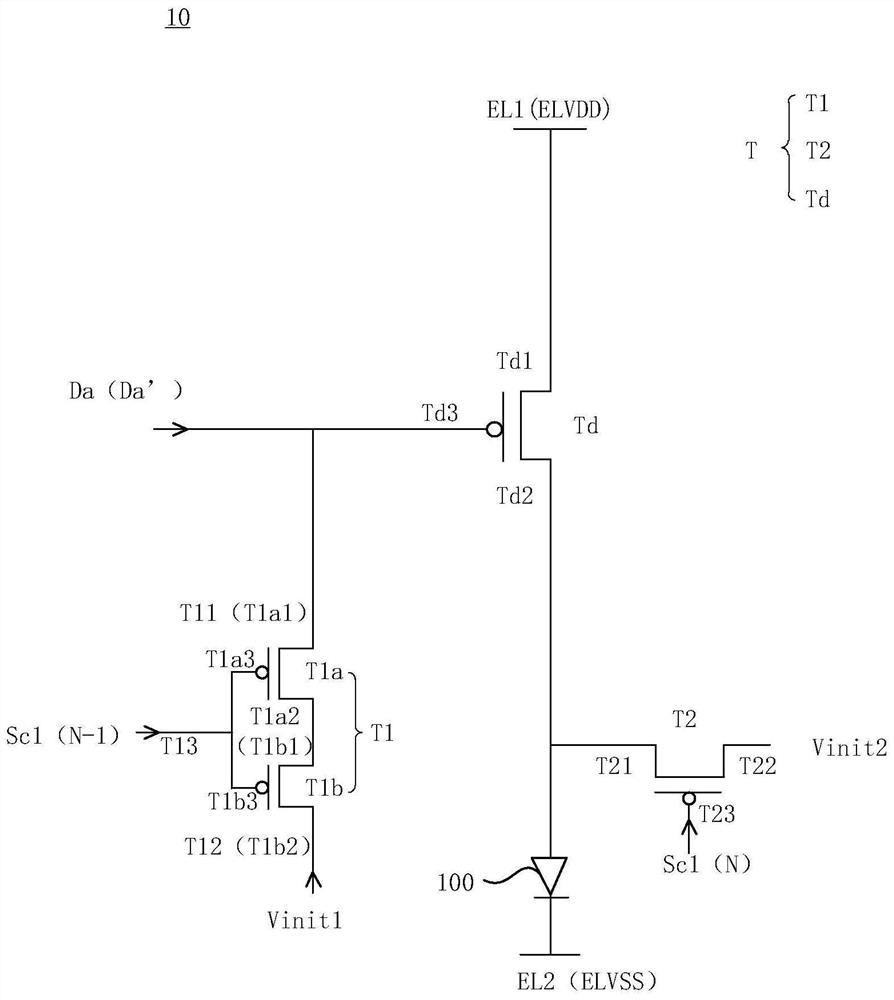

Pixel circuit, display panel and display device

PendingCN113725274AGood continuityEasy to initializeStatic indicating devicesSolid-state devicesDisplay deviceHemt circuits

The embodiment of the invention provides a pixel circuit, a display panel and a display device, which relate to the technical field of display, and are used for improving the bright spot problem of a display picture of the display panel on the premise of improving the residual image problem of the display picture of the display panel. The pixel circuit includes a light emitting device, a driving transistor, a first transistor, and a second transistor. The second electrode of the driving transistor is coupled to the light emitting device, and the driving transistor is configured to control the magnitude of current flowing through the first electrode and the second electrode in response to the voltage of the control electrode. The first electrode of the first transistor is coupled with the control electrode of the driving transistor, and the second electrode is configured to write a first initialization signal. A first electrode of the second transistor is coupled to the light emitting device, and a second electrode is configured to write a second initialization signal. The first transistor comprises at least two sub-transistors which are connected in series, and the width-to-length ratio of a channel of at least one sub-transistor is smaller than that of a channel of the second transistor.

Owner:CHENGDU BOE OPTOELECTRONICS TECH CO LTD +1