Manufacturing method of groove power device

A technology of power devices and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of thin gate oxide layer 103 damage, lower device yield, complex manufacturing process, etc., to increase the difficulty of the process , Simplified manufacturing process, low cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

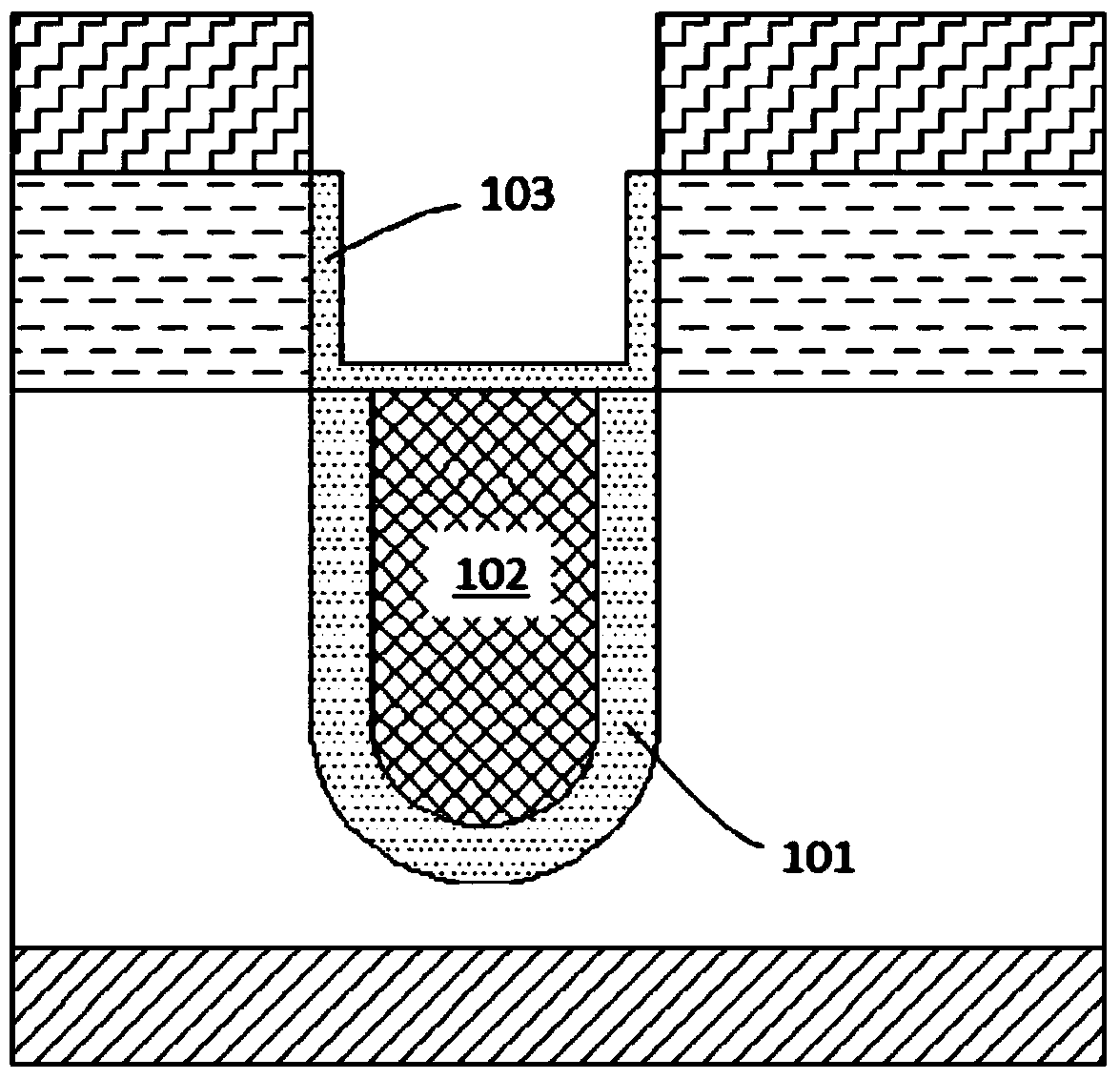

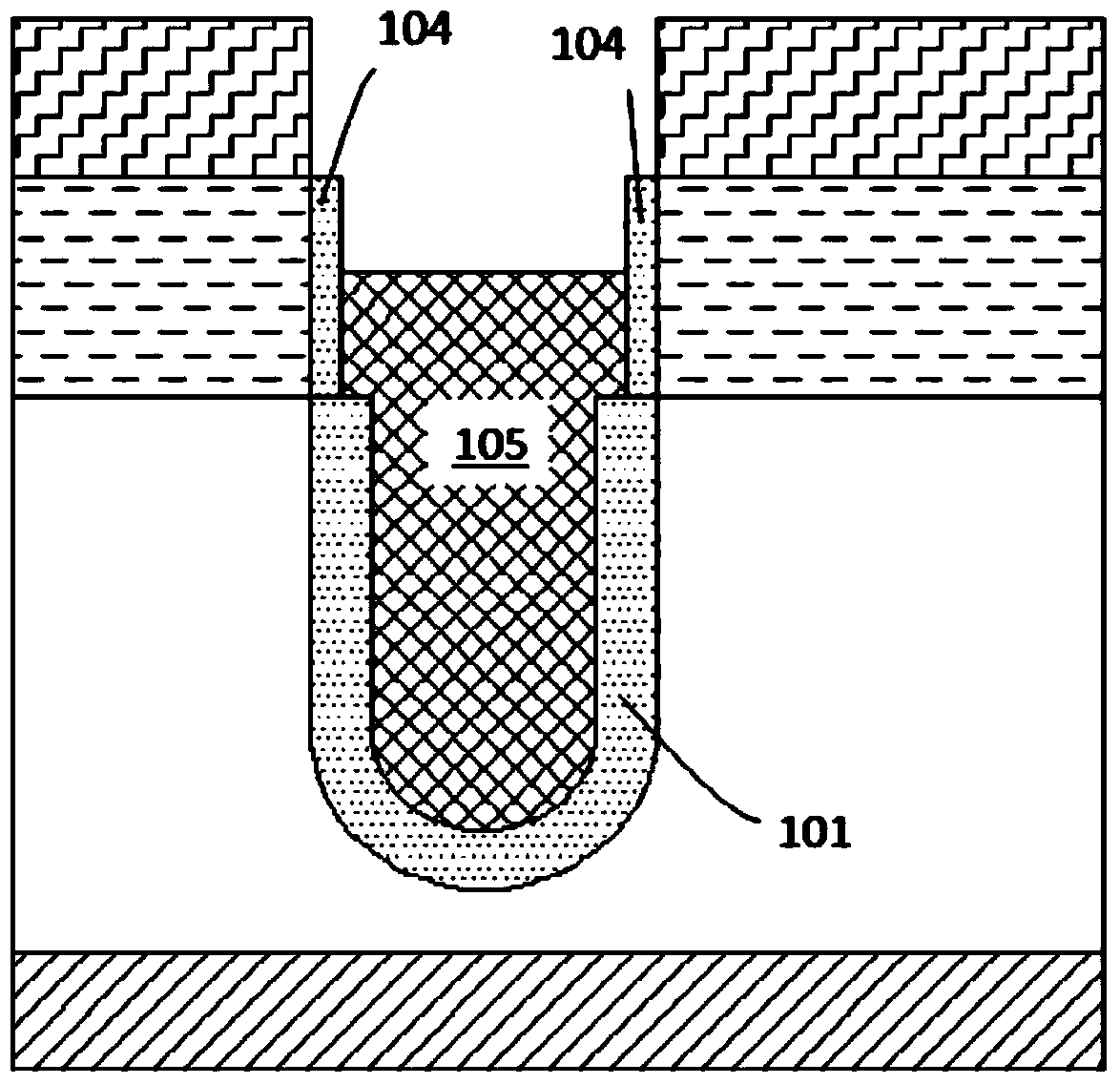

Embodiment Construction

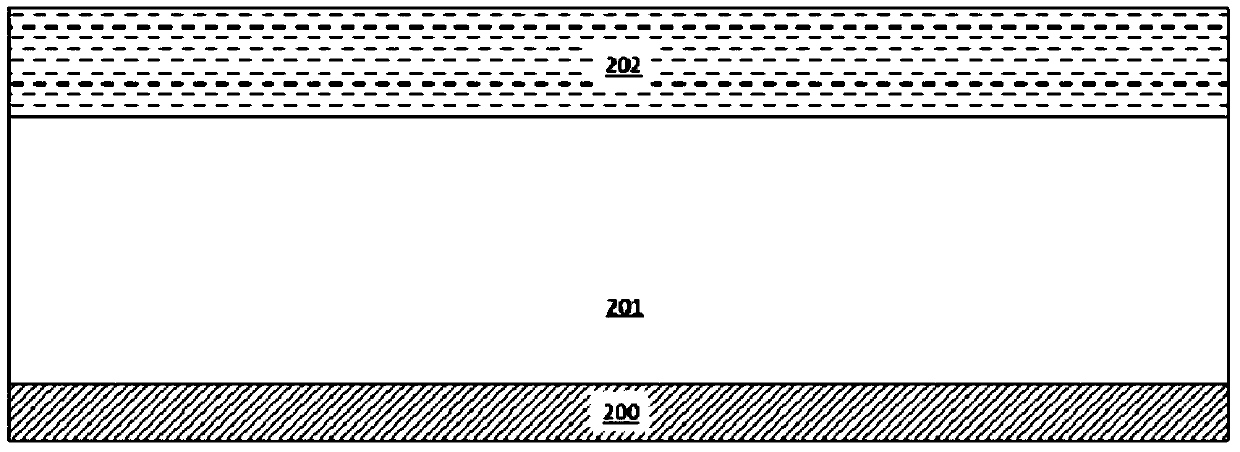

[0040] In order to clearly illustrate the specific implementation of the present invention, the figures listed in the accompanying drawings of the description enlarge the thickness of the layers and regions described in the present invention, and the size of the figures shown does not represent the actual size; the drawings are schematic , should not limit the scope of the present invention. The embodiments listed in the description should not be limited to the specific shapes of the regions shown in the drawings, but include the obtained shapes such as deviations caused by manufacturing, etc., and the curves obtained by etching usually have curved or rounded characteristics, but All are represented by rectangles in the embodiments of the present invention; meanwhile, in the following description, the term semiconductor substrate used can be understood to include the semiconductor wafer being processed and other thin film layers prepared thereon.

[0041] The specific implemen...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More