Patents

Literature

38results about How to "Wider process window" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

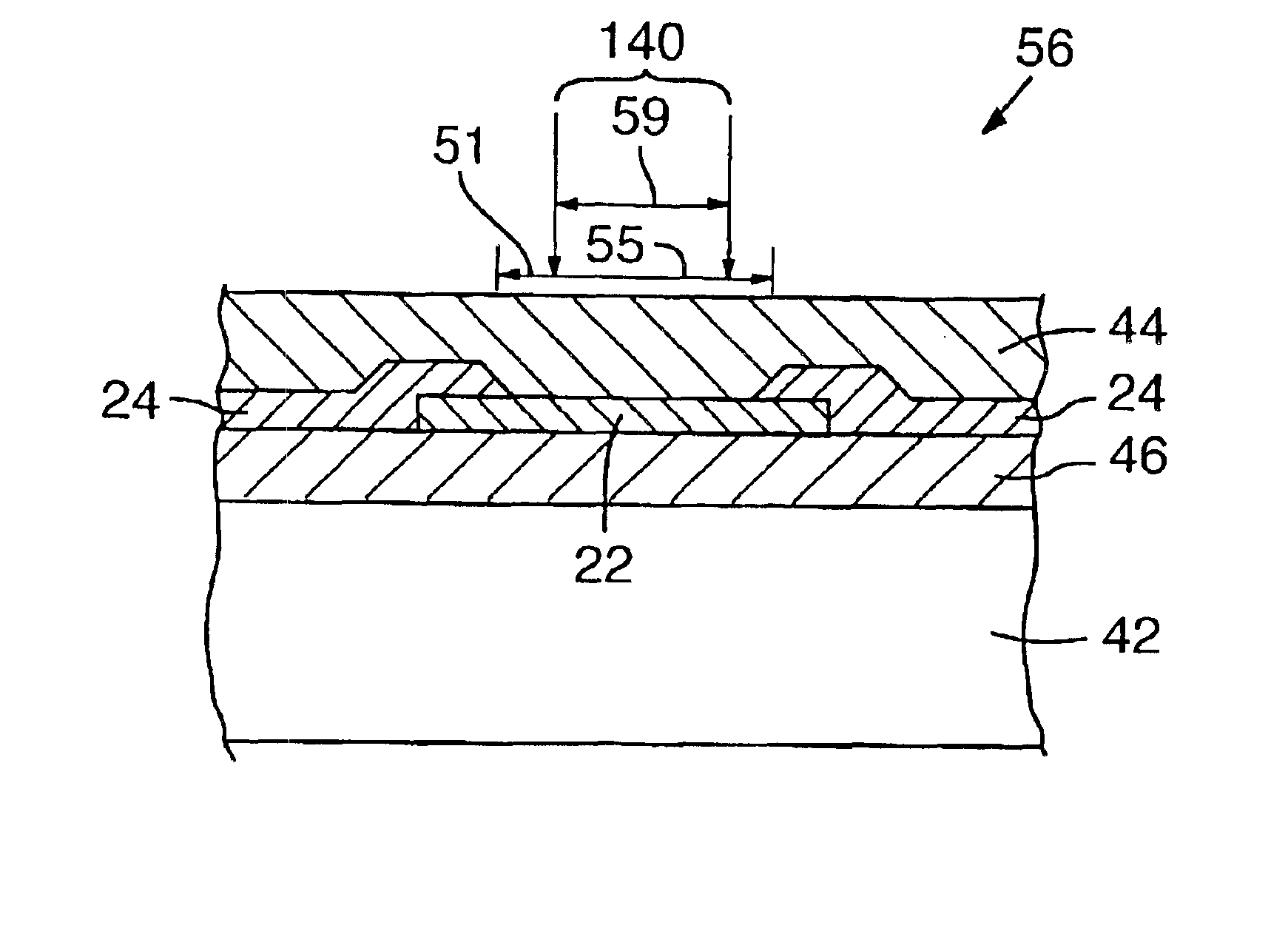

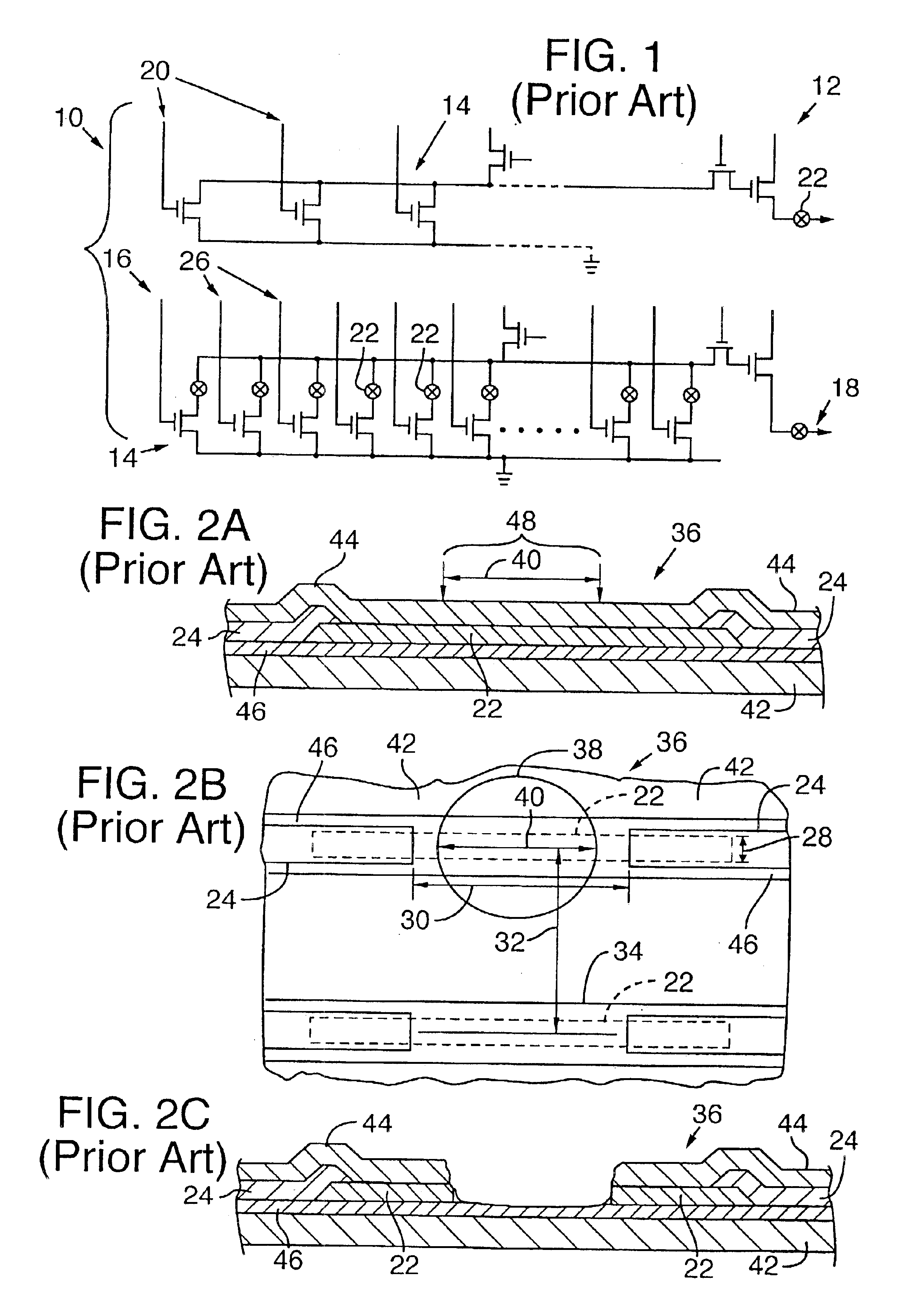

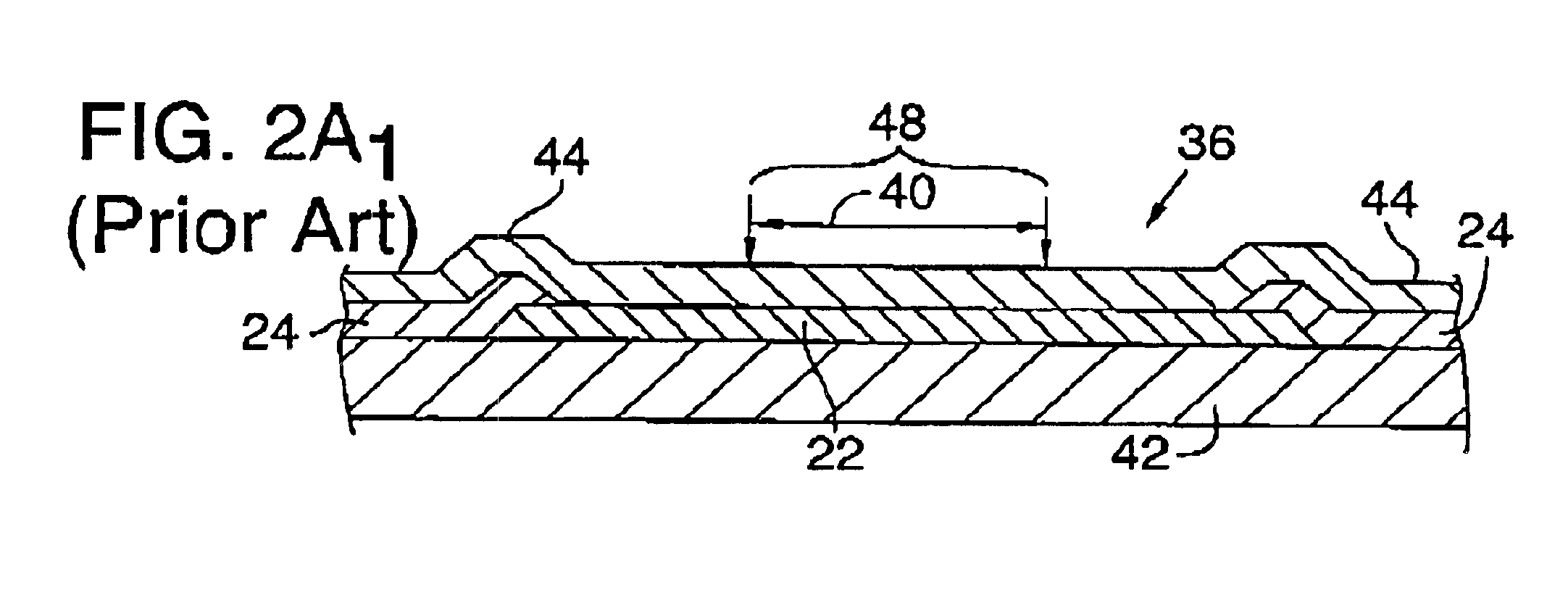

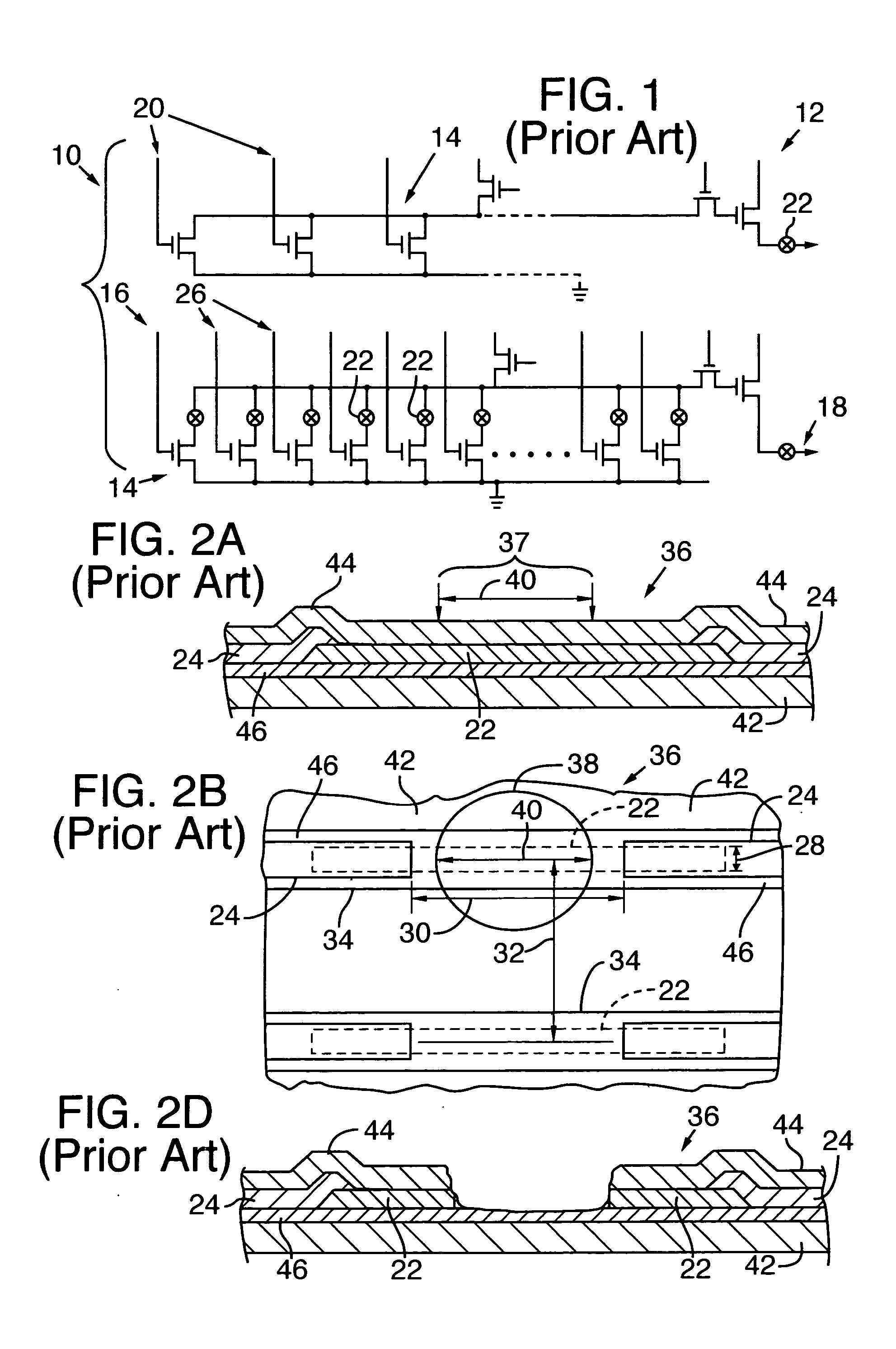

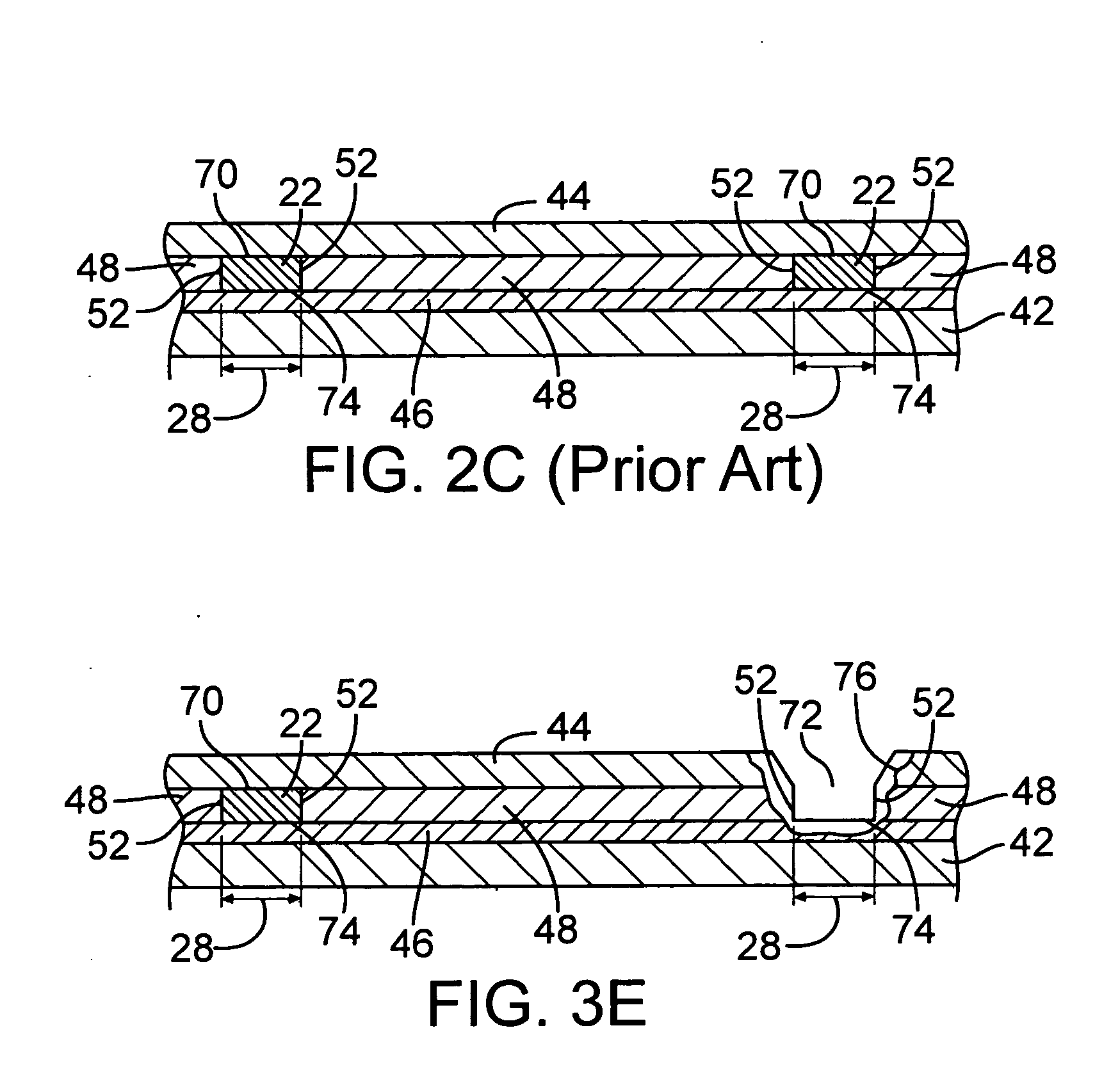

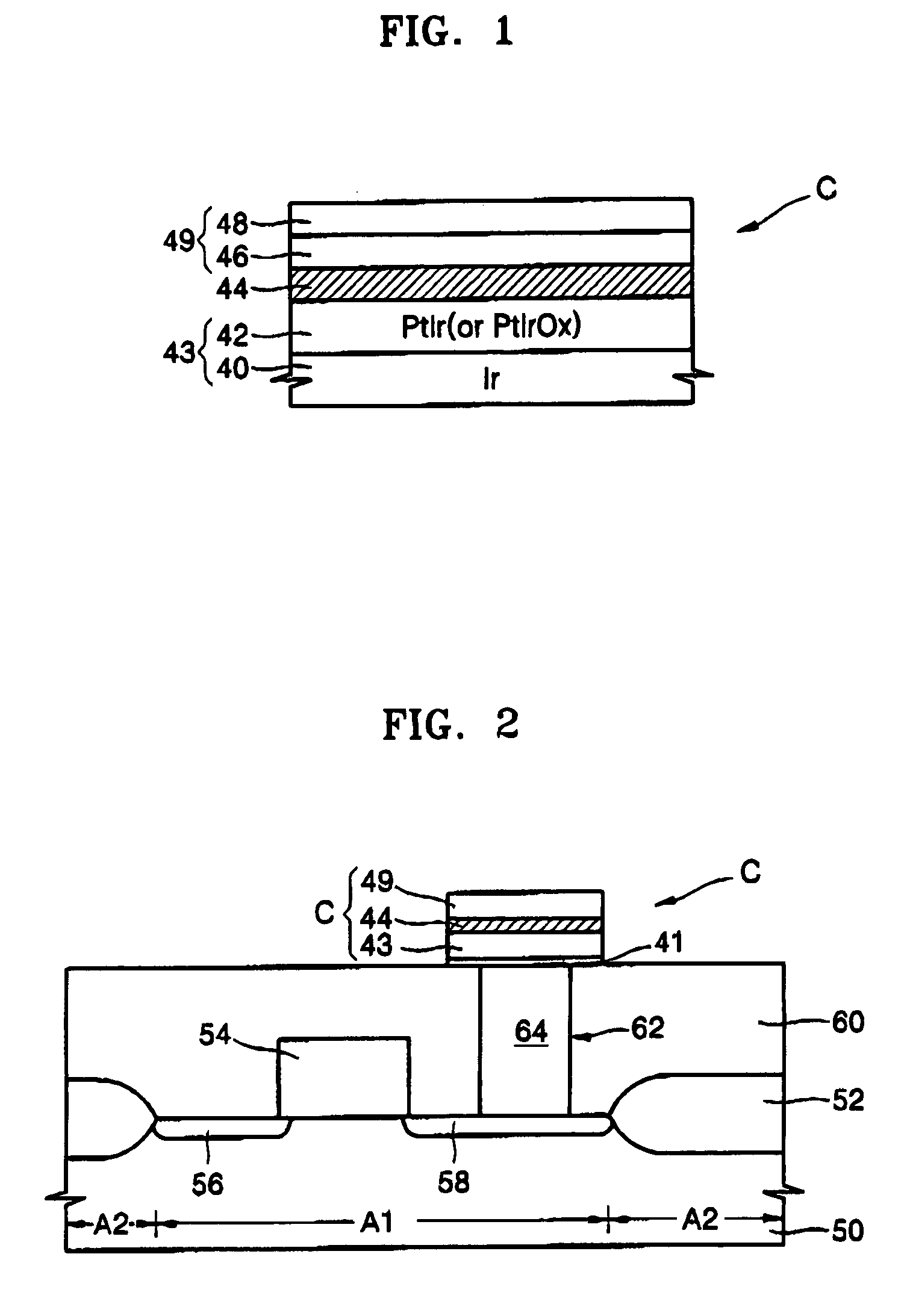

Passivation processing over a memory link

InactiveUS6887804B2Improve processing qualityAvoid and minimize substrate damage and undesirable damageSemiconductor/solid-state device detailsSolid-state devicesEtchingHarmonic

A set (50) of one or more laser pulses (52) is employed to remove passivation layer (44) over a conductive link (22). The link (22) can subsequently be removed by a different process such as chemical etching. The duration of the set (50) is preferably shorter than 1,000 ns; and the pulse width of each laser pulse (52) within the set (50) is preferably within a range of about 0.05 ps to 30 ns. The set (50) can be treated as a single “pulse” by conventional laser positioning systems (62) to perform on-the-fly material removal without stopping whenever the laser system (60) fires a set (50) of laser pulses (52) at each target area (51). Conventional wavelengths in the IR range or their harmonics in the green or UV range can be employed.

Owner:ELECTRO SCI IND INC

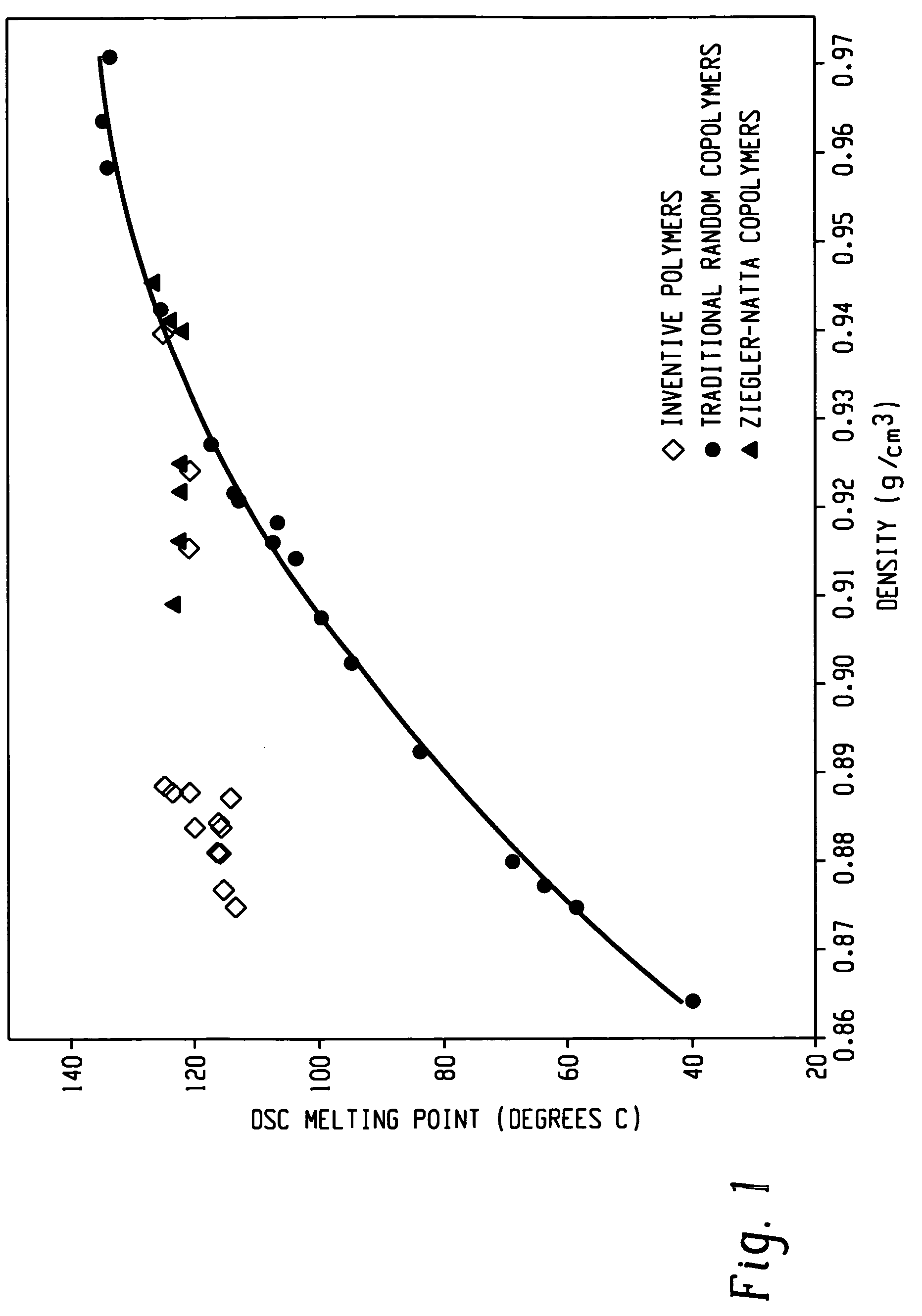

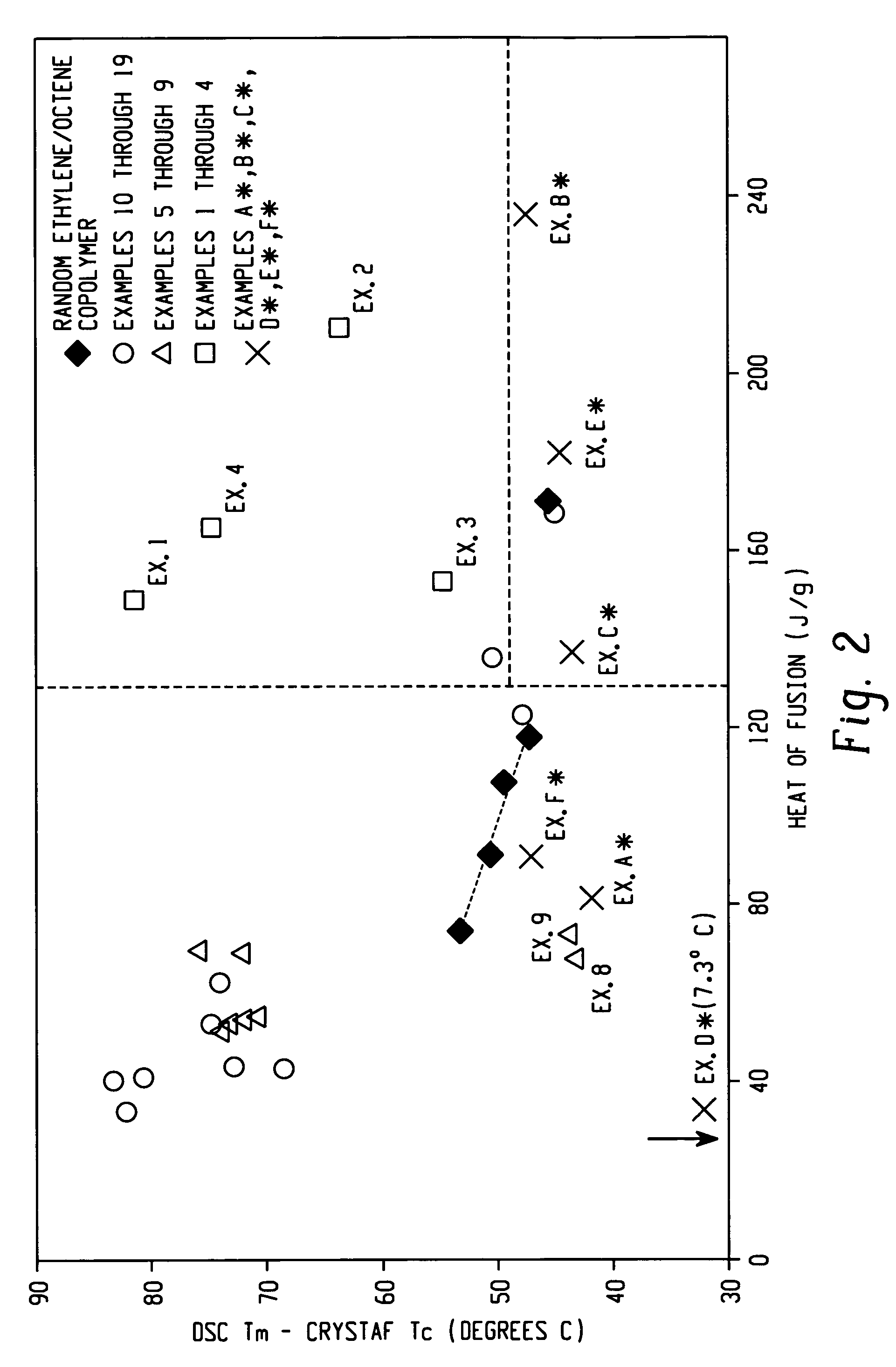

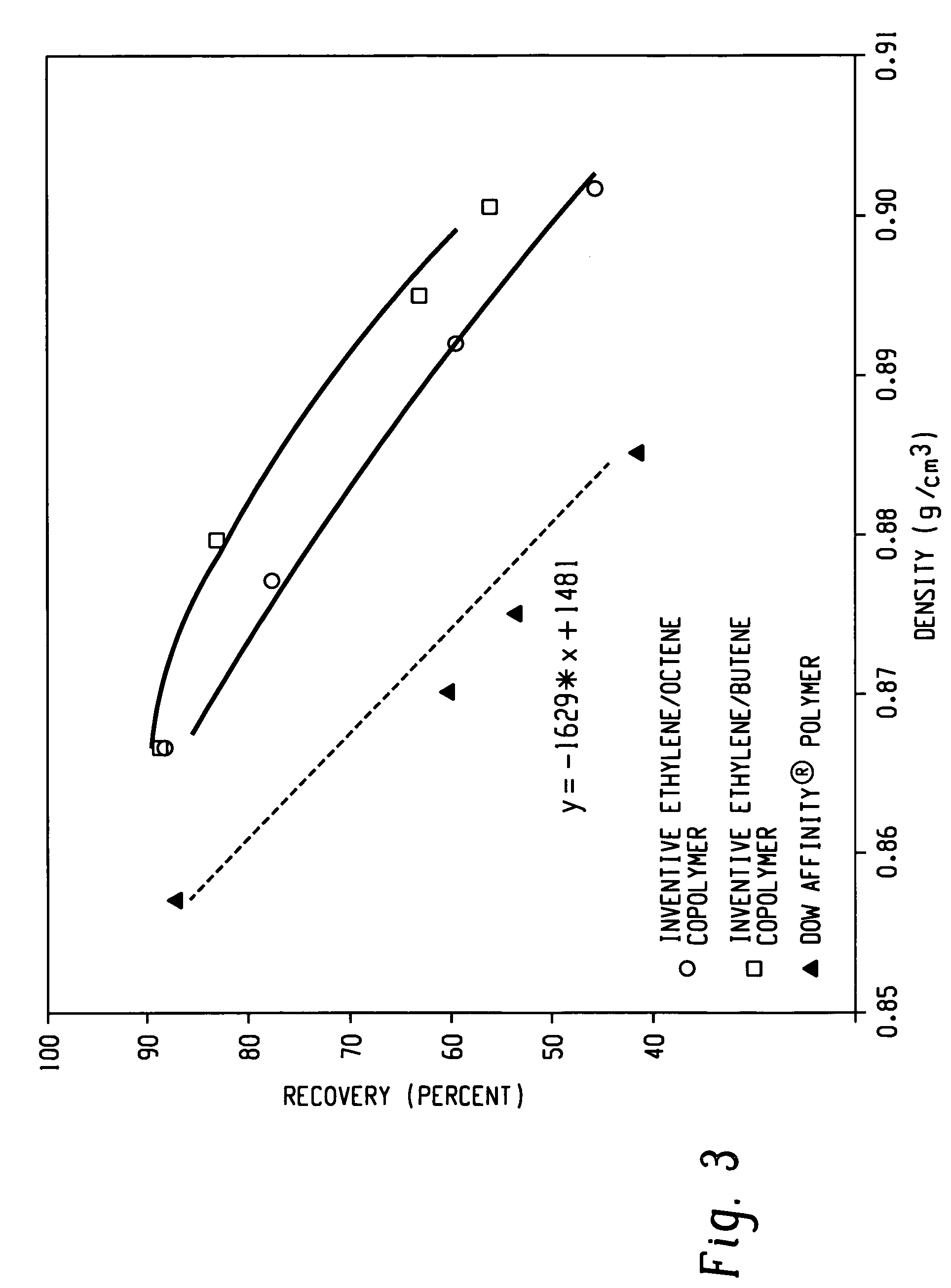

Compositions of ethylene/alpha-olefin multi-block interpolymer for blown films with high hot tack

InactiveUS7582716B2Less energyLess timeSynthetic resin layered productsBagsCelsius DegreeAlpha-olefin

The present invention relates to film layers and compositions having improved hot tack properties. The compositions comprise at least one ethylene / α-olefin interpolymer, wherein the ethylene / α-olefin interpolymer may have, for example, a Mw / Mn from about 1.7 to about 3.5, at least one melting point, Tm, in degrees Celsius, and a density, d, in grams / cubic centimeter, wherein the numerical values of Tm and d correspond to the relationship:Tm>−2002.9+4538.5(d)−2422.2(d)2.

Owner:DOW GLOBAL TECH LLC

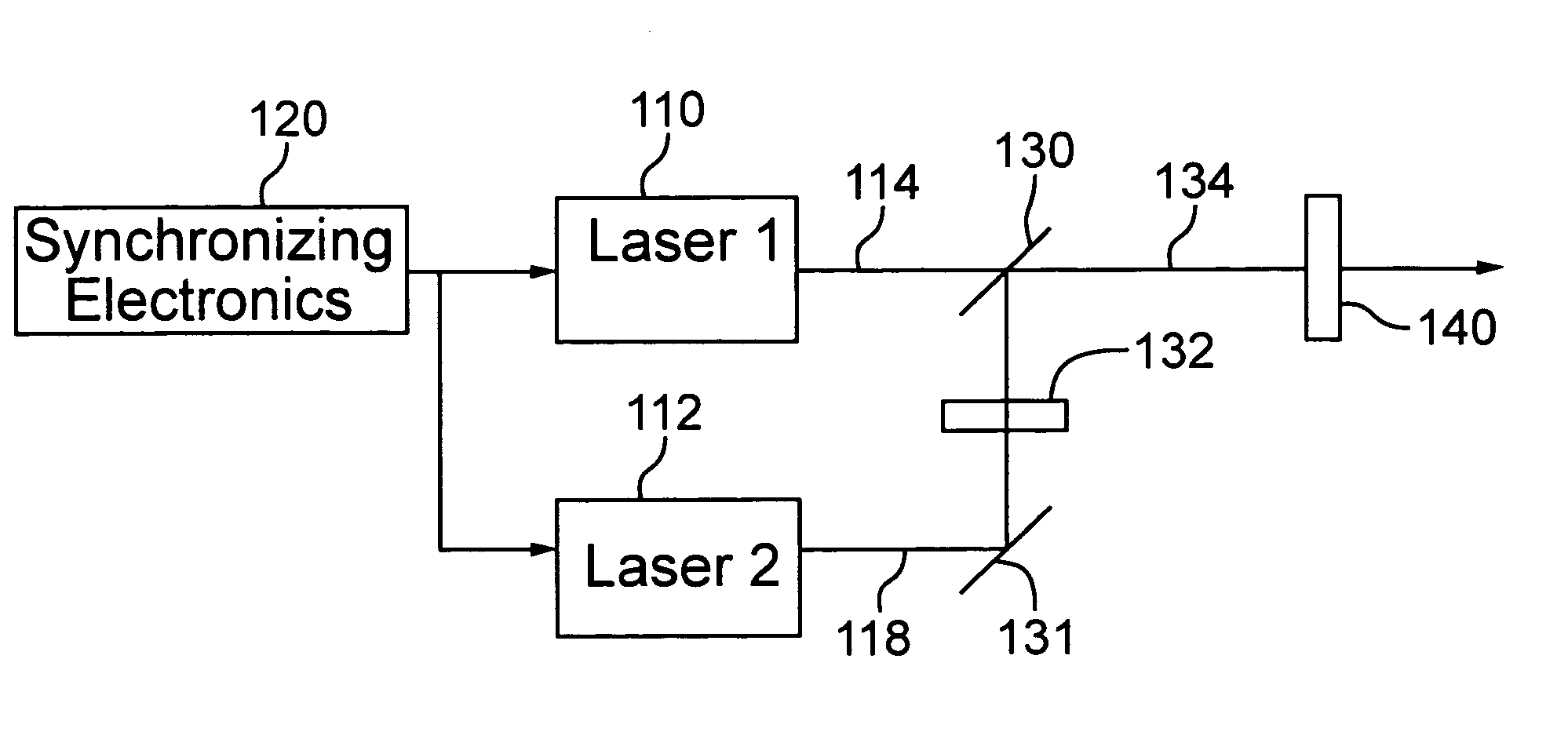

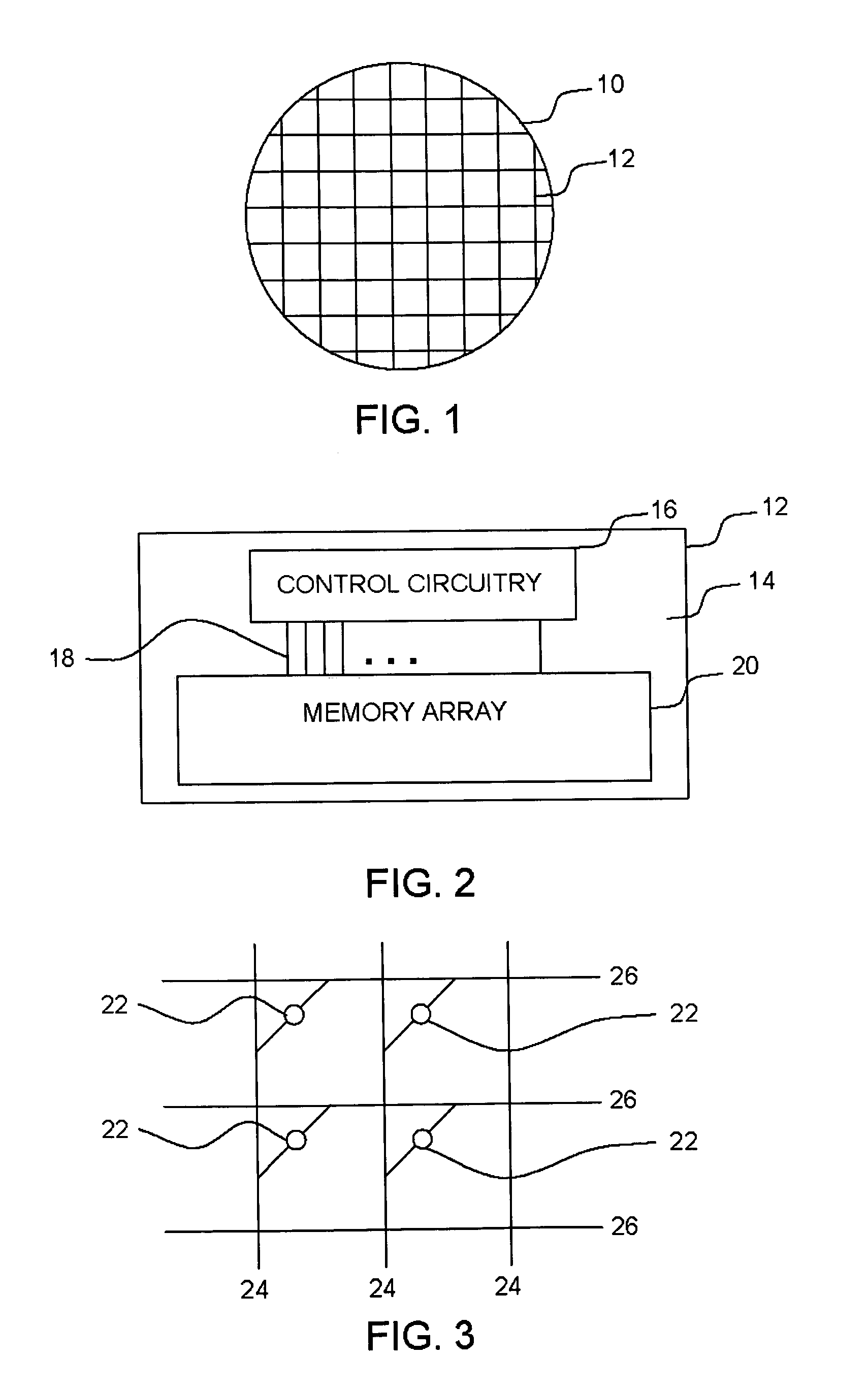

Methods of and laser systems for link processing using laser pulses with specially tailored power profiles

ActiveUS20050067388A1Improve removal qualityImprove processing qualityLaser detailsSemiconductor/solid-state device detailsPulse energyUltraviolet

Owner:ELECTRO SCI IND INC

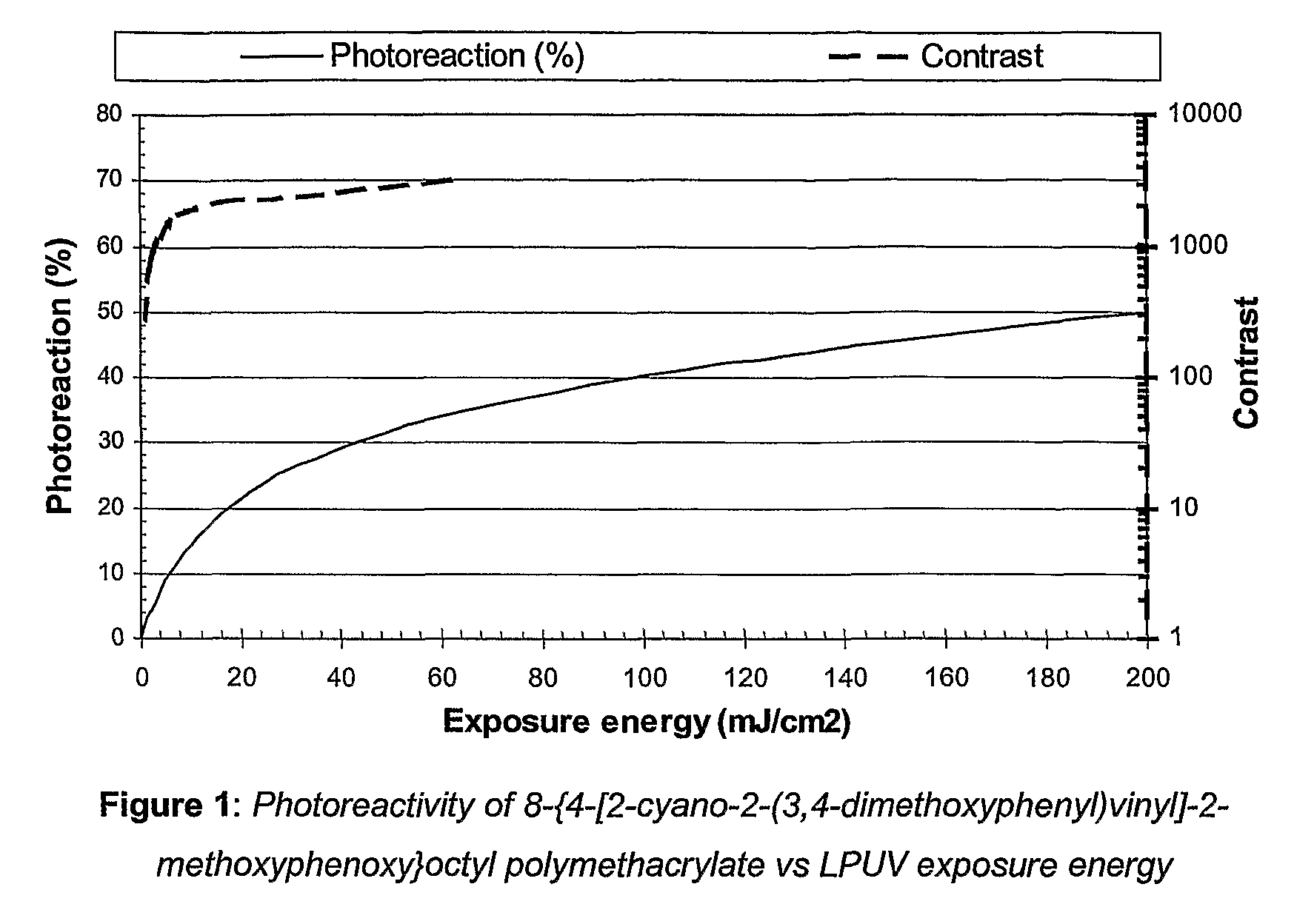

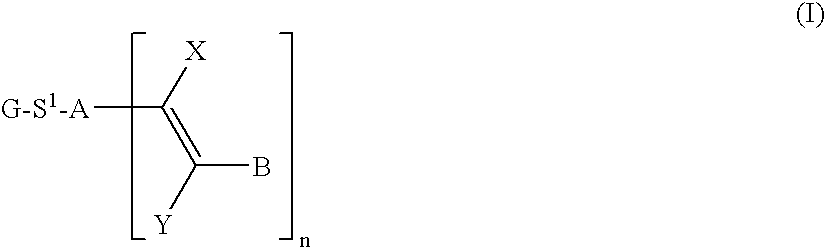

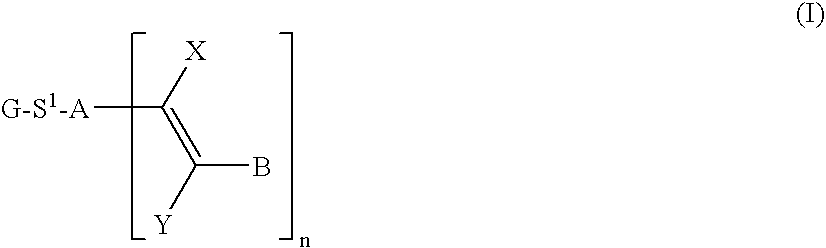

Functionalized photoreactive compounds

ActiveUS7959990B2Increase photosensitivityWider process windowLiquid crystal compositionsThin material handlingUltimate tensile strengthElectron

The present invention concerns functionalized photoreactive compounds of formula (I), that are particularly useful in materials for the alignment of liquid crystals. Due to the adjunction of an electron withdrawing group to specific molecular systems bearing an unsaturation directly attached to two unsaturated ring systems, exceptionally high photosensitivities, excellent alignment properties as well as good mechanical robustness could be achieved in materials comprising said functionalized photoreactive compounds of the invention.

Owner:ROLIC AG

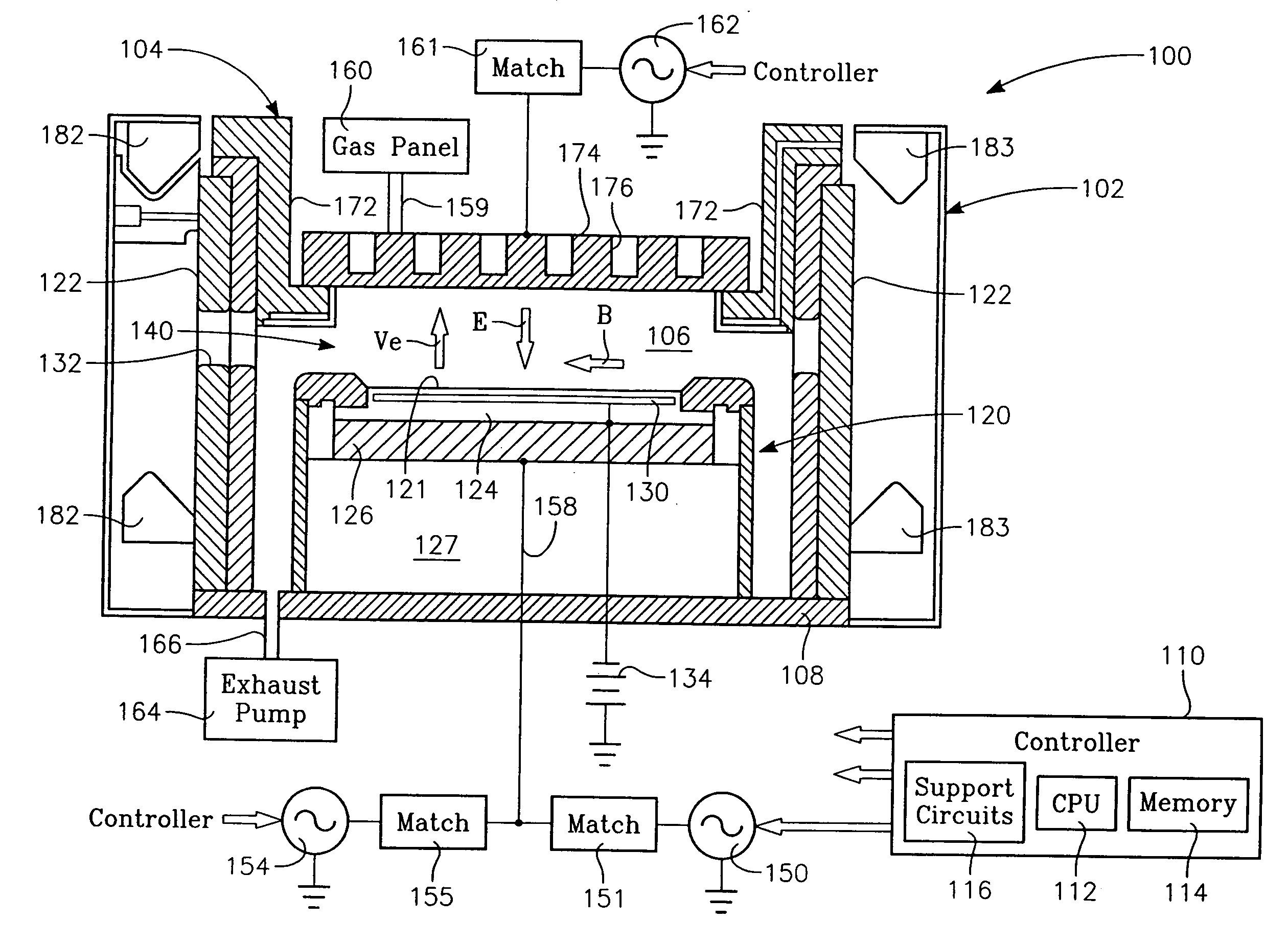

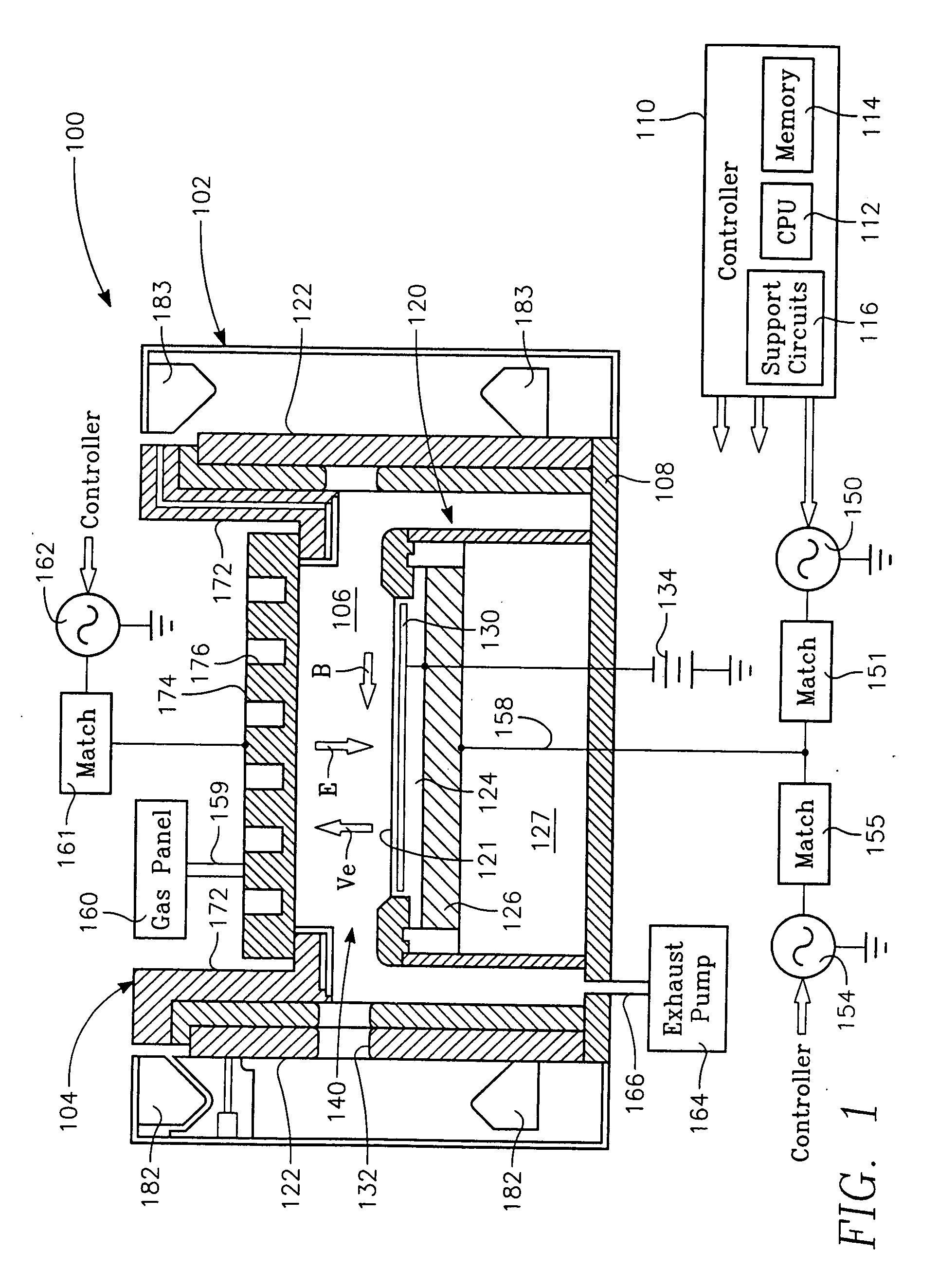

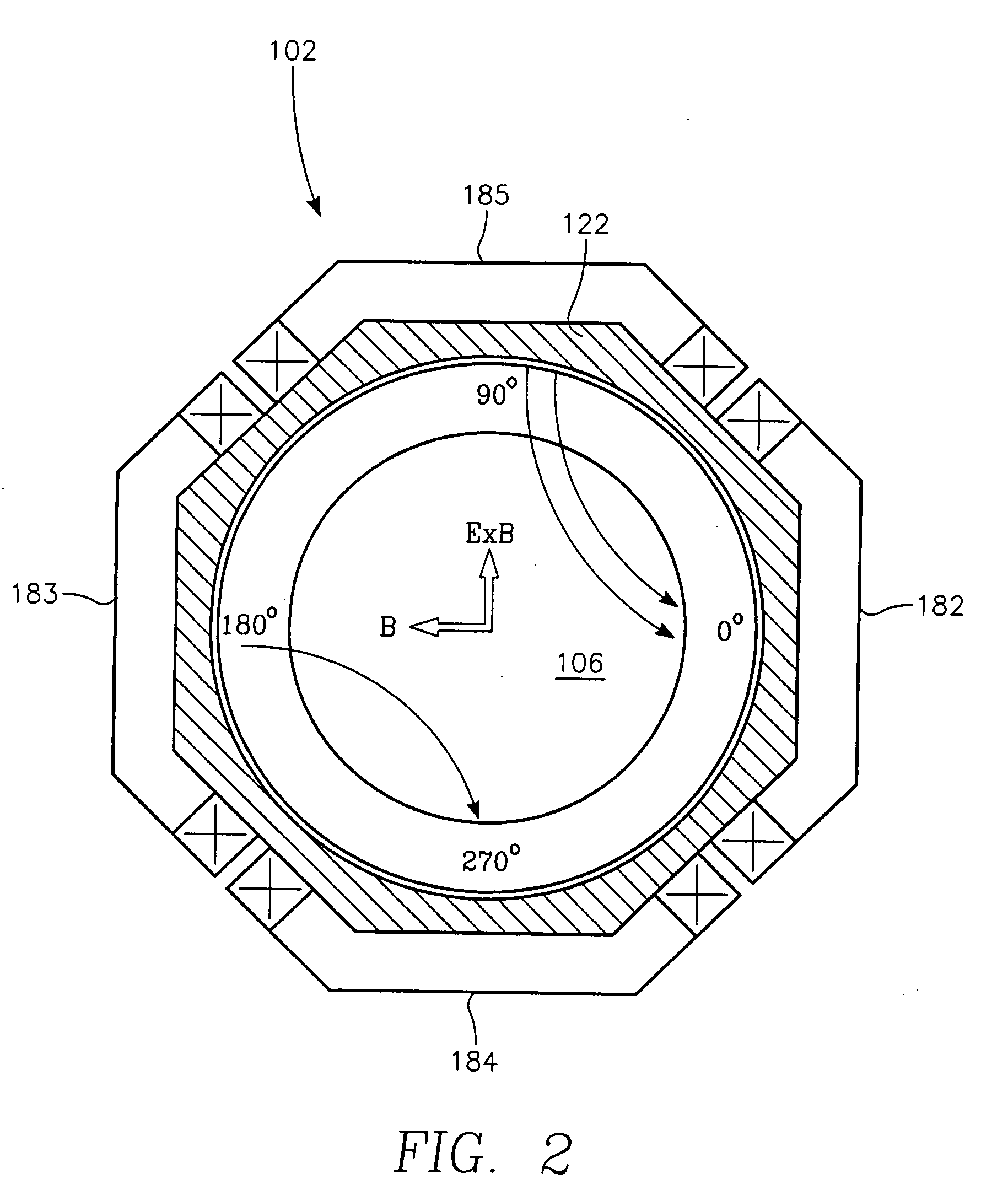

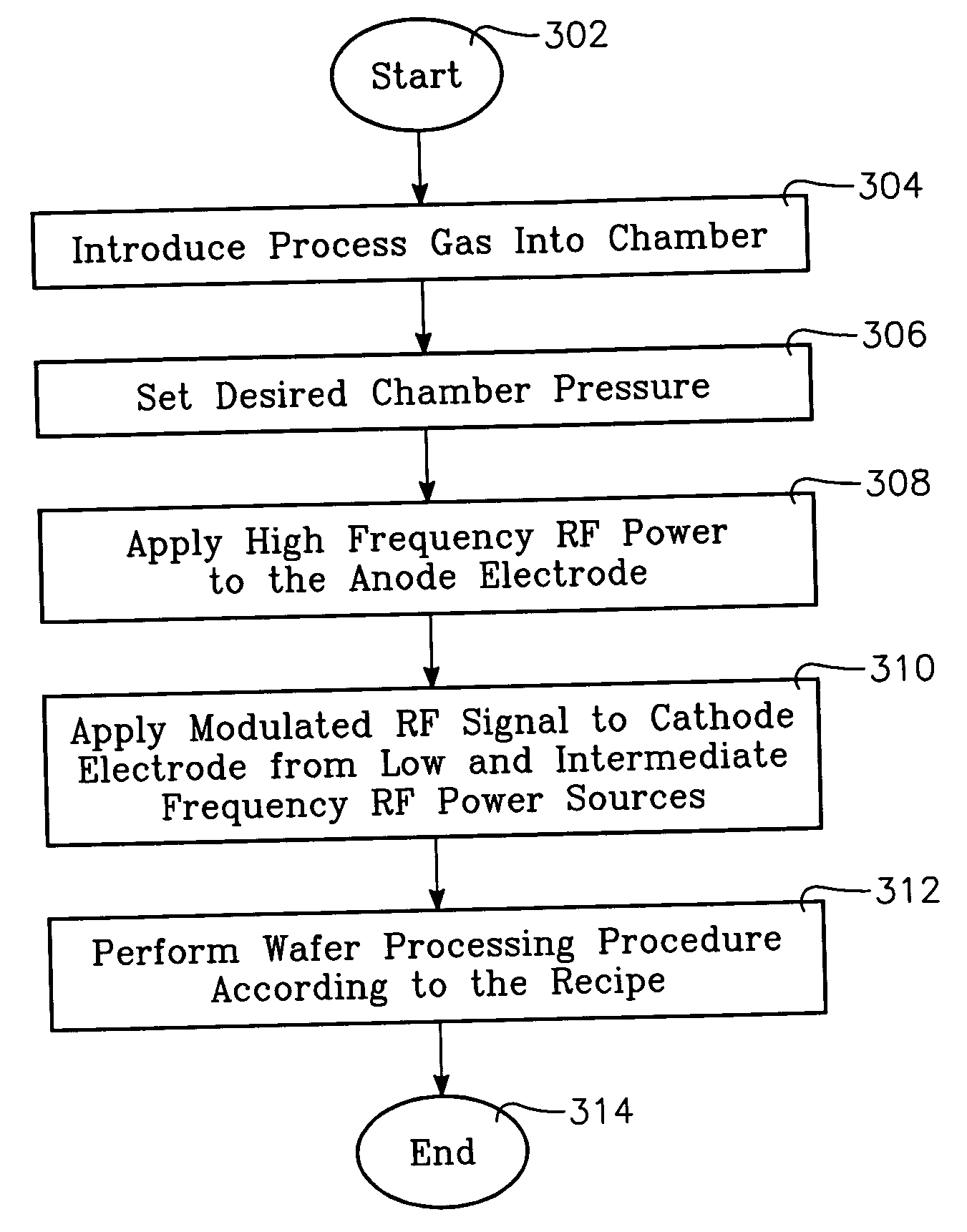

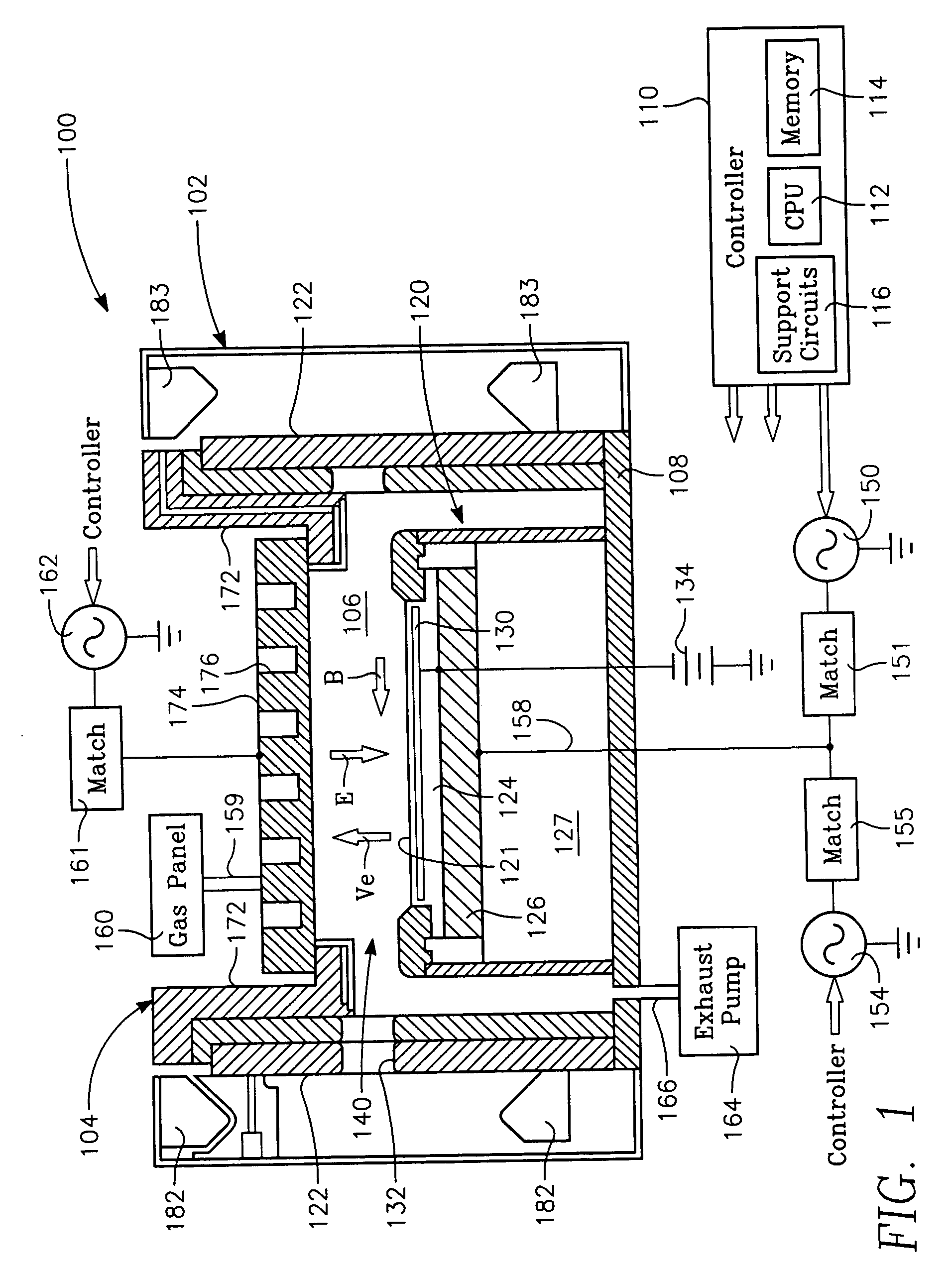

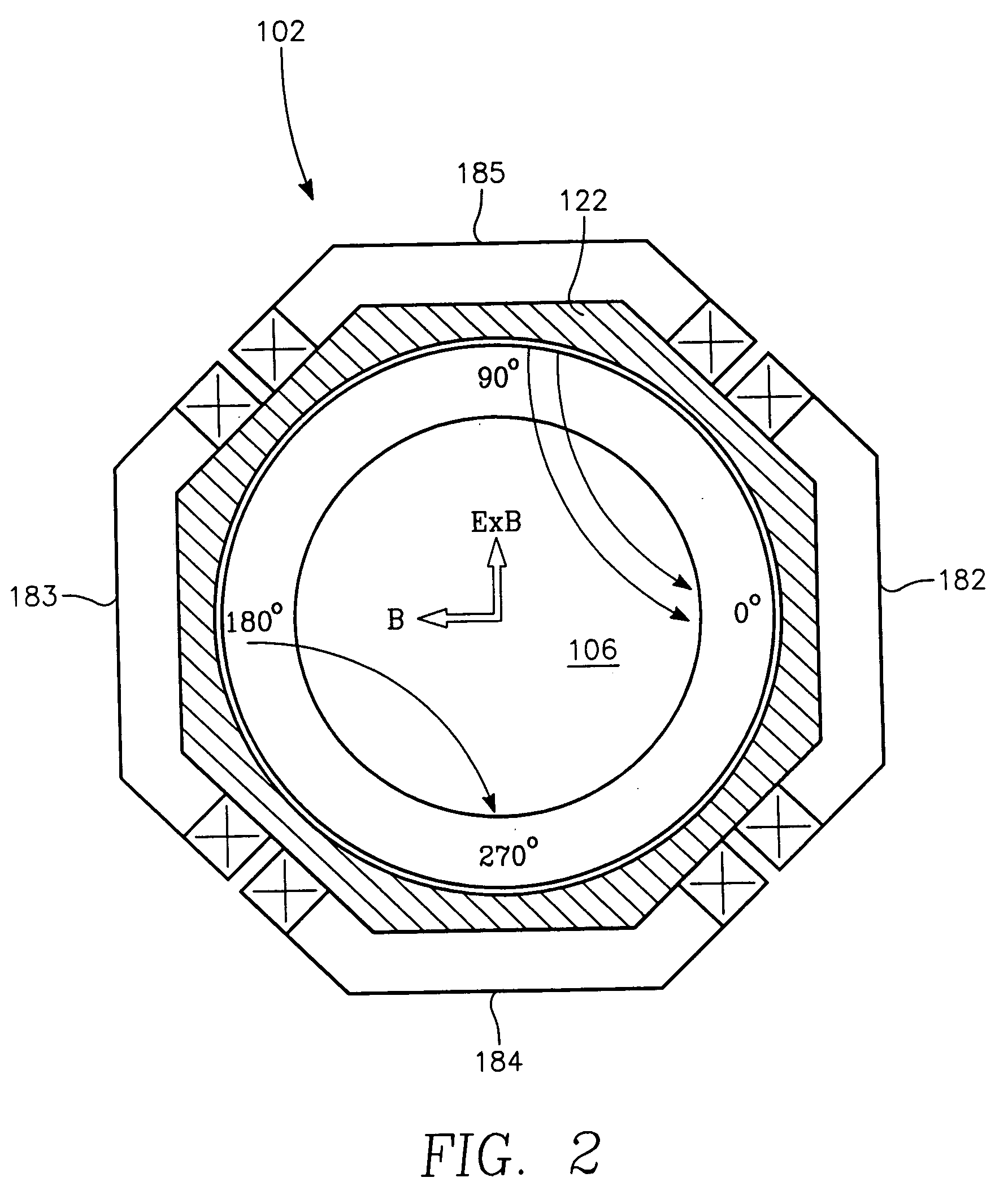

Etch chamber with dual frequency biasing sources and a single frequency plasma generating source

InactiveUS20060175015A1Increased process windowExpand coverageElectric discharge tubesDecorative surface effectsDual frequencyHigh frequency power

A method and apparatus for selectively controlling a plasma in a processing chamber during wafer processing. The method includes providing process gasses into the chamber over a wafer to be processed, and providing high frequency RF power to a plasma generating element and igniting the process gases into the plasma. Modulated RF power is coupled to a biasing element, and wafer processing is performed according to a particular processing recipe. The apparatus includes a biasing element disposed in the chamber and adapted to support a wafer, and a plasma generating element disposed over the biasing element and wafer. A first power source is coupled to the plasma generating element, and a second power source is coupled to the biasing element. A third power source is coupled to the biasing element, wherein the second and third power sources provide a modulated signal to the biasing element.

Owner:APPLIED MATERIALS INC

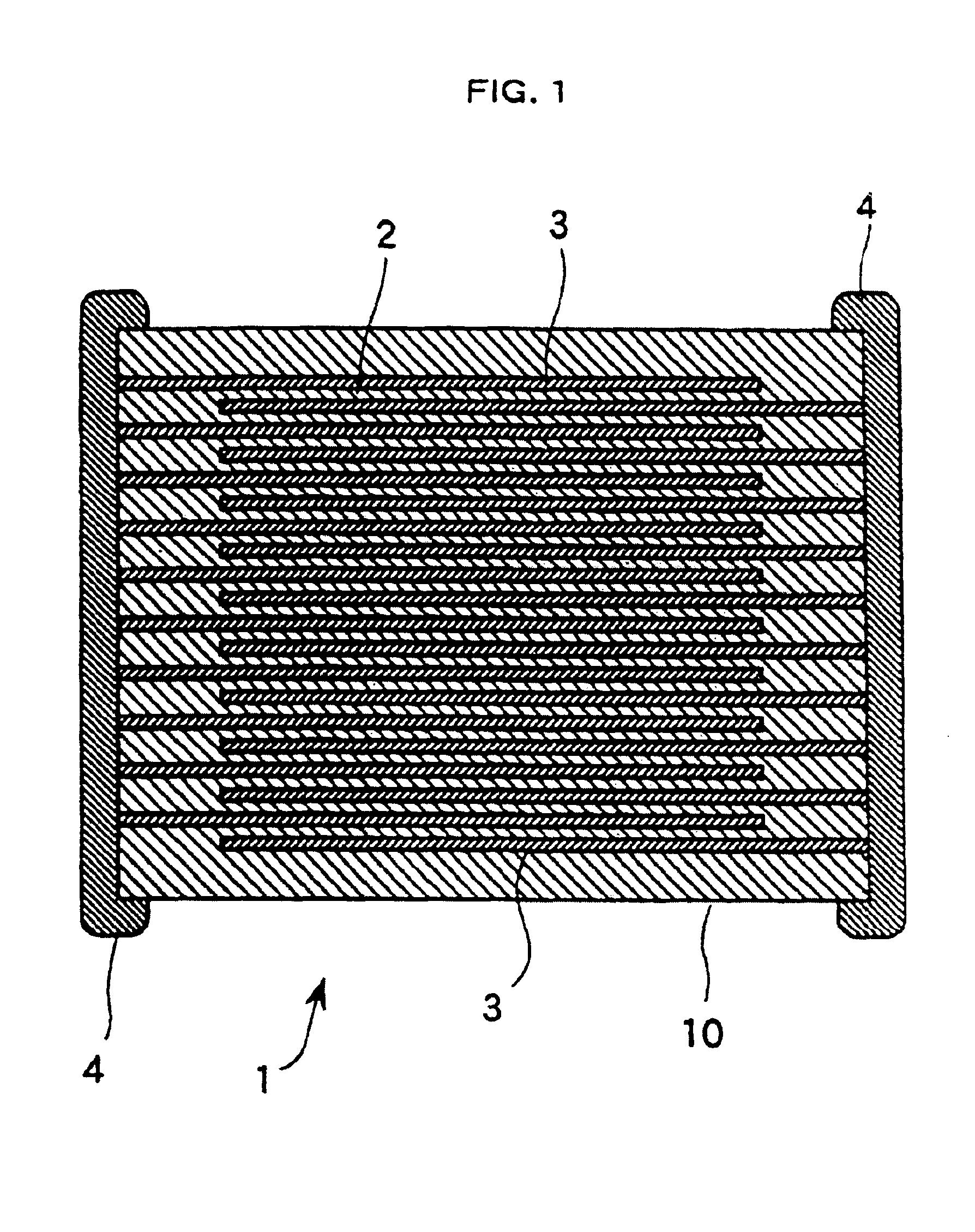

Copper termination inks containing lead free and cadmium free glasses for capacitors

ActiveUS6982864B1Improve adhesionGood chemical resistanceFixed capacitor dielectricFixed capacitor terminalsCopperCadmium Cation

Lead-free and cadmium-free glass composition that is particularly suitable for use in conductive ink applications. The invention includes a capacitor comprising a copper termination, the copper termination is made by firing an ink including a glass component, the glass component may comprise up to about 65 mole % ZnO, up to about 51 mole % SrO, about 0.1 to about 61 mole % B2O3, up to about 17 mole % Al2O3, about 0.1 to about 63 mole % Sio2, up to about 40 mole % BaO+CaO, and up to about 20 mole % MgO.

Owner:FERRO CORP

Etch chamber with dual frequency biasing sources and a single frequency plasma generating source

InactiveUS20070020937A1Increased process windowExpand coverageElectric discharge tubesSemiconductor/solid-state device manufacturingDual frequencyHigh frequency power

A method and apparatus for selectively controlling a plasma in a processing chamber during wafer processing. The method includes providing process gasses into the chamber over a wafer to be processed, and providing high frequency RF power to a plasma generating element and igniting the process gases into the plasma. Modulated RF power is coupled to a biasing element, and wafer processing is performed according to a particular processing recipe. The apparatus includes a biasing element disposed in the chamber and adapted to support a wafer, and a plasma generating element disposed over the biasing element and wafer. A first power source is coupled to the plasma generating element, and a second power source is coupled to the biasing element. A third power source is coupled to the biasing element, wherein the second and third power sources provide a modulated signal to the biasing element.

Owner:CHEN JIN YUAN +2

Functionalized Photoreactive Compounds

ActiveUS20080274304A1Increase photosensitivityWider process windowLiquid crystal compositionsOrganic chemistryUltimate tensile strengthElectron

The present invention concerns functionalized photoreactive compounds of formula (I), that are particularly useful in materials for the alignment of liquid crystals. Due to the adjunction of an electron withdrawing group to specific molecular systems bearing an unsaturation directly attached to two unsaturated ring systems, exceptionally high photosensitivities, excellent alignment properties as well as good mechanical robustness could be achieved in materials comprising said functionalized photoreactive compounds of the invention.

Owner:ROLIC AG

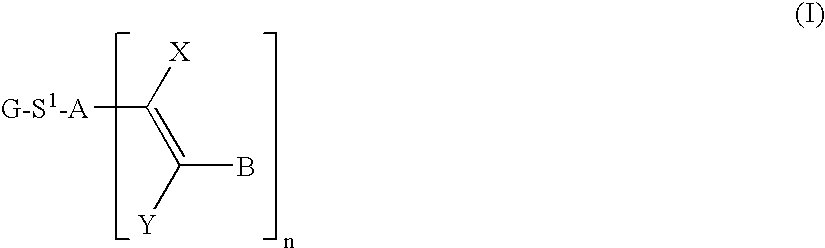

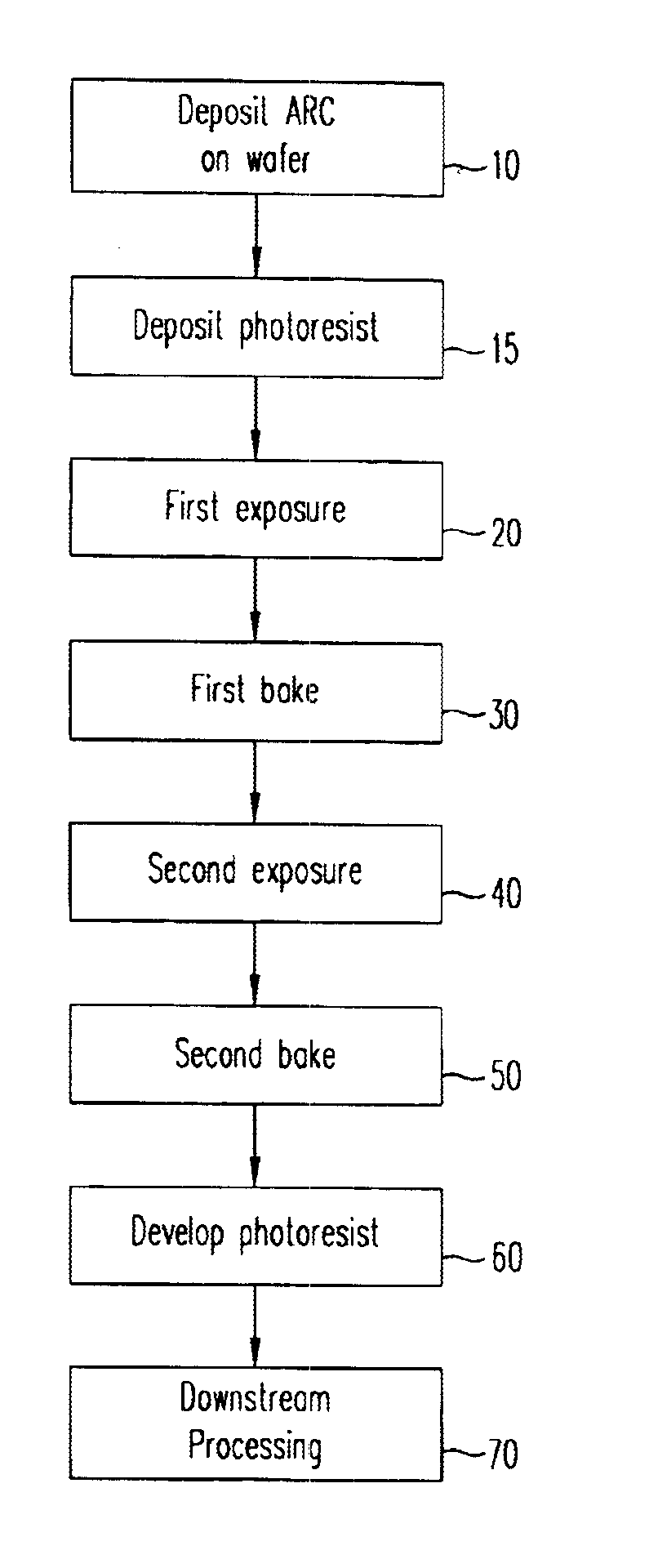

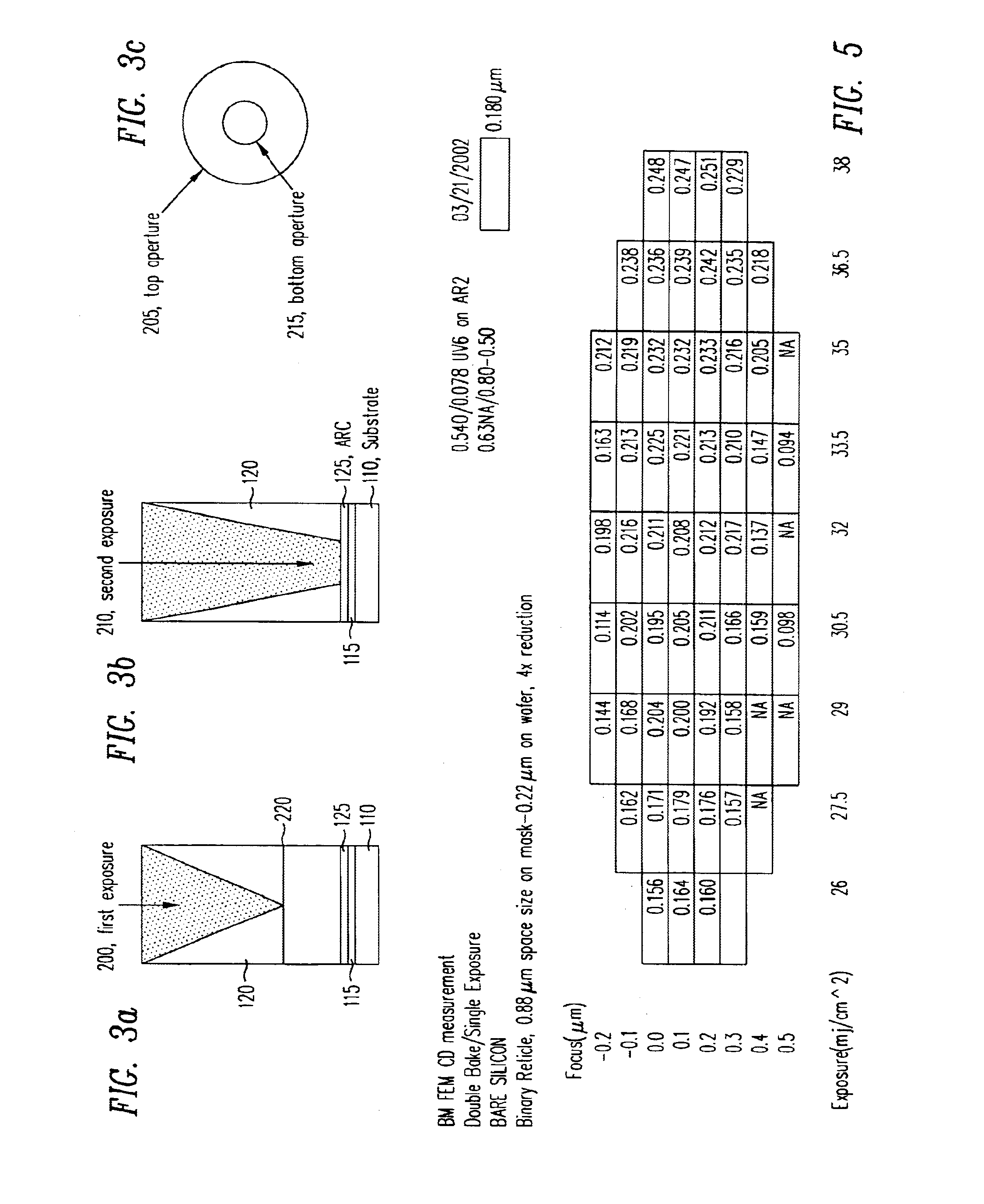

Photolithography method including a double exposure/double bake

InactiveUS6881524B2Little variabilityWider process windowPhotomechanical exposure apparatusMicrolithography exposure apparatusCooking & bakingResist

A photoresist exposure process is disclosed which produces features which are substantially smaller than the aperture dimension of the mask used to make the feature. The smaller feature size results from a double exposure of the photoresist, combined with a double baking process to create the features in the photoresist. The double baking process thins the layer of photoresist, prior to the second exposure, thereby improving the resolution of the mark created by the second exposure on the photoresist. The process also uses a binary bias mask through which the first exposure is made, which overlaps with the area of the second exposure, to allow a process tolerance for the realignment of the mask over the wafer for the second exposure.

Owner:PROMOS TECH INC

Copper termination inks containing lead free and cadmium free glasses for capacitors

ActiveUS7339780B2Improve adhesionGood chemical resistanceElectrolytic capacitorsFixed capacitor dielectricCopperCadmium Cation

A reduction resistant lead-free and cadmium-free glass composition that is particularly suitable for use in conductive ink applications is disclosed. The invention includes a capacitor, which includes a conductive copper termination. The copper termination is made by firing an ink including a glass component, which may include ZnO, provided the amount does not exceed about 65 mole %; B2O3, provided the amount does not exceed about 61 mole %; and, SiO2, provided the amount does not exceed about 63 mole %. The molar ratio of B2O3 to SiO2 is from about 0.05 to about 3.

Owner:FERRO CORP

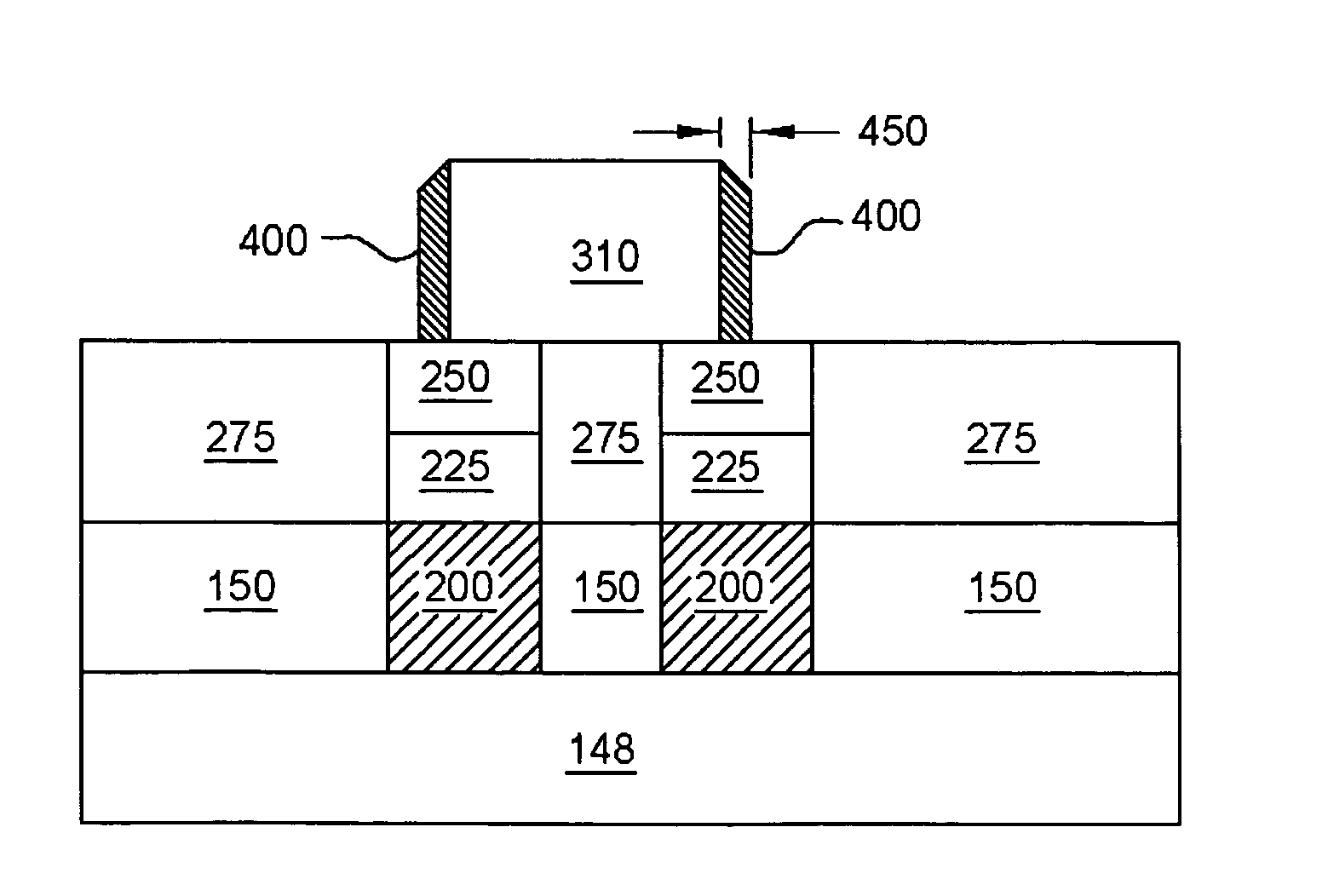

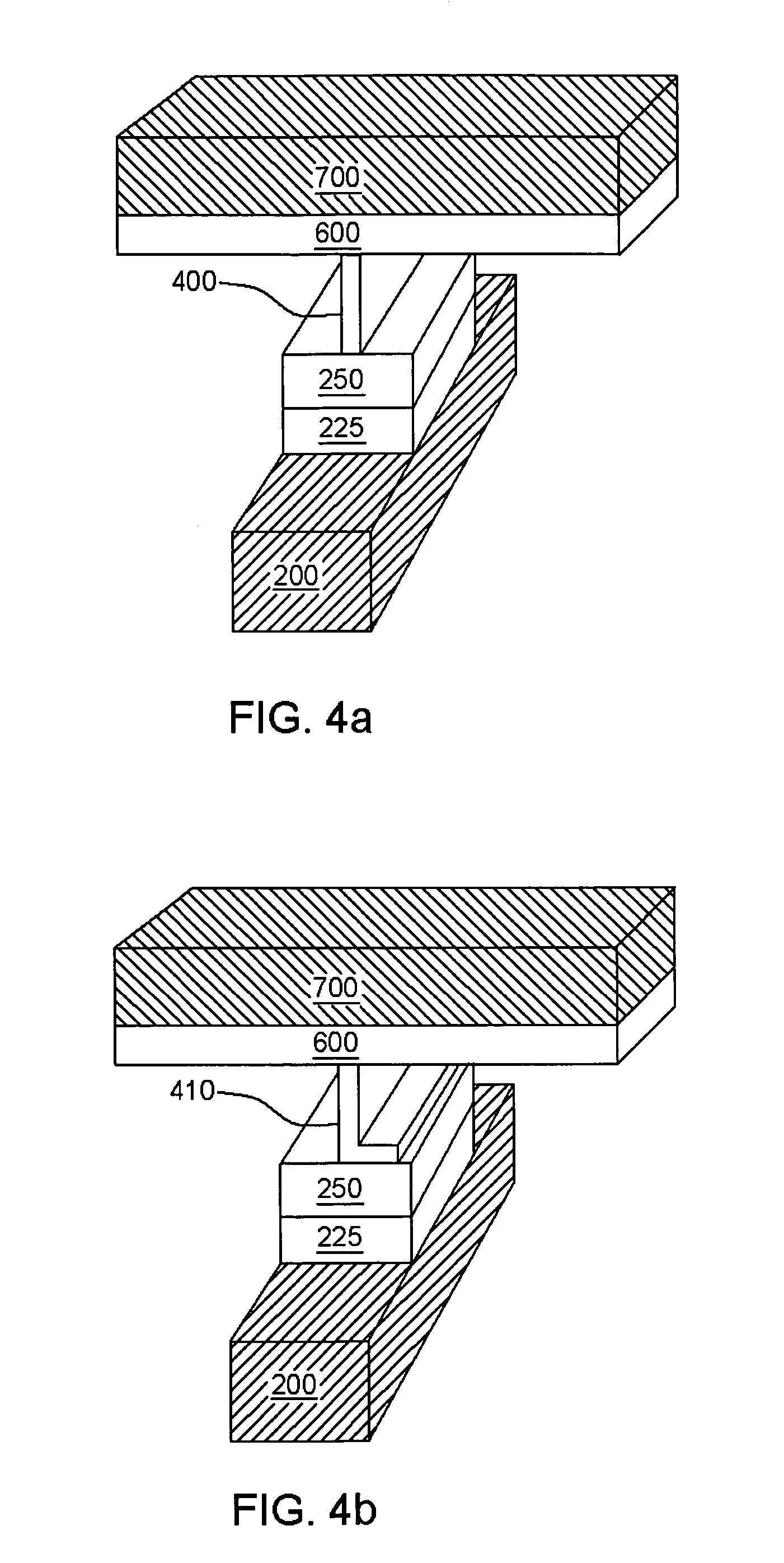

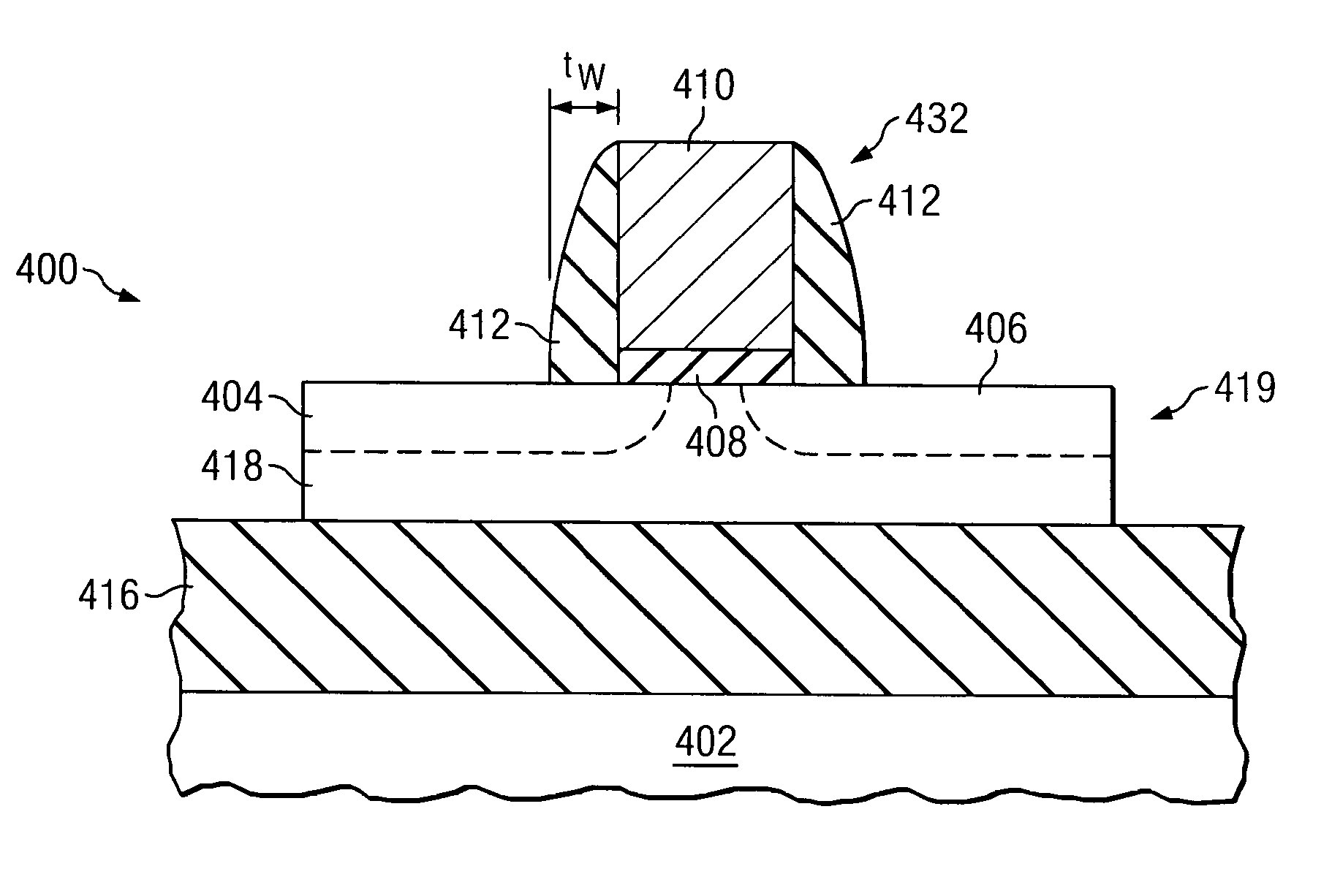

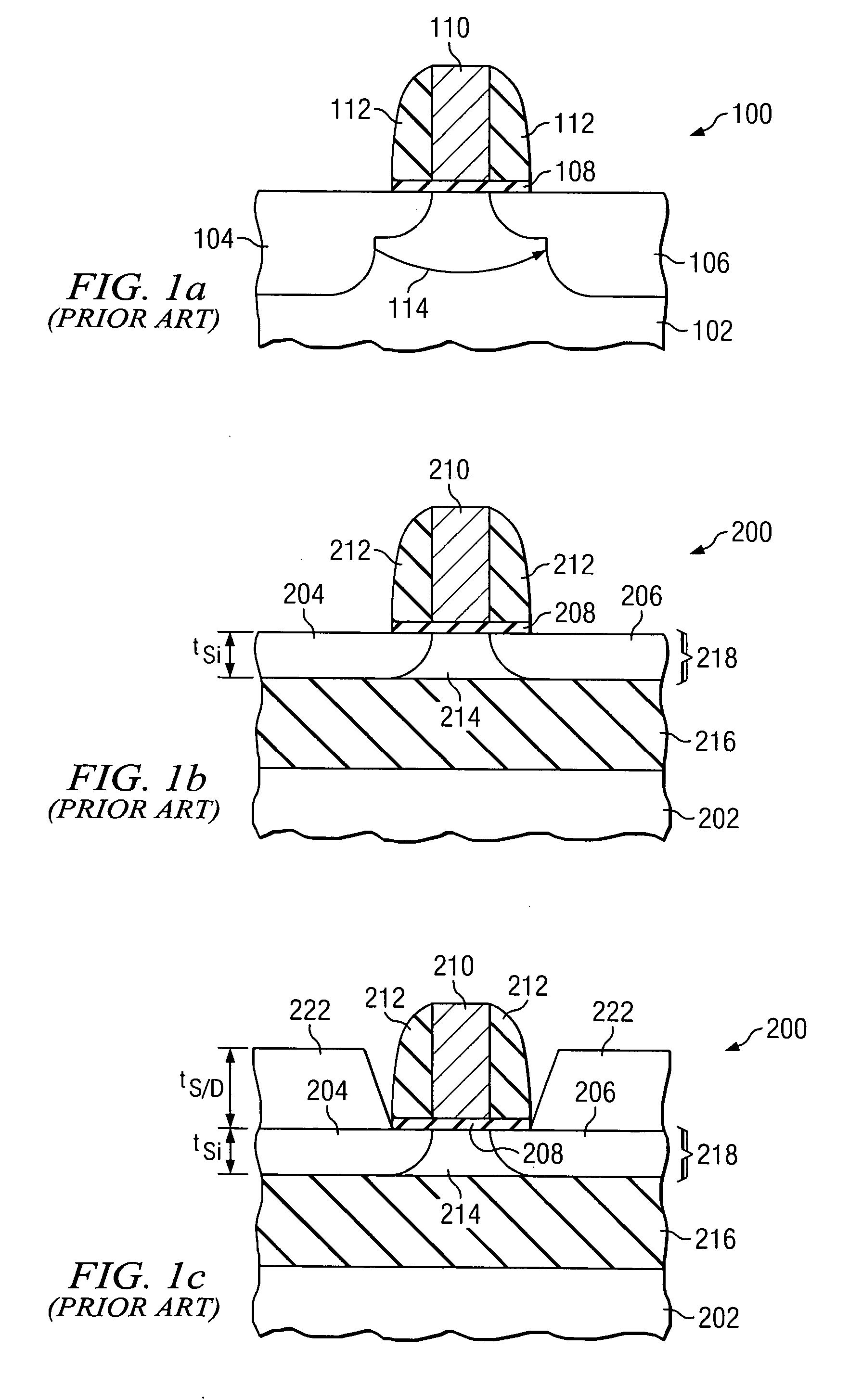

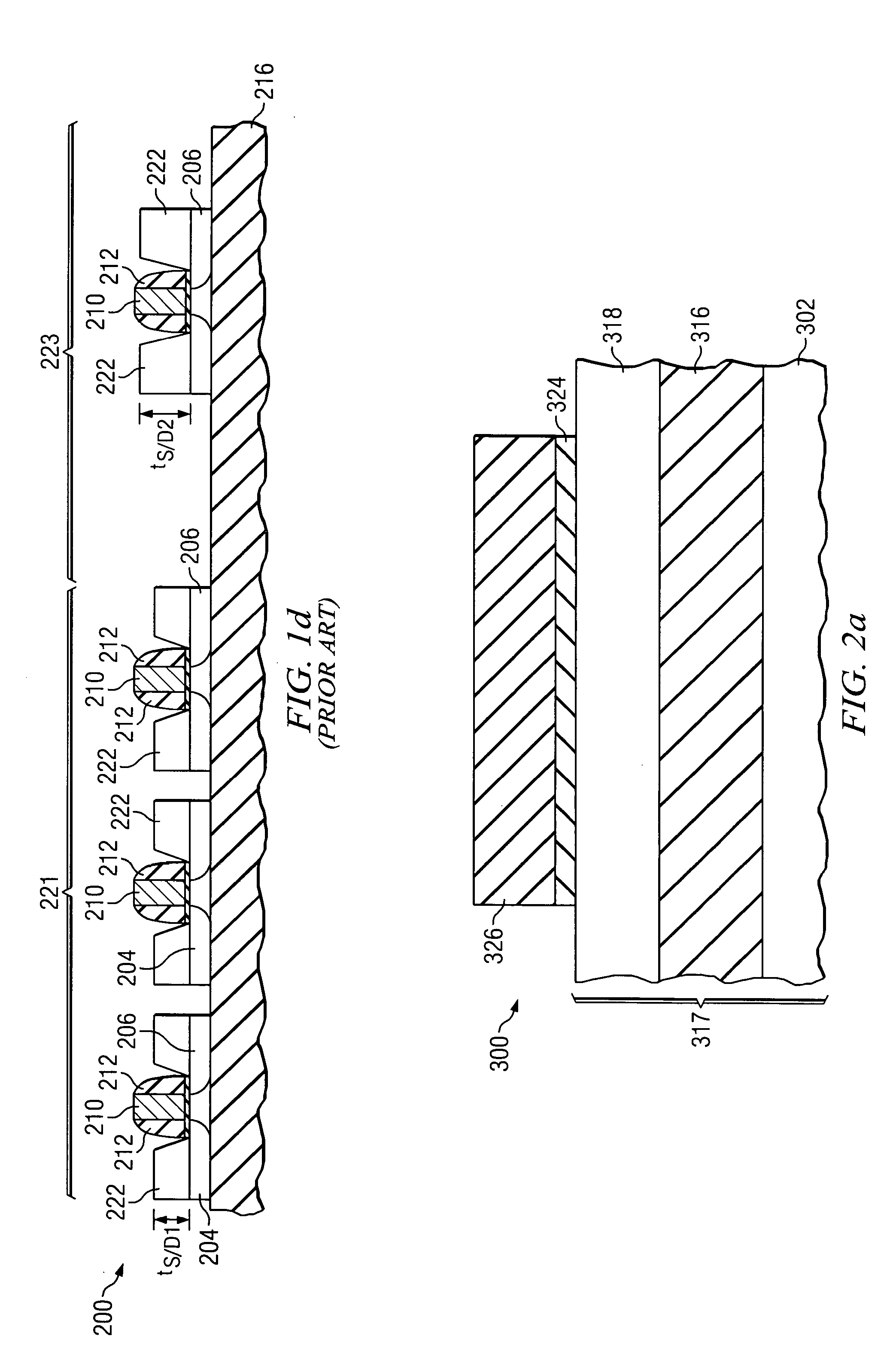

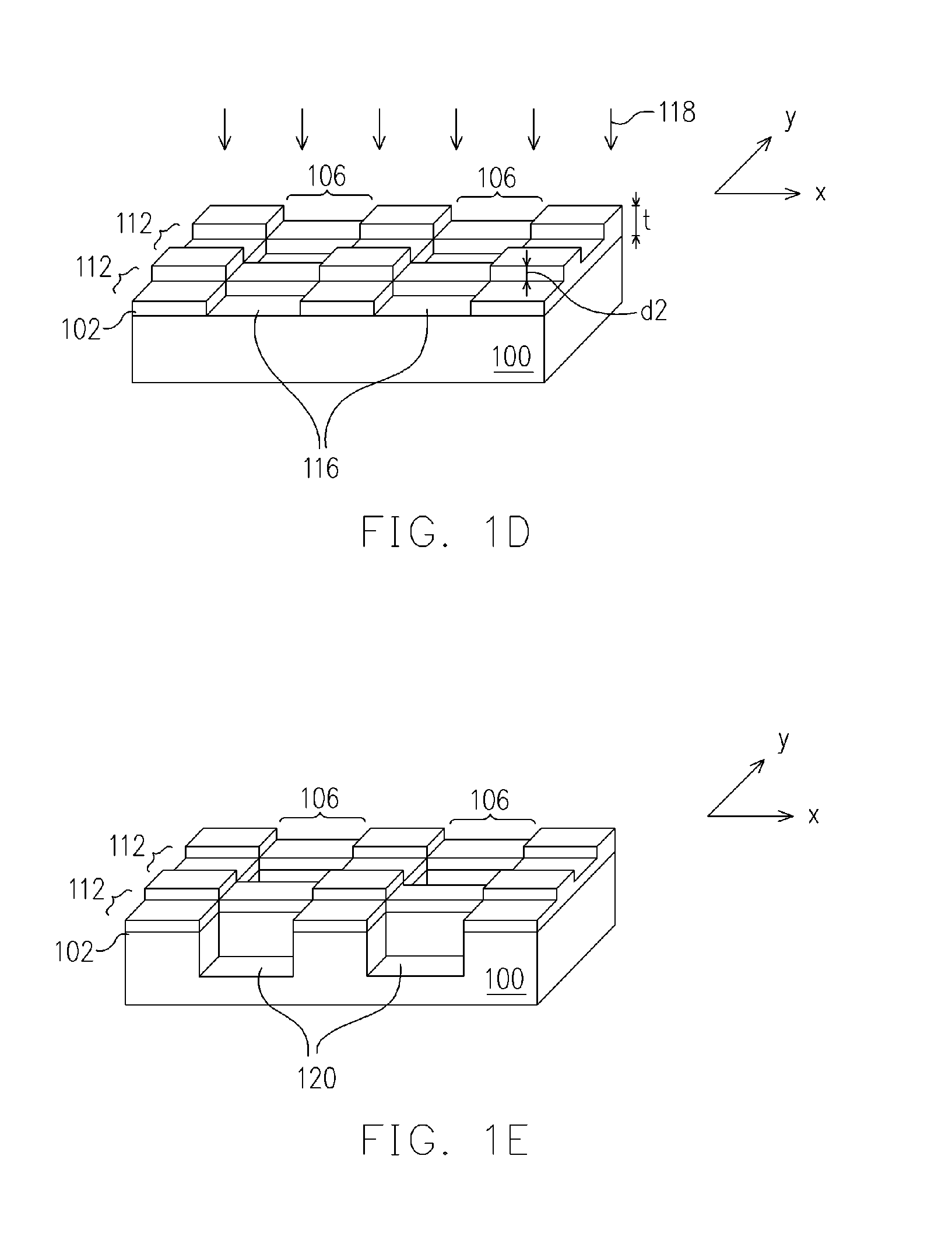

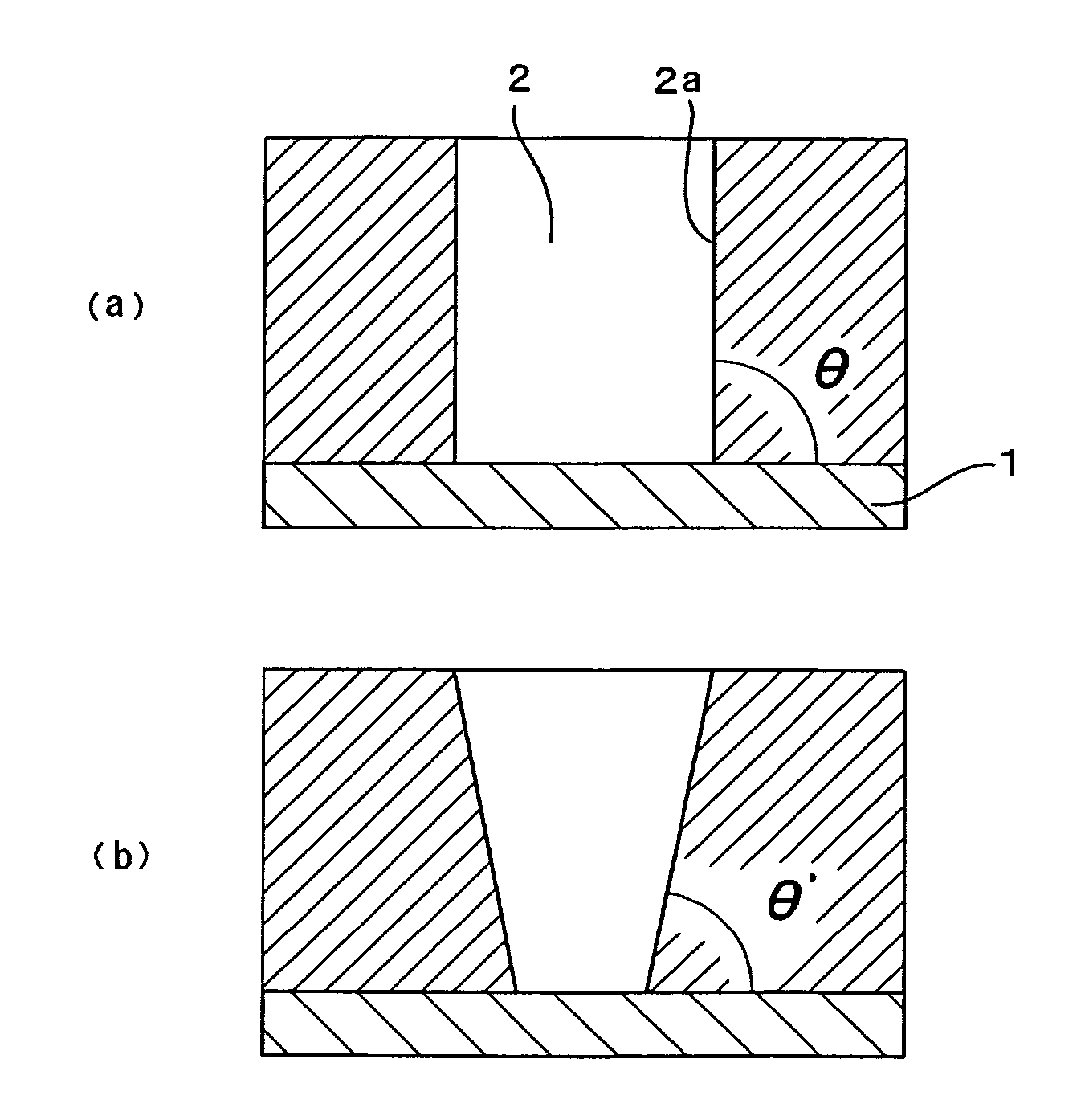

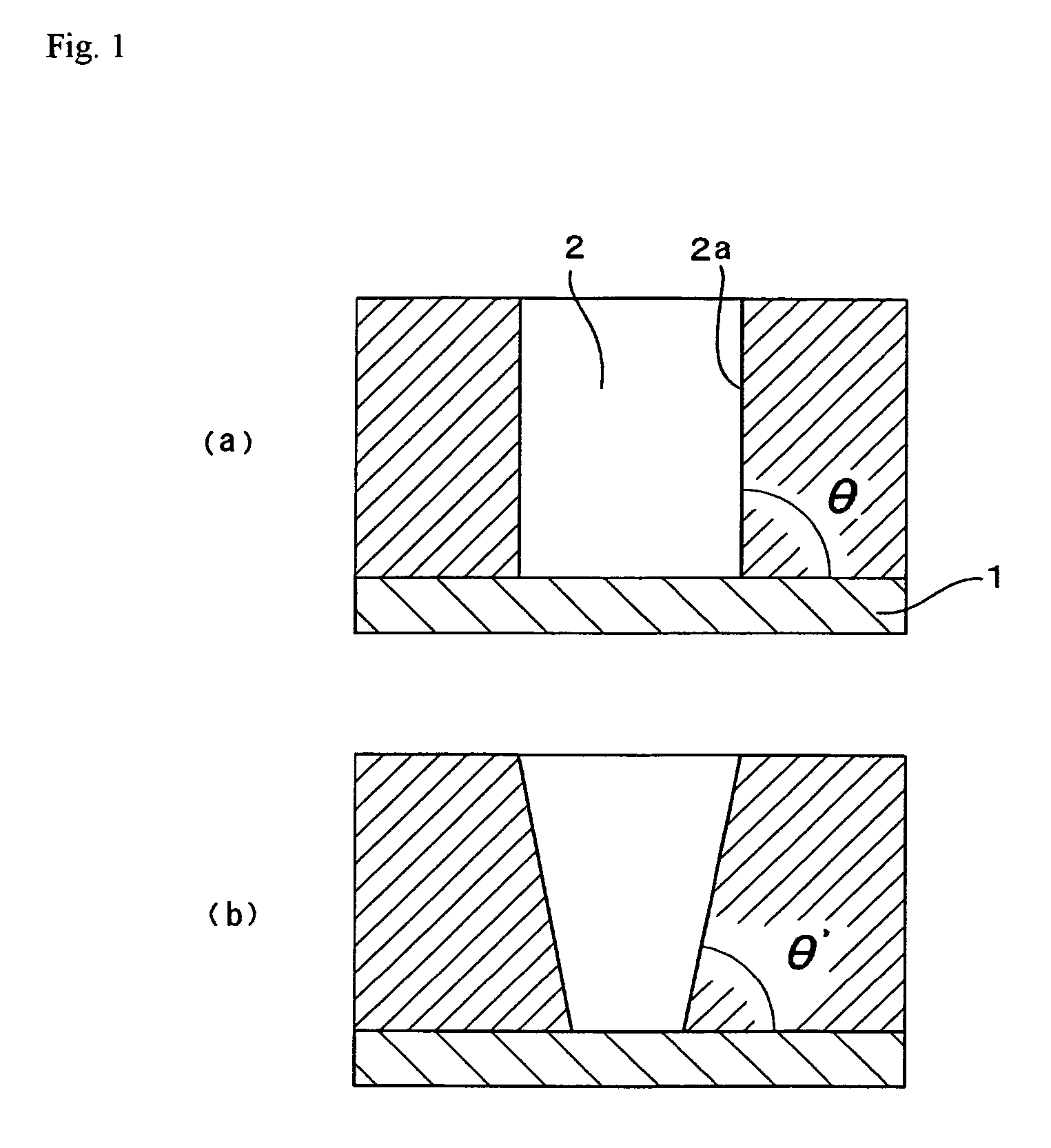

I-shaped and L-shaped contact structures and their fabrication methods

Contact structures having I shapes and L shapes, and methods of fabricating I-shaped and L-shaped contact structures, are employed in semiconductor devices and, in certain instances, phase-change nonvolatile memory devices. The I-shaped and L-shaped contact structures produced by these methods exhibit relatively small active areas. The methods that determine the contact structure dimensions employ conventional semiconductor deposit and etch processing steps that are capable of creating readily reproducible results.

Owner:MACRONIX INT CO LTD

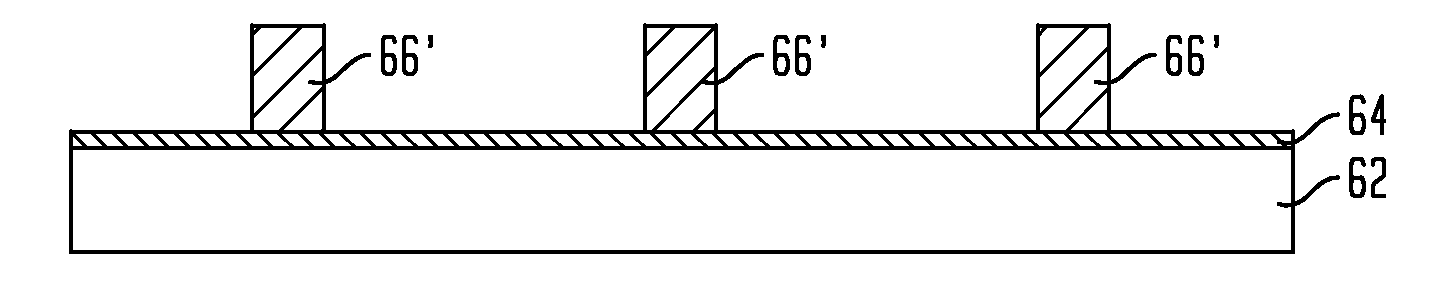

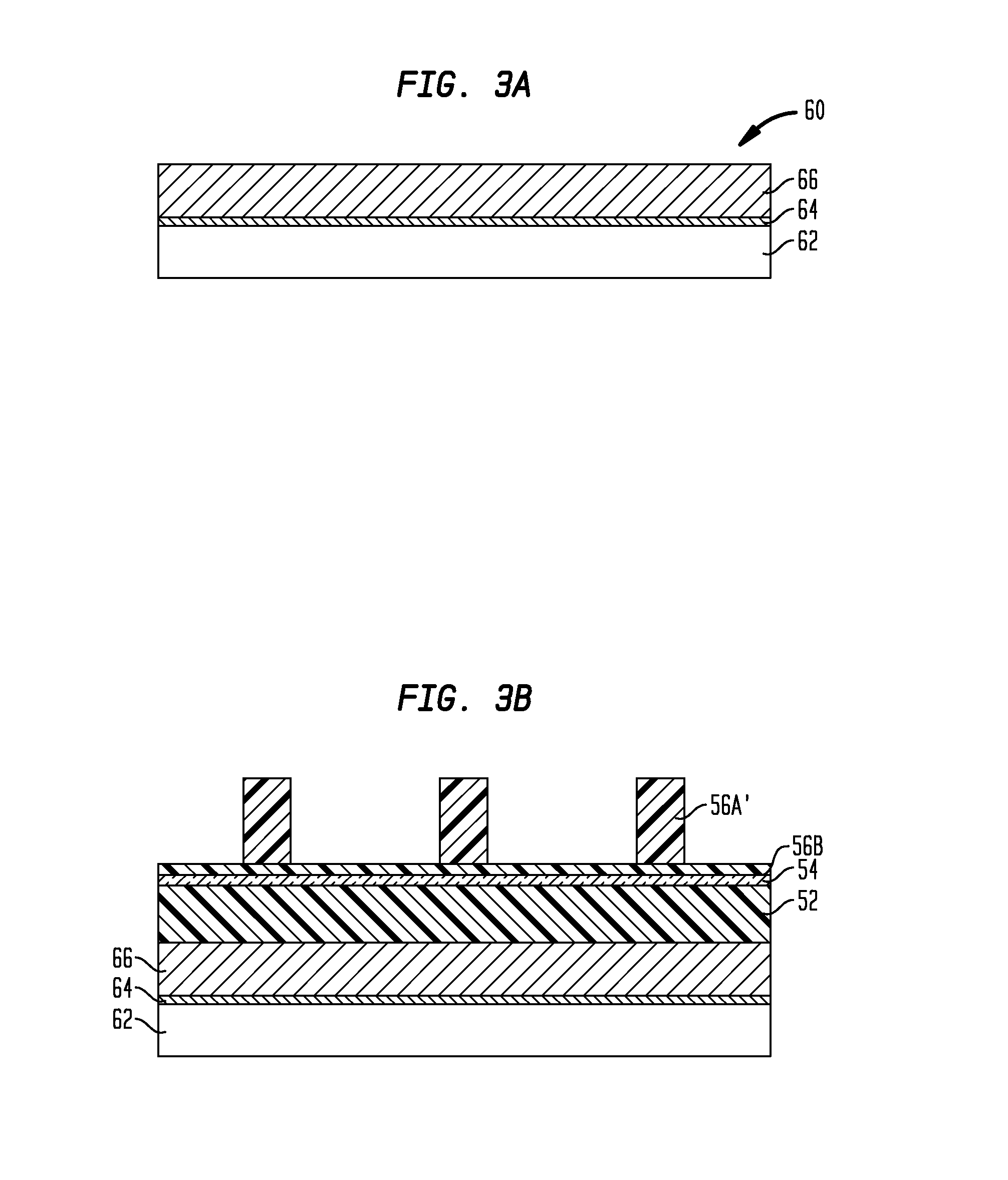

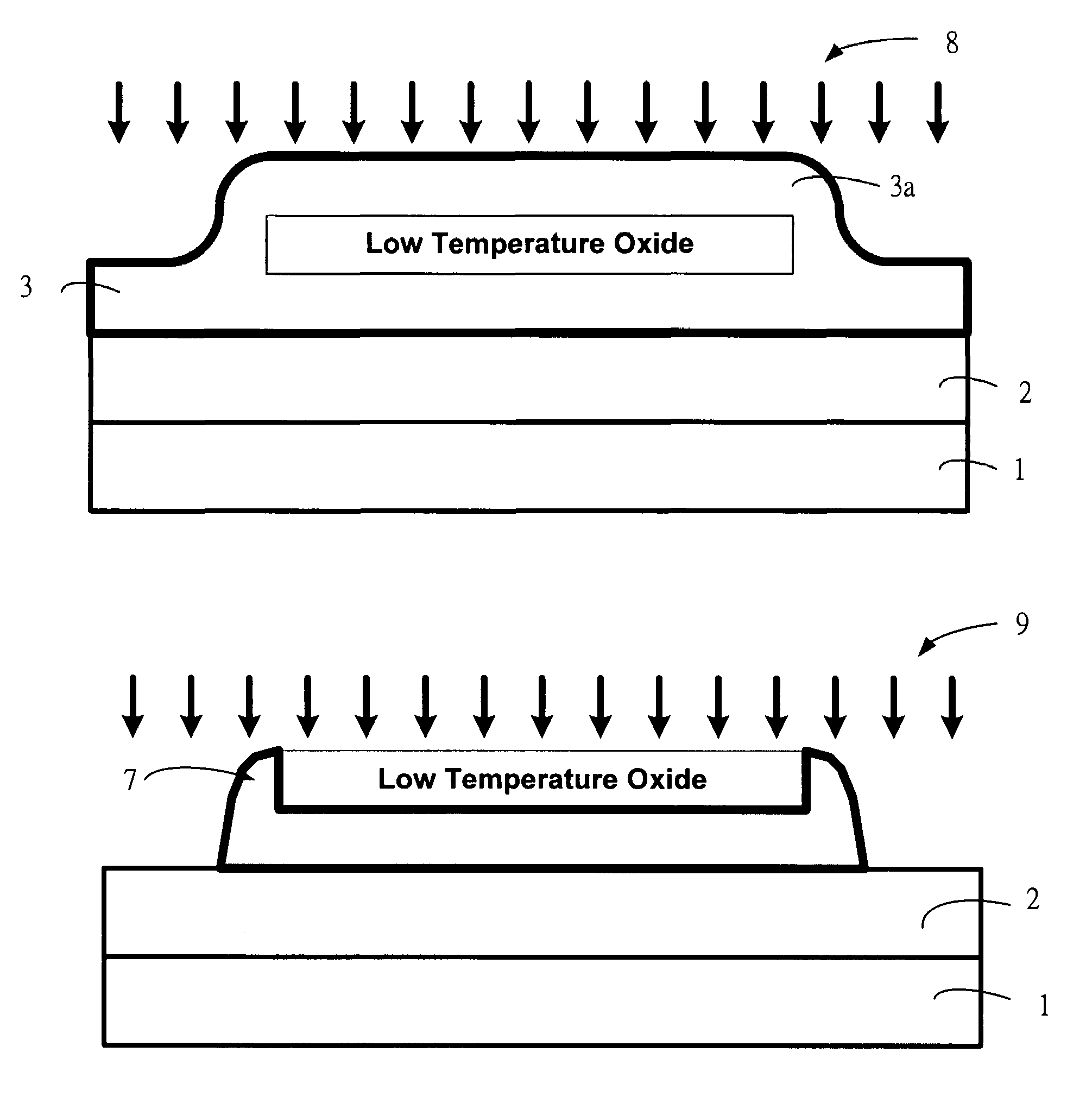

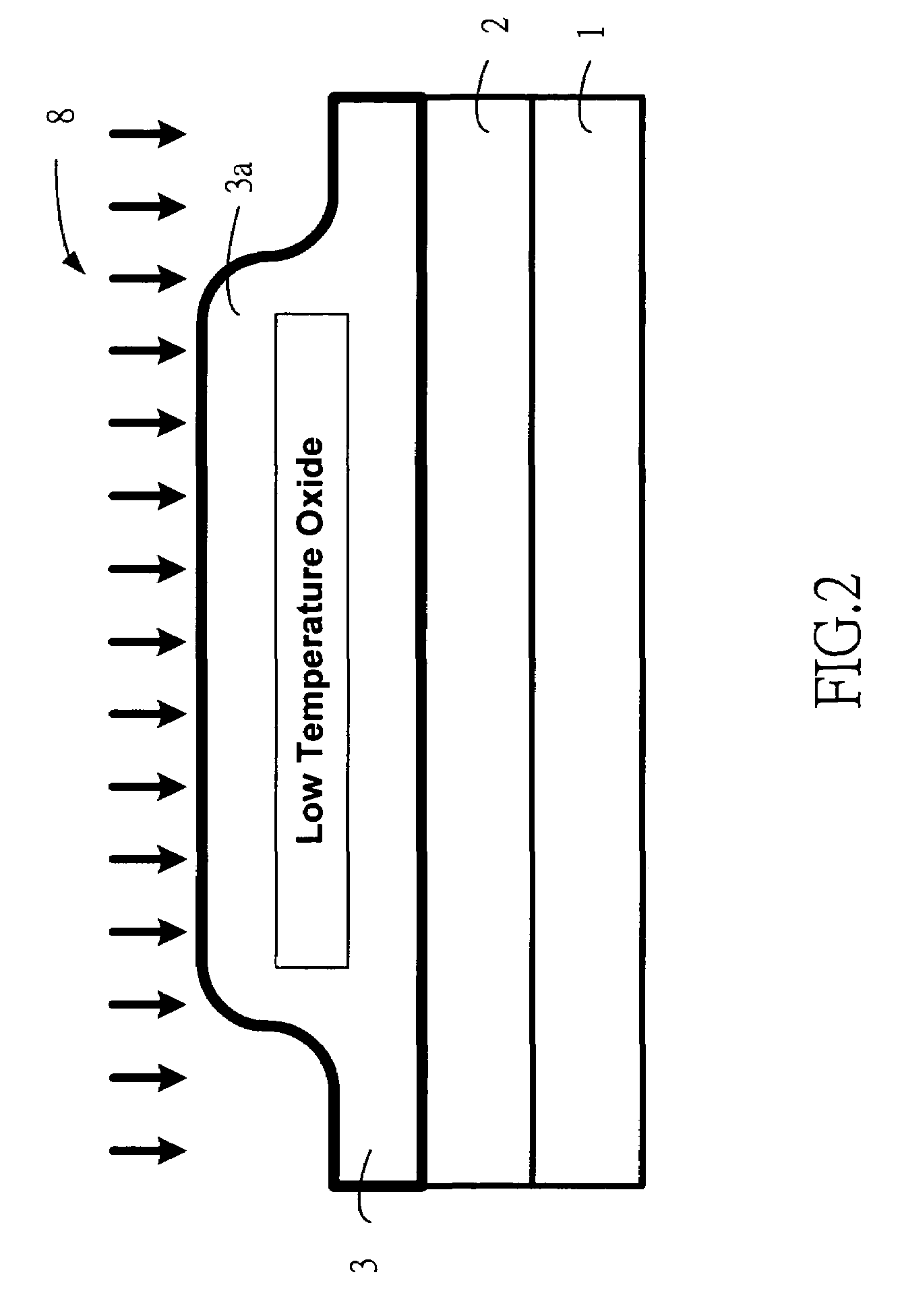

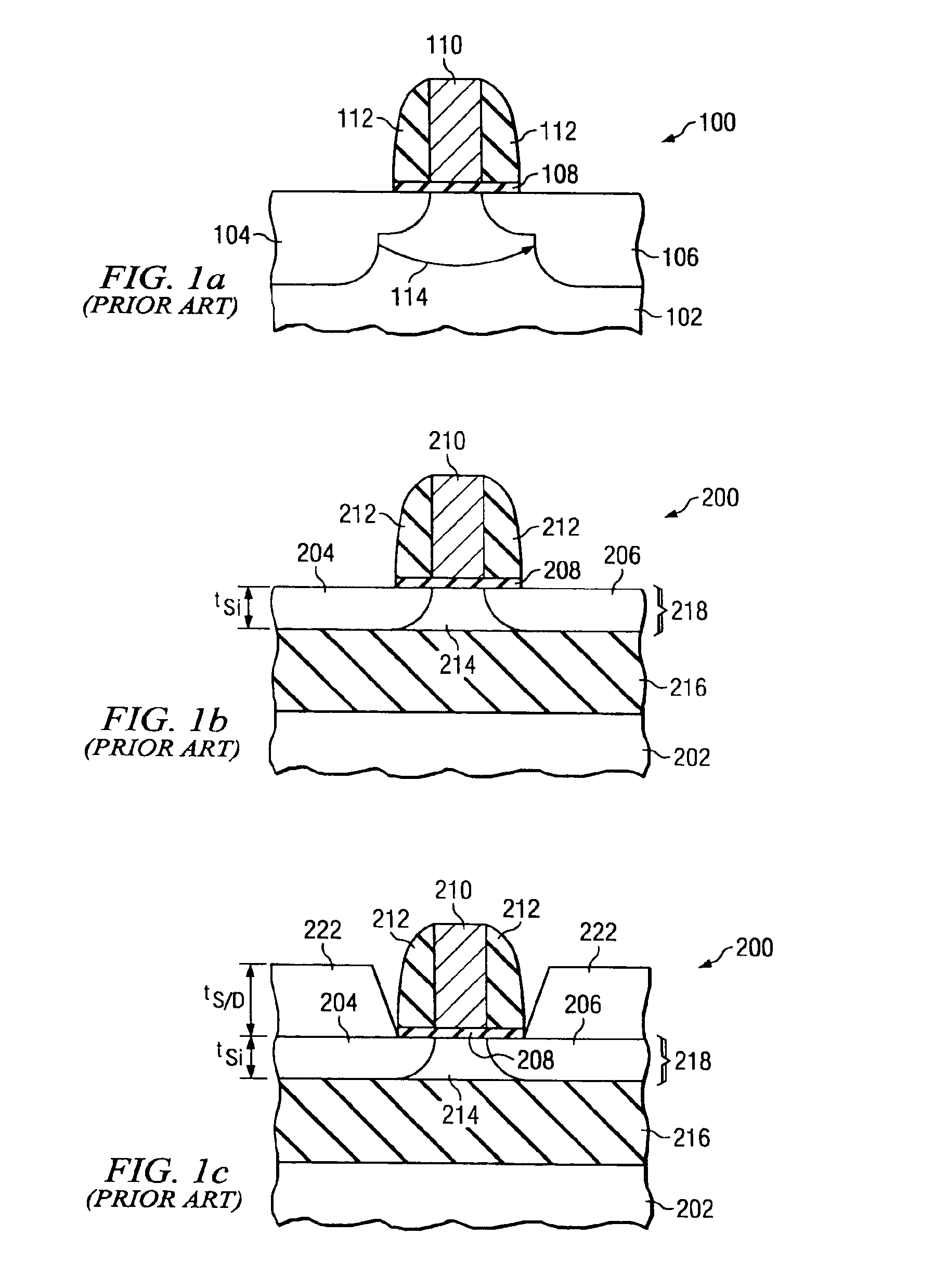

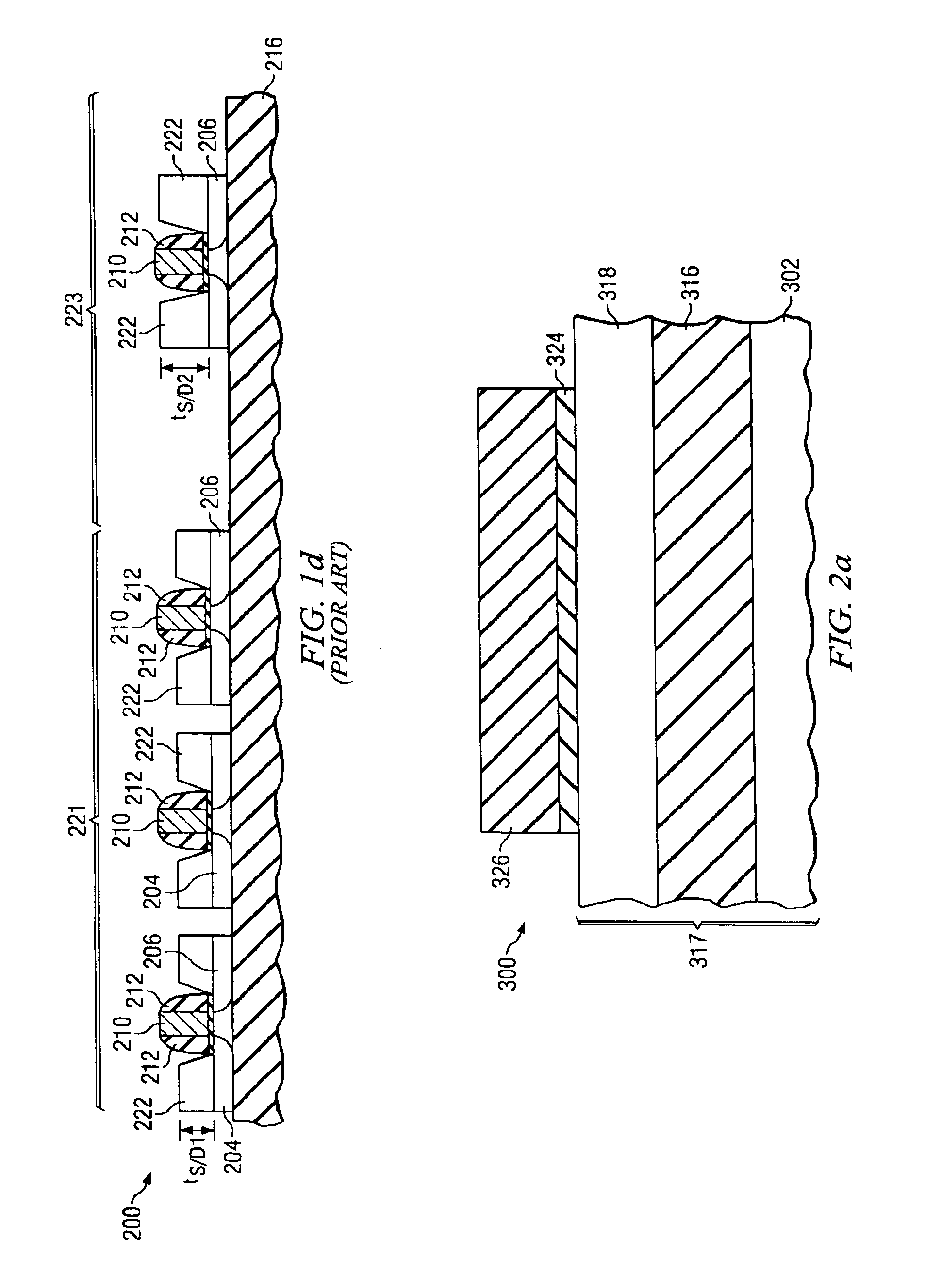

Trilayer resist scheme for gate etching applications

InactiveUS20080045011A1Minimizing extendAvoiding flopSemiconductor/solid-state device manufacturingResistDiamond-like carbon

A trilayer resist (TLR) patterning scheme is provided to enable gate conductors, particularly polySi gate conductors, with critical dimensions (CDs) of less than 40 nm and minimal LER and LWR. In accordance with the present invention, the inventive patterning scheme utilizes an organic / inorganic / organic multilayer stack instead of an organic layer used in the prior art. The top organic layer of the inventive TLR is a photoresist material such as a 193 nm photoresist that is located atop an antireflective coating (ARC), which is also comprised of an organic material. The middle inorganic layer of the TLR comprises any oxide layer such as, for example, a low temperature (less than or equal to 250° C.) chemical vapor deposited (CVD) oxide, an oxide derived from TEOS (tetraethylorthosilicate), silicon oxide, a silane oxide, or a Si-containing ARC material. The bottom organic layer of the TLR comprises any organic layer such as, for example, a Near Frictionless Carbon (NFC), a diamond-like carbon, a thermosetting polyarylene ether.

Owner:GLOBALFOUNDRIES INC

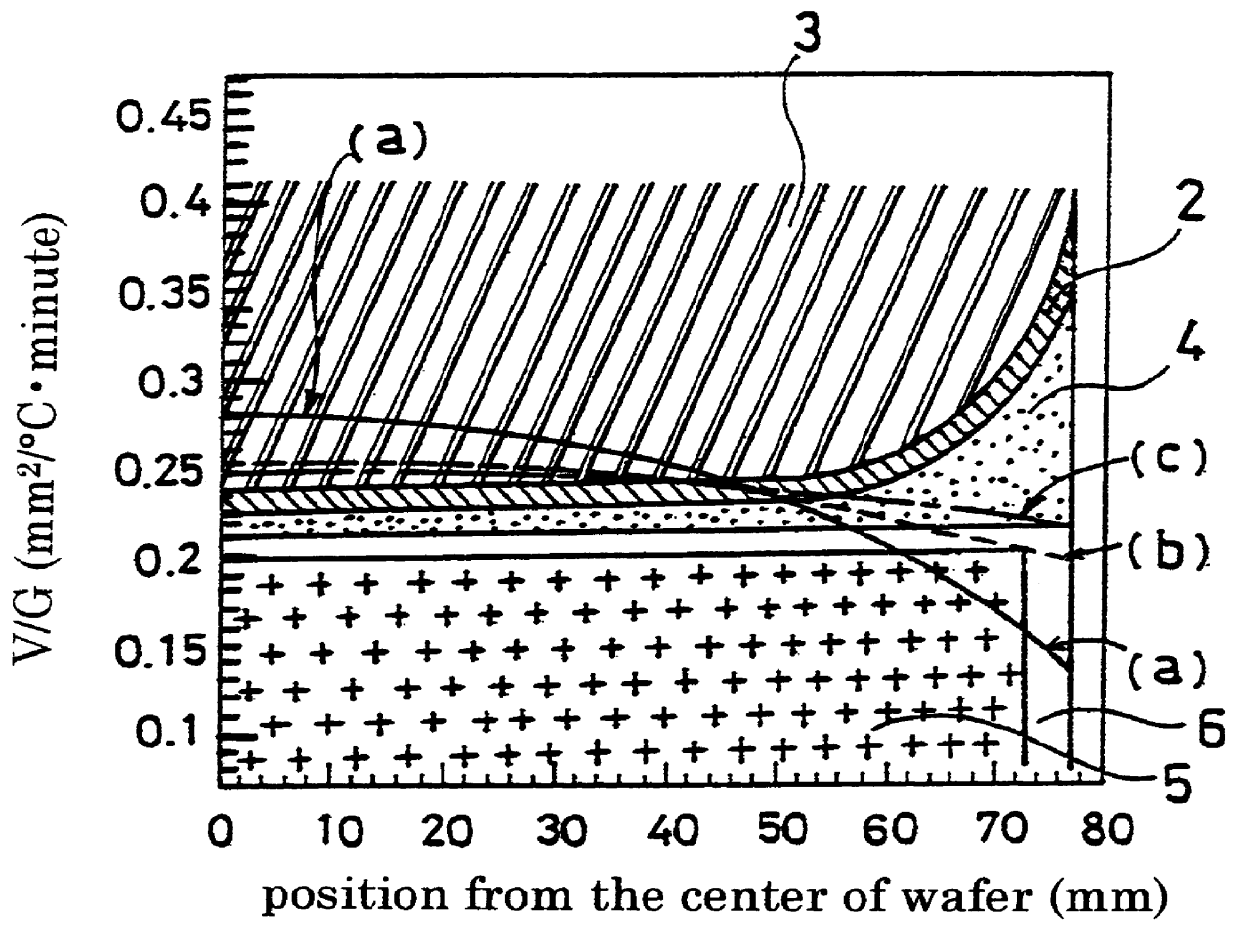

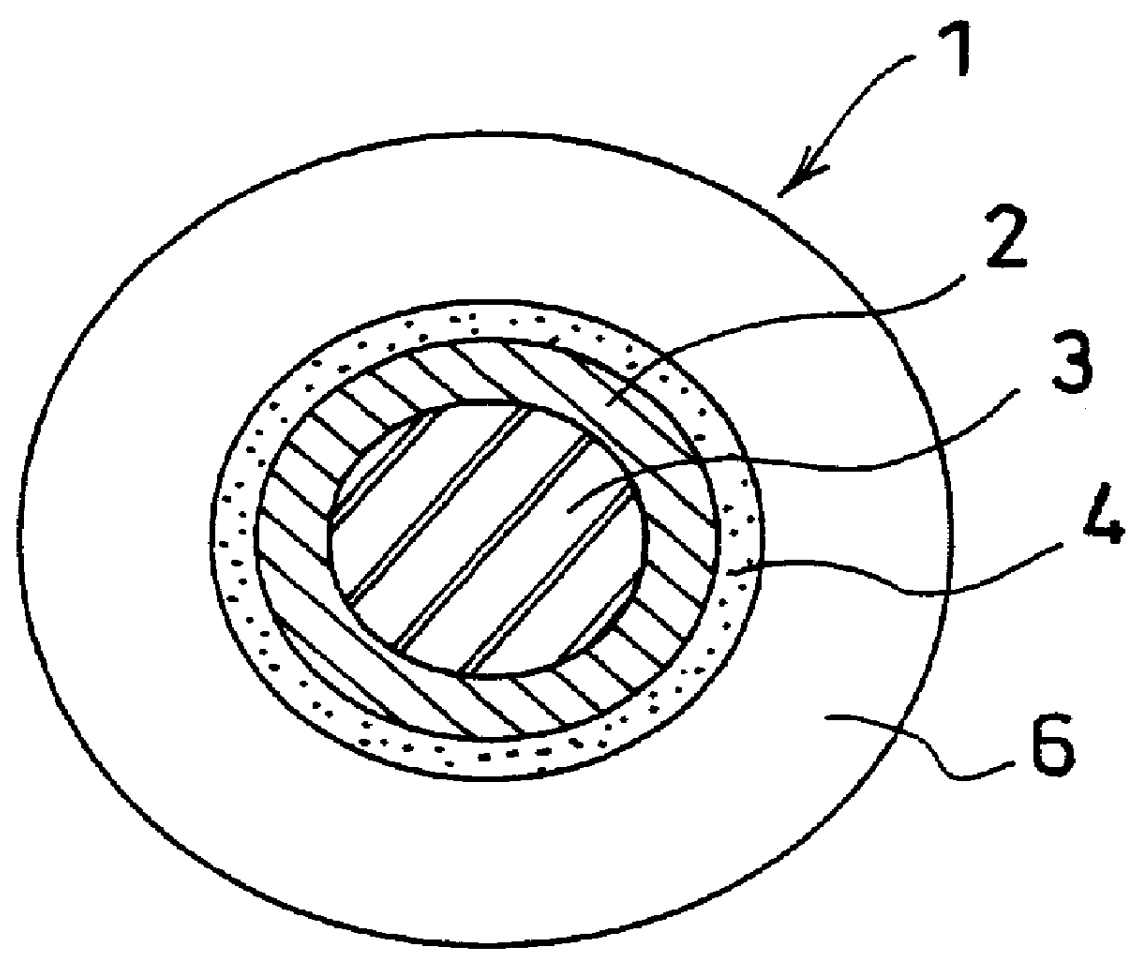

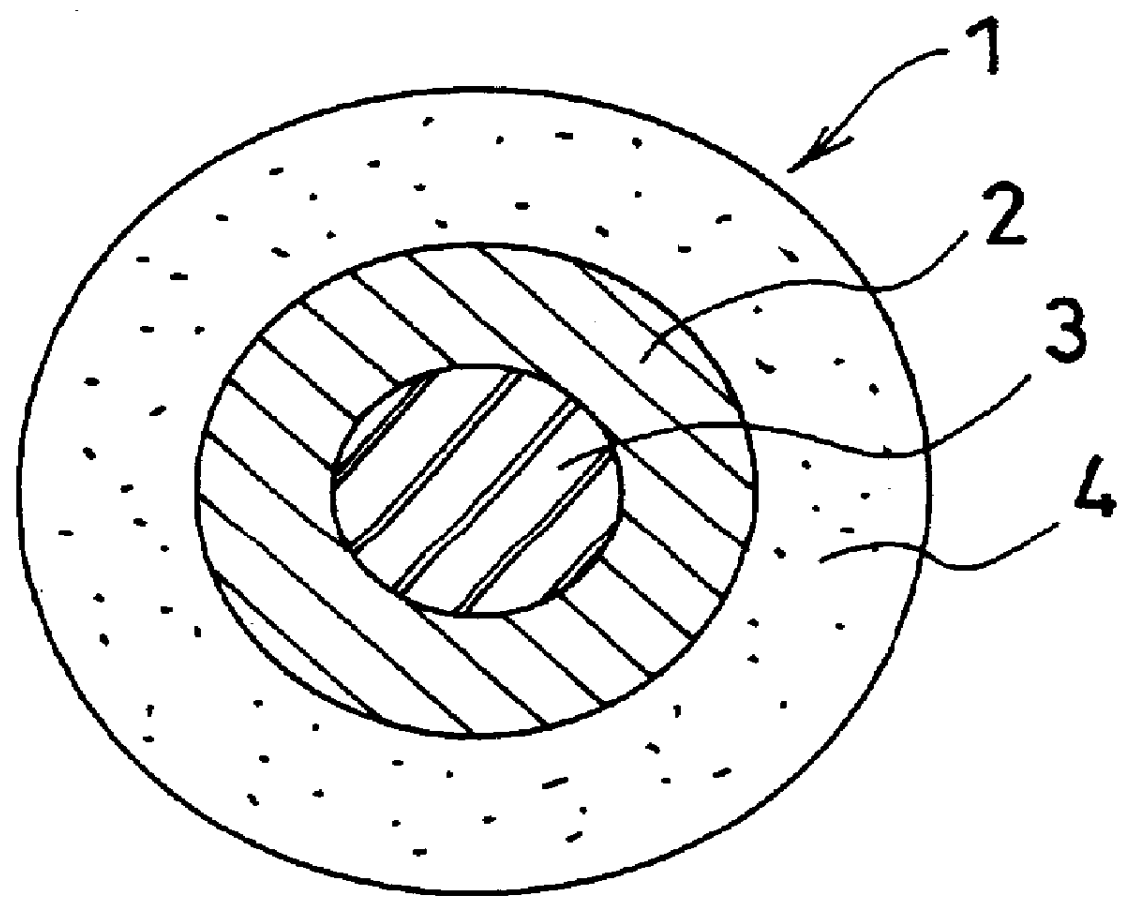

Method for making a silicon single crystal wafer

InactiveUS6113687AWider process windowImprove productivityPolycrystalline material growthSemiconductor/solid-state device manufacturingRadial positionCzochralski method

A silicon single crystal wafer having good device characteristics can be manufactured according to the Czochralski method without formation of any dislocation cluster within a crystal surface. Where a silicon single crystal having an oxygen concentration of less than 8.5x1017 atoms / cm3 (ASTM F1188-88) is manufactured, a radius of a latent zone of oxidation induced stacking defects ring-likely-distributed in the crystal surface is made within a range of 70% to 0% of a crystal radius, and a value of V / G (mm2 / DEG C.xminute) is controlled at a predetermined critical value or over at radial positions except an outermost periphery of the crystal when a pulling rate is taken as V (mm / minute), and a crystalline temperature gradient along the pulling axis is taken as G ( DEG C. / mm). On the other hand, when a silicon single crystal having an oxygen concentration of not less than 8.5x1017 atoms / cm3 (ASTM F1188-88) is manufactured, a pulling rate is further set at 1.0 mm / minute or over. In the method for manufacturing the silicon single crystal wafer, it is preferred to calculate the crystalline temperature gradient G along the pulling axis through heat transfer calculation, set the critical value of V / G at 0.20 mm2 / DEG C.xminute, and control the value of V / G at a value larger than the critical value.

Owner:SUMITOMO MITSUBISHI SILICON CORP

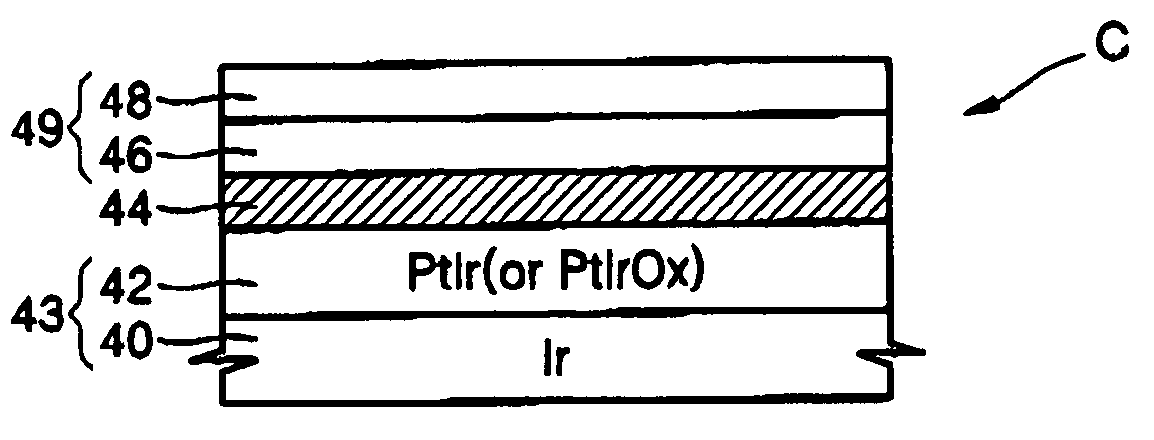

Capacitor of a semiconductor device, memory device including the same and method of munufacturing the same

InactiveUS20050161726A1Reduce leakage currentPromote growthTransistorSolid-state devicesDevice materialAlloy

In a capacitor, a memory device including the capacitor, and a method of manufacturing the capacitor, the capacitor includes a lower electrode comprising a single layer of one selected from the group including a noble metal alloy and an oxide thereof, a dielectric film formed on the lower electrode, and an upper electrode formed on the dielectric film.

Owner:SAMSUNG ELECTRONICS CO LTD

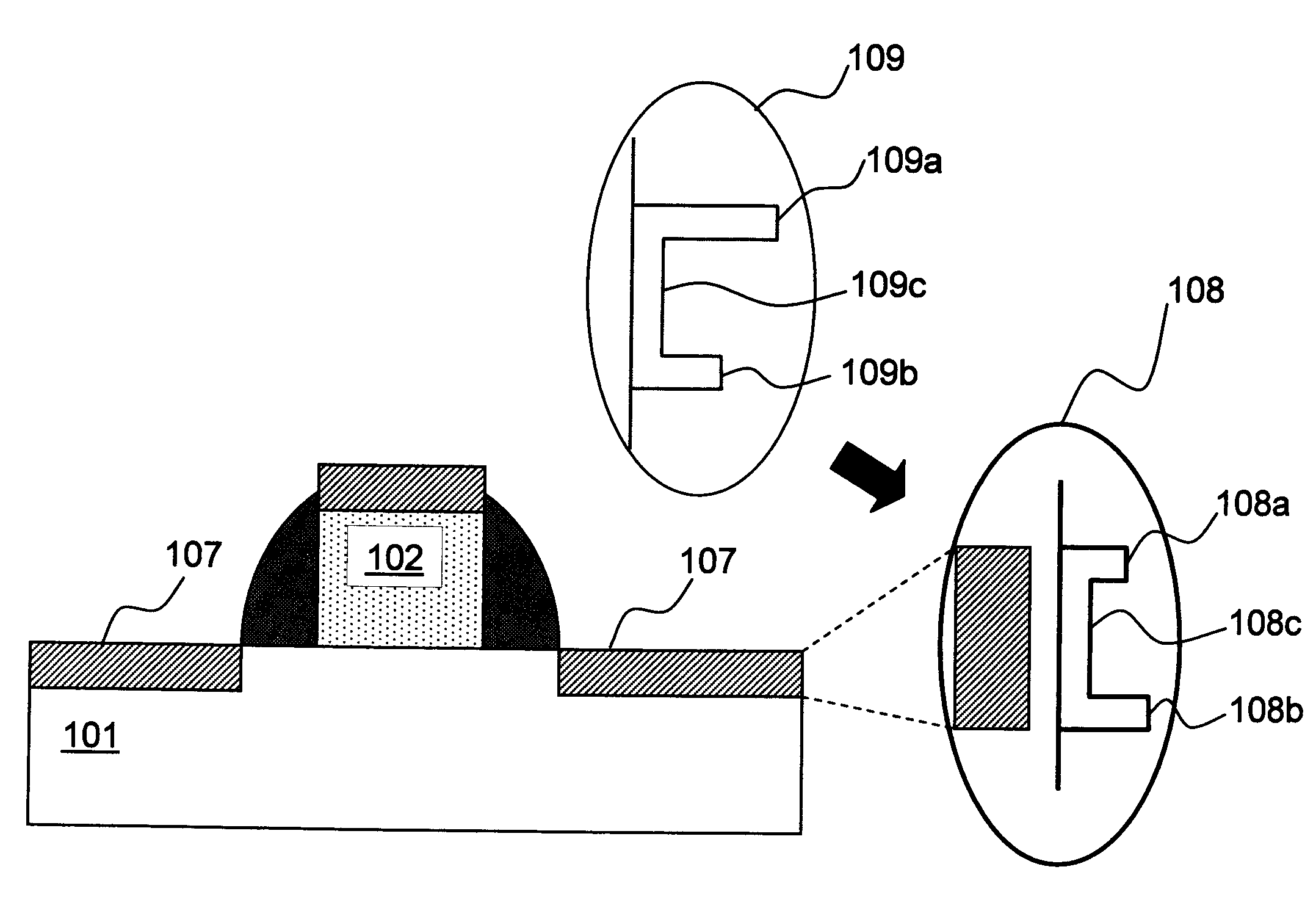

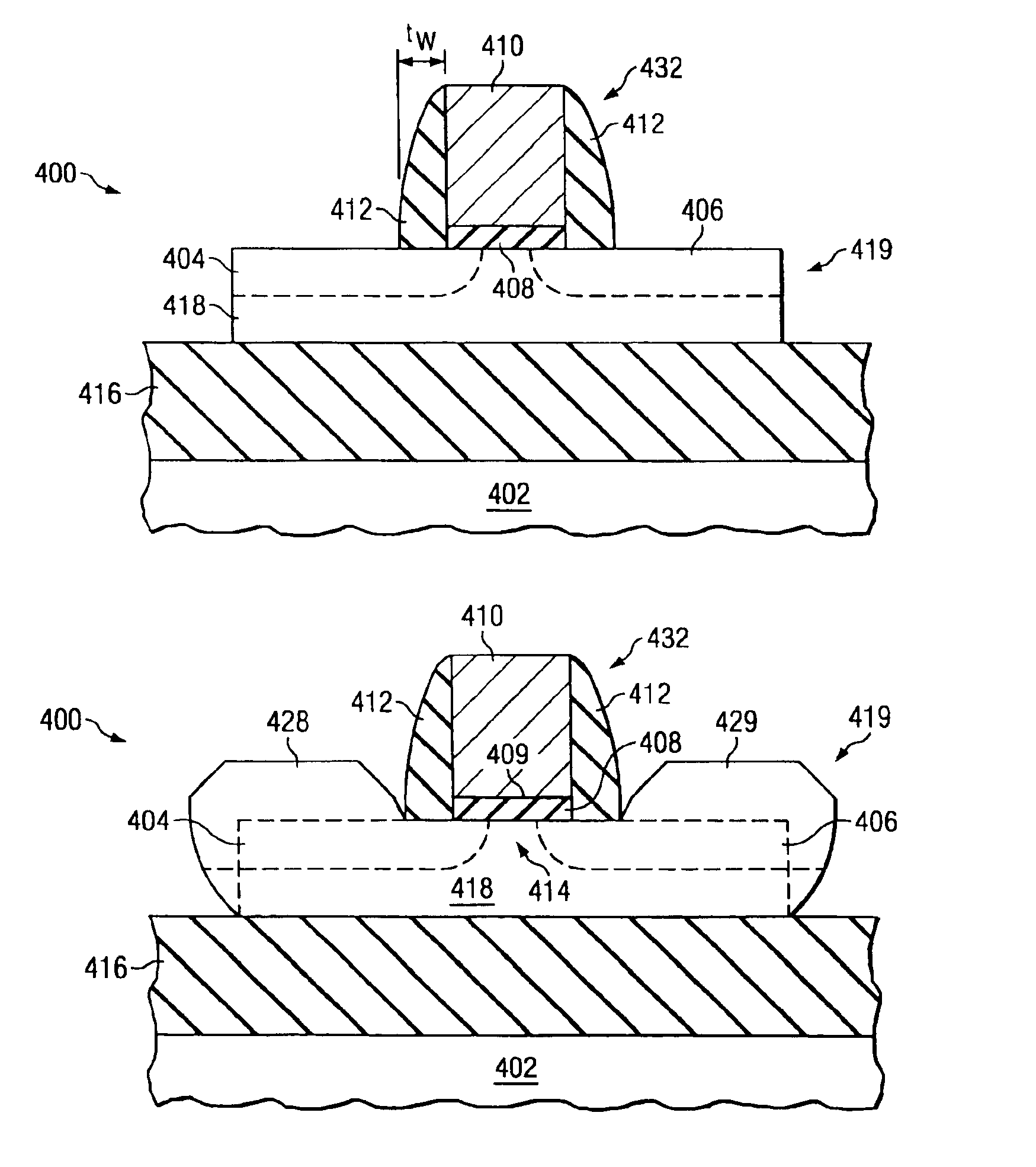

Semiconductor device with raised segment

ActiveUS20050156248A1Inexpensively formedRaised source and drain structure to be formed with easeTransistorSolid-state devicesSemiconductor materialsDevice material

A device having a raised segment, and a manufacturing method for same. An SOI wafer is provided having a substrate, an insulating layer disposed over the substrate, and a layer of semiconductor material disposed over the insulating layer. The semiconductor material is patterned to form a mesa structure. The wafer is annealed to form a raised segment on the mesa structure.

Owner:TAIWAN SEMICON MFG CO LTD

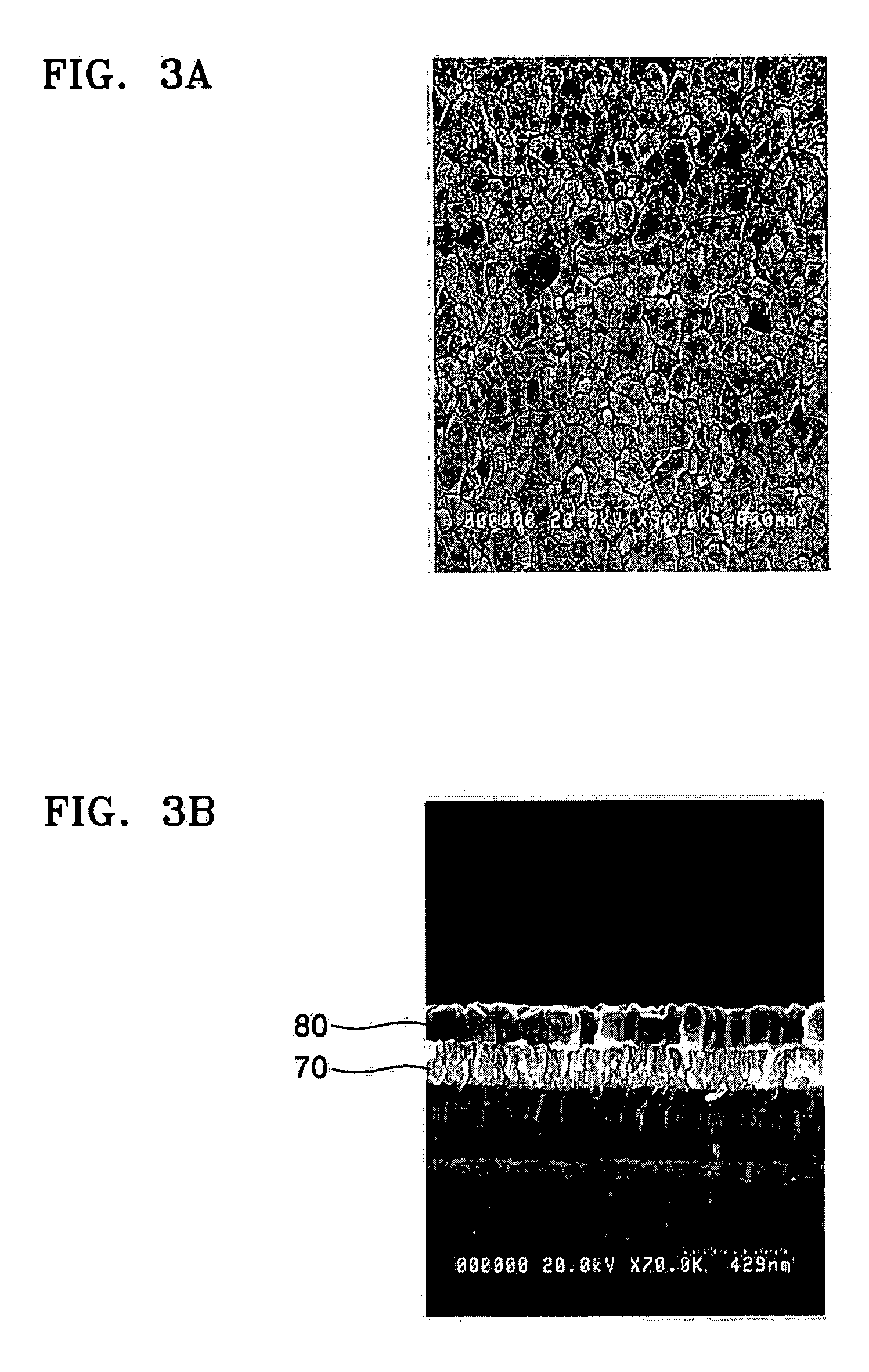

Nickel-silicide formation with differential pt composition

InactiveUS20110169058A1Wider process windowReduced and less defectivitySemiconductor/solid-state device manufacturingSemiconductor devicesNickelPhysical vapor deposition

Embodiments of the invention provide a method of forming nickel-silicide. The method may include depositing first and second metal layers over at least one of a gate, a source, and a drain region of a field-effect-transistor (FET) through a physical vapor deposition (PVD) process, wherein the first metal layer is deposited using a first nickel target material containing platinum (Pt), and the second metal layer is deposited on top of the first metal layer using a second nickel target material containing no or less platinum than that in the first nickel target material; and annealing the first and second metal layers covering the FET to form a platinum-containing nickel-silicide layer at a top surface of the gate, source, and drain regions.

Owner:AURIGA INNOVATIONS INC

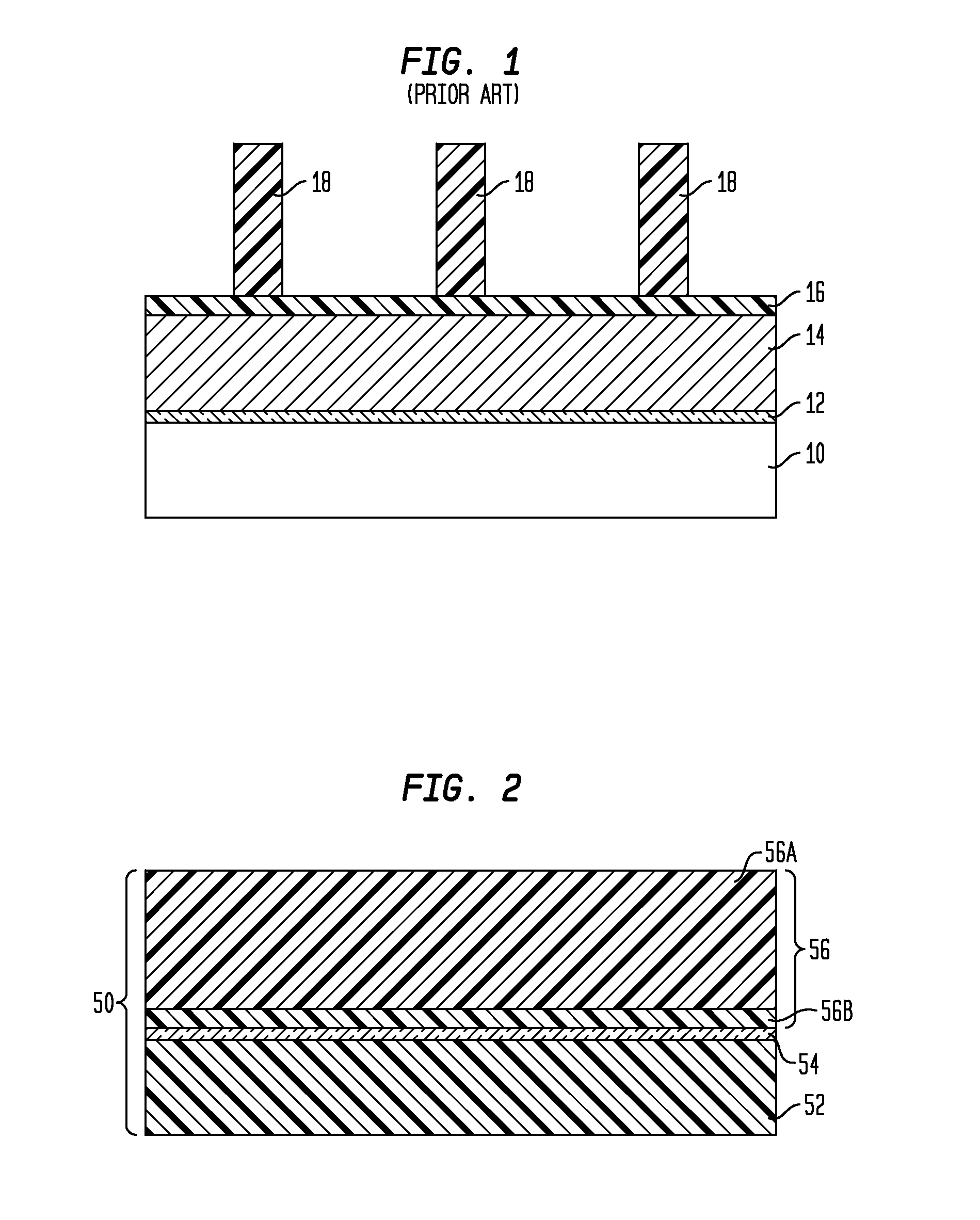

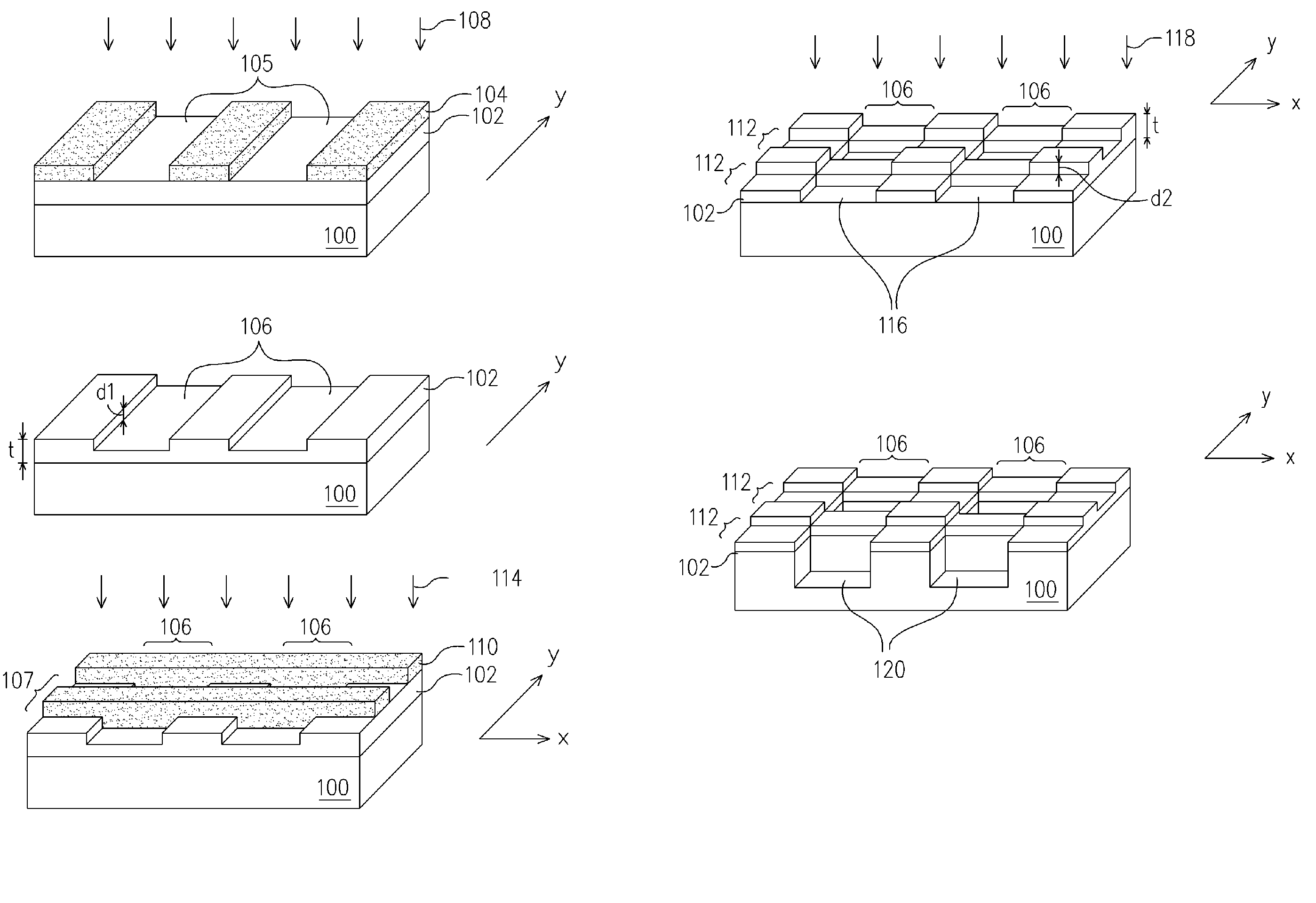

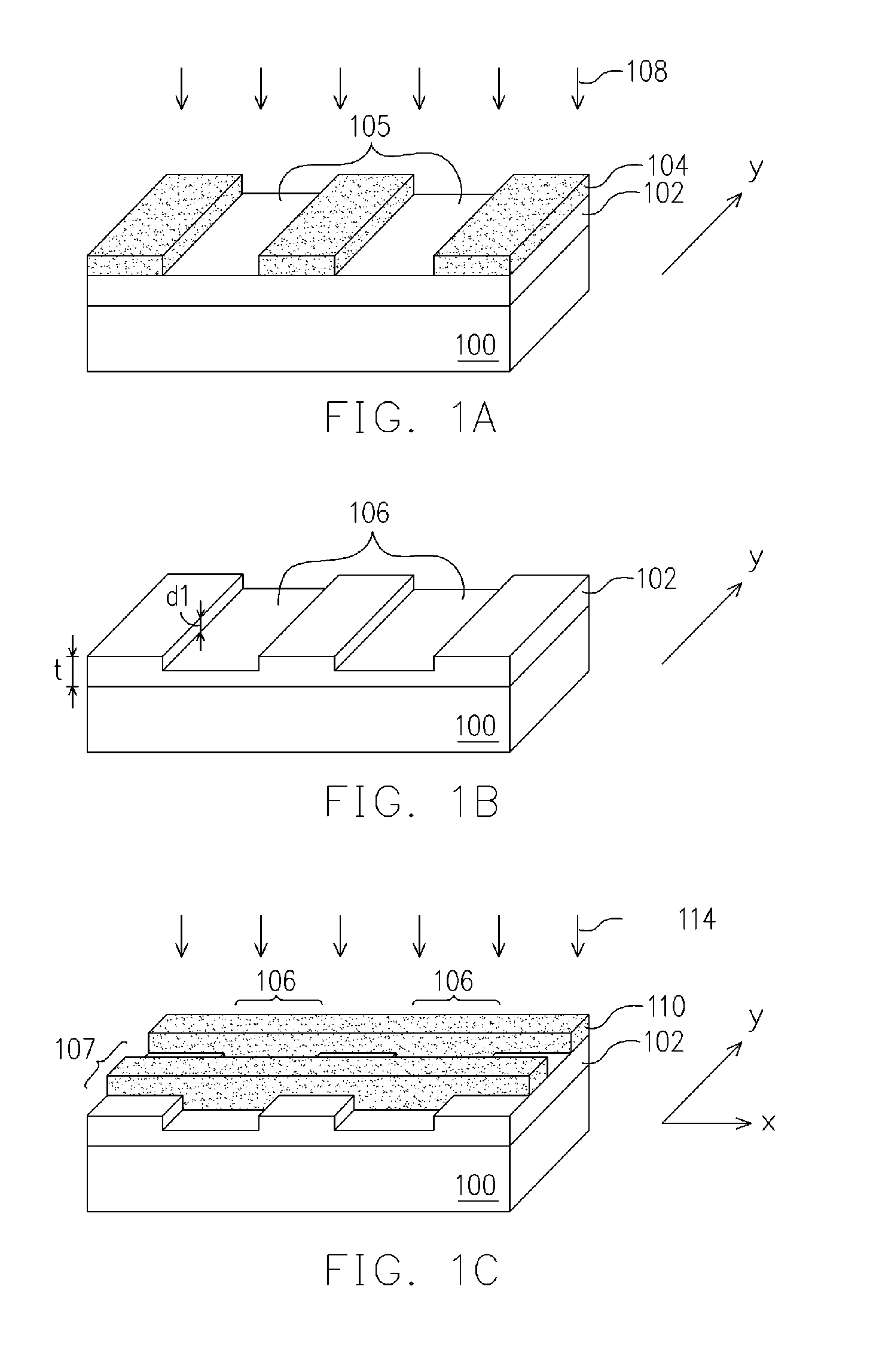

Method of manufacturing contact hole

InactiveUS20070082472A1Improve abilitiesIncreased process windowSemiconductor/solid-state device manufacturingEngineeringPhotolithography

A method of manufacturing contact hole is provided. First, a mask layer is formed on a substrate and a plurality of trenches is formed in the mask layer along two directions that cross over each other. The depth of the trenches is not greater than the thickness of the mask layer. However, there is an opening in the mask layer in the place where the trenches cross over each other. The opening exposes the substrate. Part of the substrate exposed by the opening is removed to form a contact hole in the substrate. In photolithography, it is easier to form lines than to form dots. Hence, the dimensions of contact holes are more precisely controlled.

Owner:POWERCHIP SEMICON CORP

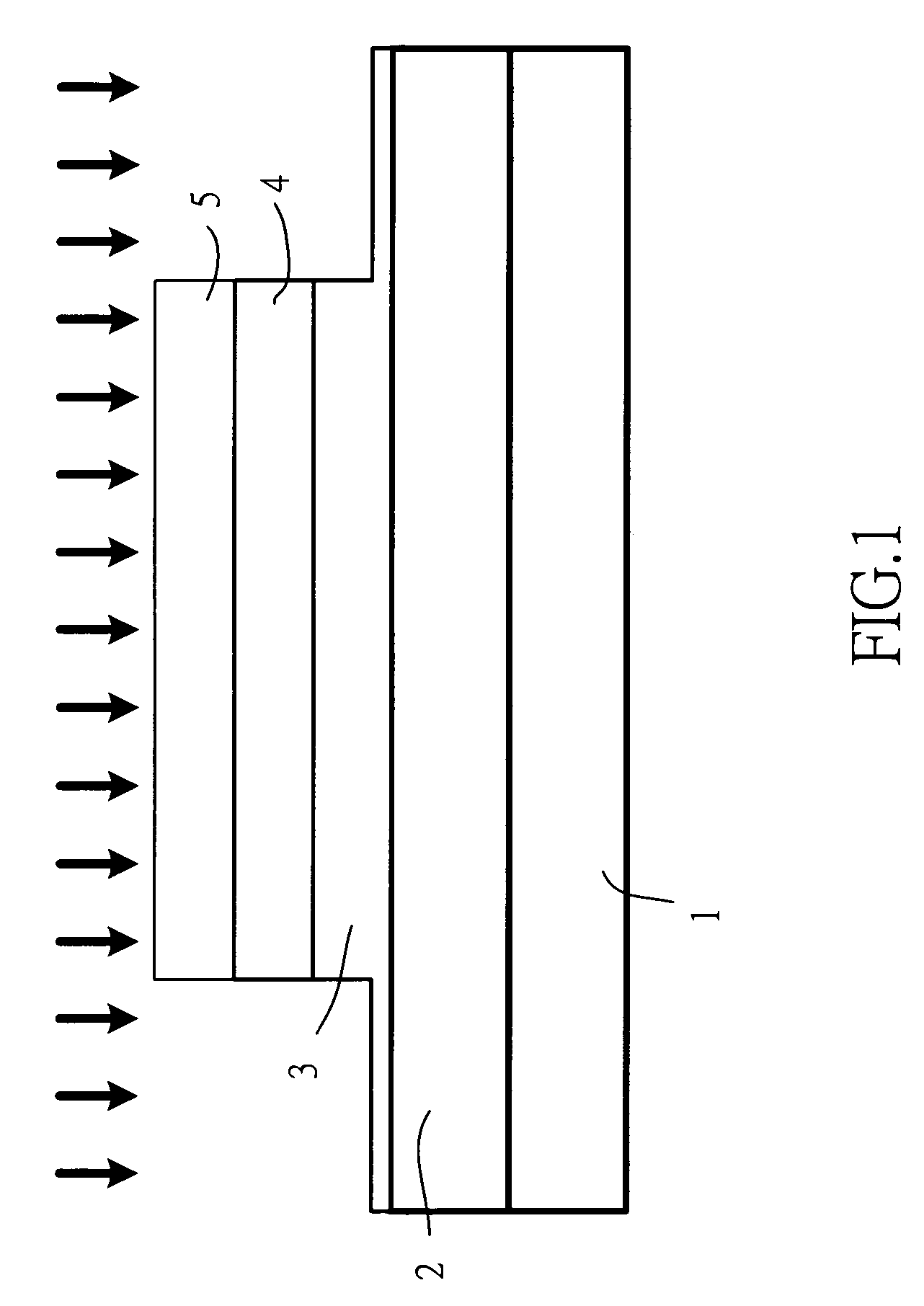

Method for fabrication of polycrystalline silicon thin film transistors

InactiveUS7115449B2Improve mobilityReduce the differenceSolid-state devicesSemiconductor/solid-state device manufacturingAnisotropic plasmaActive layer

The present invention provides a method for fabrication of polycrystalline silicon thin film transistors, which forms a silicon spacer on the sidewall of the active layer of a thin film transistor (TFT) by way of anisotropic plasma etching in a single direction. The silicon spacer provides a mechanism for laser recrystallization on the sidewall to prevent the active layer from shrinkage or shelling-off after the laser recrystallization. According to the present invention, large grains can be formed in the channel without additional mask during production. By doing so, the characteristics of the components are enhanced; the uniformity is improved; and, the production cost is lowered. Therefore, this technique will play an important role in the fields of low temperature polycrystalline silicon thin film transistor (LTPS-TFT).

Owner:NAT CHIAO TUNG UNIV

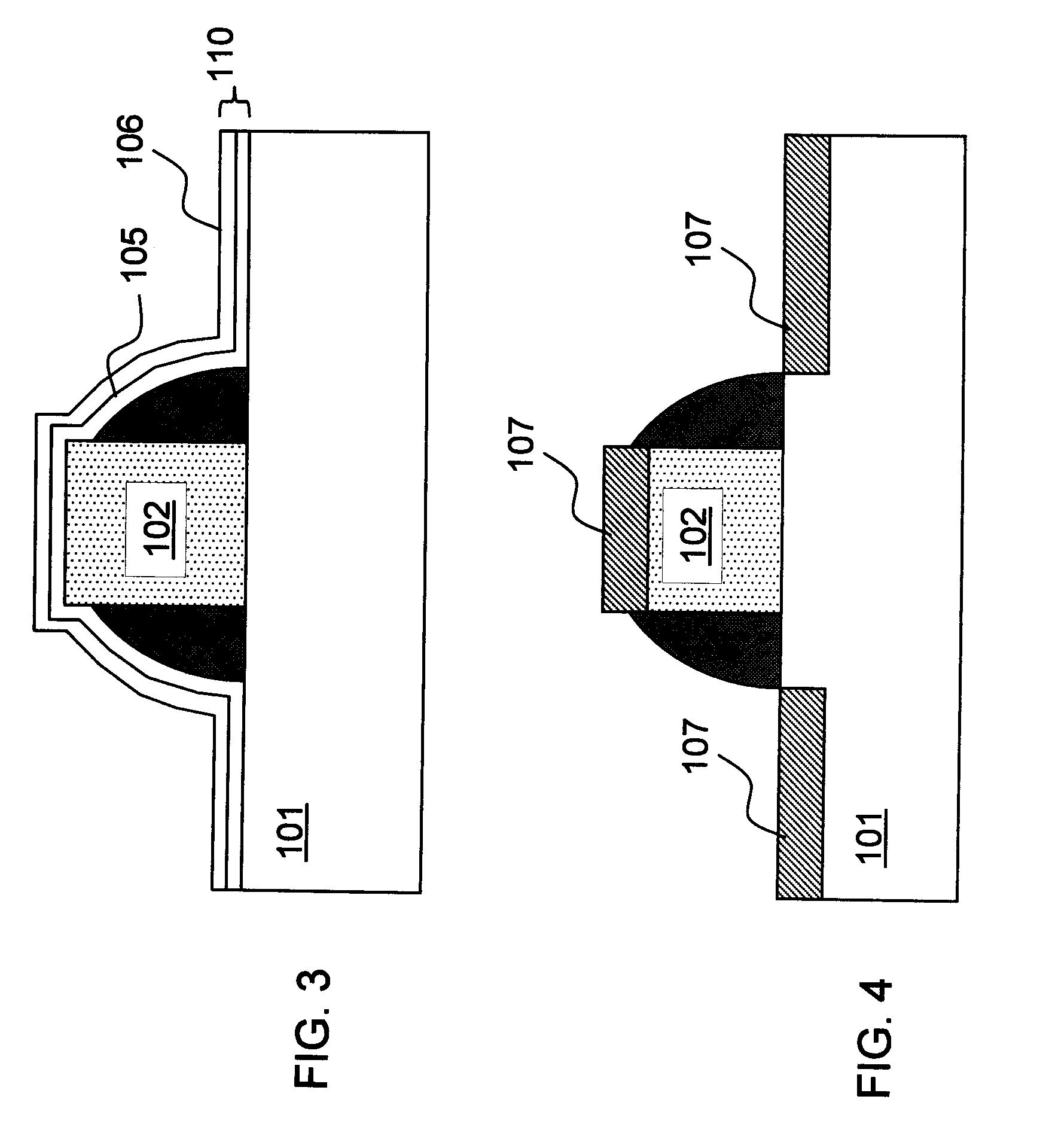

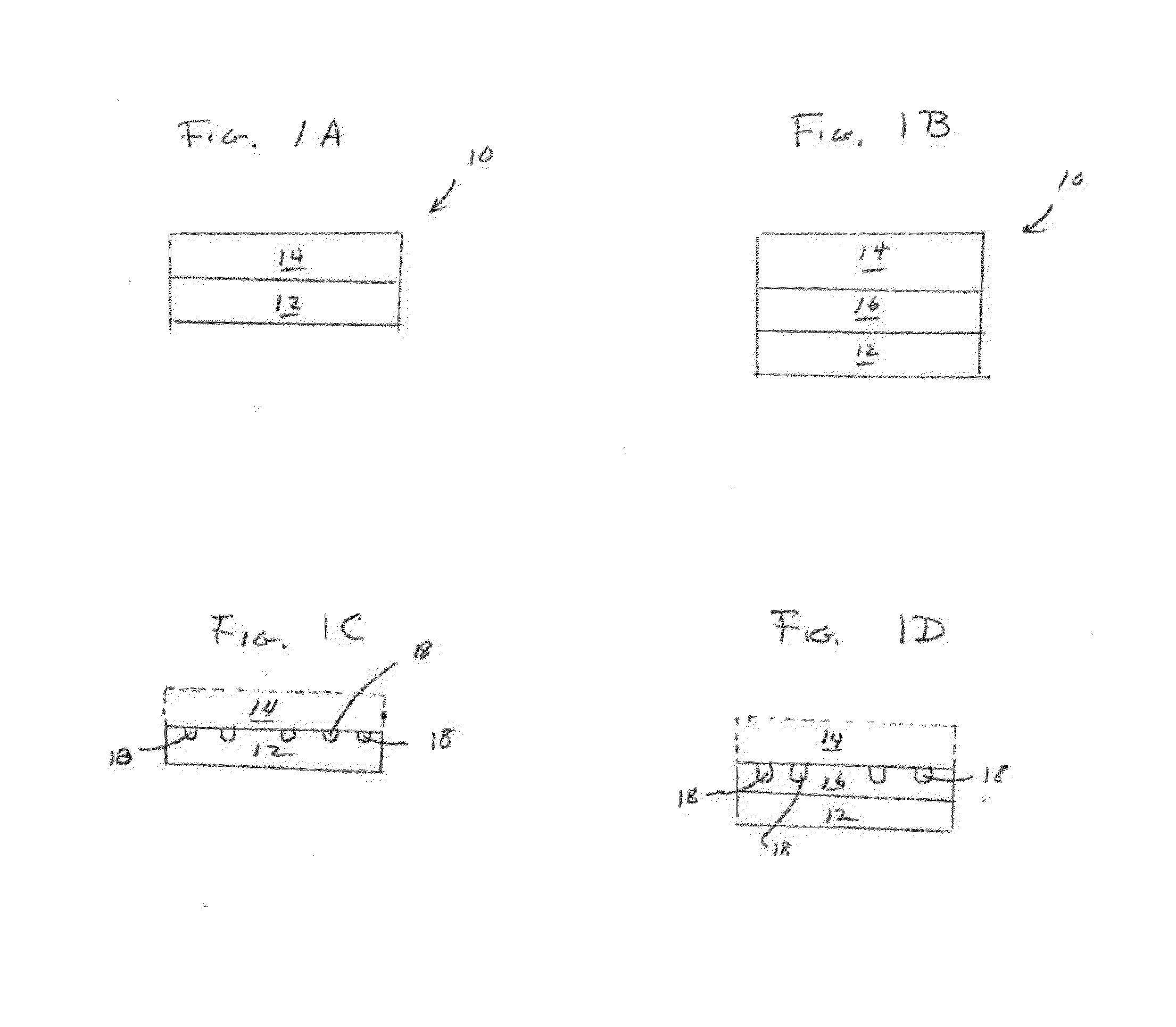

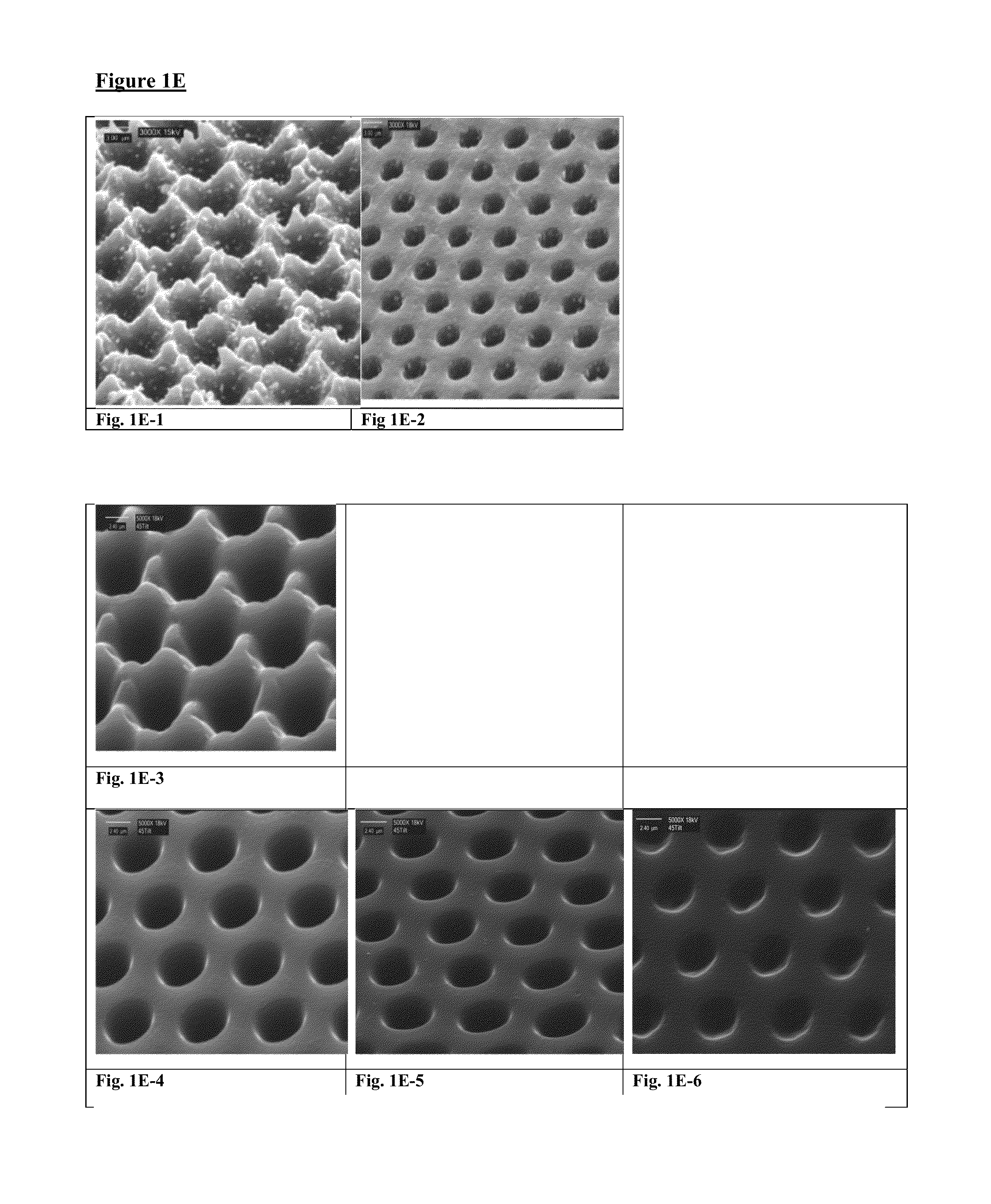

Microcavity carrier with image enhancement for laser ablation

ActiveUS20140261992A1Good release effectGood reproducibilityLamination ancillary operationsLayered product treatmentAnisotropic conductive filmEngineering

A carrier belt for fabricating a device or component such as an anisotropic conductive film. The carrier belt includes a substrate having a sacrificial image enhancing layer. Microcavities are formed in the carrier by laser ablation through the image enhancing layer. After the image enhancement layer is removed, a plurality of conductive particles are distributed into an array of microcavities formed by laser ablation on a surface of a carrier belt and transferred to an adhesive layer. The image enhancing layer enables one to form microcavities with a fine pitch and spacing and partitions having a high aspect ratio.

Owner:POLAROID IP BV

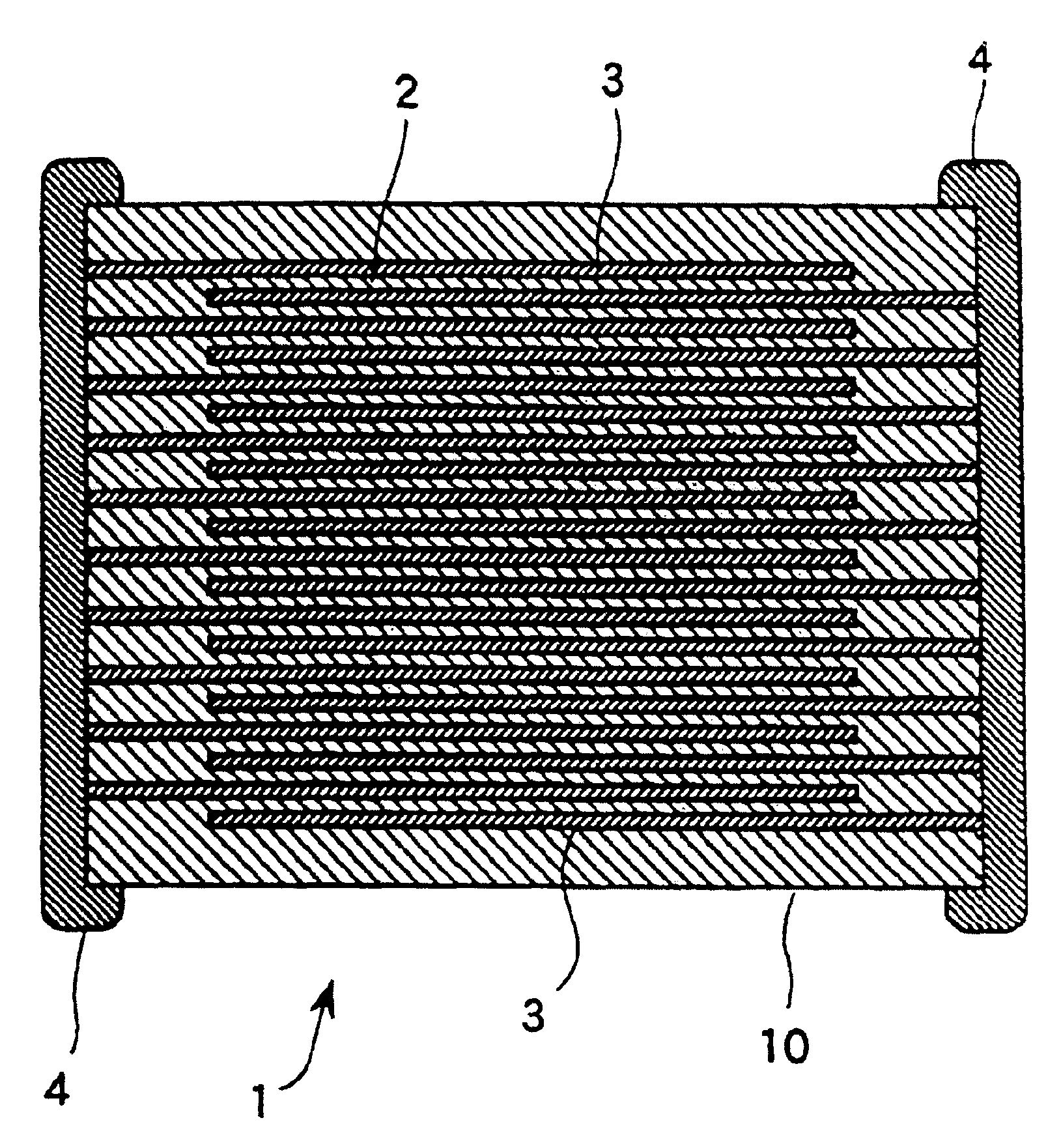

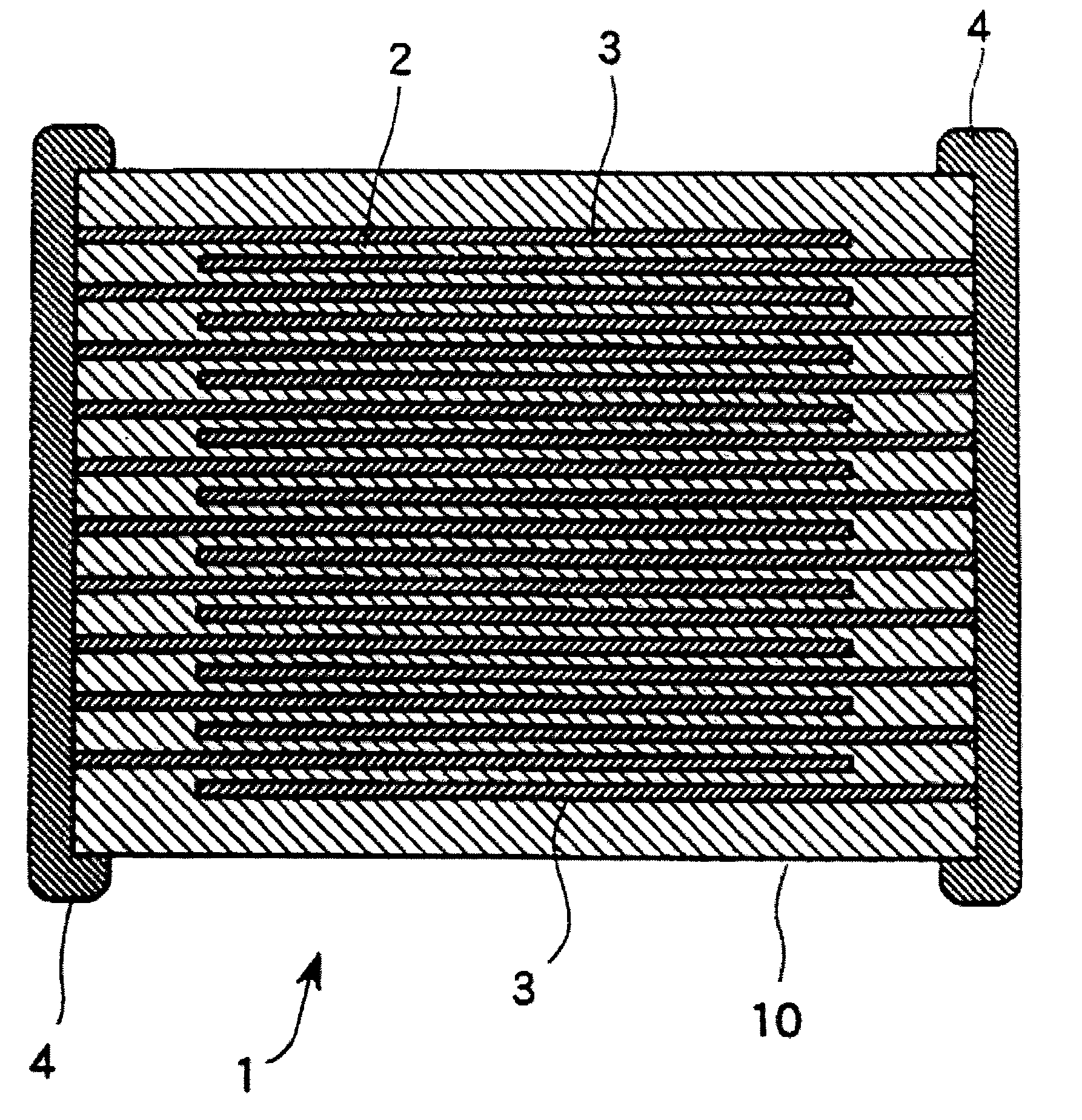

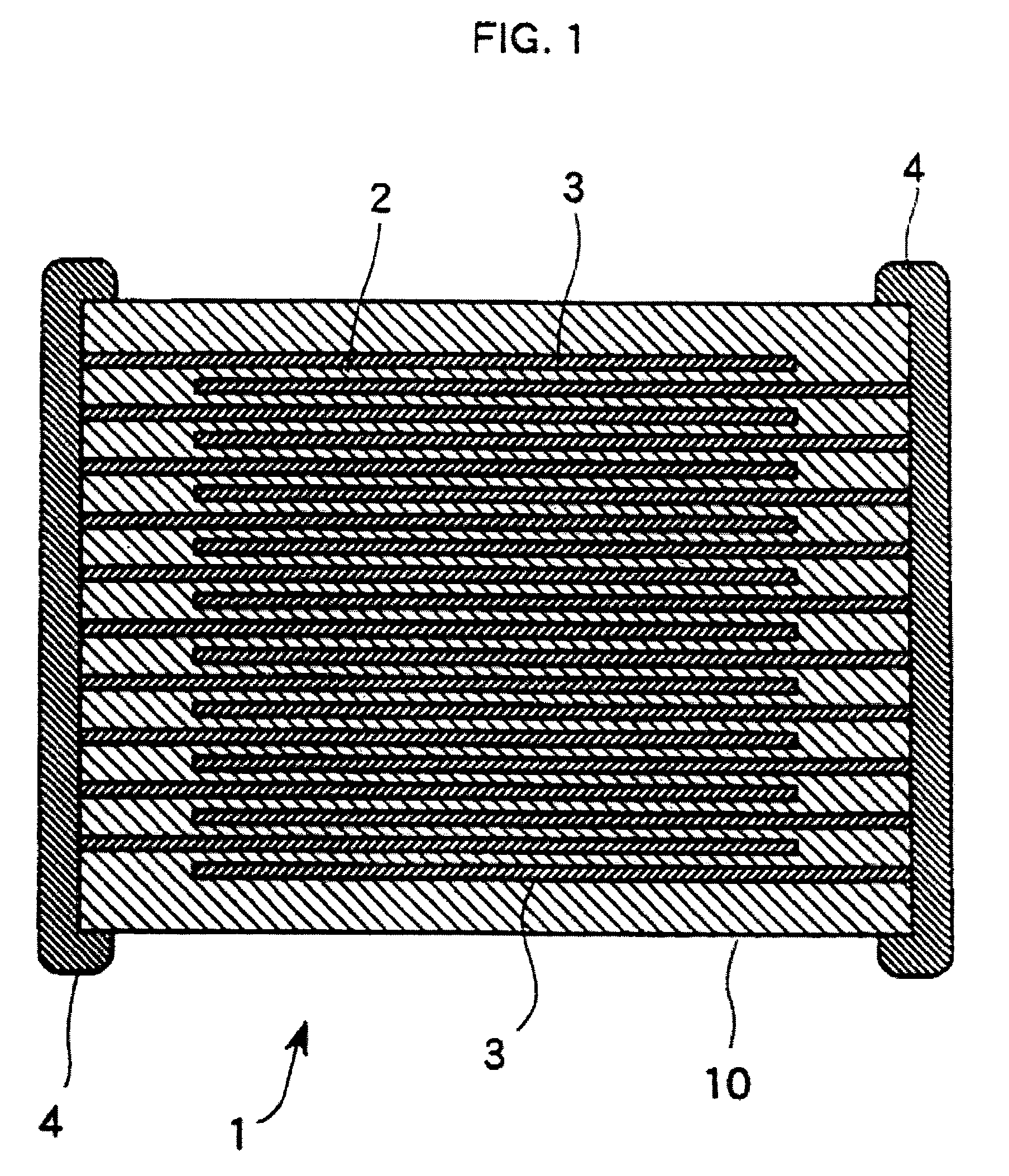

Terminal electrode compositions for multilayer ceramic capacitors

InactiveUS7083744B2Wider process windowAppropriate densityConductive materialNon-conductive material with dispersed conductive materialNitrogen atmosphereCeramic capacitor

The present invention relates to terminal electrode compositions for multilayer ceramic capacitors. More specifically, it relates to terminal electrode compositions for multilayer ceramic capacitors which have a metal oxide component selected from SnO2, V2O5 and MoO3. The compositions can be fired at a low temperature in a nitrogen atmosphere.

Owner:EI DU PONT DE NEMOURS & CO

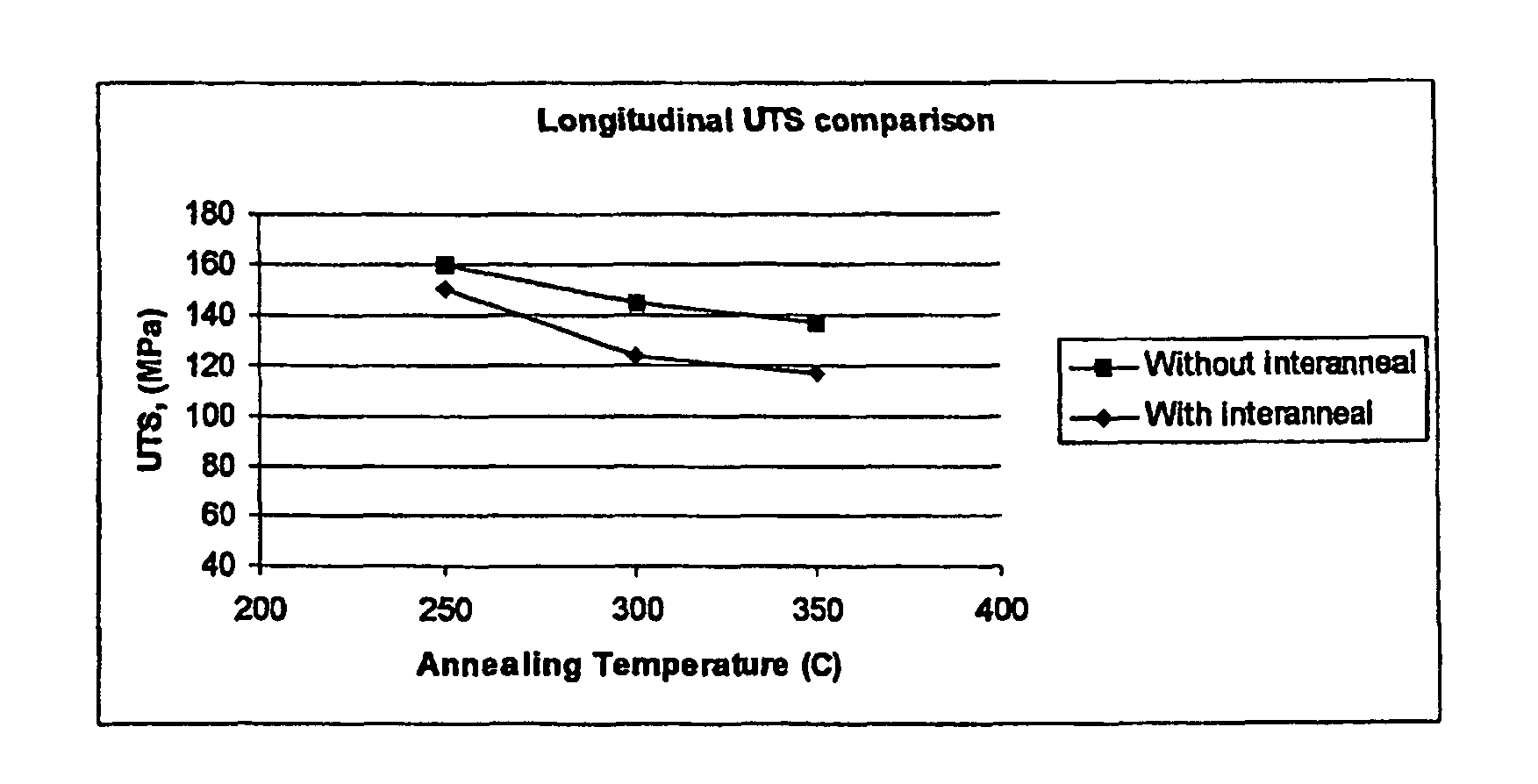

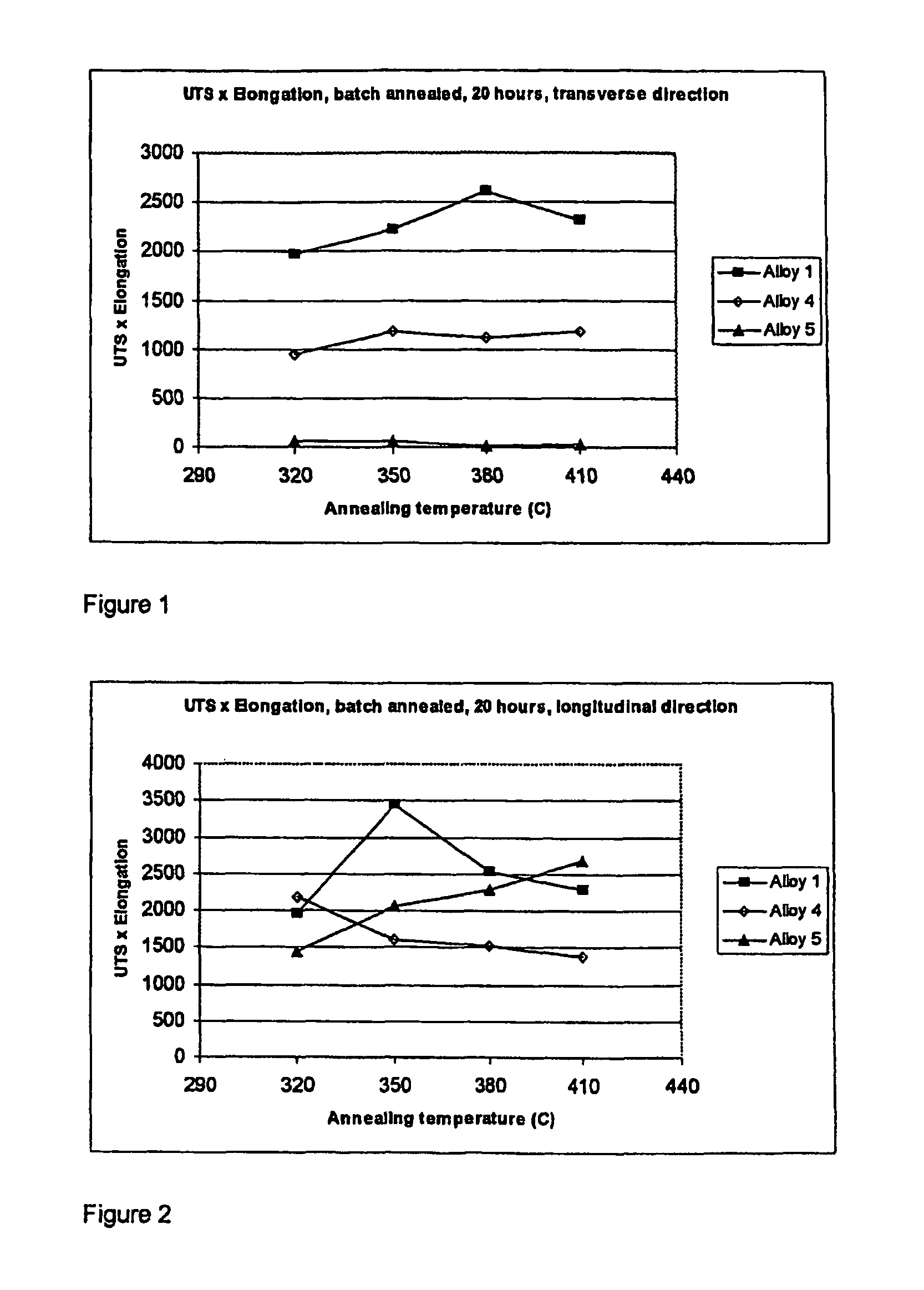

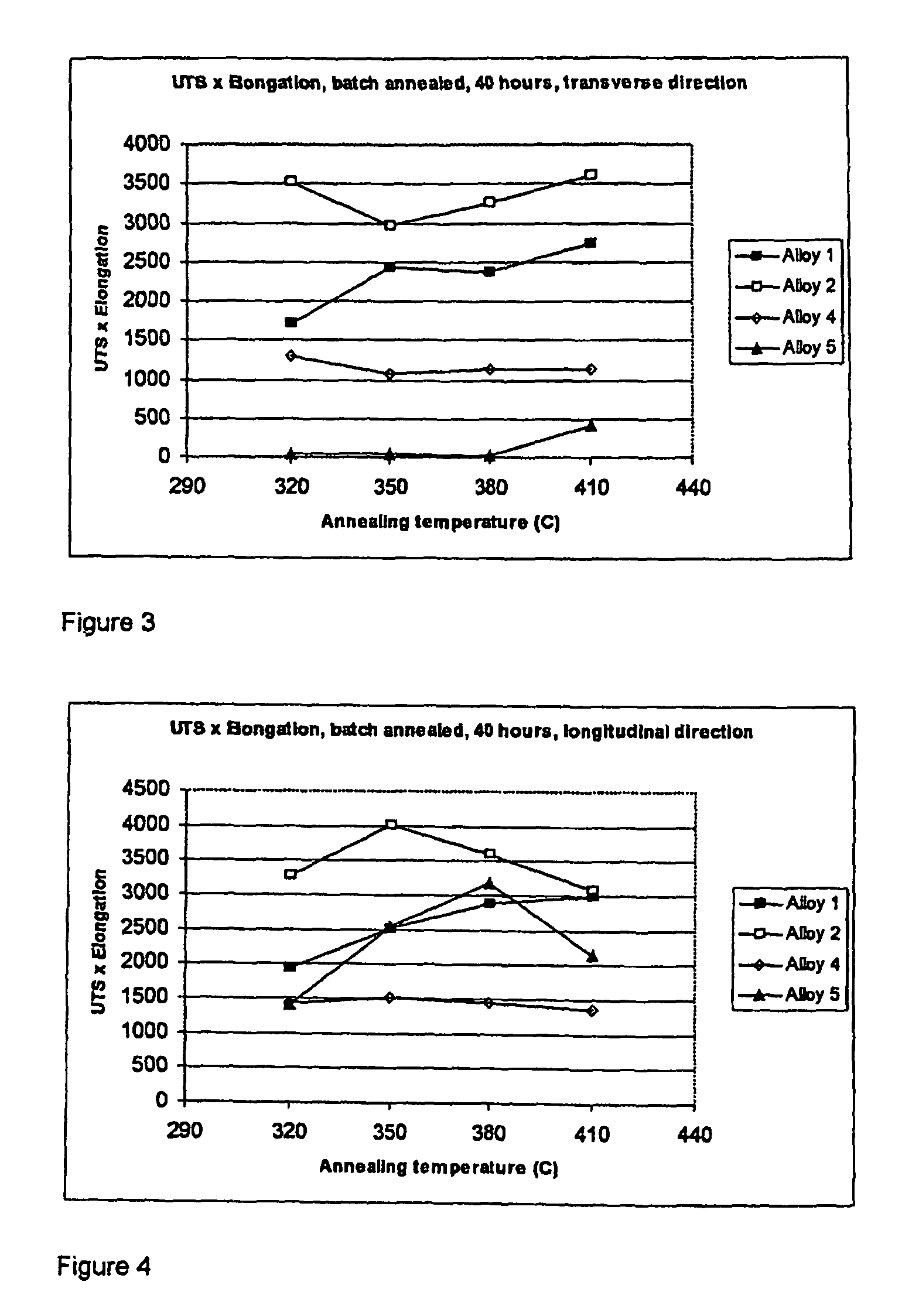

Aluminium foil alloy

The present invention relates to a method of making an aluminum alloy product having a gauge below 200 μm. It also relates to an aluminum alloy product having a gauge below the same value and to containers for food packaging application made from the aluminum alloy product. The invention is process of manufacturing an aluminum alloy comprising the following steps: continuous casting an aluminum alloy melt of the following composition, (in weight %): Fe 1.0-1.8, Si 0.3-0.8, Mn up to 0.25, other elements less than or equal to 0.05 each and less than or equal to 0.15 in total, balance aluminum, cold rolling the cast product without an interanneal step to a gauge below 200 μm and final annealing the cold rolled product.

Owner:EUROFOIL LUXEMBOURG

Film deposition apparatus with low plasma damage and low processing temperature

ActiveUS9303312B2Minimize and eliminate such damageMinimize unwanted and uneven bombardmentElectric discharge tubesVacuum evaporation coatingClosed loopEngineering

Owner:AREESYS TECH

Semiconductor device with raised segment

InactiveUS6872606B2Inexpensively formedSmall thicknessTransistorSolid-state devicesSemiconductor materialsEngineering

A device having a raised segment, and a manufacturing method for same. An SOI wafer is provided having a substrate, an insulating layer disposed over the substrate, and a layer of semiconductor material disposed over the insulating layer. The semiconductor material is patterned to form a mesa structure. The wafer is annealed to form a raised segment on the mesa structure.

Owner:TAIWAN SEMICON MFG CO LTD

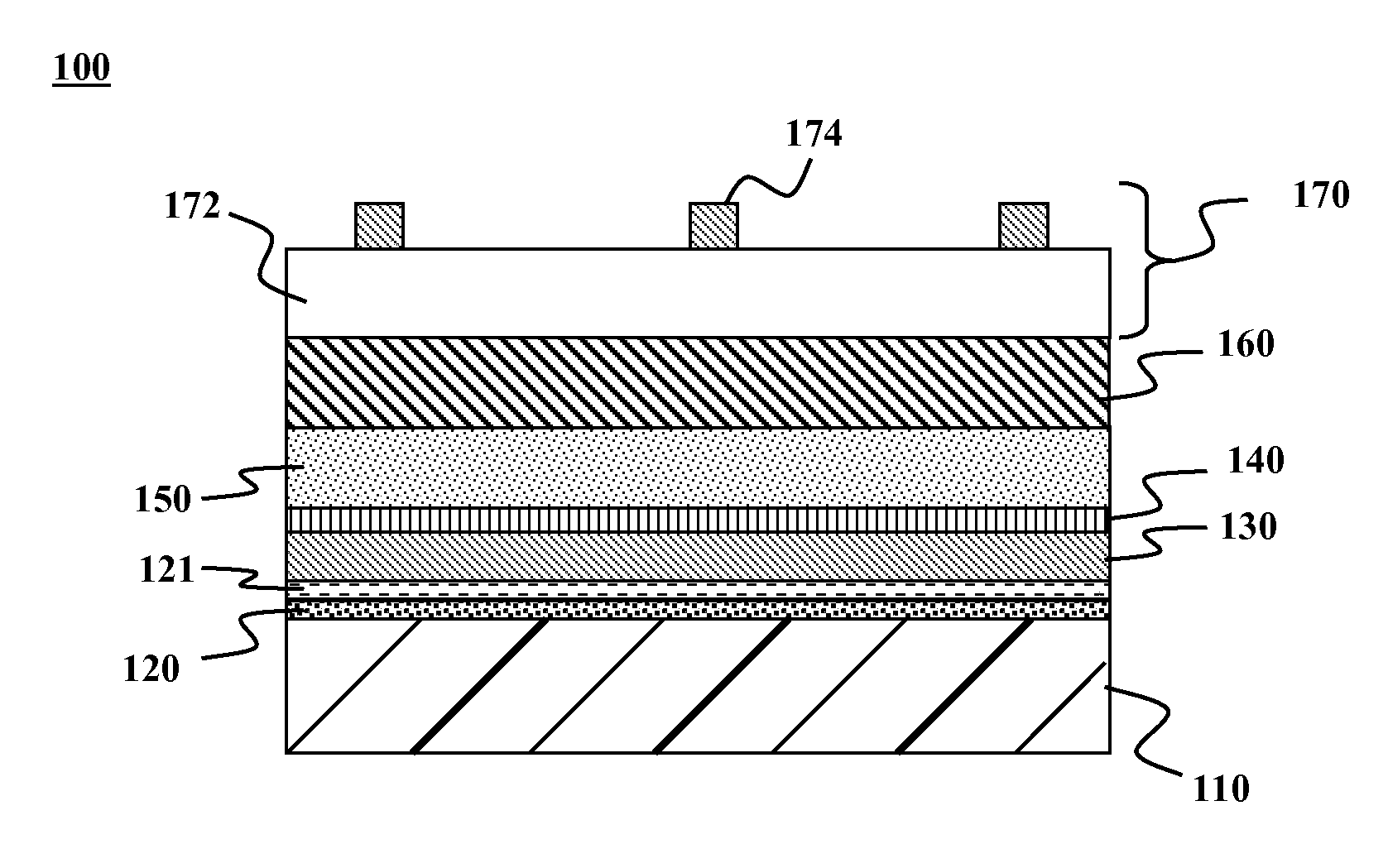

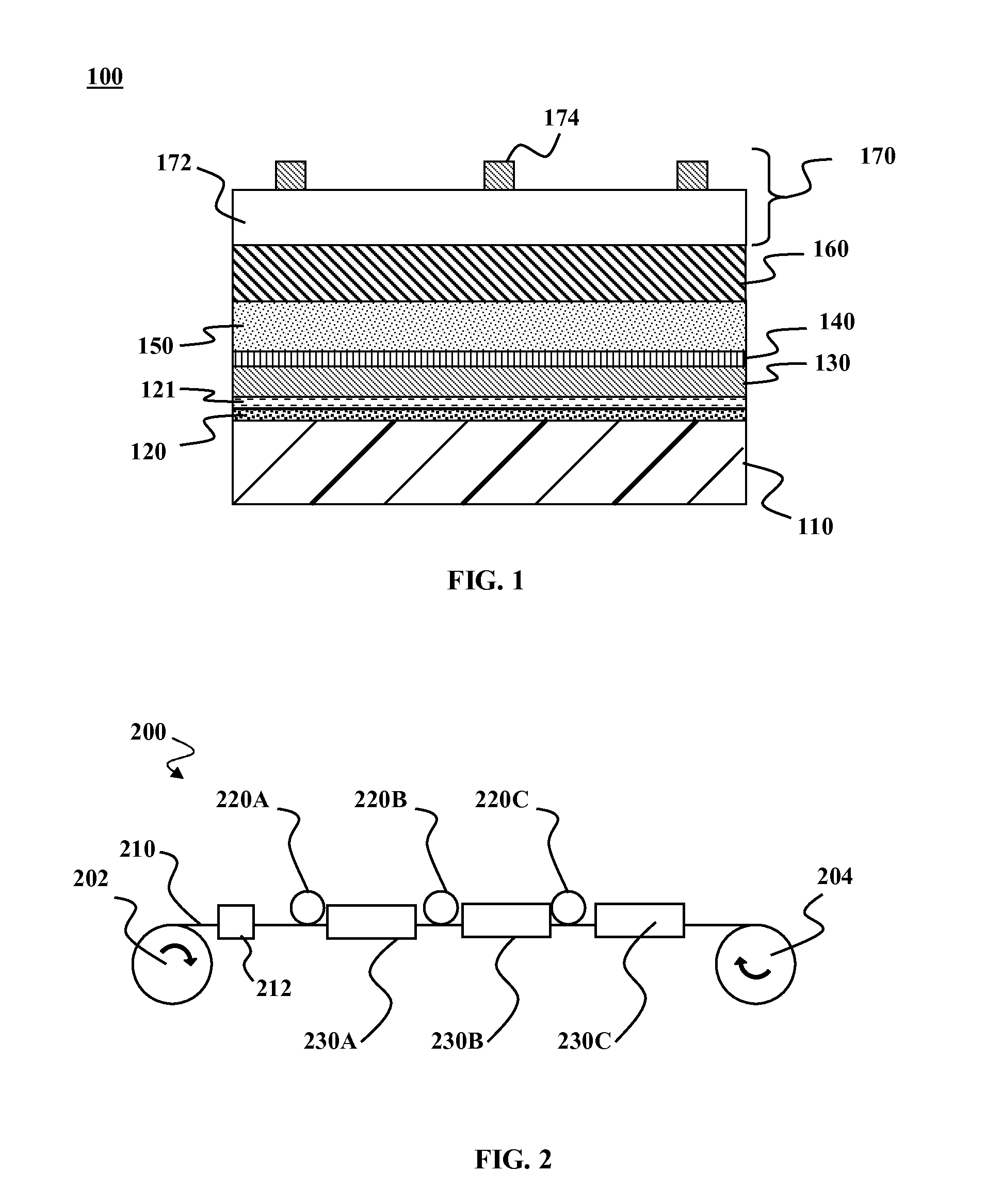

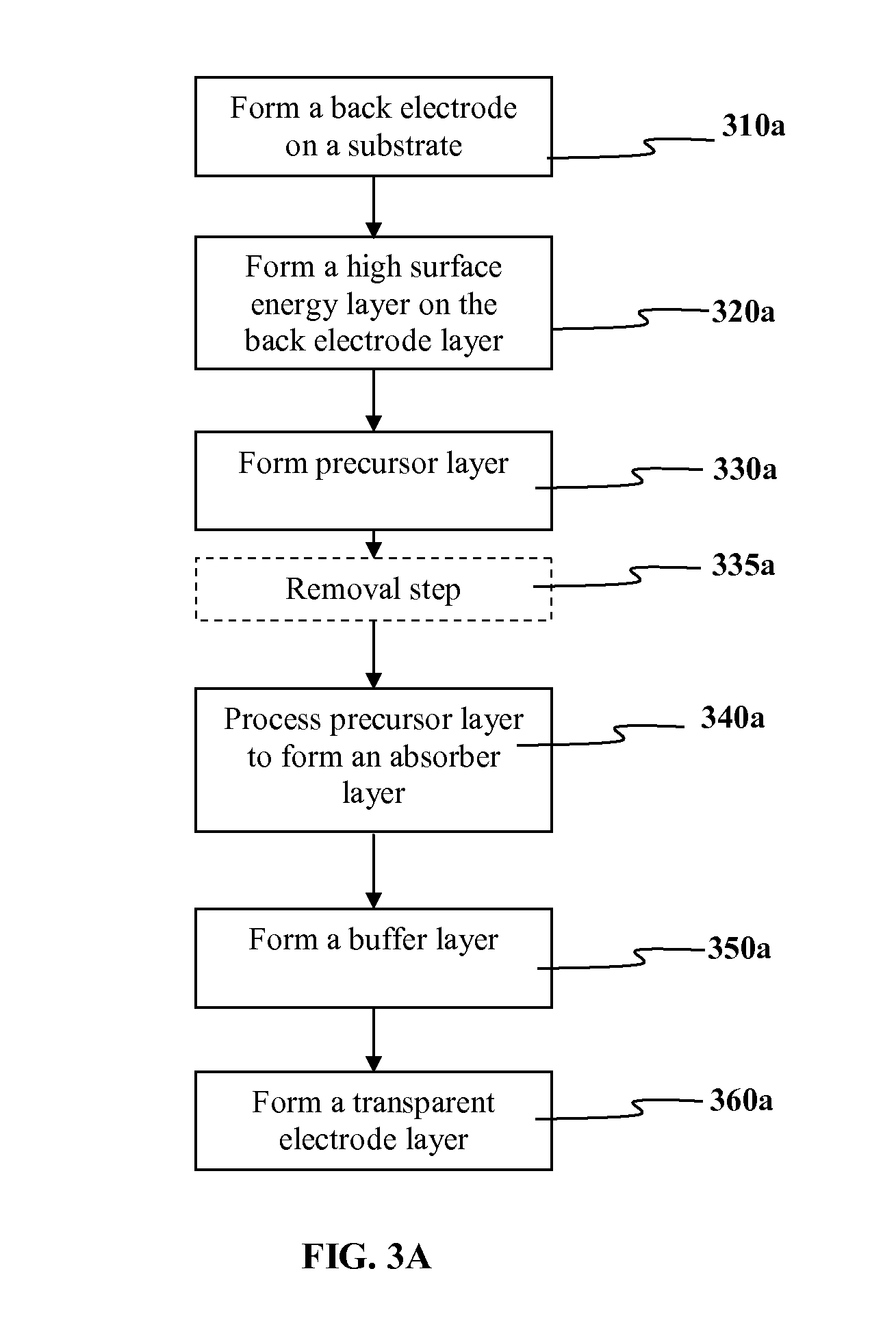

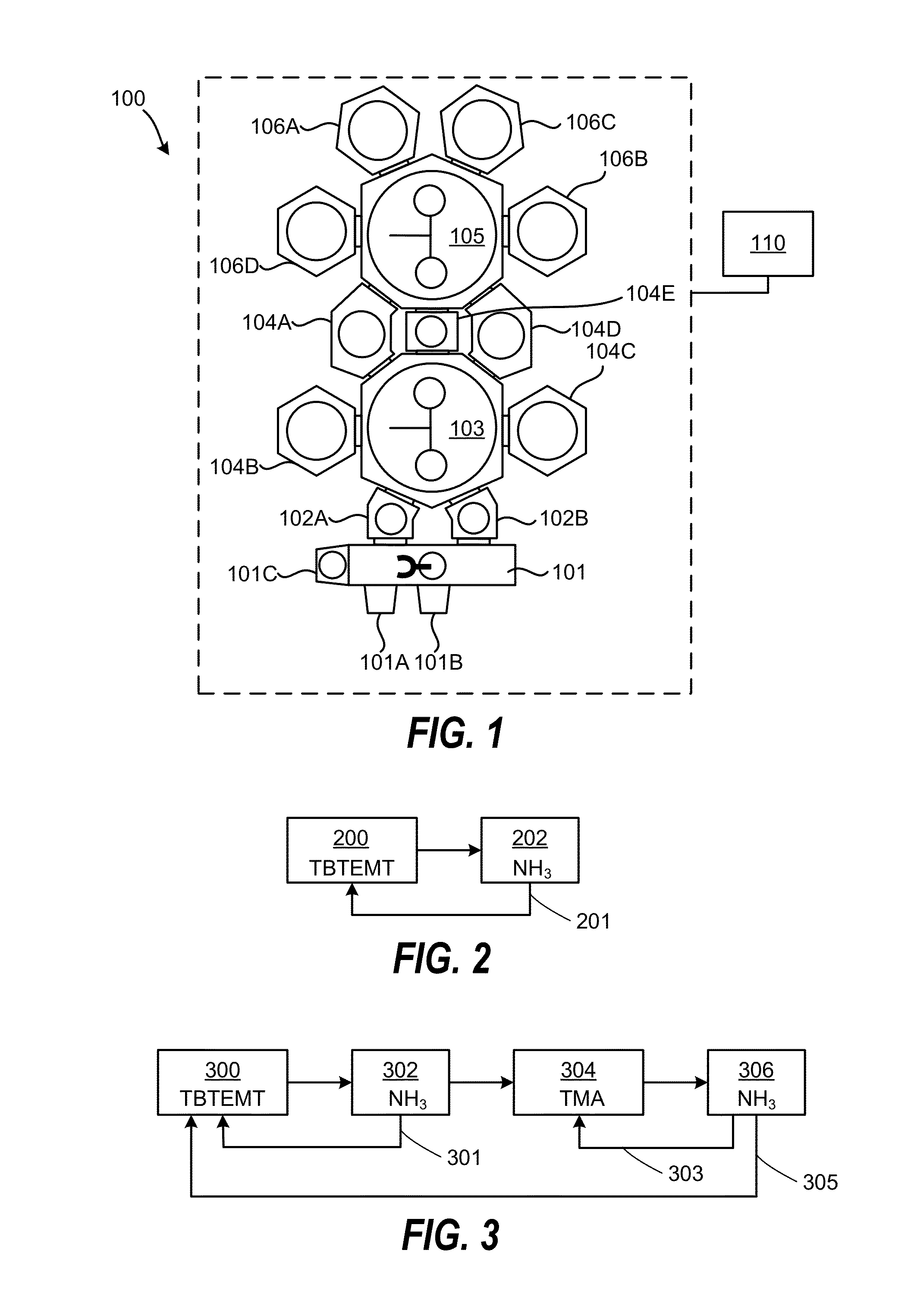

Deposition of a high surface energy thin film layer for improved adhesion of group i-iii-vi2 solar cells

InactiveUS20140224312A1Reduce formationLayer is highSemiconductor/solid-state device manufacturingPhotovoltaic energy generationSemiconductor materialsSubject matter

A thin film photovoltaic cell includes a light absorption layer of Group I-III-VI2 semiconductor materials and a high surface energy thin film layer that improves adhesion between the light absorption layer and an underlying electrode layer. The high surface energy thin film either replaces or is deposited on top of the back electrode to decrease the formation of voids at the back interface during absorber growth / deposition and thereby enabling a wider process window and improved cell efficiencies. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:AERIS CAPITAL SUSTAINABLE IP

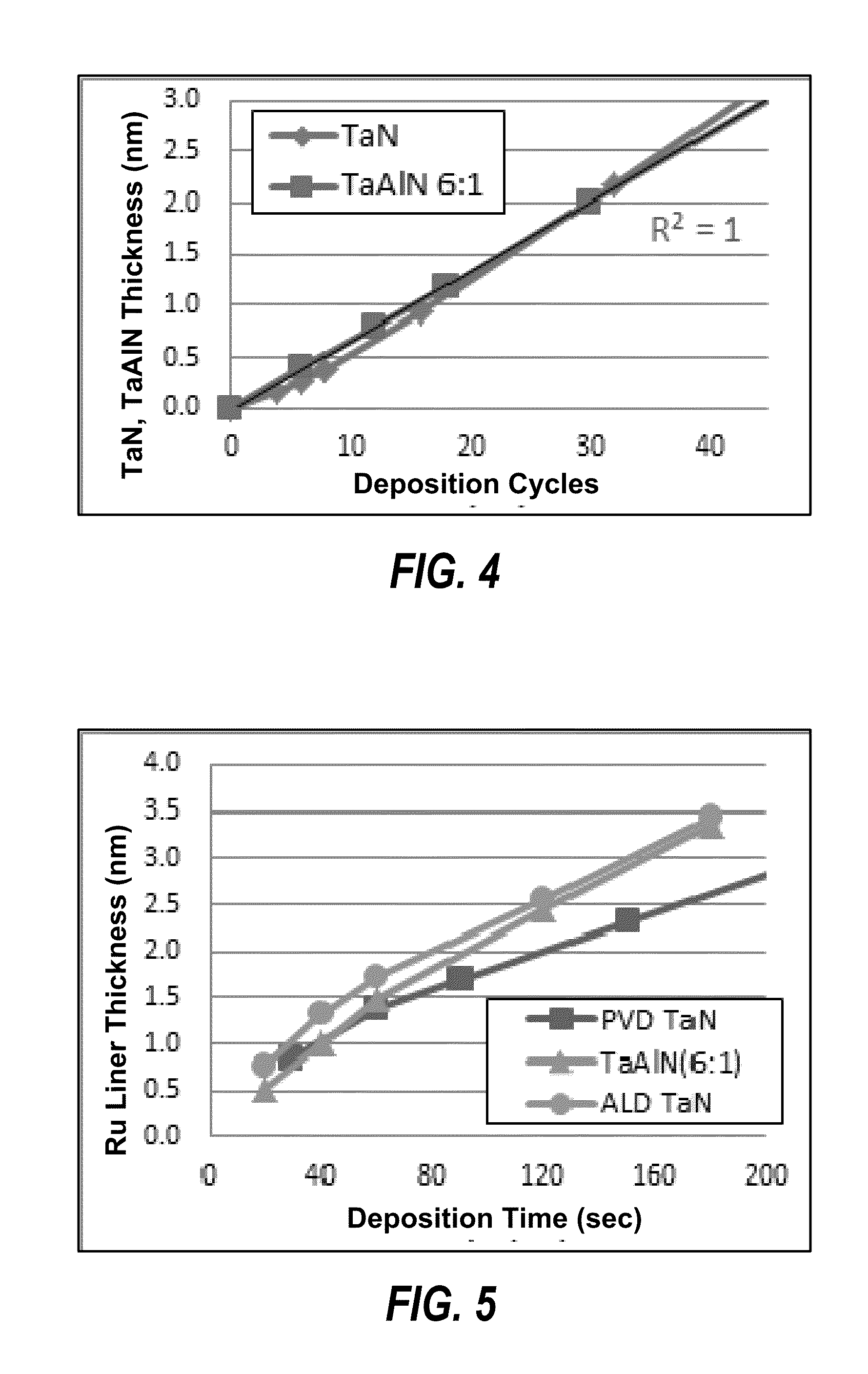

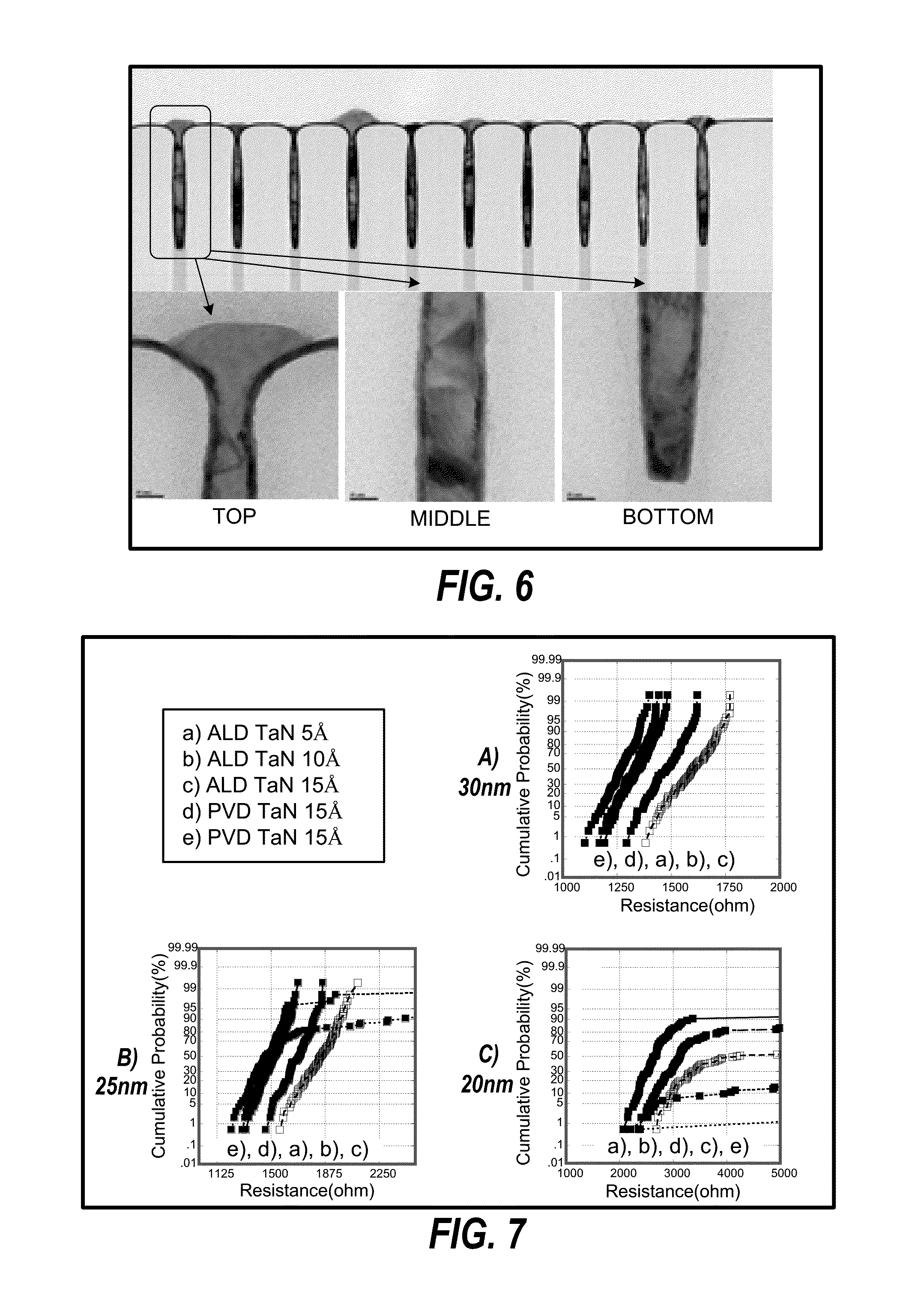

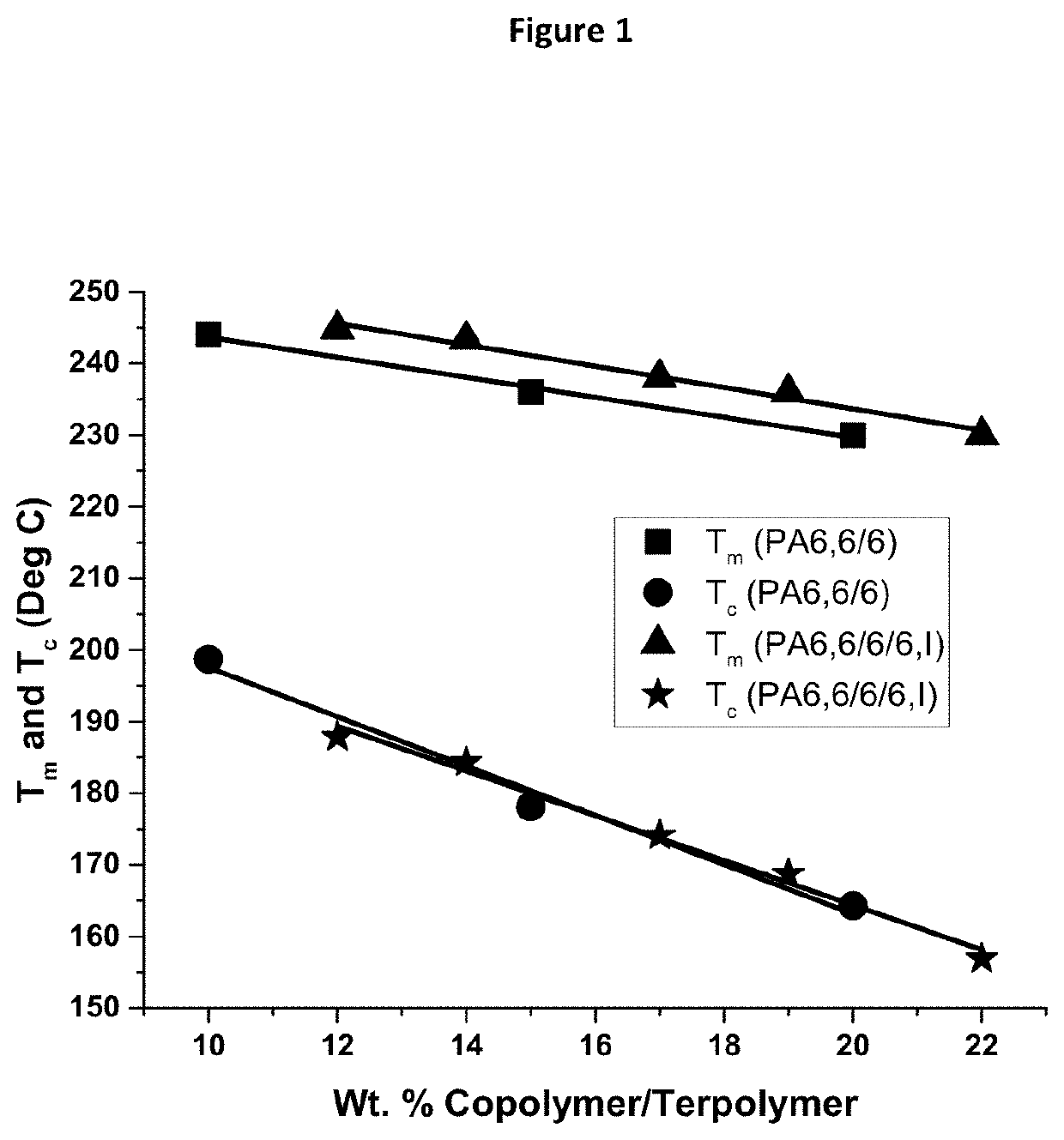

INTEGRATION OF ALD BARRIER LAYER AND CVD Ru LINER FOR VOID-FREE Cu FILLING

ActiveUS20150221550A1Superior metal fillingWide design flexibilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringCopper

Methods for integration of atomic layer deposition (ALD) of barrier layers and chemical vapor deposition (CVD) of Ru liners for Cu filling of narrow recessed features for semiconductor devices are disclosed in several embodiments. According to one embodiment, the method includes providing a substrate containing a recessed feature, depositing a conformal barrier layer by ALD in the recessed feature, where the barrier layer contains TaN or TaAlN, depositing a conformal Ru liner by CVD on the barrier layer, and filling the recessed feature with Cu metal.

Owner:TOKYO ELECTRON LTD

Propylene homopolymers for biaxially oriented films

ActiveUS7056592B2Easy to processWider process windowSynthetic resin layered productsDomestic articlesEthylene HomopolymersPolymer chemistry

Propylene homopolymers useful in the manufacture of biaxially oriented films are provided. More particularly, the propylene homopolymers of the present invention are useful as core material for a multilayer biaxially oriented film. The propylene homopolymers of the present invention attain these properties by control of the average meso sequence length, Nm, in the xylene insoluble phase of the polymer concurrently with control of the quantity of xylene solubles in the polymer as a whole. The propylene homopolymers according to the current invention comprise from about 97 to about 91 percent by weight of a xylene insoluble fraction, and from about 9 to about 3 percent by weight of a xylene soluble fraction. The xylene insoluble fraction has a meso run length of less than or equal to 130. Further, the ratio, r, of the meso run length of the xylene insoluble fraction to the percent content of the xylene soluble fraction in the propylene homopolymers is 22 or less, as determined by the equation:Nm / % XS=r where: Nm=average meso sequence length of the xylene insoluble fraction; and% XS=the percent content of xylene solubles in the propylene homopolymer.

Owner:BRASKEM AMERICA

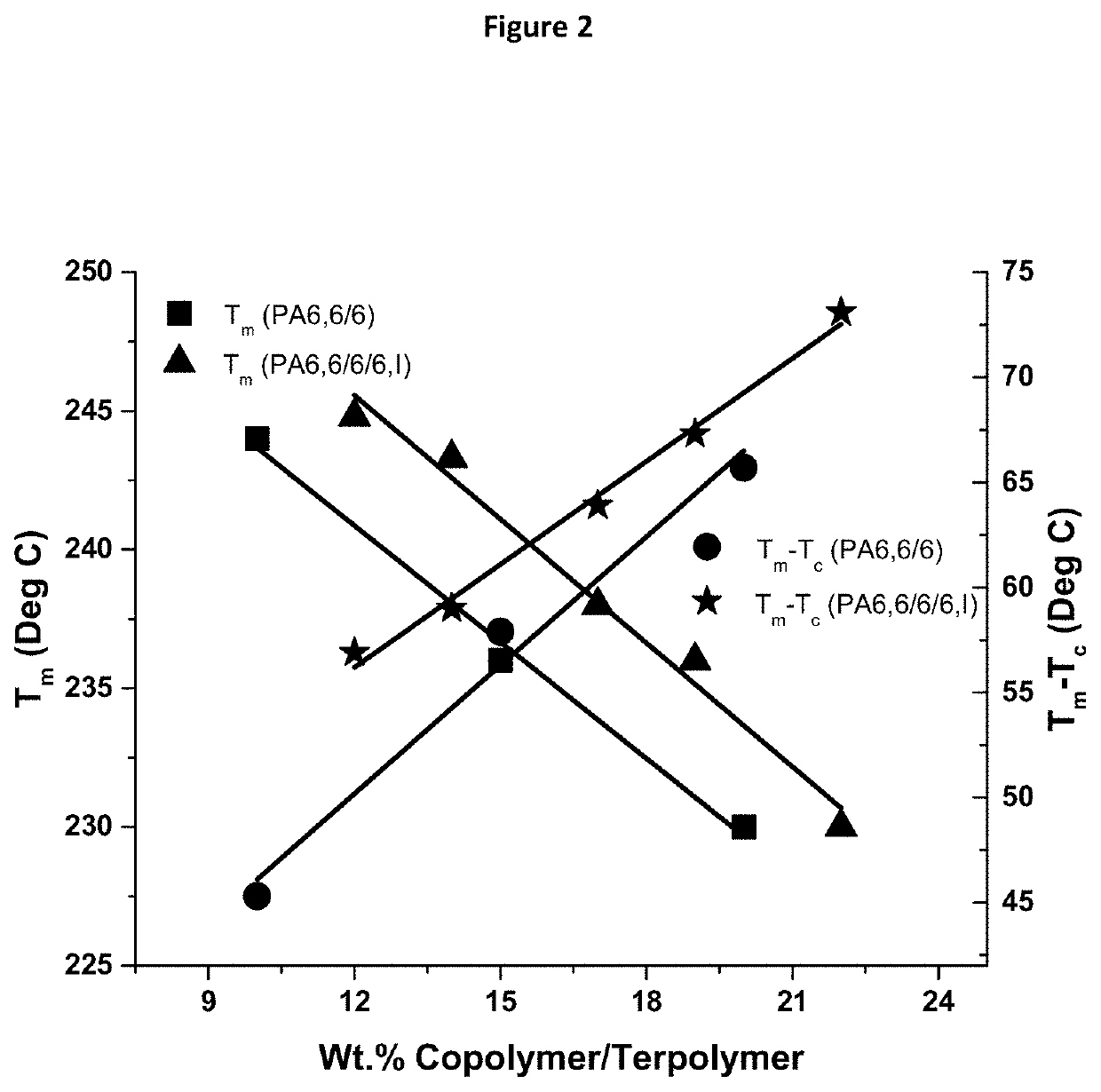

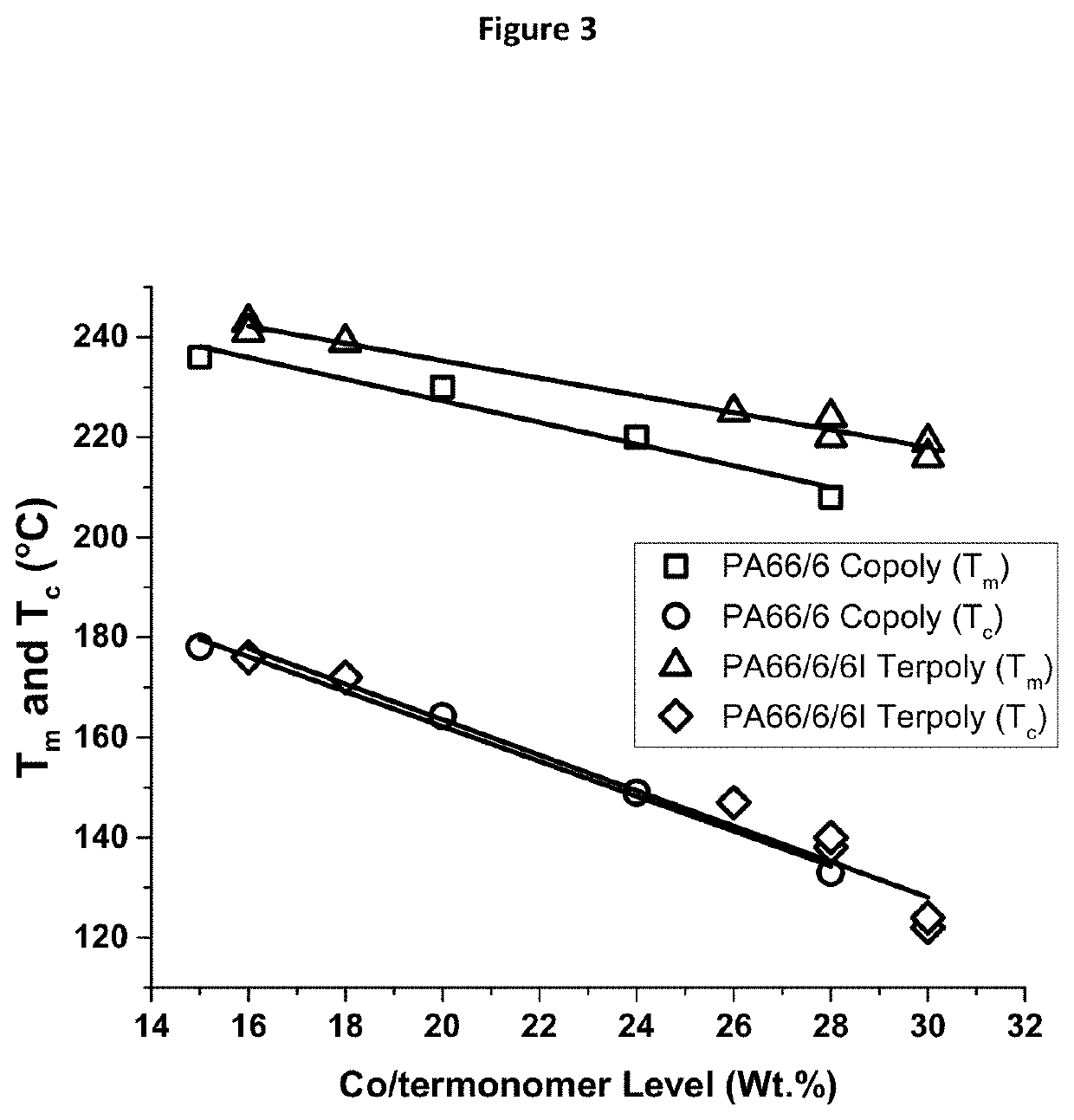

Nylon Terpolymers

ActiveUS20200032057A1High melting pointLow moisture absorptionSynthetic resin layered productsDomestic containersComposite materialPolymer chemistry

A terpolymer composition is described that contains a statistical amount of 50-98 wt % of a first repeating AA-BB comonomer unit; 1-25 wt % of a second repeating AA-BB comonomer unit; and 1-25 wt % of a repeating lactam comonomer unit or 1-25 wt % of a third repeating AA-BB comonomer unit, where the terpolymer composition exhibits a high melting point similar to that of PA66 while also exhibiting a significantly reduced crystallization rate and crystallization temperature.

Owner:ASCEND PERFORMANCE MATERIALS OPERATIONS

Resin composition for forming fine pattern and method for forming fine pattern

ActiveUS8715901B2Applicability to resistResist controllabilityPhotosensitive materialsSemiconductor/solid-state device manufacturingResistAlcohol

A resin composition which, in forming a fine pattern by a heat treatment of a resist pattern formed by using a photoresist, can be applied onto the resist pattern, can cause the resist pattern to smoothly shrink by heat treatment, and can be easily washed away by a treatment with an alkaline aqueous solution, and a method for efficiently forming a fine resist pattern using the resin composition are provided. The resin composition comprises a resin containing a hydroxyl group, a crosslinking component, and an alcohol solvent containing water in an amount of 10 wt % or less for the total solvent, wherein the alcohol in the alcohol solvent is a monovalent alcohol having 1 to 8 carbon atoms.

Owner:JSR CORPORATIOON

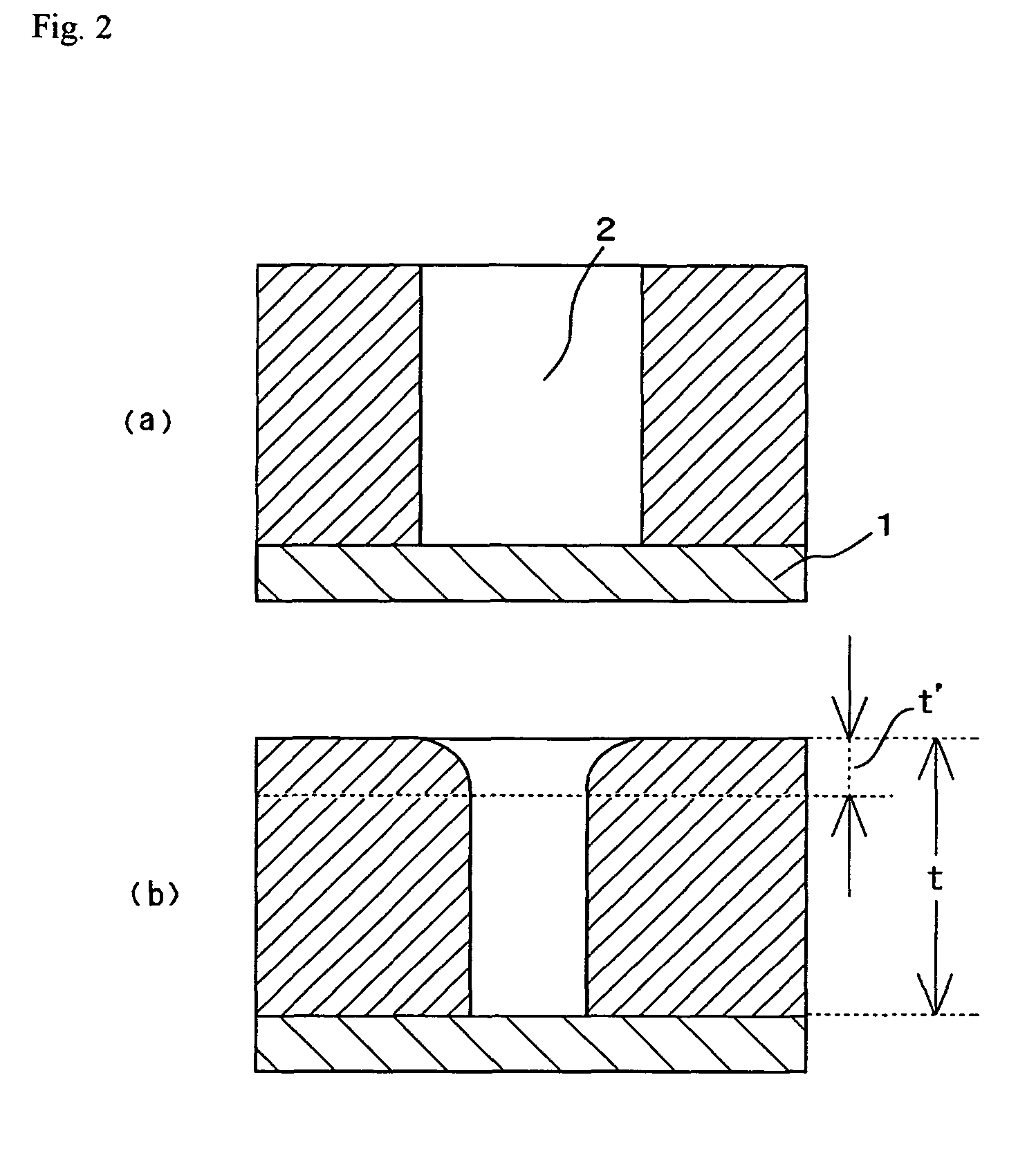

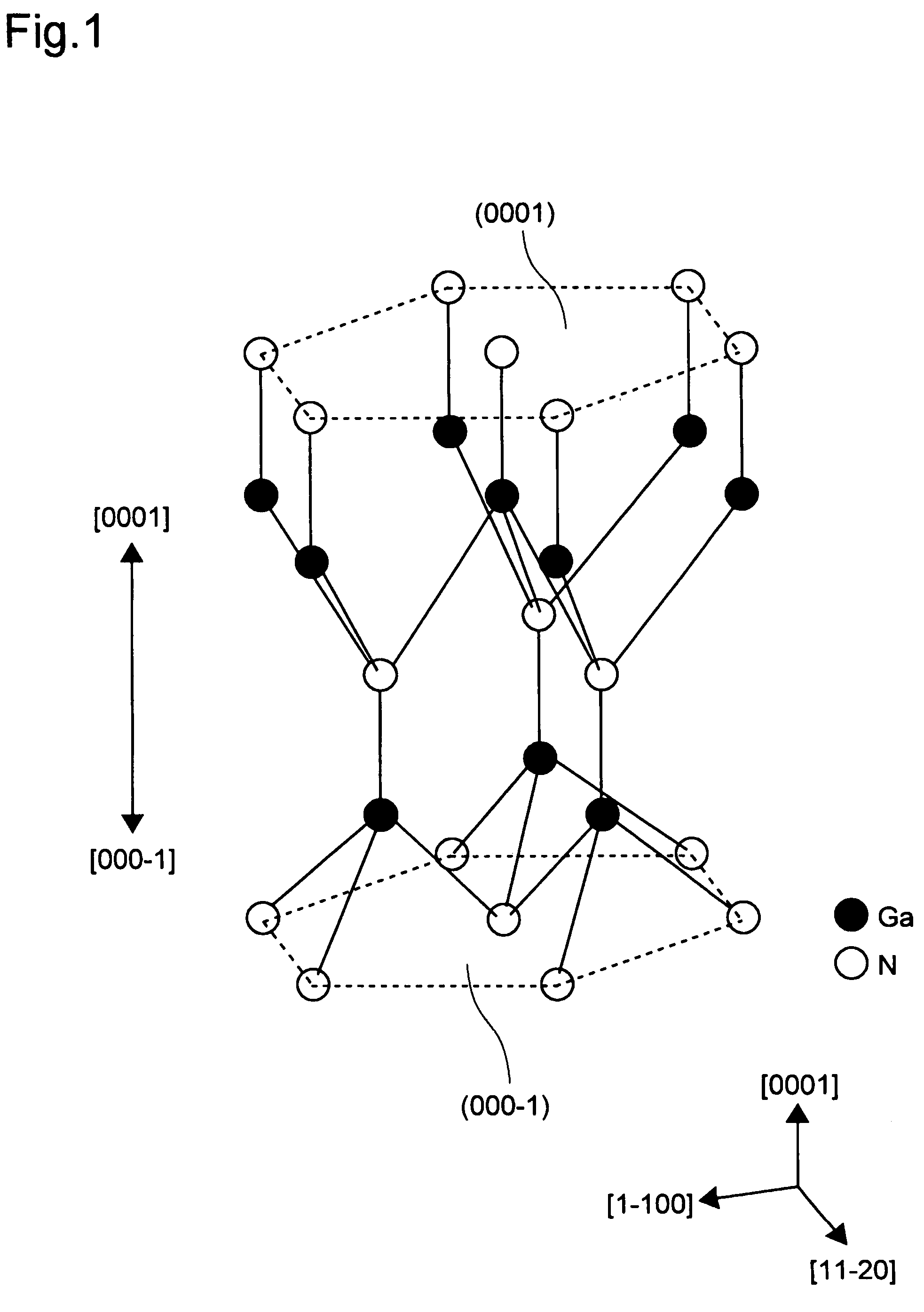

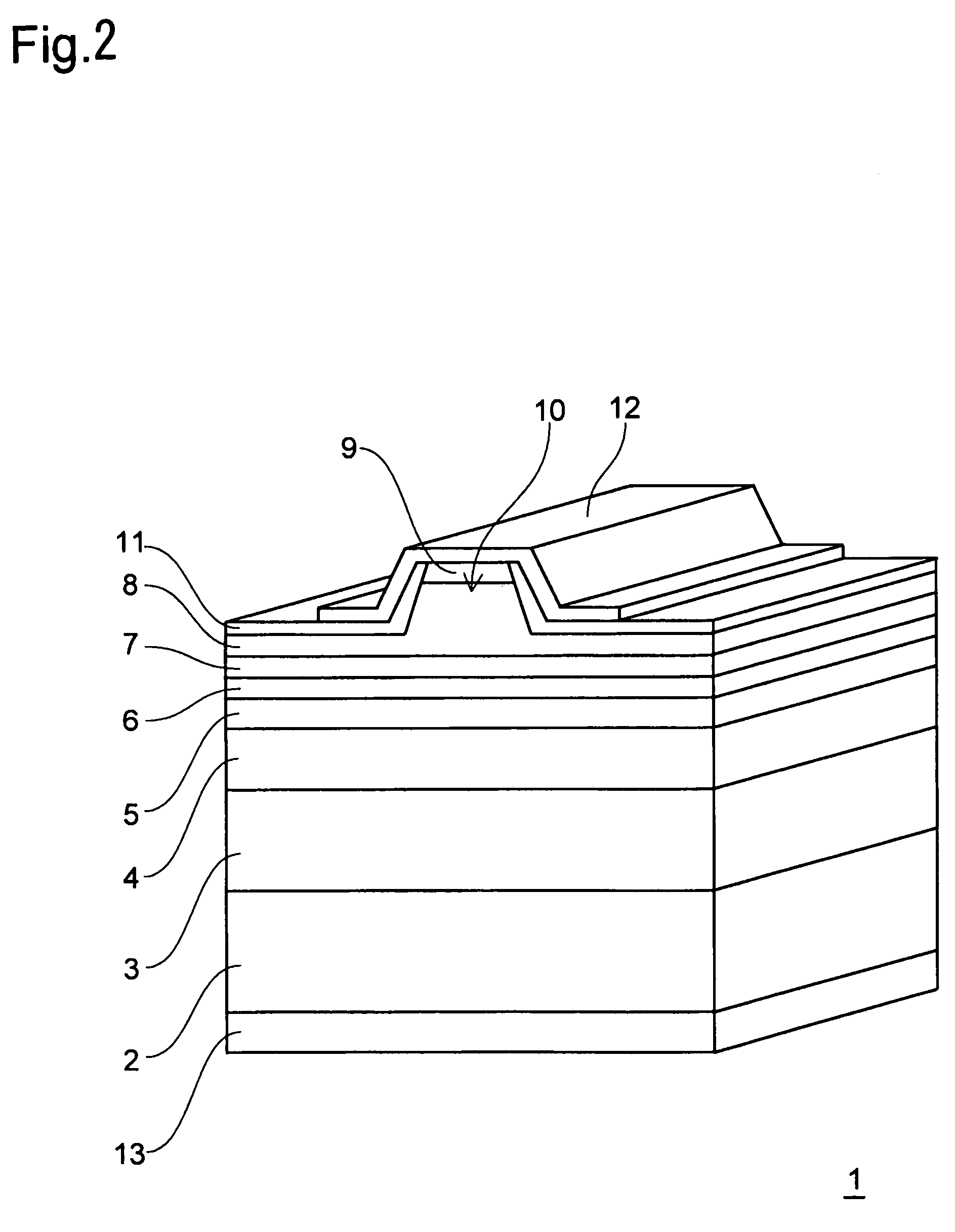

Light emitting element and manufacturing method thereof

InactiveUS7928460B2Increase productionImprove responseOptical wave guidanceLaser detailsCrystal structureFaceting

In a laser chip 1 using a nitride semiconductor having a hexagonal crystal structure, the −c plane is used as a first resonator facet A, which is the side of the laser chip 1 through which light is emitted. On the first resonator facet A, that is, on the −c plane, a facet protection film 14 is formed. This ensures firm joint between the first resonator facet A and the facet protection film 14 and alleviates deterioration of the first resonator facet A.

Owner:SHARP FUKUYAMA LASER CO LTD

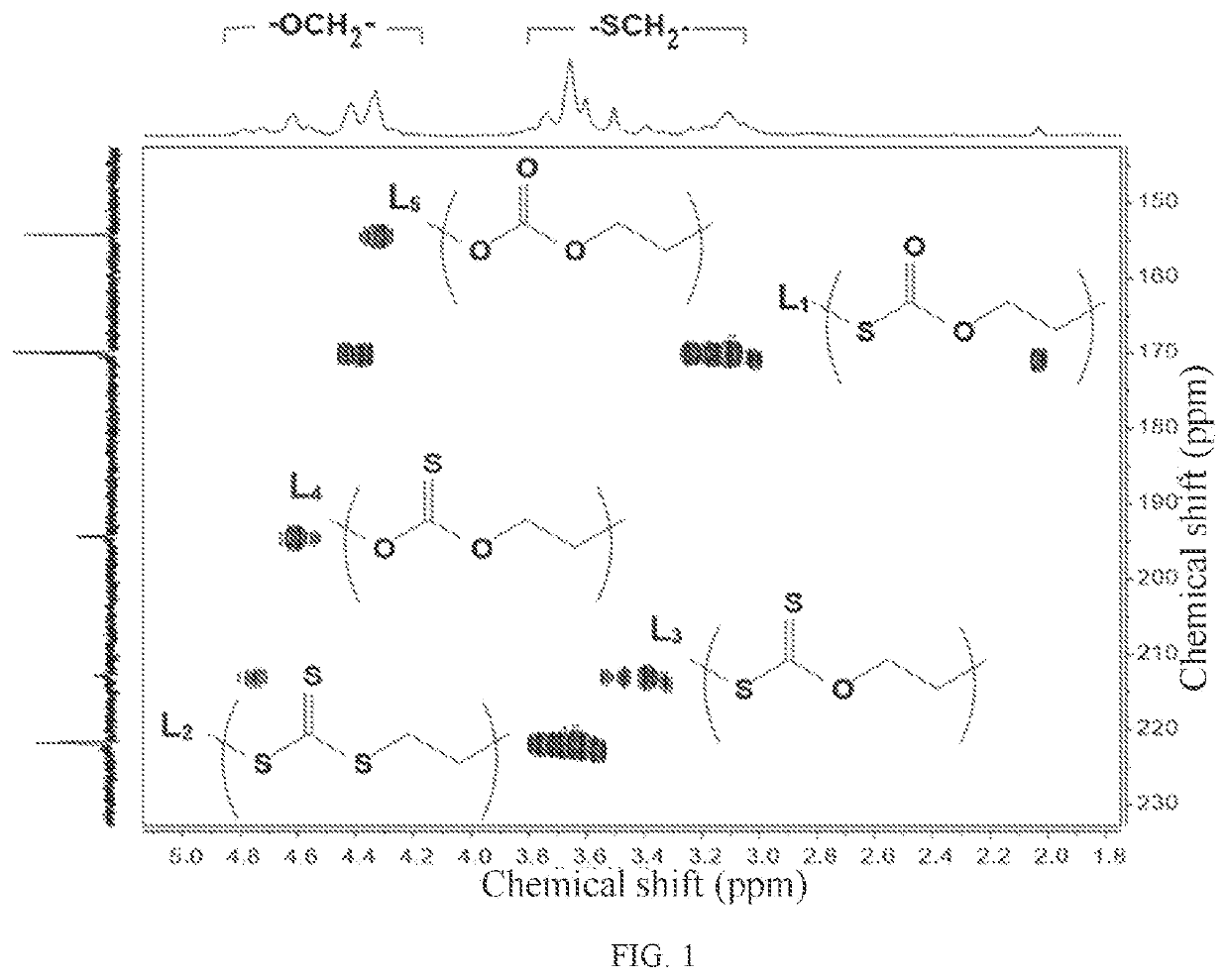

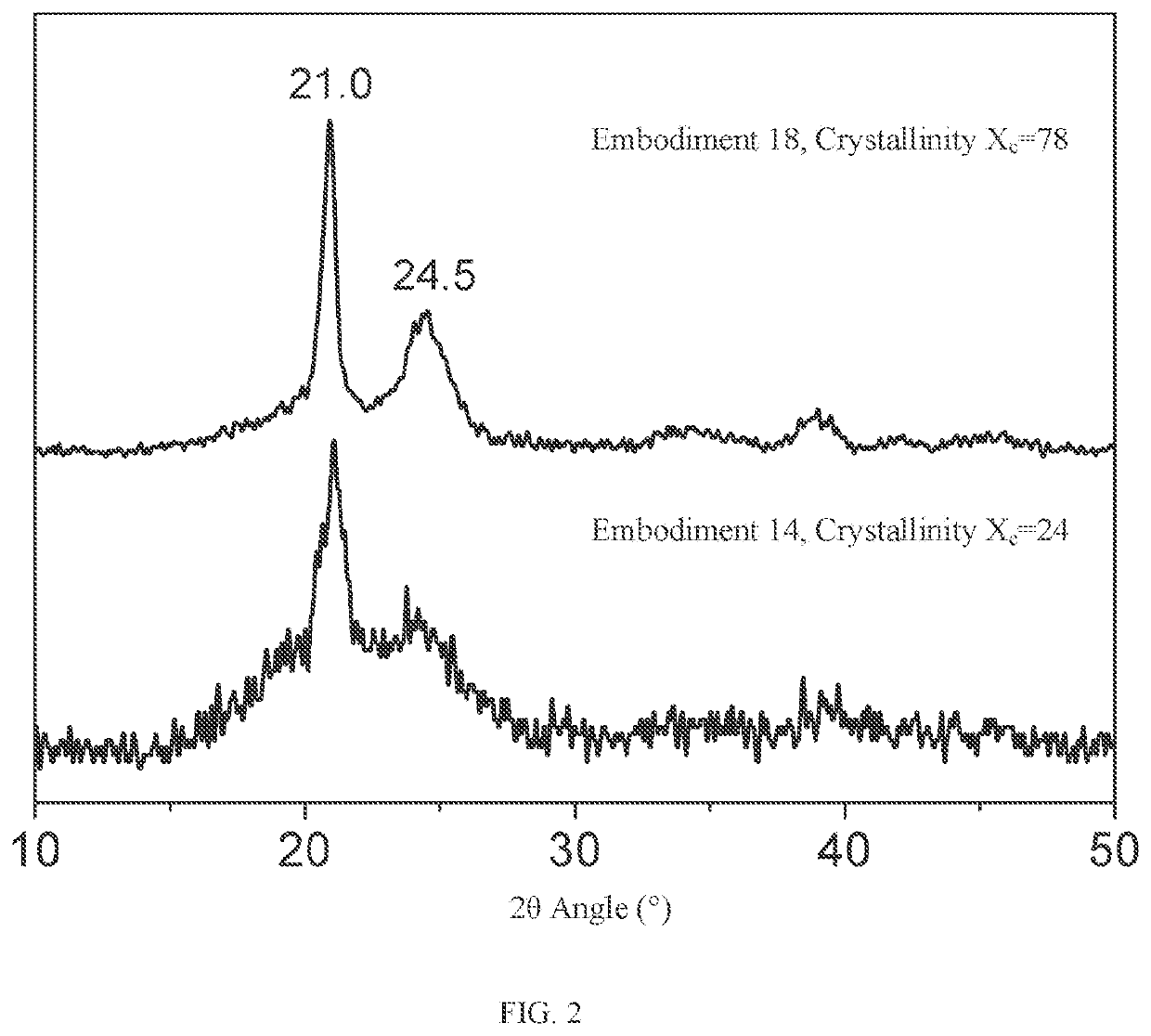

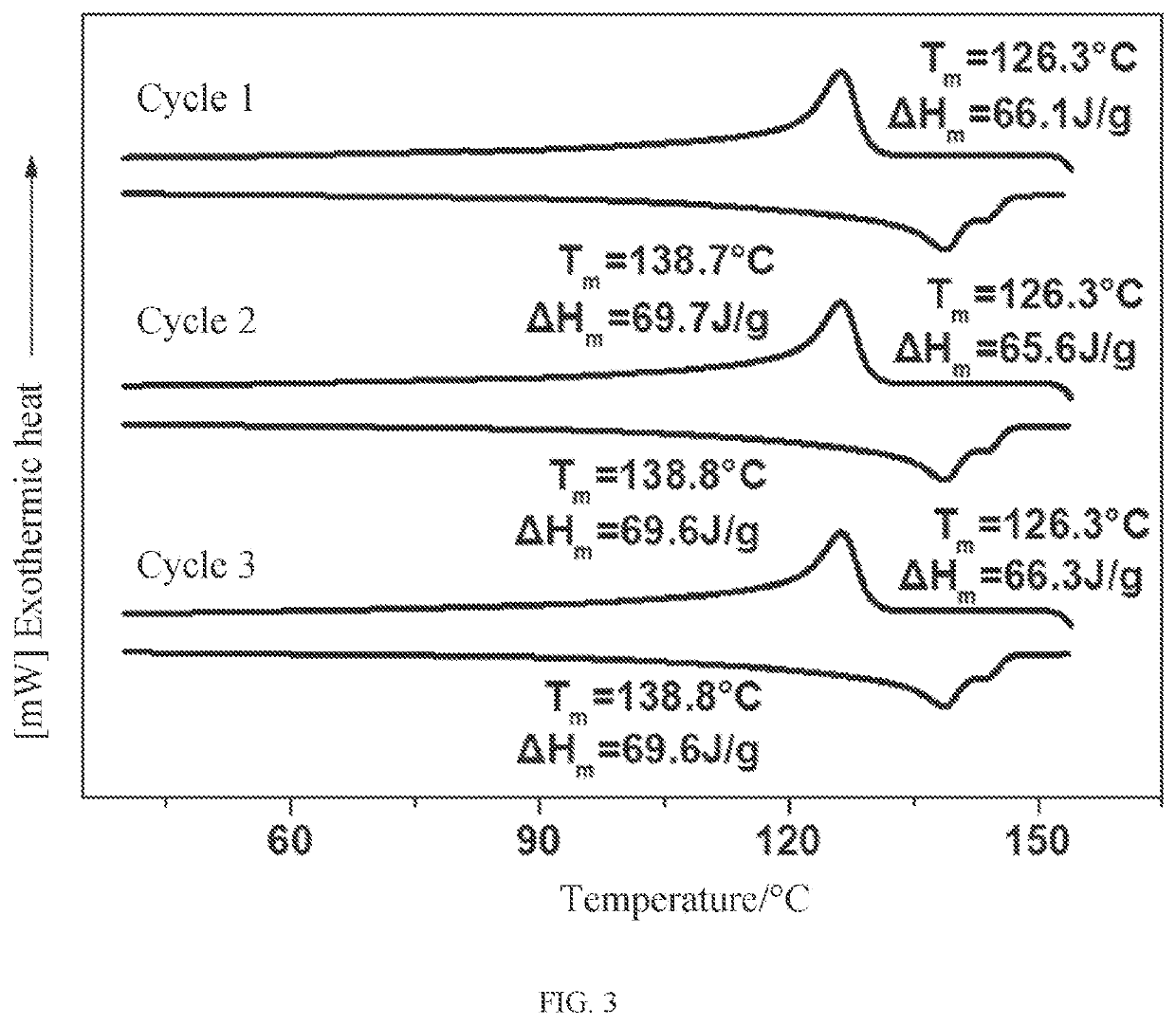

Crystalline polythiocarbonate and preparation method therefor

The present disclosure provides a crystalline polythiocarbonate and a preparation method thereof. The crystalline polythiocarbonate is a random copolymer and includes five structural units L1 to L5 as shown in the following formula. The method includes carrying out a polymerization reaction natively or in solution using carbon disulfide, ethylene oxide, selectively added third monomer, initiator, Lewis acid, selectively added chain transfer agent, and selectively added solvent as raw materials. This method provides a new way for high value-added application of carbon disulfide and ethylene oxide by using inexpensive carbon disulfide and ethylene oxide as monomers; the product is a random copolymerized crystalline polythiocarbonate with novel structure, which has various chain link structures and excellent mechanical properties, processing properties and degradability.

Owner:ZHEJIANG UNIV