Patents

Literature

46results about How to "Coupling capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Touch device and touch display panel

InactiveUS20100149116A1Reduce couple capacitanceIncrease intensityStatic indicating devicesNon-linear opticsElectrical and Electronics engineeringElectrode

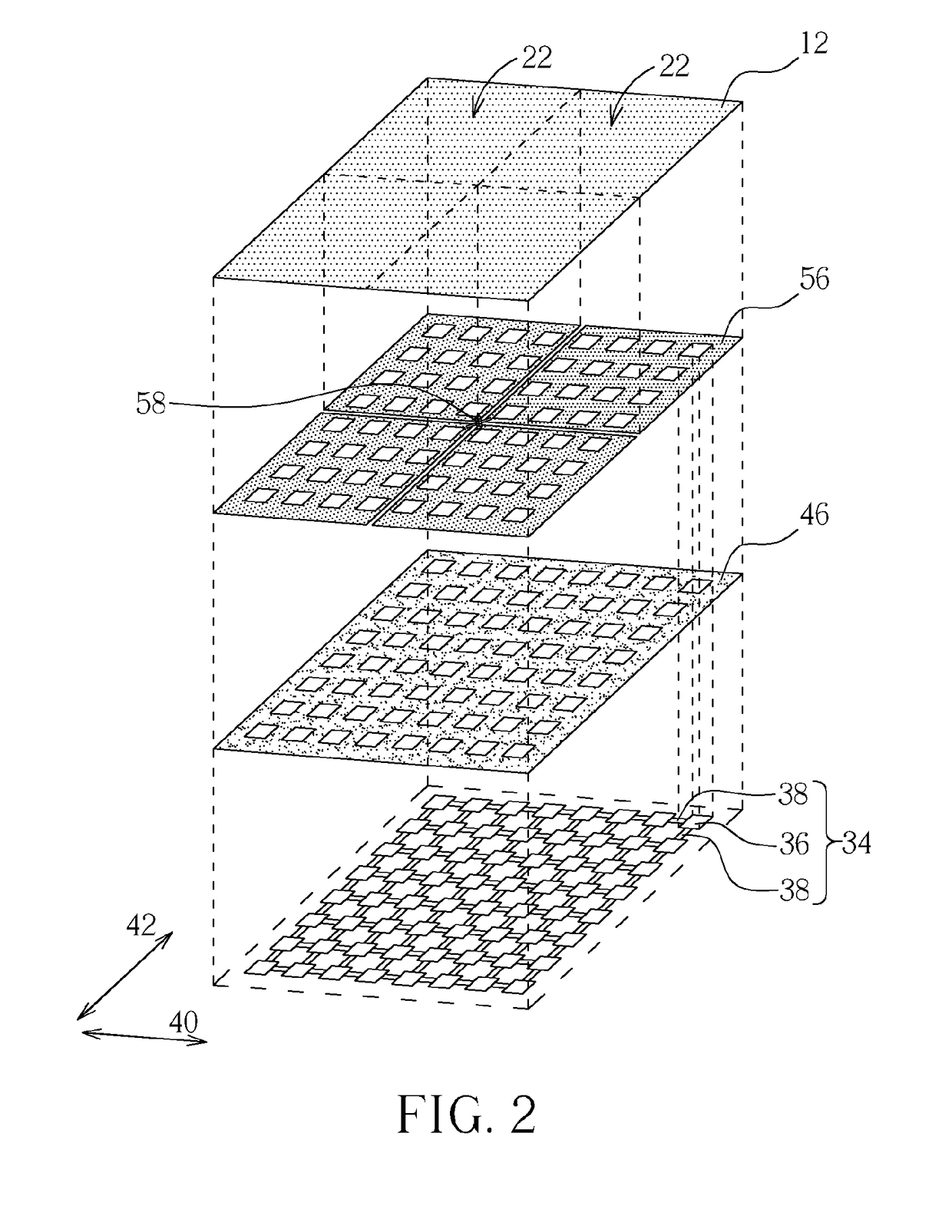

A touch device includes a patterned sensing electrode structure, an insulating layer and a patterned common electrode layer. The patterned sensing electrode structure is disposed on a surface of a substrate, defining a plurality of displaying regions and a light-shielding region. The patterned sensing electrode structure corresponds to the light-shielding region, and exposes the displaying regions. The insulating layer covers the patterned sensing electrode structure. The patterned common electrode layer is disposed on the insulating layer, and the patterned common electrode layer includes a plurality of electrode portions corresponding to the displaying regions and a plurality of connecting portions disposed between the adjacent electrode portions and electrically connected to the electrode portions.

Owner:AU OPTRONICS CORP

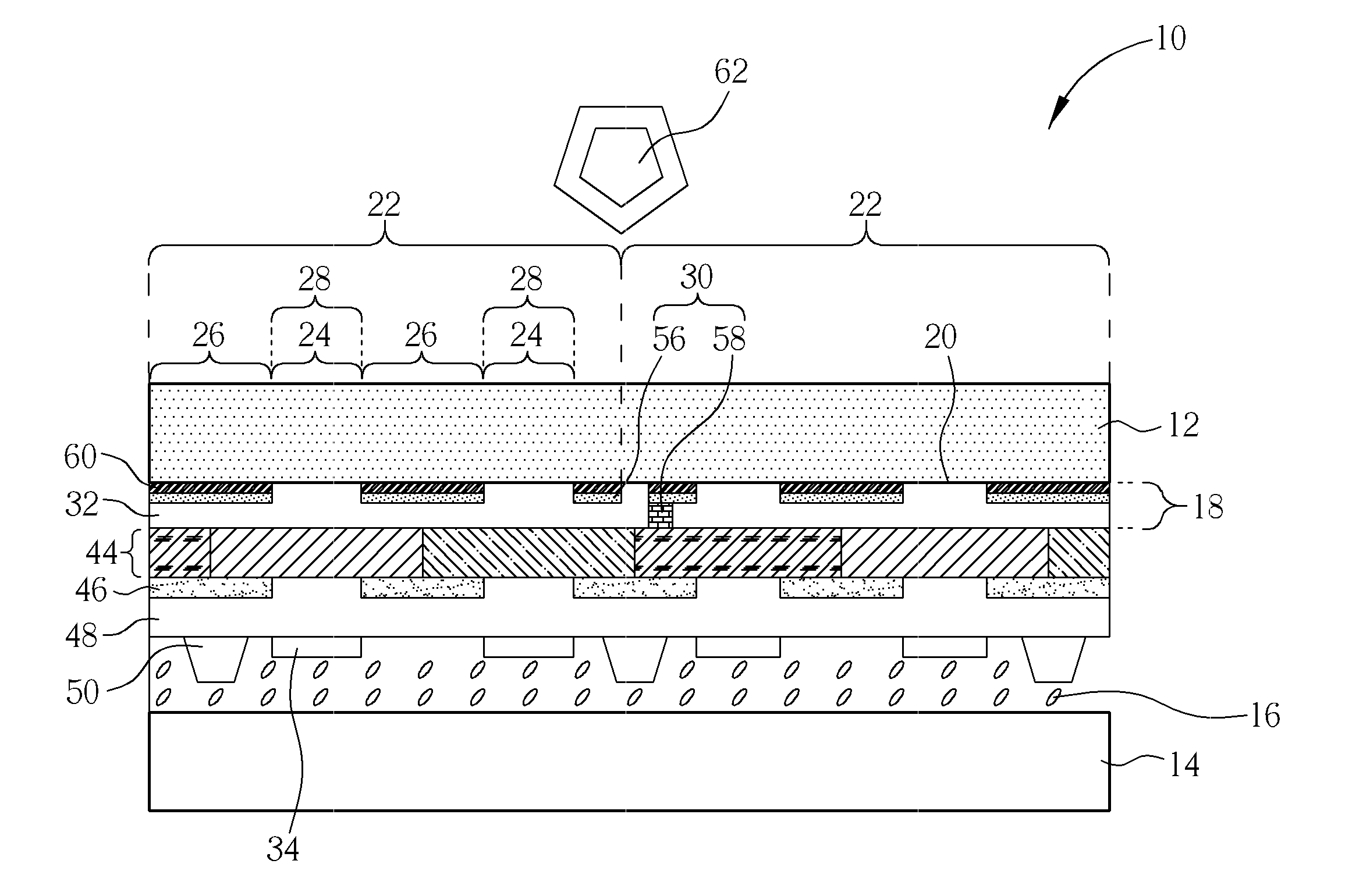

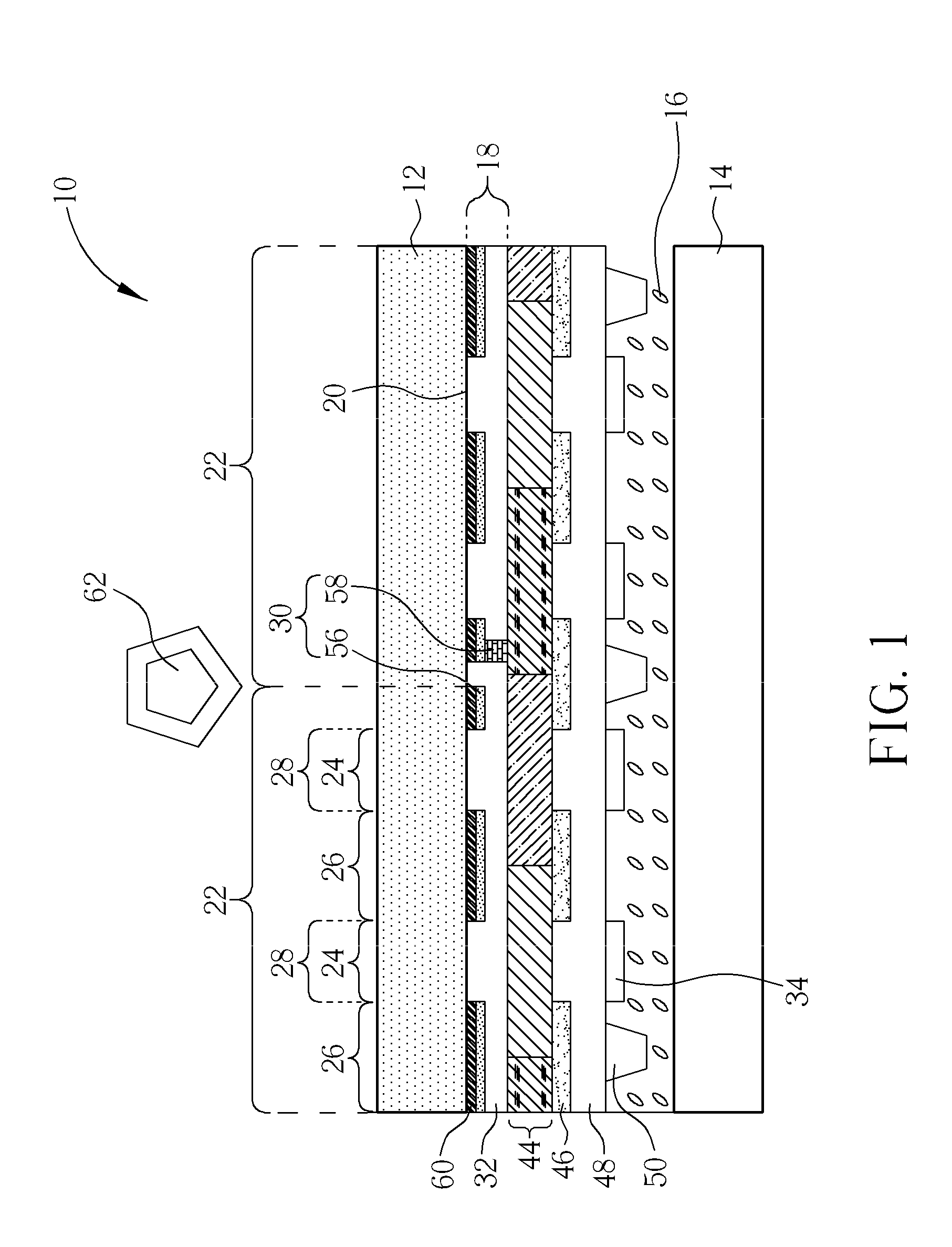

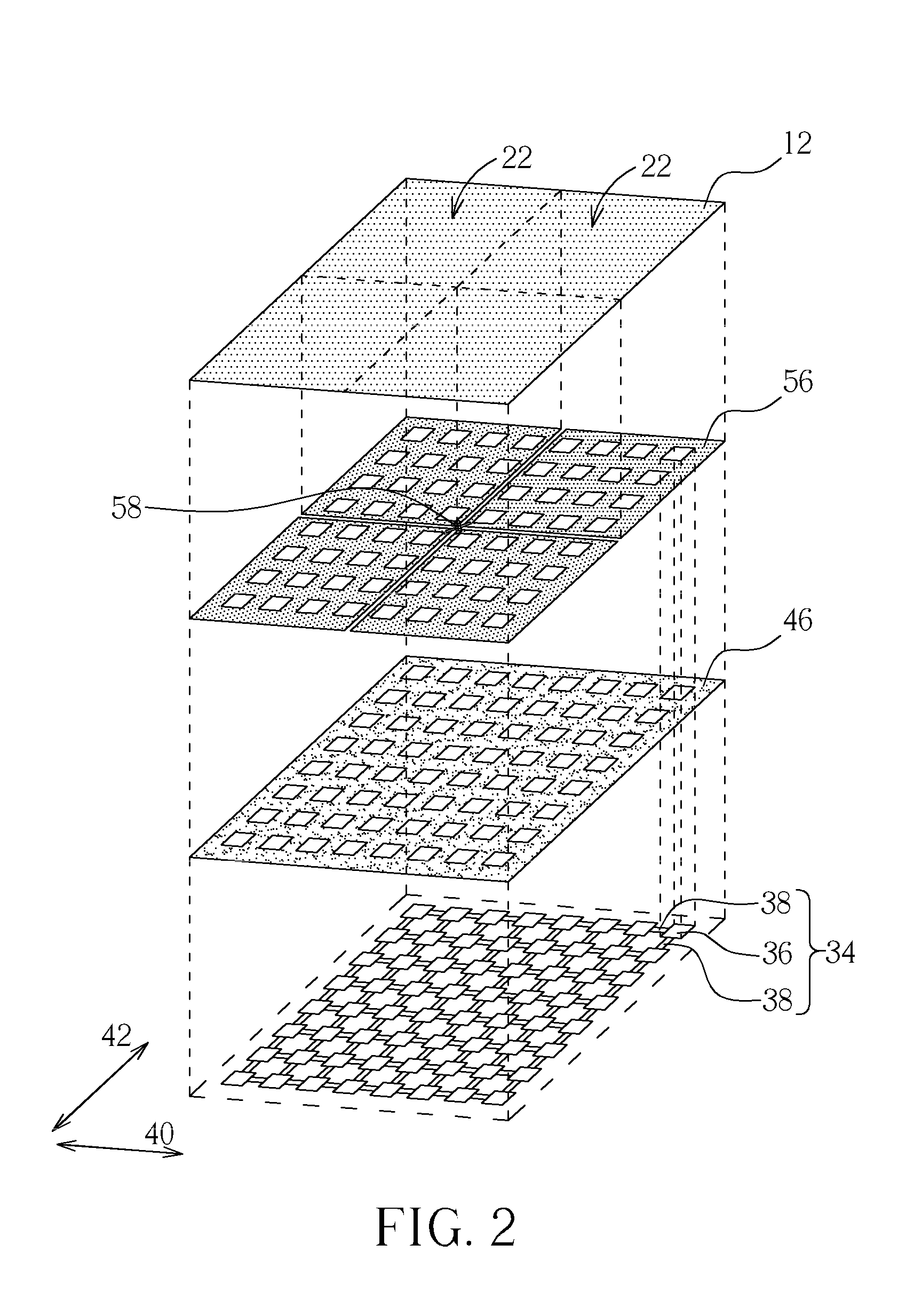

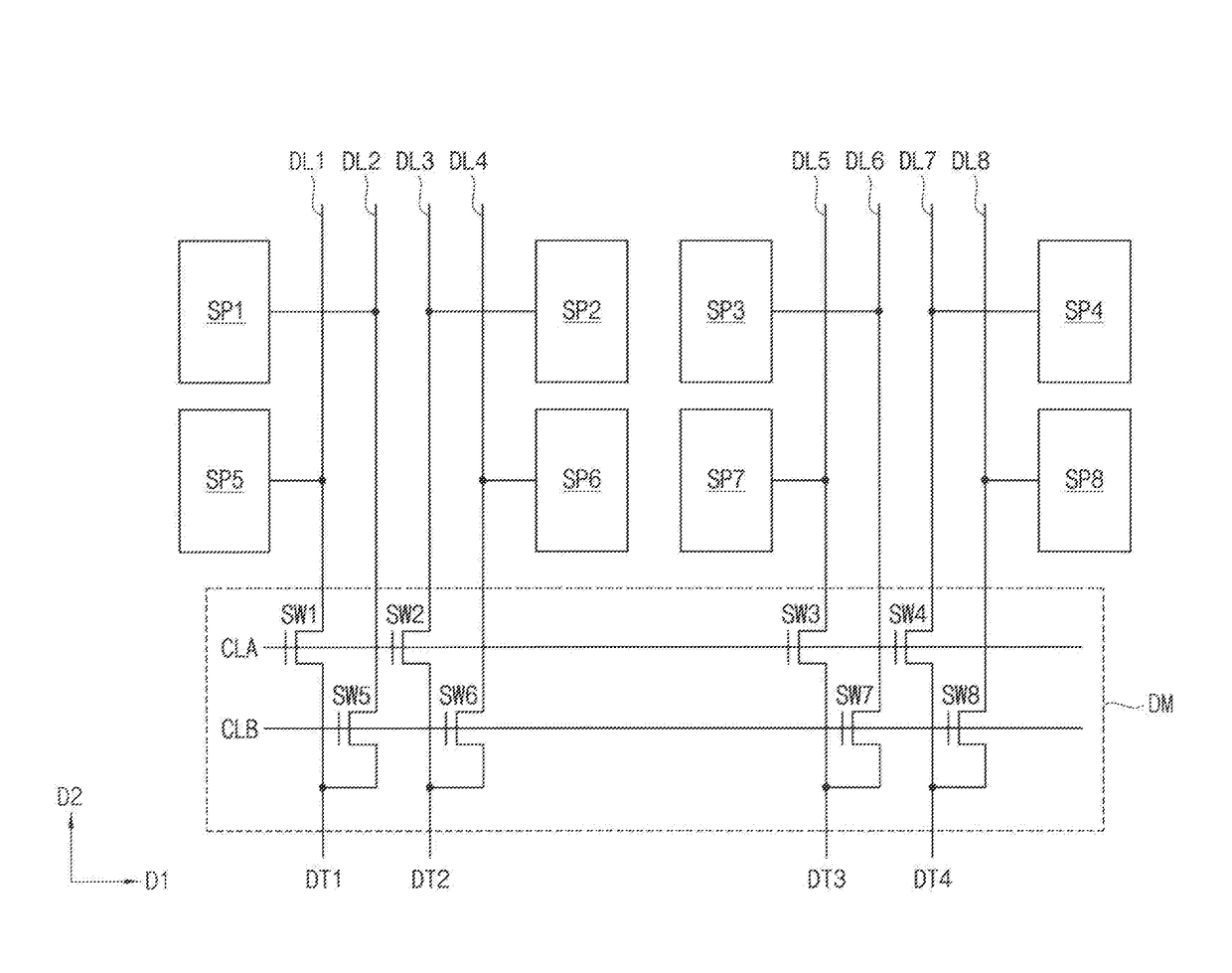

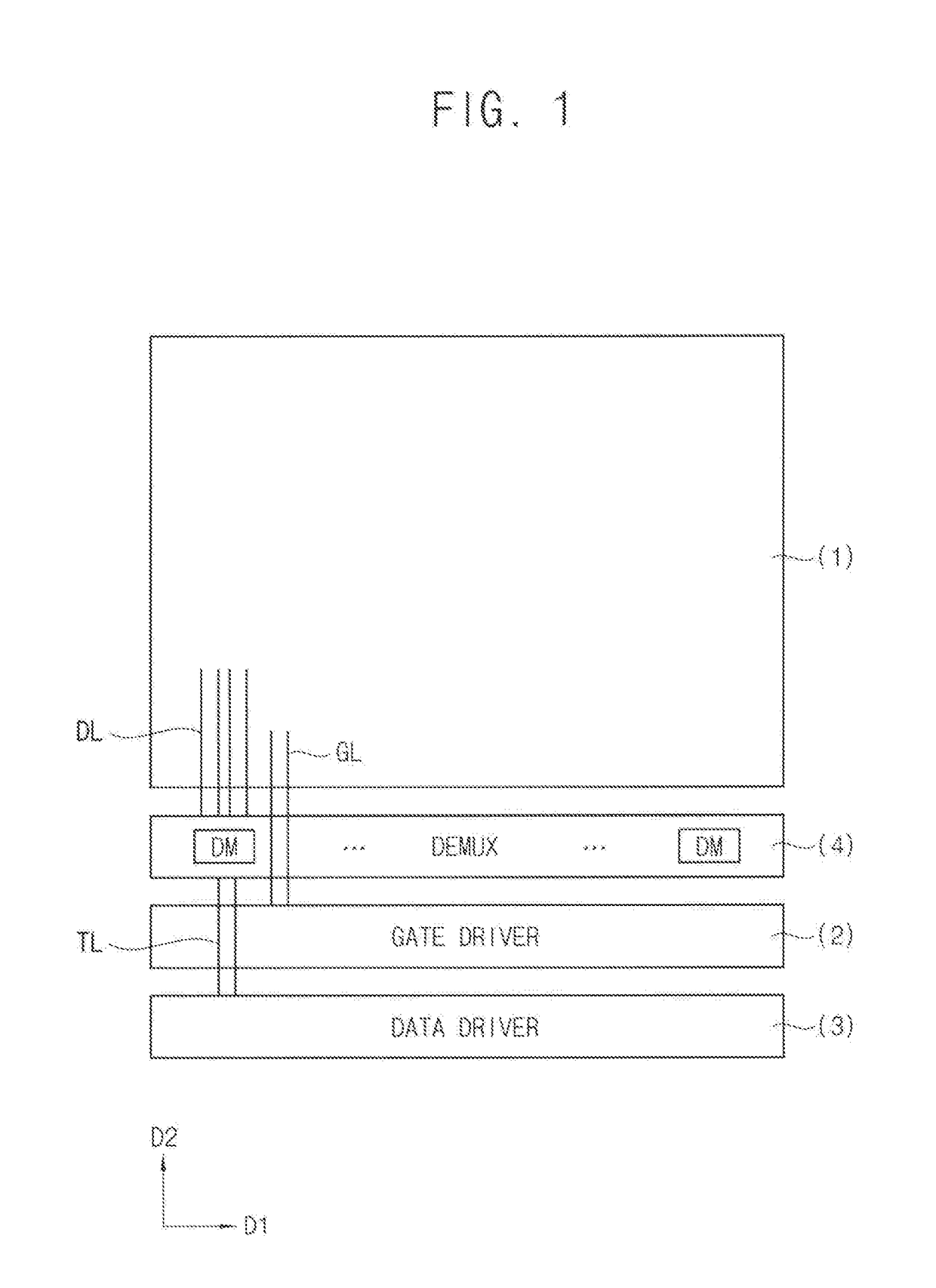

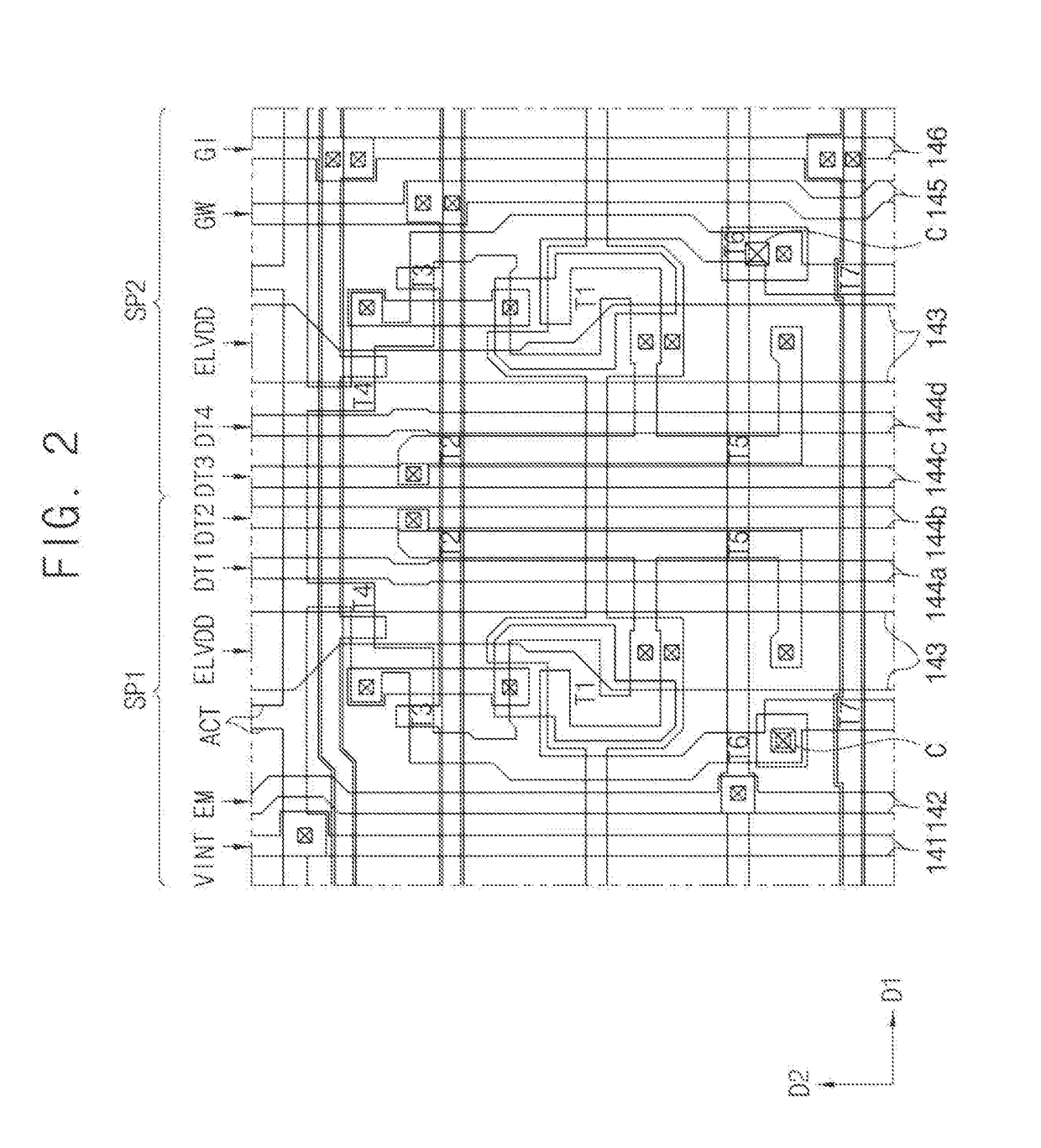

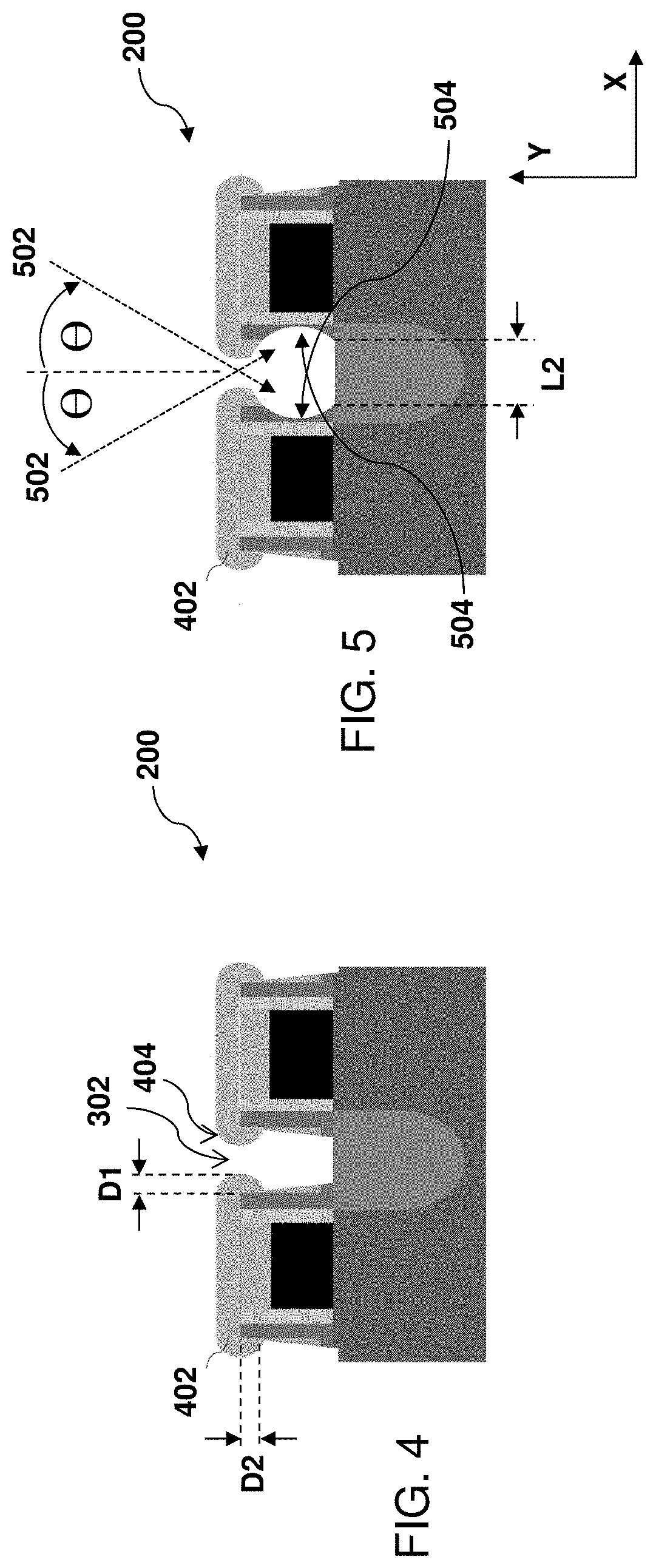

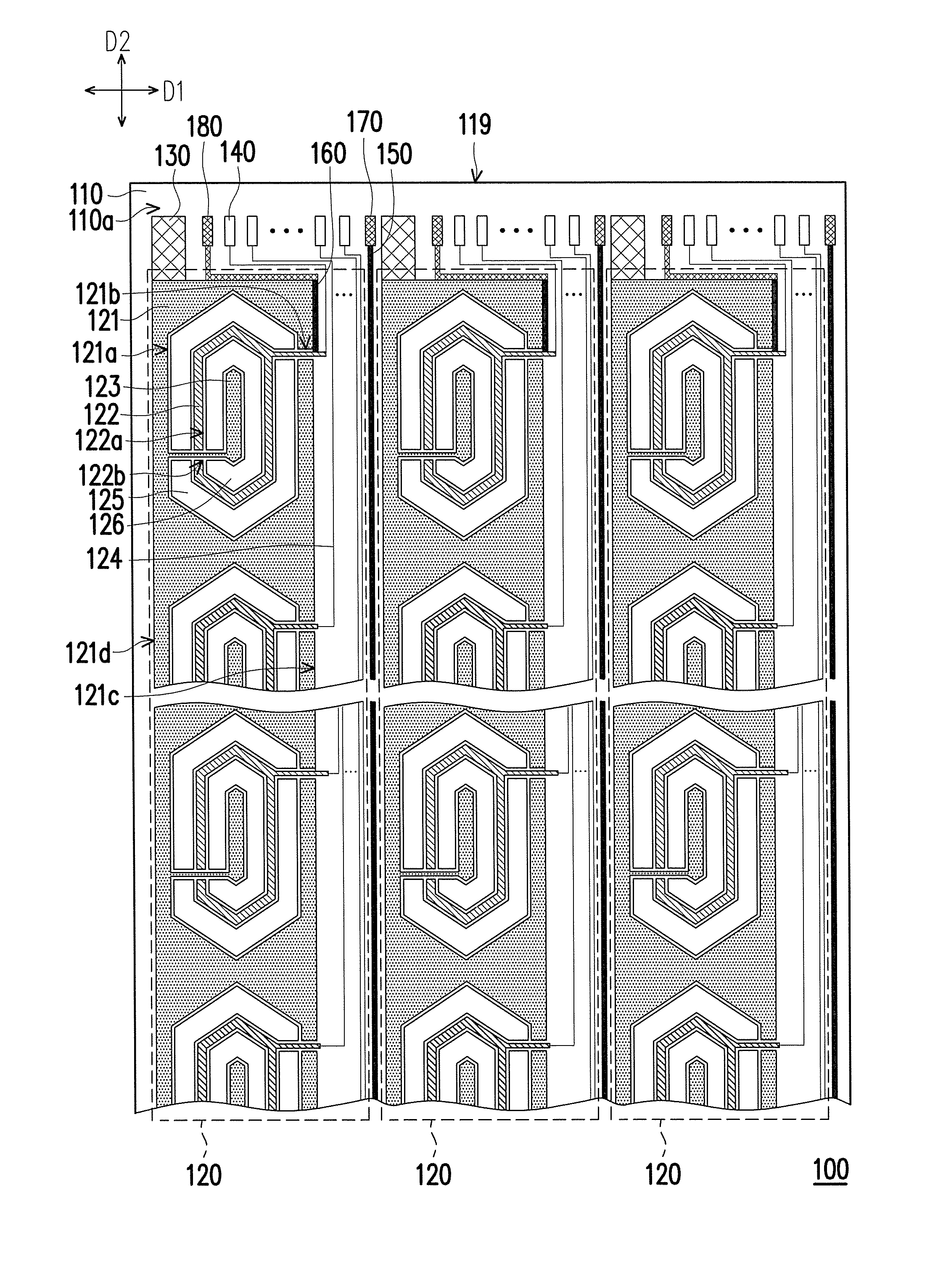

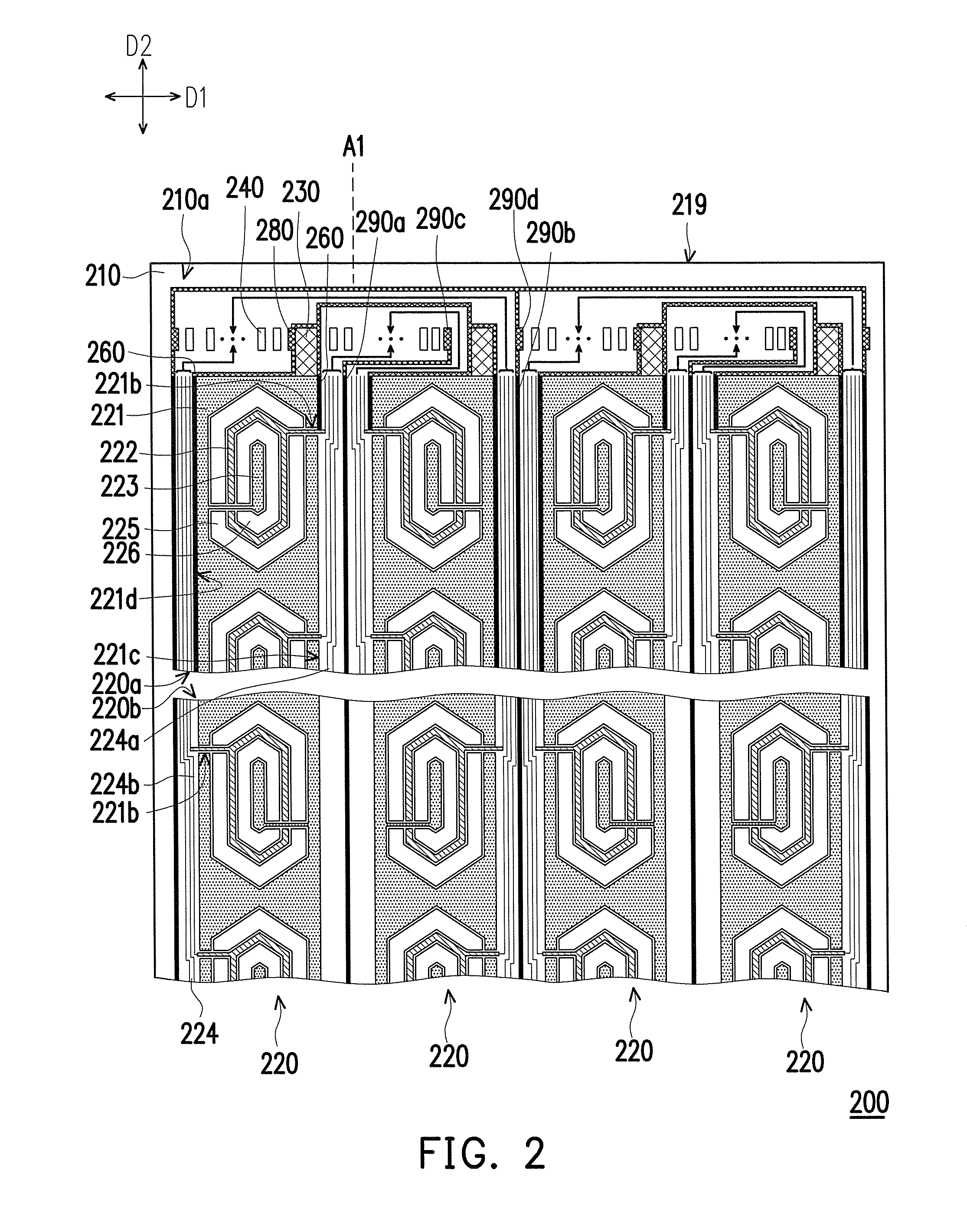

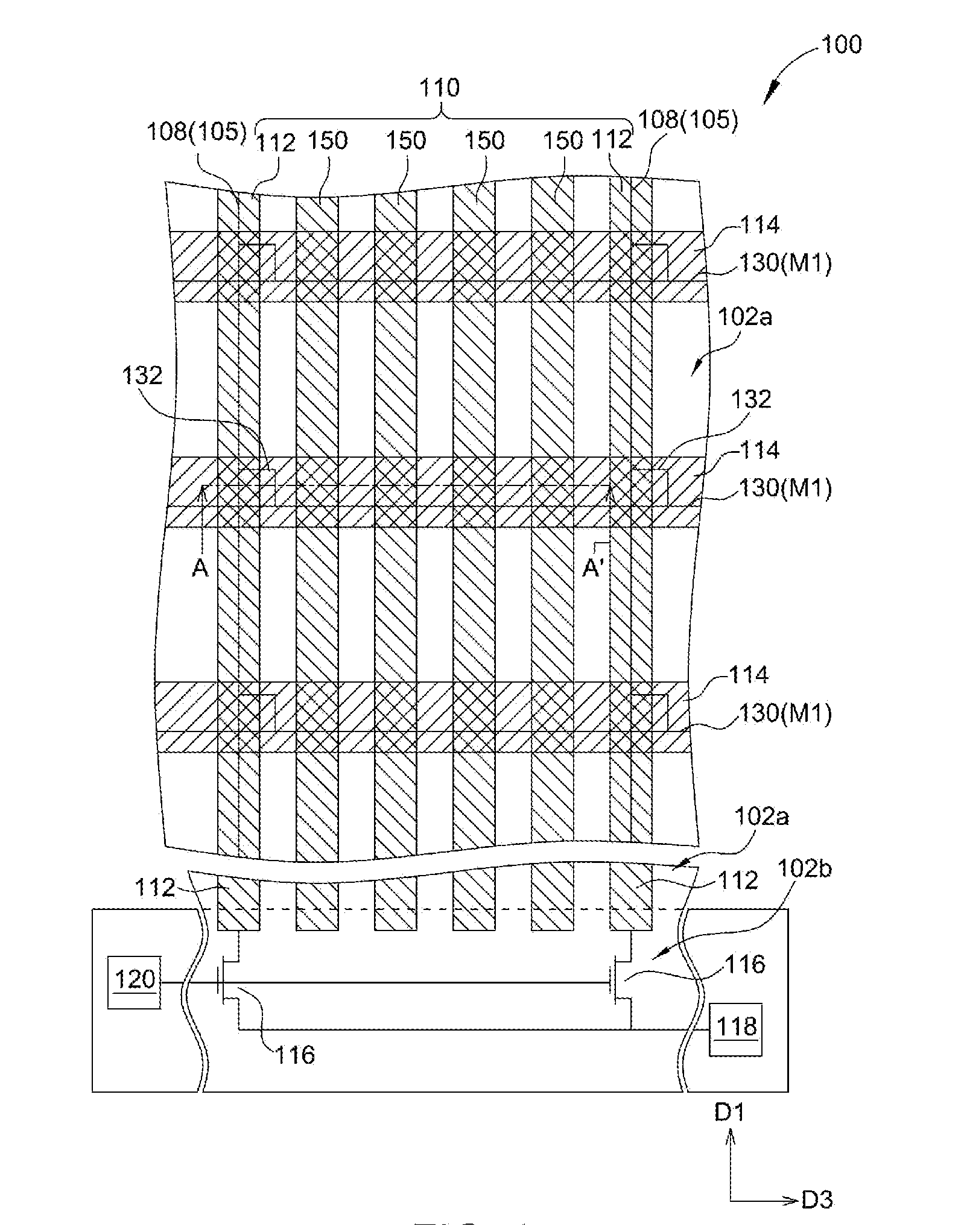

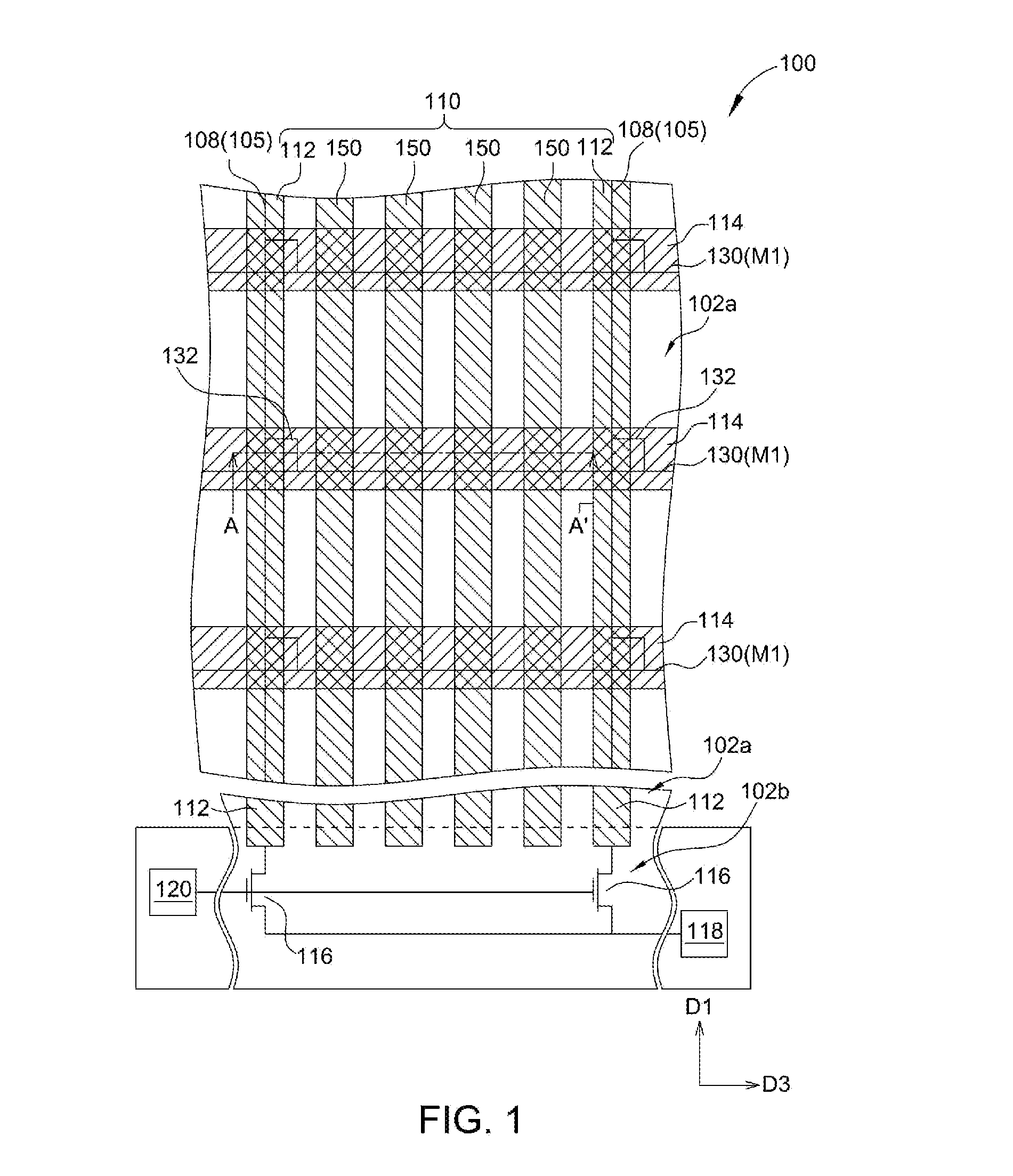

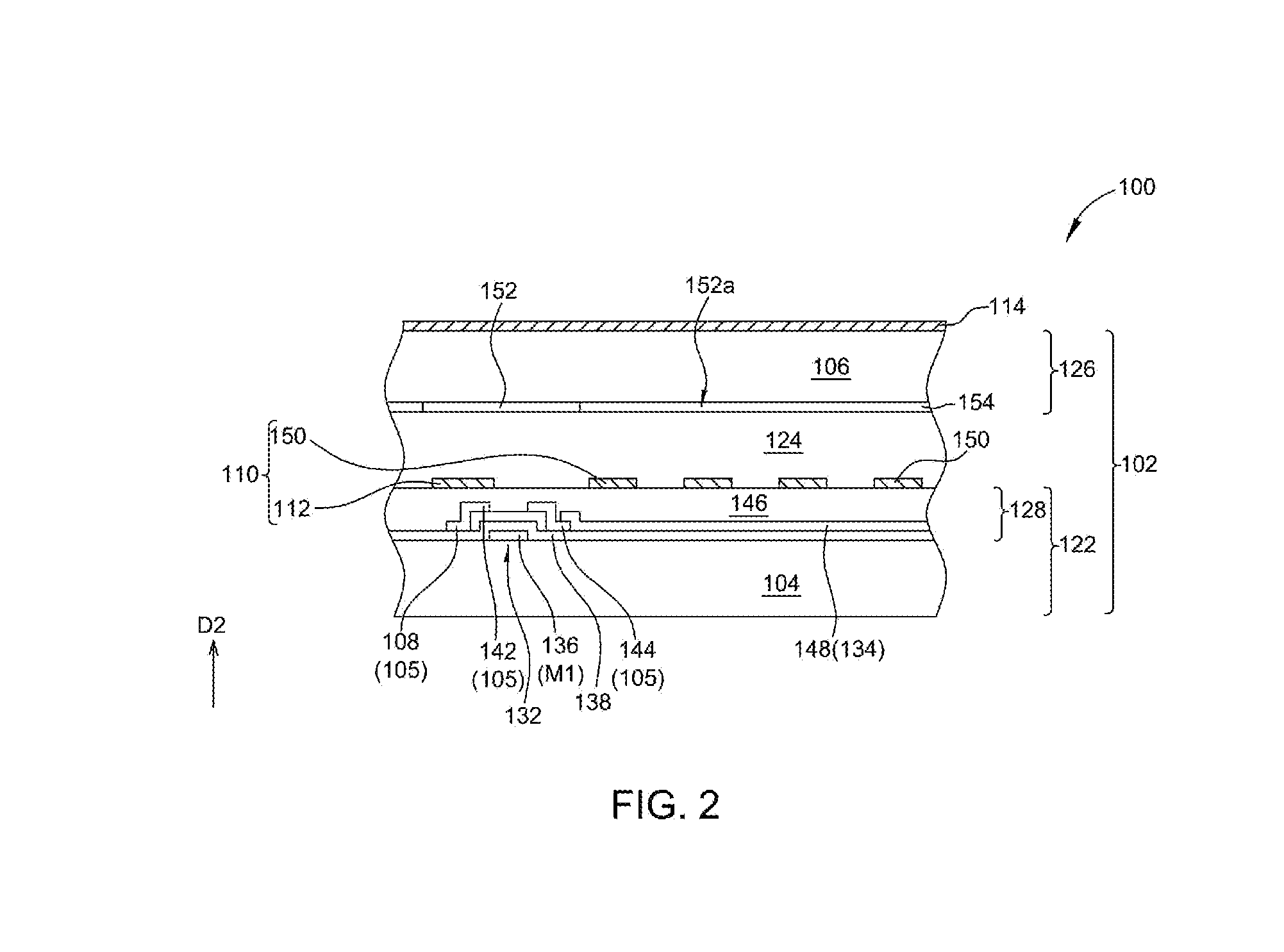

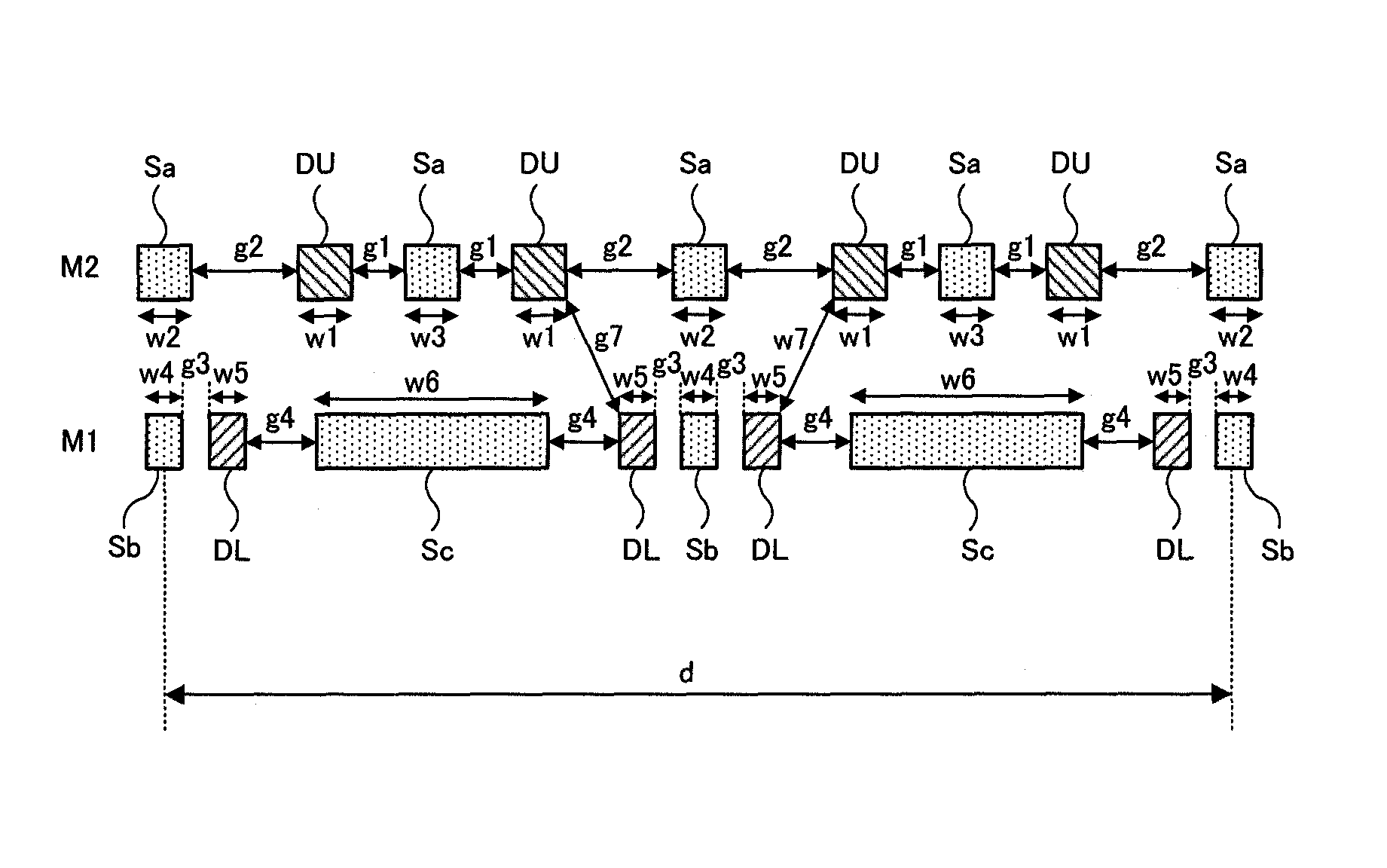

Display apparatus

InactiveUS20170069271A1Coupling capacitanceReduce coupling capacitanceStatic indicating devicesSolid-state devicesEngineeringData lines

Owner:SAMSUNG DISPLAY CO LTD

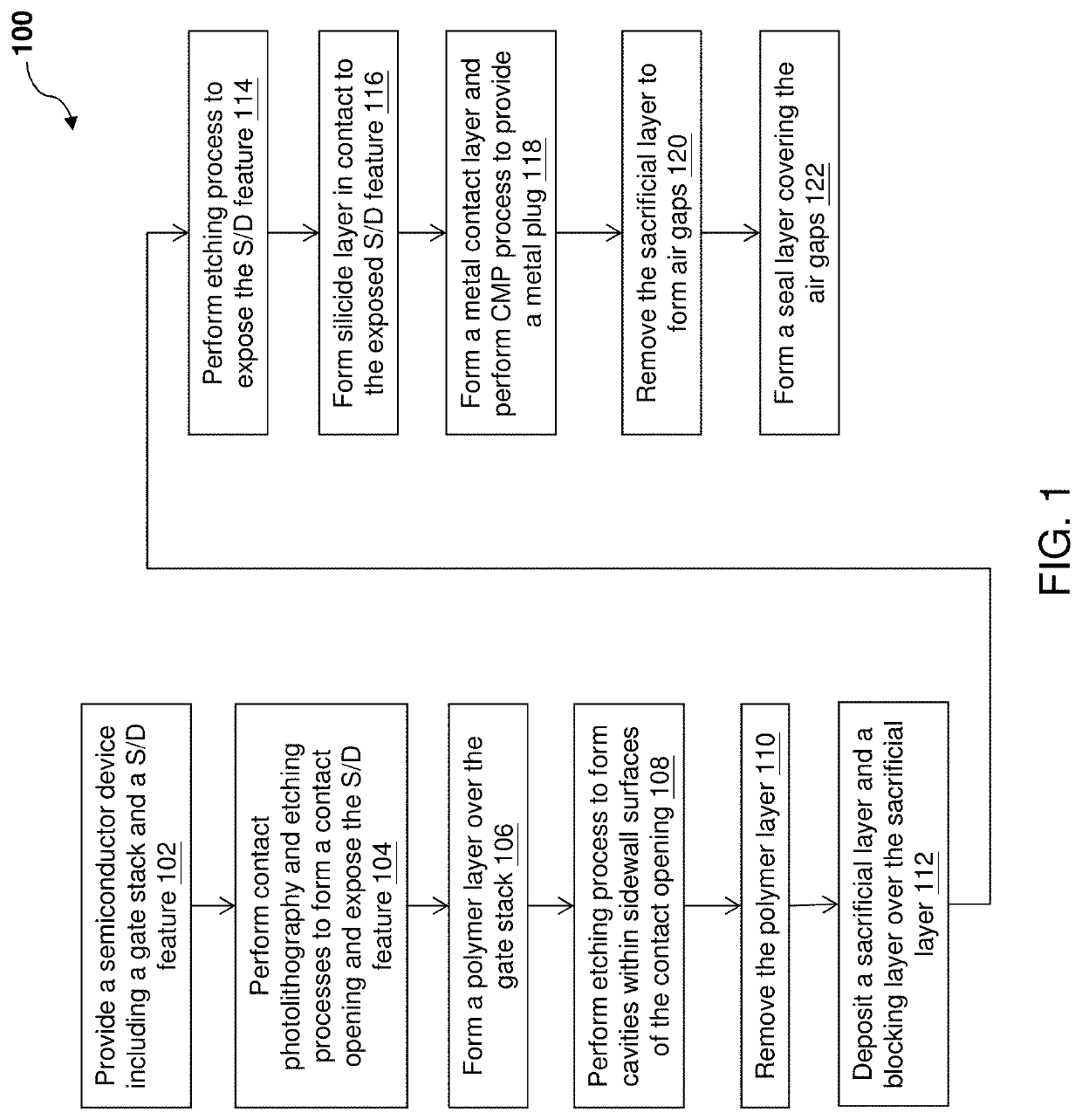

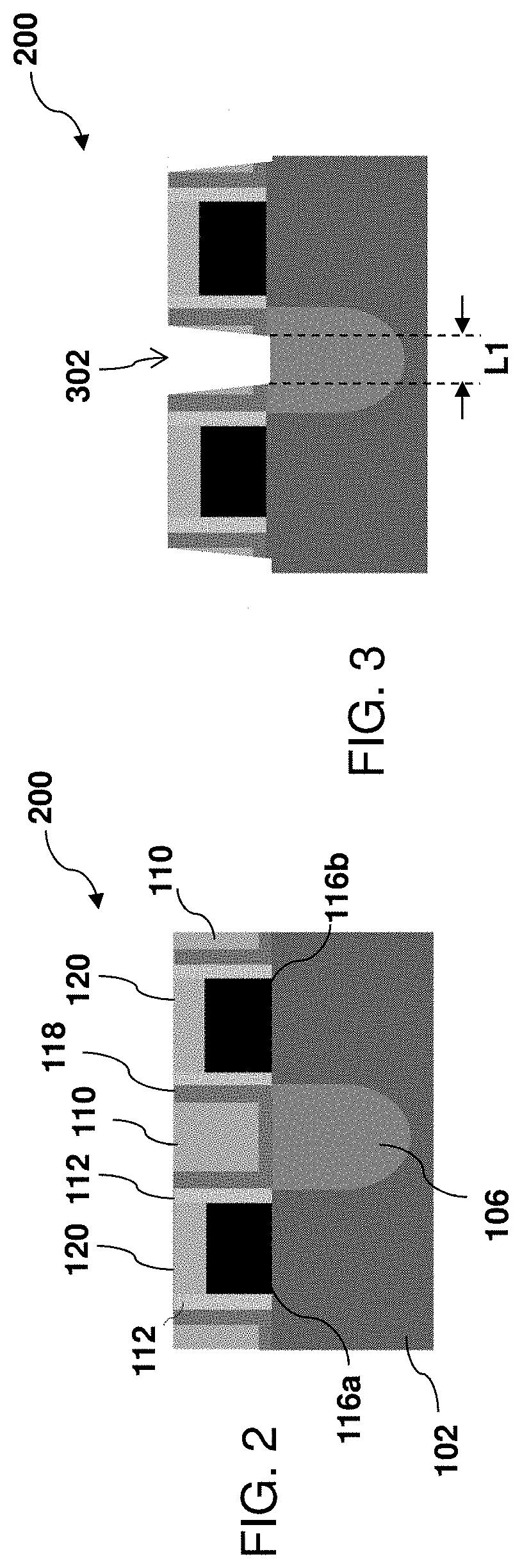

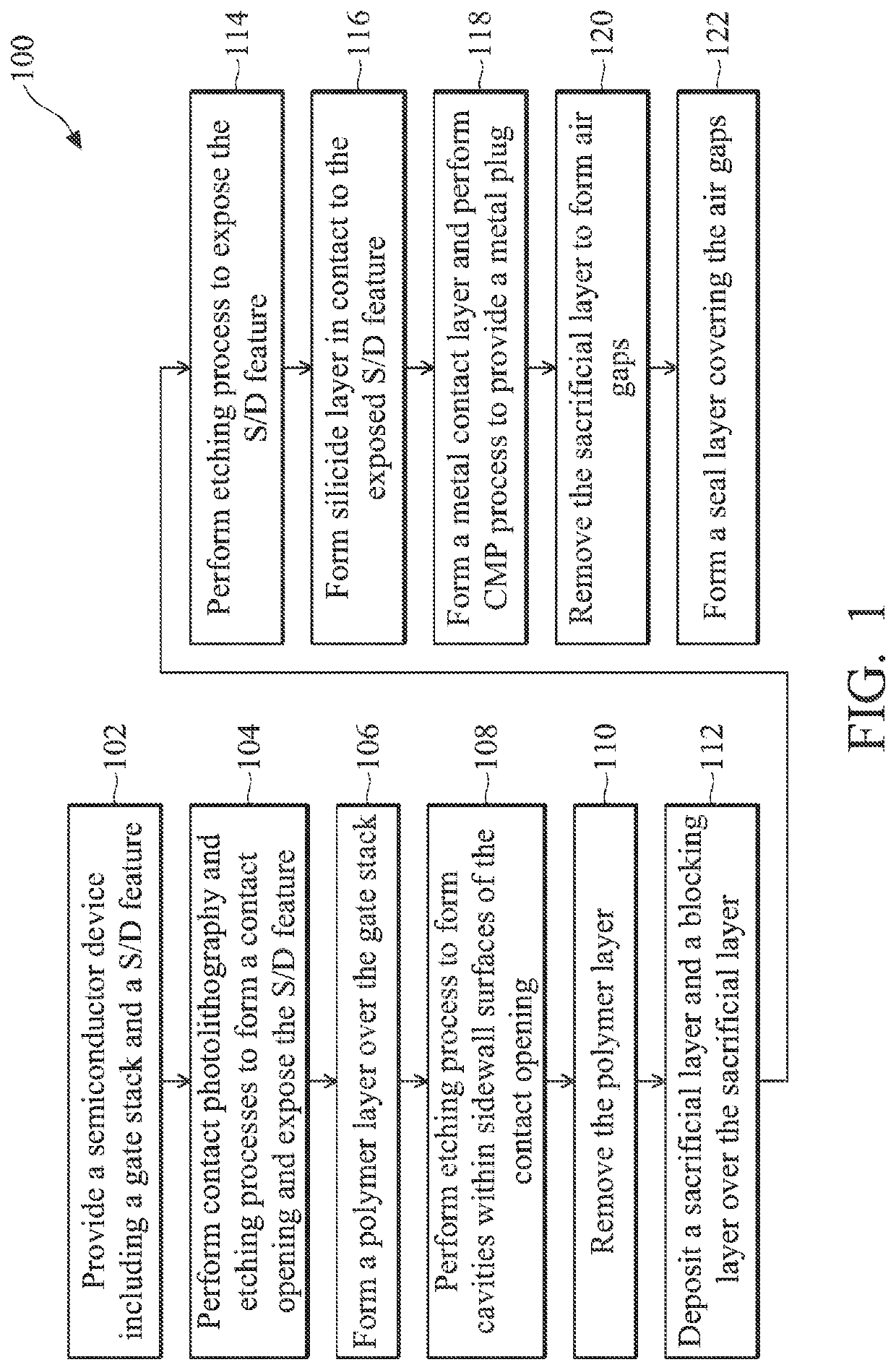

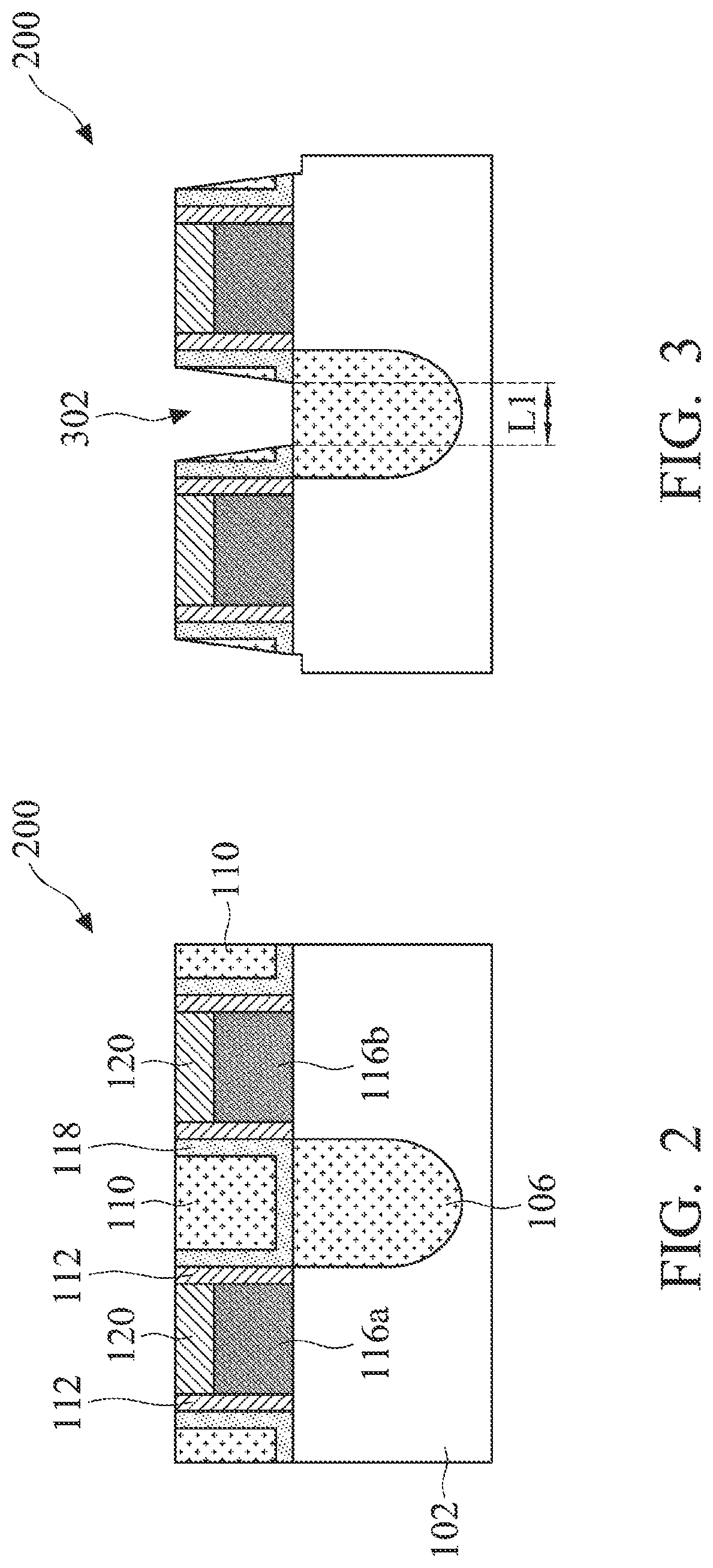

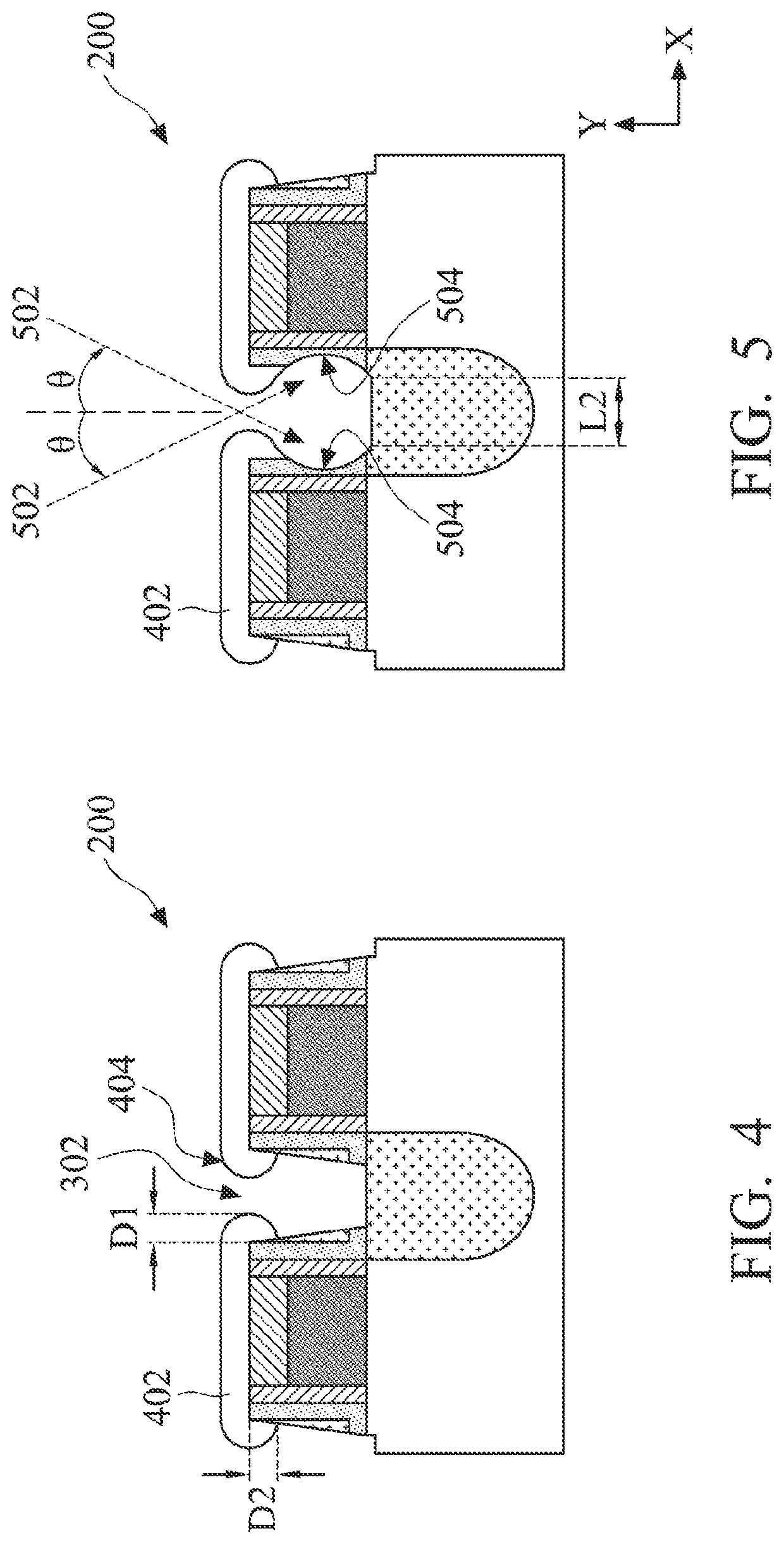

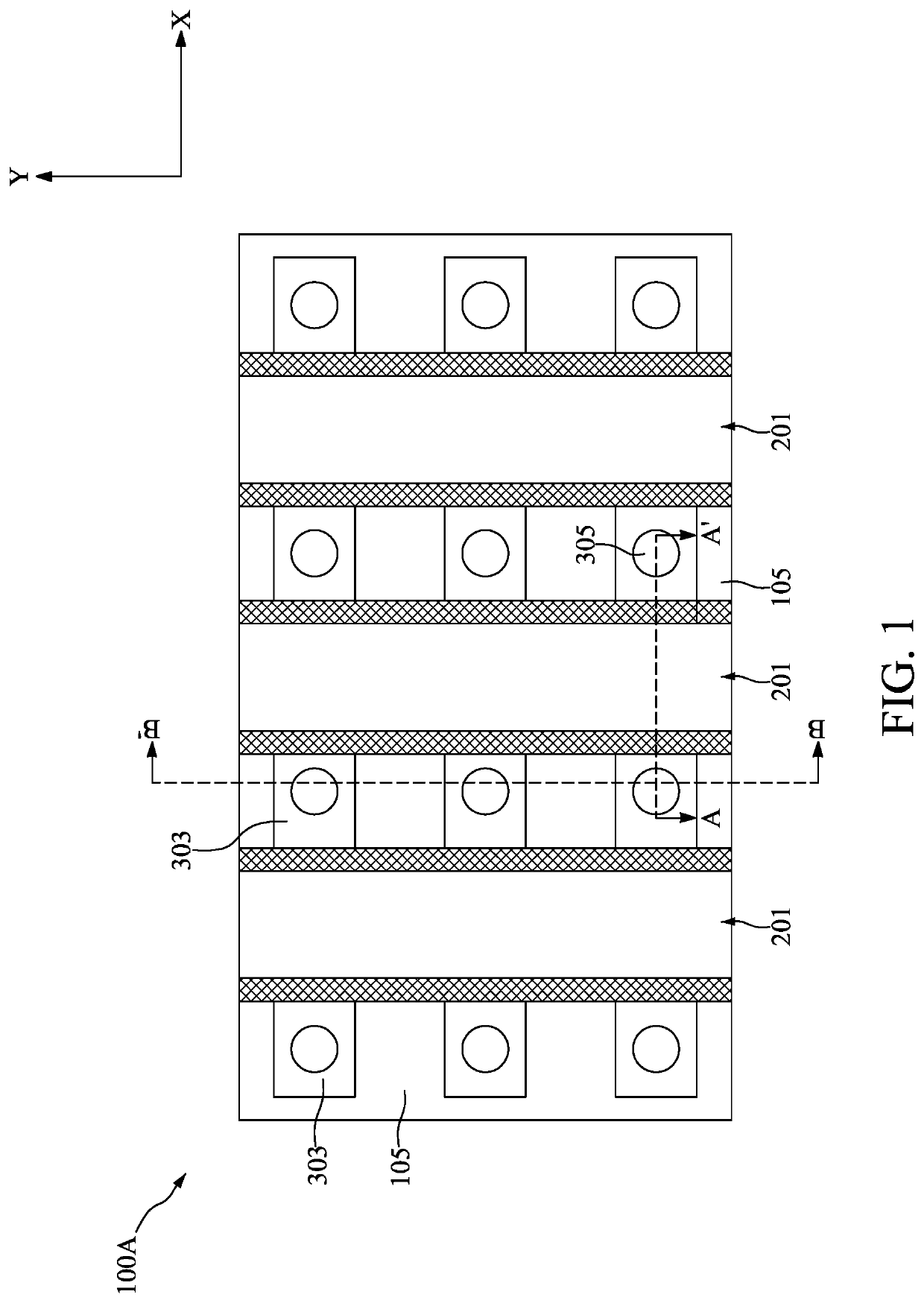

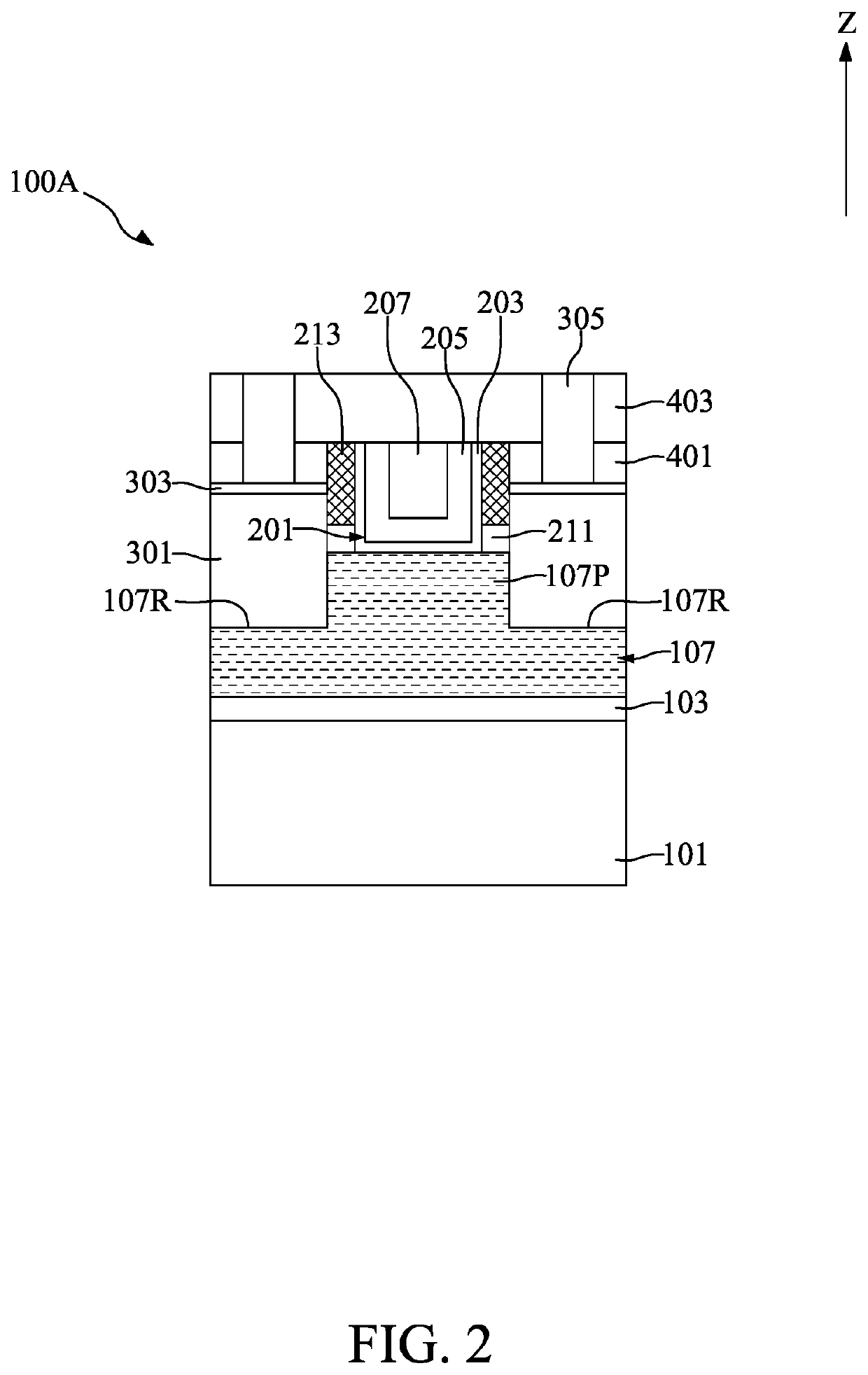

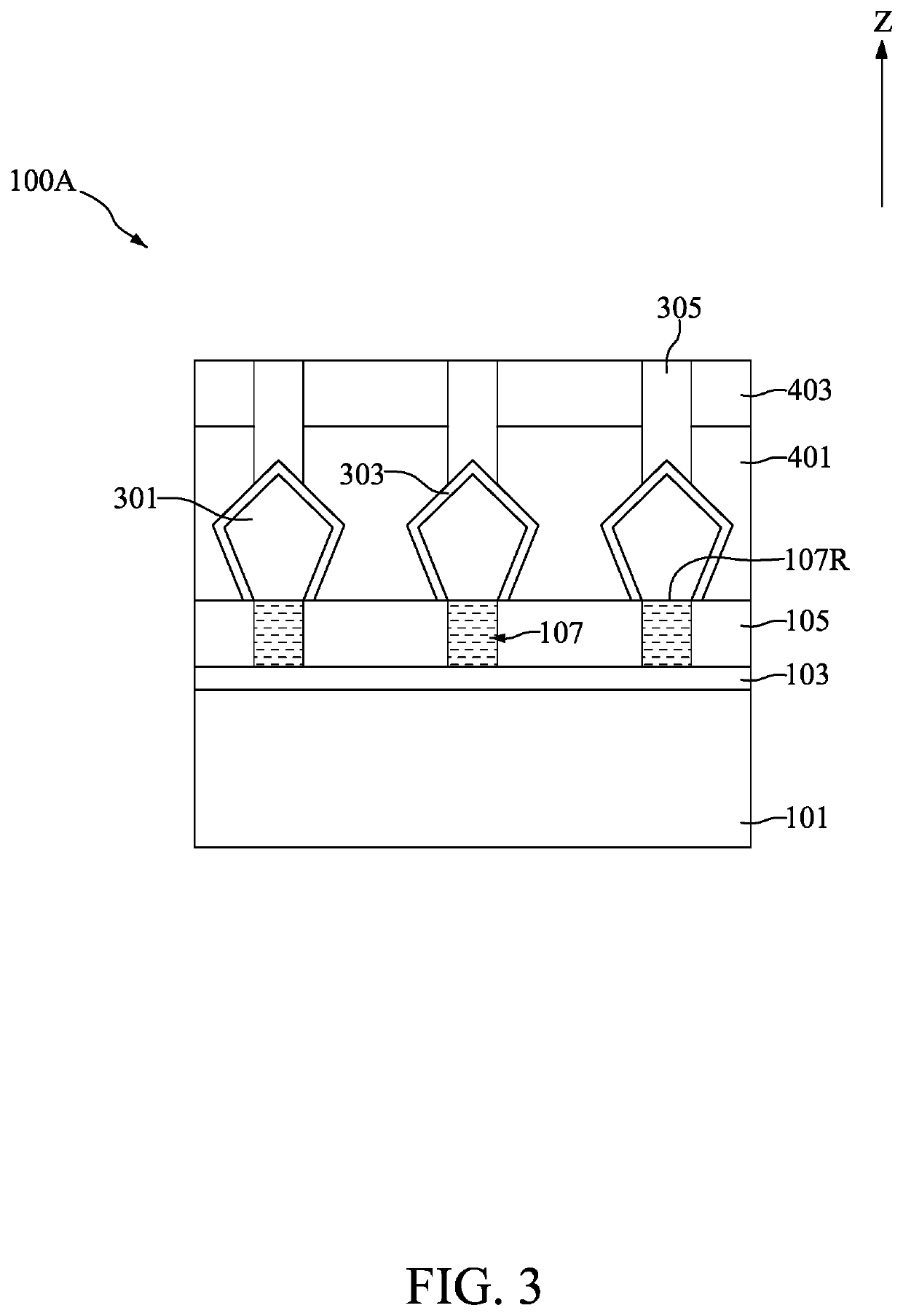

Contact air gap formation and structures thereof

ActiveUS20200135591A1Eliminate riskLow effective capacitanceTransistorSolid-state devicesEngineering physicsMaterials science

A method of forming a device includes providing a transistor having a gate structure and a source / drain structure adjacent to the gate structure. A cavity is formed along a sidewall surface of a contact opening over the source / drain structure. After forming the cavity, a sacrificial layer is deposited over a bottom surface and along the sidewall surface of the contact opening including within the cavity. A first portion of the sacrificial layer along the bottom surface of the contact opening is removed to expose a portion of the source / drain structure. A metal plug is then formed over the portion of the exposed source / drain structure. A remaining portion of the sacrificial layer is removed to form an air gap disposed between the metal plug and the gate structure. Thereafter, a seal layer is deposited over the air gap to form an air gap spacer.

Owner:TAIWAN SEMICON MFG CO LTD

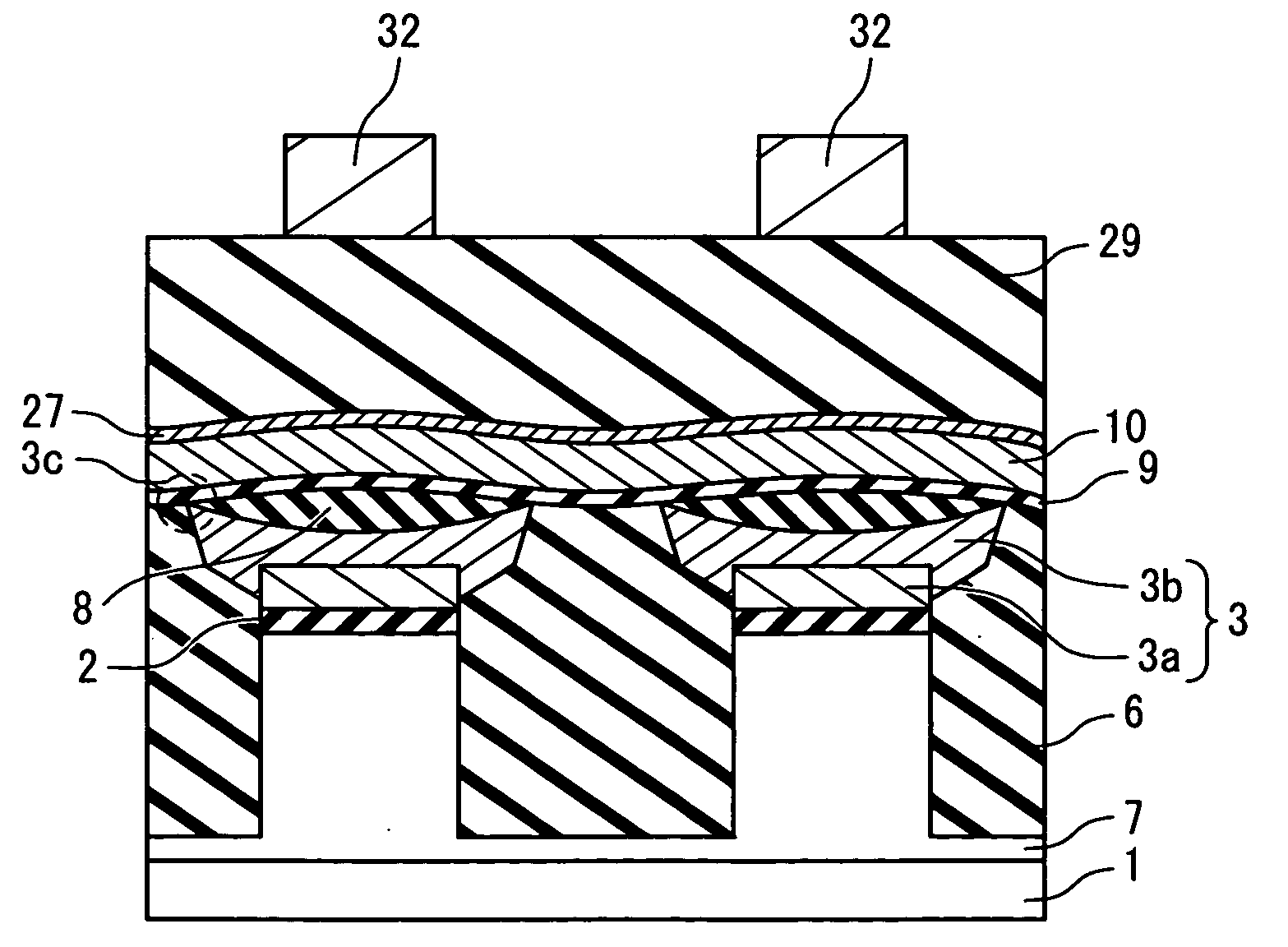

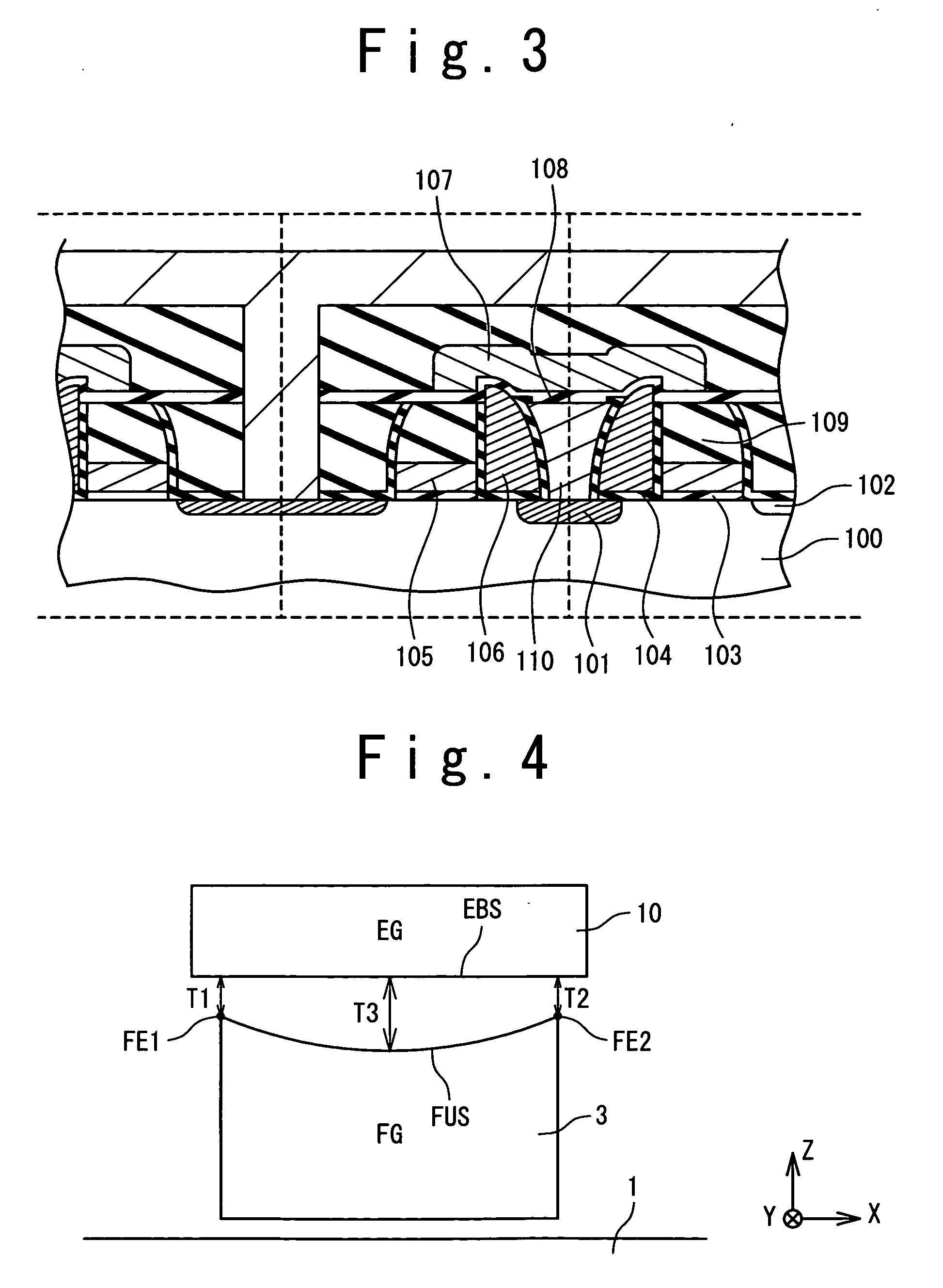

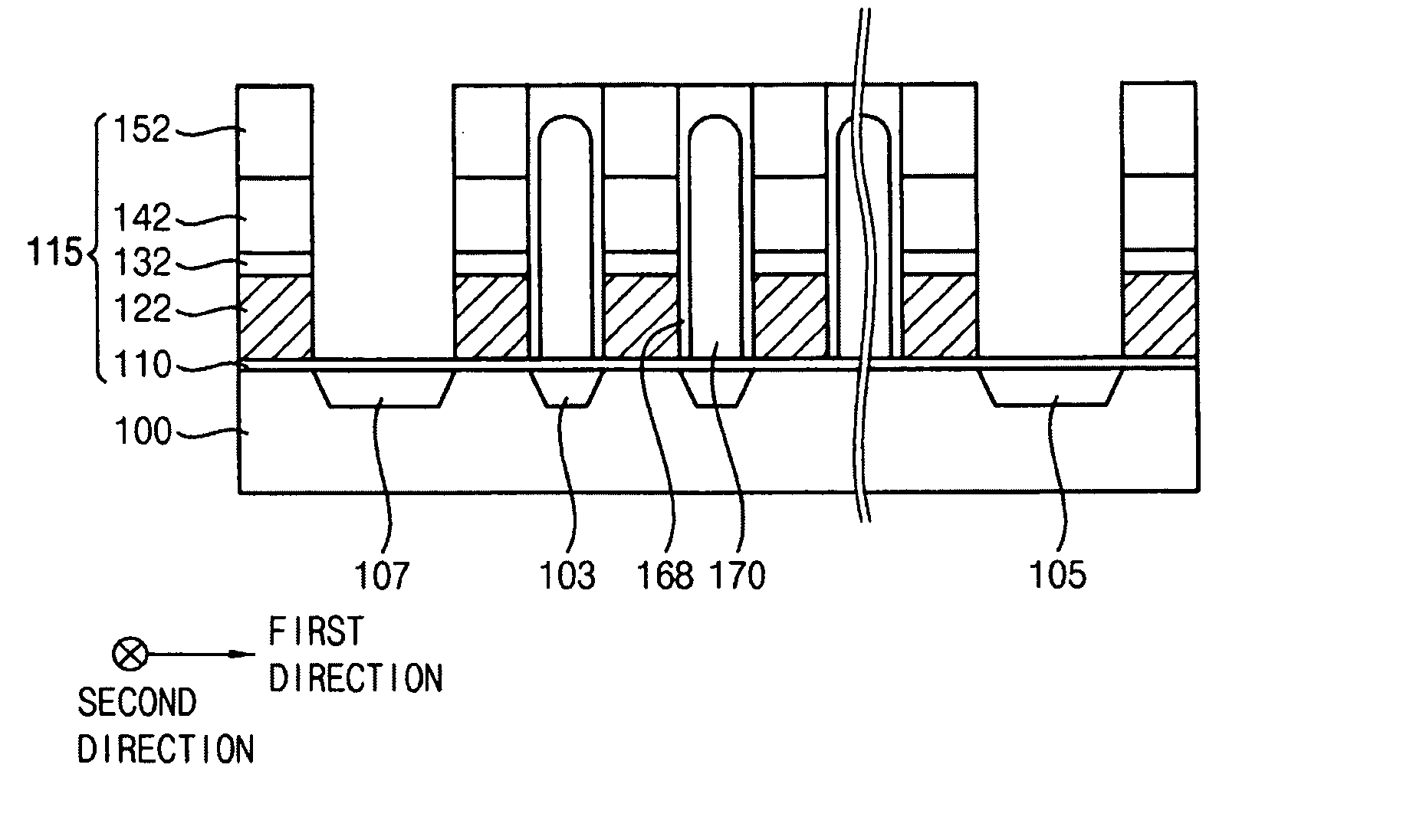

Nonvolatile semiconductor memory device and method of manufacturing the same

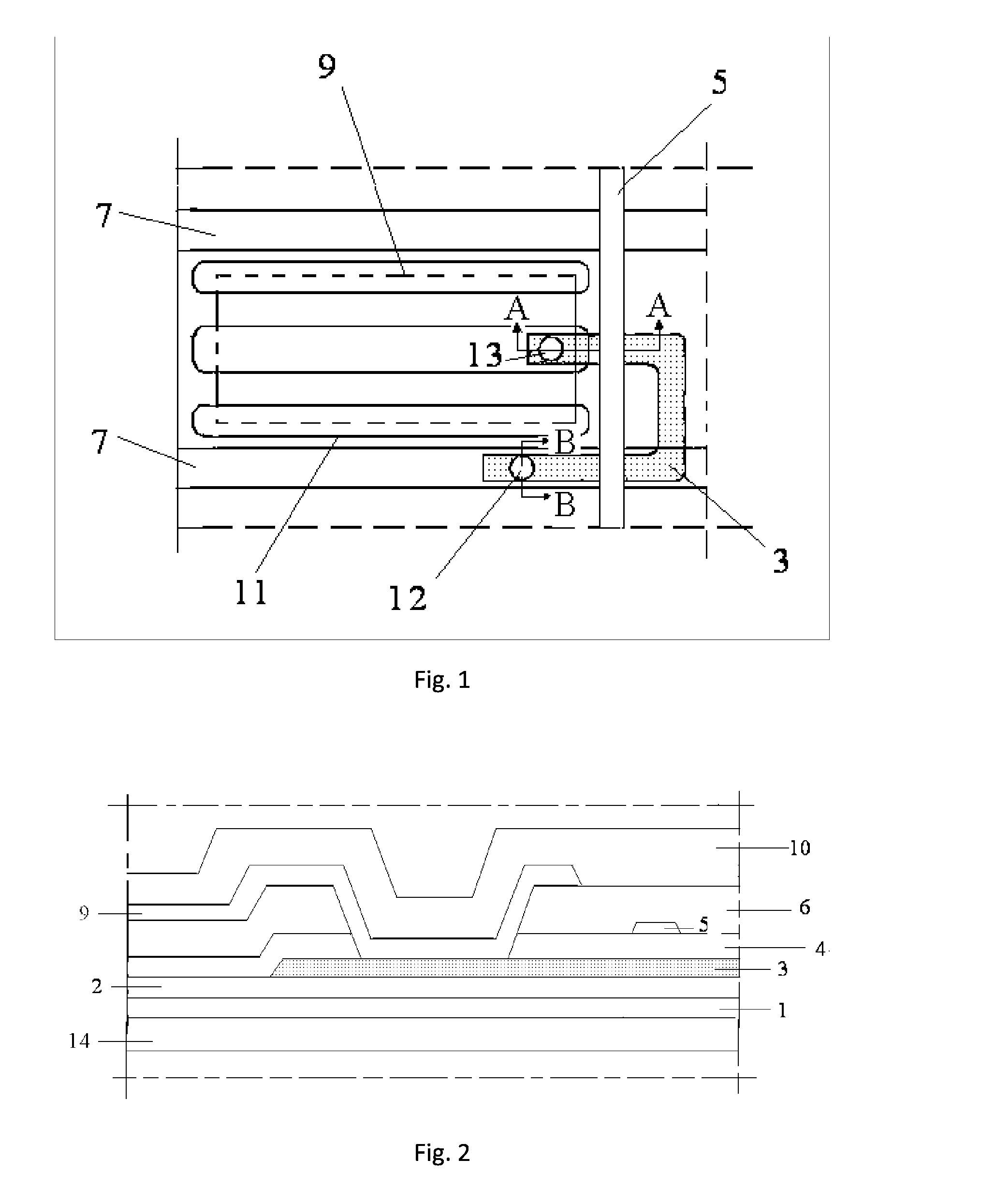

InactiveUS20090200600A1Couple capacitanceImprove erase efficiencyTransistorSolid-state devicesSemiconductor memorySemiconductor

A nonvolatile semiconductor memory device has: a semiconductor substrate; a control gate and a floating gate that are formed side by side on a gate insulating film on a channel region in the semiconductor substrate; and an erase gate facing an upper surface of the floating gate and totally located above the upper surface of the floating gate. The upper surface of the floating gate includes a first side and a second side that face each other. A bottom surface of the erase gate is closer to the first side and the second side than the upper surface between the first side and the second side.

Owner:RENESAS ELECTRONICS CORP

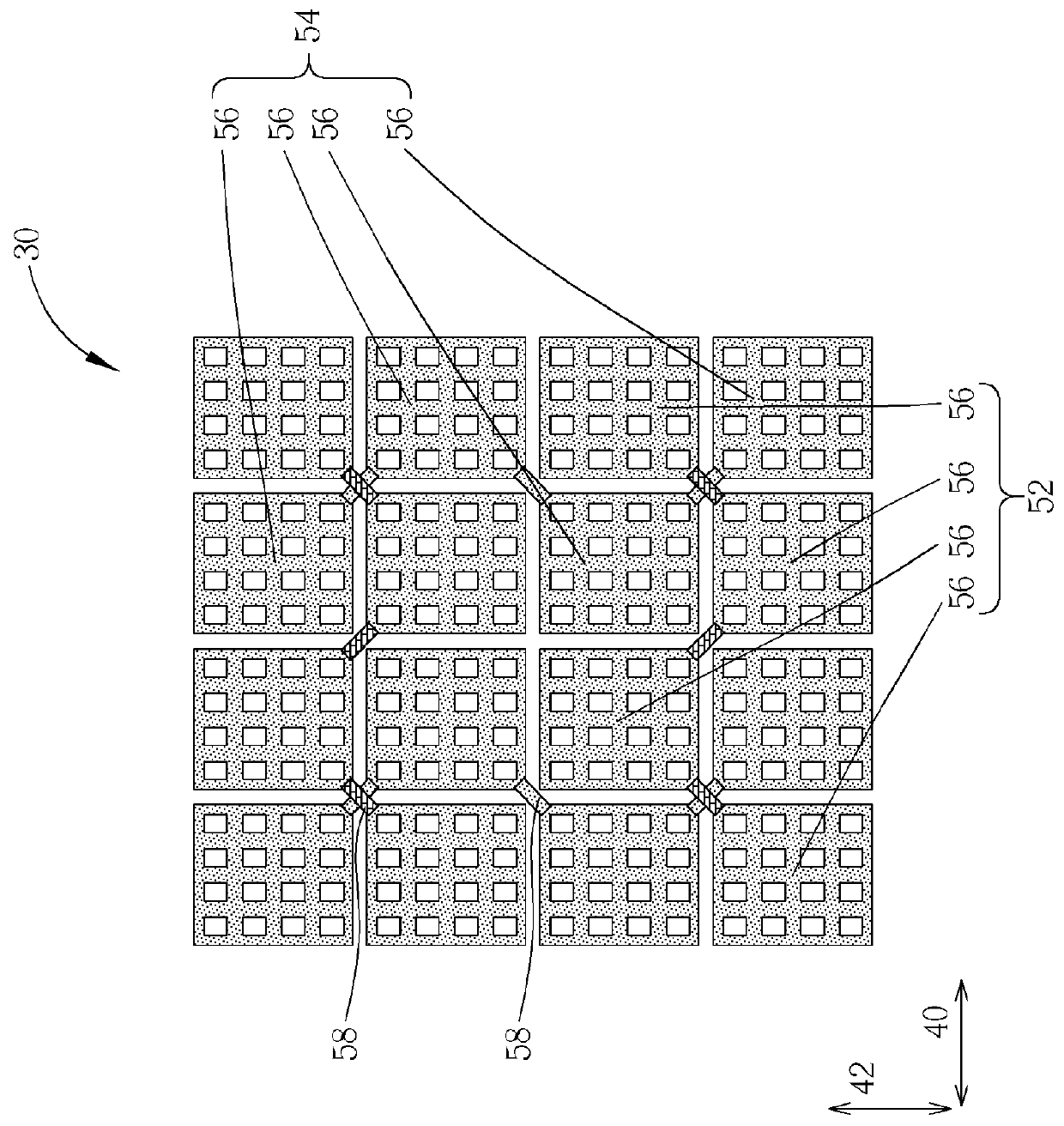

Touch panel

ActiveUS20130240341A1Favorable touch sensing qualityCoupling capacitanceElectronic switchingInput/output processes for data processingEngineeringTouch panel

A touch panel includes a substrate and sensing units. Each sensing unit includes an electrode line, first electrode patterns, second electrode patterns and connecting lines. The electrode line extends along a second direction and has first openings arranged along the second direction and first breaches corresponding to the first openings. Each first breach connects the corresponding first opening and the exterior of the electrode line. The first electrode patterns are respectively disposed in the first openings. Each first electrode pattern has a second opening and a second breach connecting the second opening and the exterior of first electrode pattern. The second electrode patterns are respectively disposed in the second openings and respectively connected with the electrode line through the second breaches. The connecting lines are disposed on at least one side of the electrode line and connected with the corresponding first electrode pattern through the first breach.

Owner:HTC CORP

Touch display panel

InactiveUS20160034072A1Reduce coupling capacitanceHigh strengthStatic indicating devicesInput/output processes for data processingDisplay deviceEngineering

A touch display device includes a patterned sensing electrode structure, an insulating layer and a patterned common electrode layer. The patterned sensing electrode structure is disposed on a surface of a substrate, defining a plurality of displaying regions and a light-shielding region. The patterned sensing electrode structure corresponds to the light-shielding region, and exposes the displaying regions. The insulating layer covers the patterned sensing electrode structure. The patterned common electrode layer is disposed on the insulating layer, and the patterned common electrode layer includes a plurality of electrode portions corresponding to the displaying regions and a plurality of connecting portions disposed between the adjacent electrode portions and electrically connected to the electrode portions.

Owner:AU OPTRONICS CORP

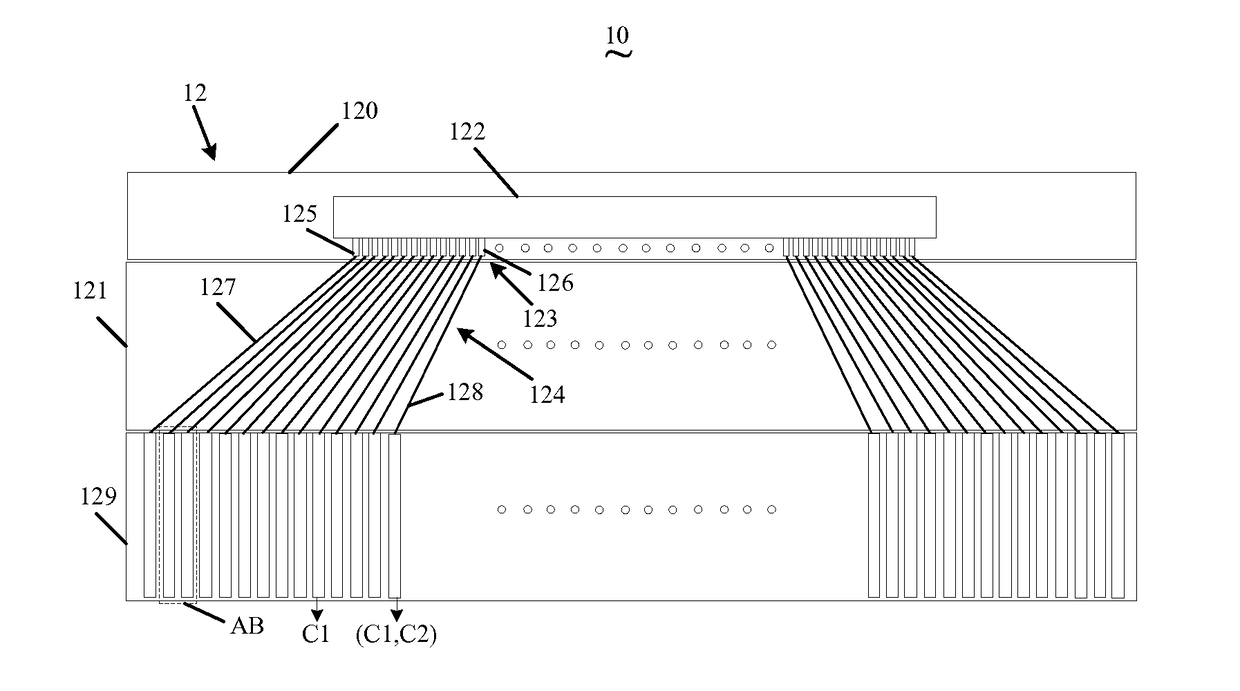

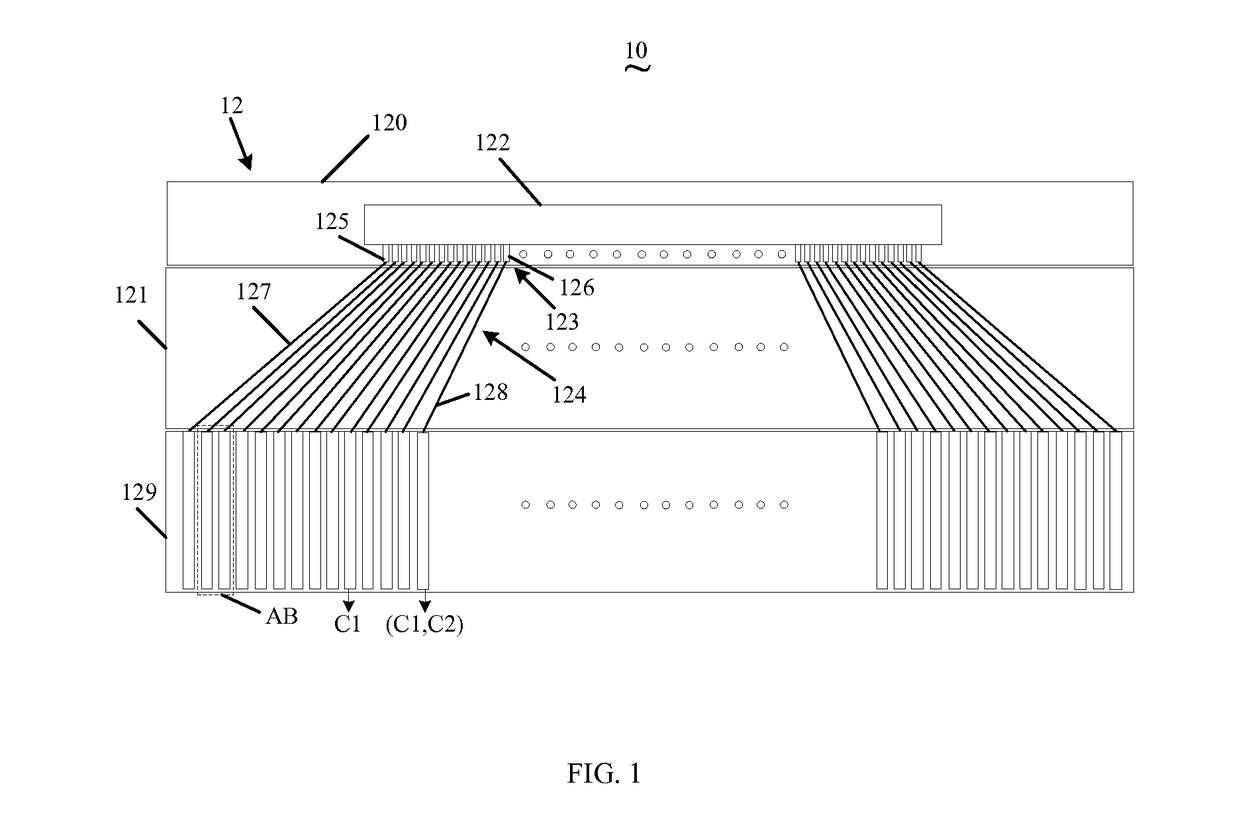

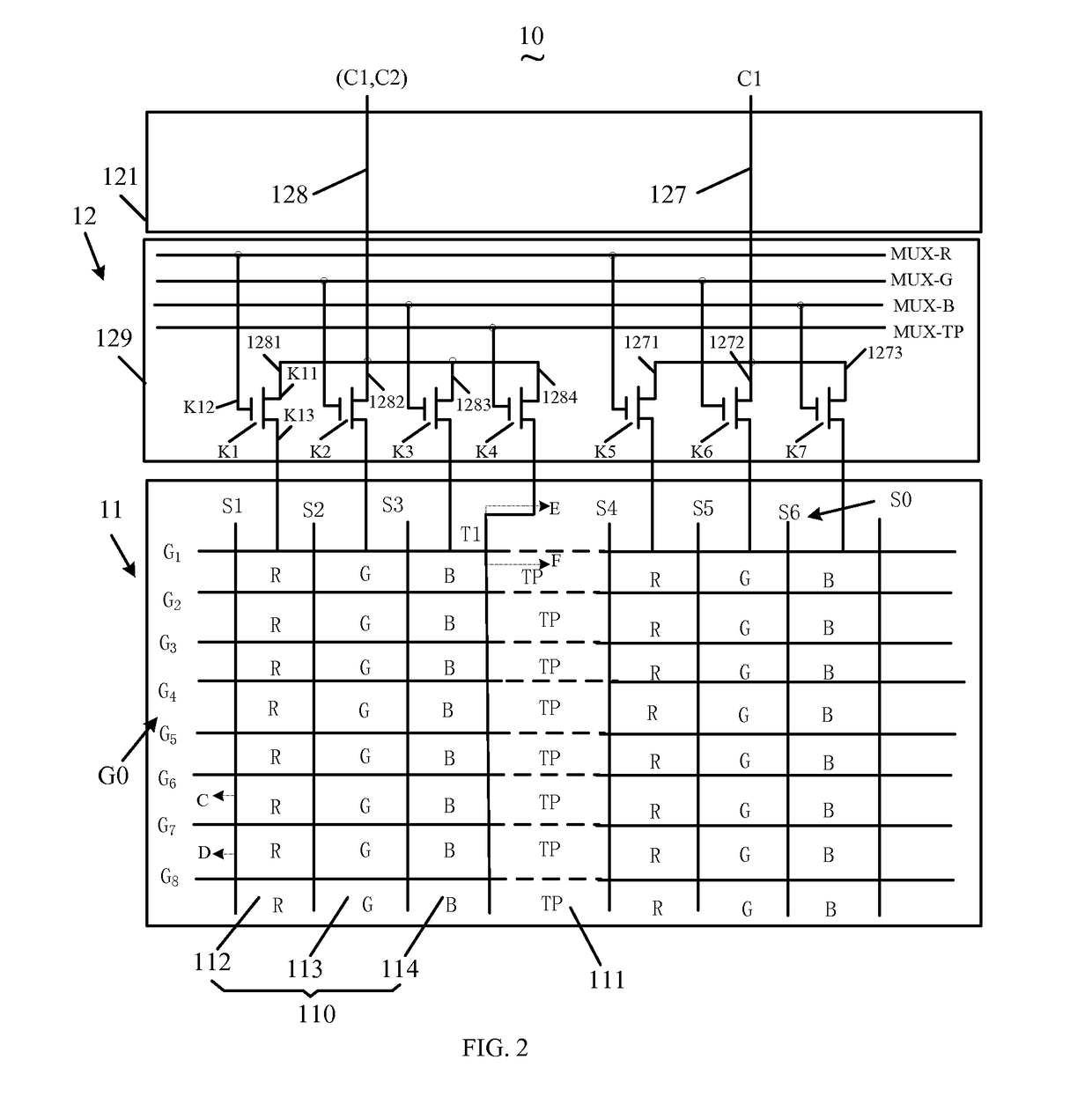

Touch display device, driving method thereof and manufacturing method thereof

InactiveUS20160062502A1Reduce thicknessReduce weightInput/output processes for data processingCapacitanceTouch Senses

A touch display device includes a substrate, a conductive layer and a transparent layer. The conductive layer is disposed on the substrate layer, and includes a plurality of metal lines, which extend along a first direction and are insulated from one another. The transparent layer is disposed on the conductive layer, and includes a plurality of first electrode strips, which extend along the first direction and individually overlap with at least one of the metal lines in a second direction substantially perpendicular to the substrate. The first electrode strips are disposed between a plurality of second electrode strips and the metal lines. The second electrode strips extend along a third direction different from the first direction and are disposed above the transparent layer. The second electrode strips form capacitance coupling with the metal lines via the first electrode strips to perform touch sensing.

Owner:ILI TECHNOLOGY CORPORATION

Touch panels and the driving method thereof

ActiveUS20170139534A1Reduce difficultyImprove performanceStatic indicating devicesNon-linear opticsCapacitanceManufacturing technology

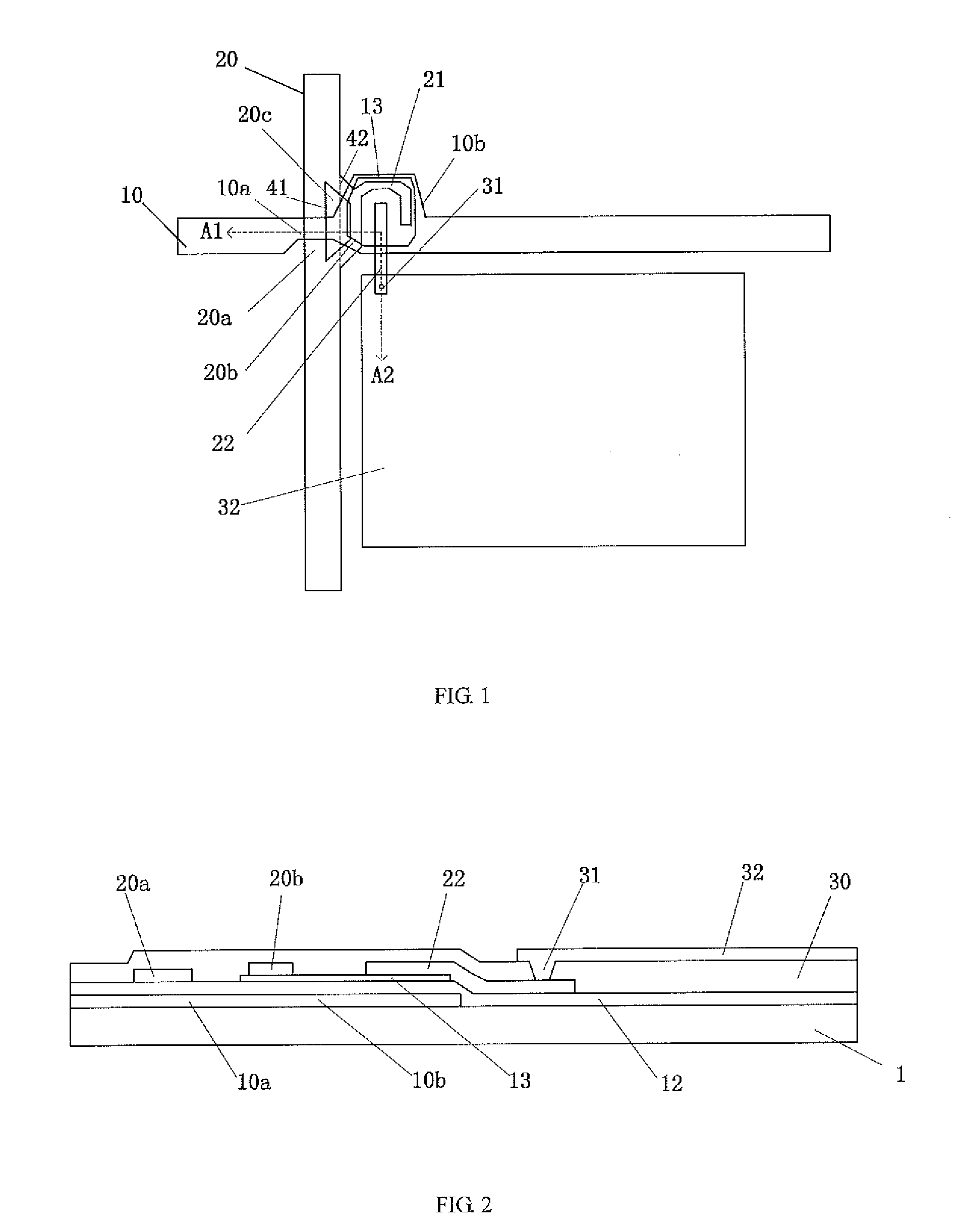

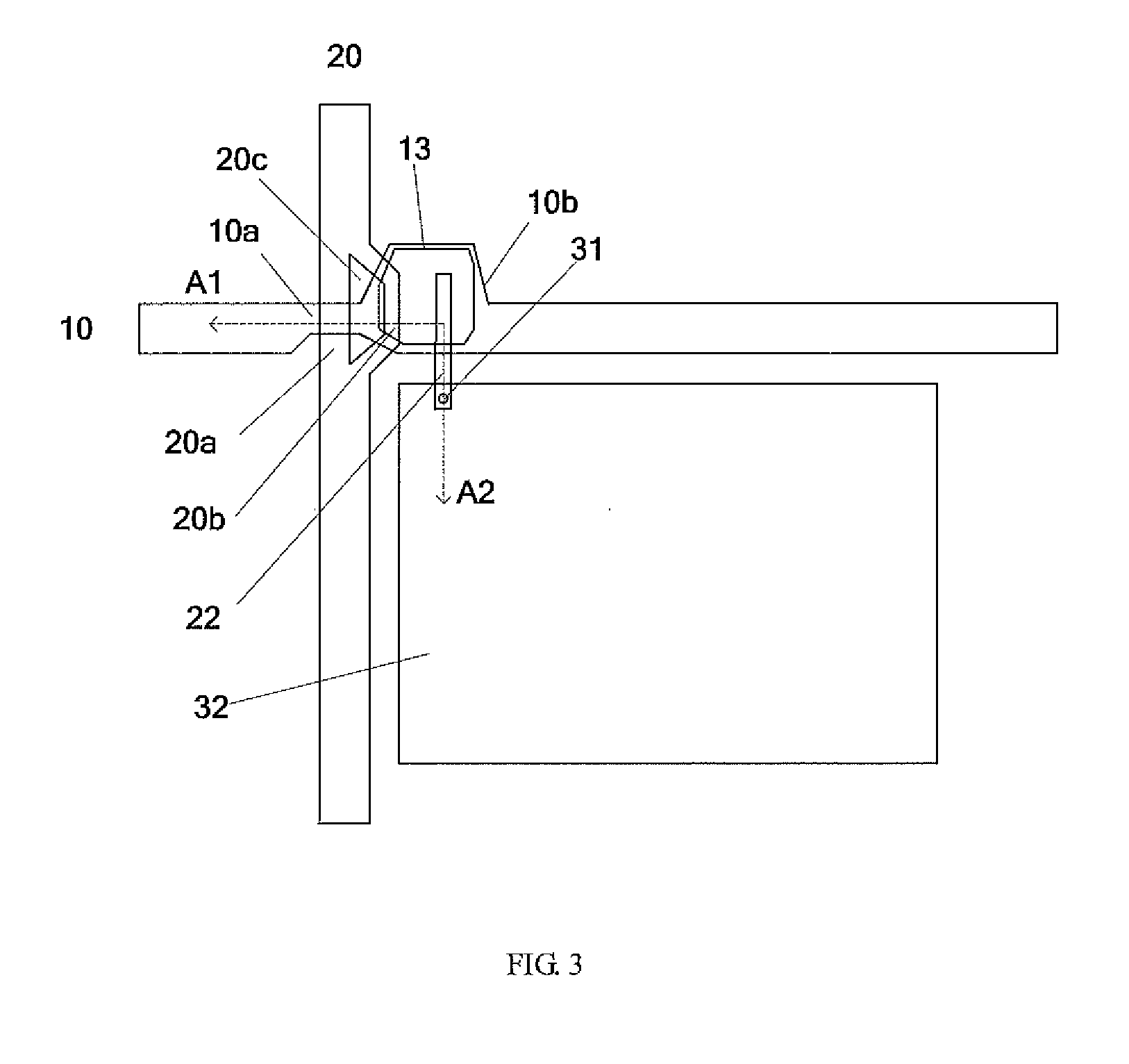

A touch panel and a driving method are described in the present disclosure. A driving chip is arranged within a chip area of a non-display area. The driving chip includes a plurality of pins. At least a portion of the pins outputs first driving signals for controlling the pixel electrodes, and outputs second driving signals for controlling the touch sensor. A plurality of wirings corresponding to the pins is arranged within the fan area, and the wirings transmit the first driving signals and the second driving signals outputted by the pins. In view of the above, the difficulties of the bonding manufacturing process are reduced. At the same time, the coupling capacitance between the wirings is reduced, and thus the display performance and the touch sensibility of the touch panel 10 are enhanced.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD +1

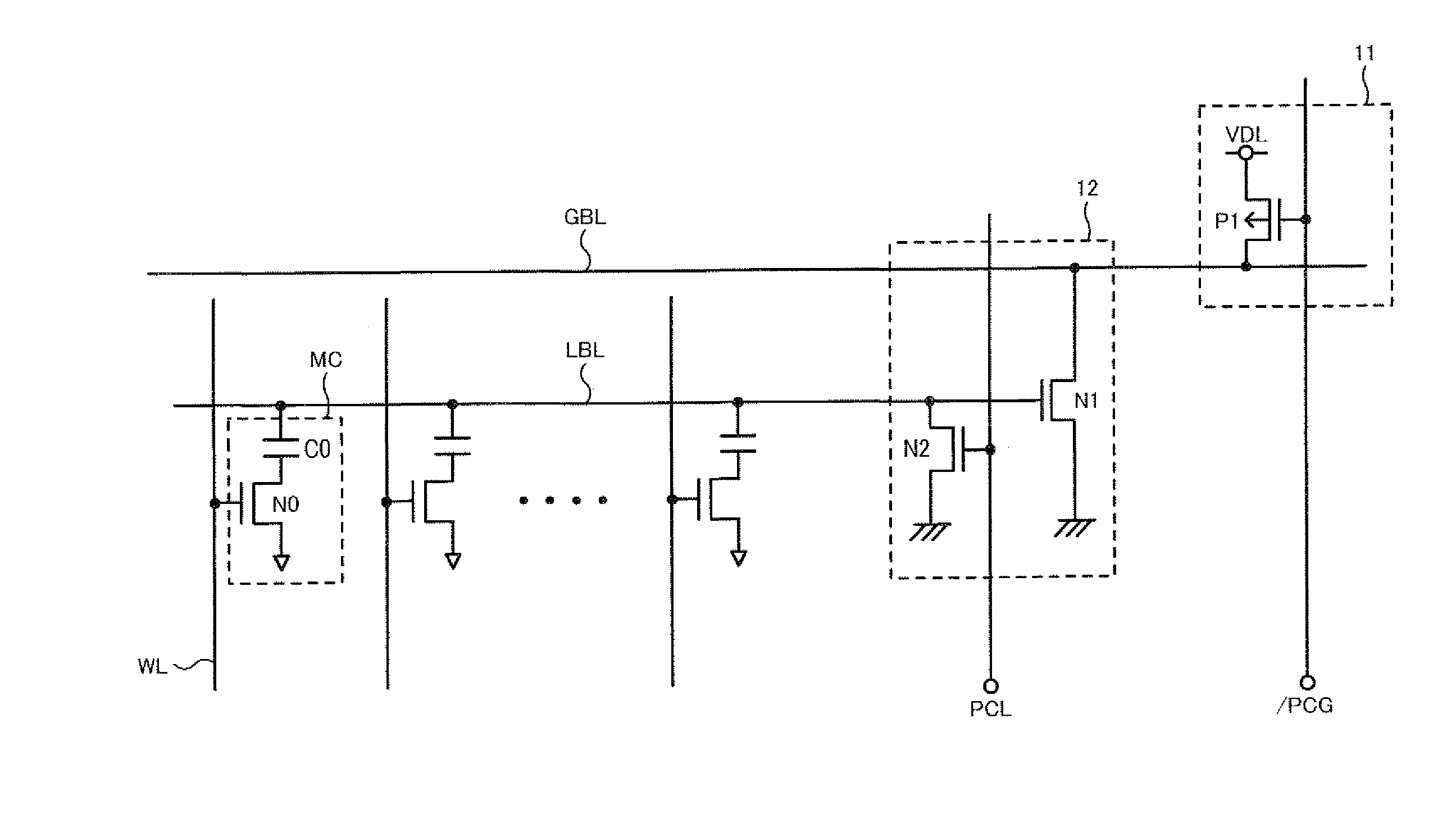

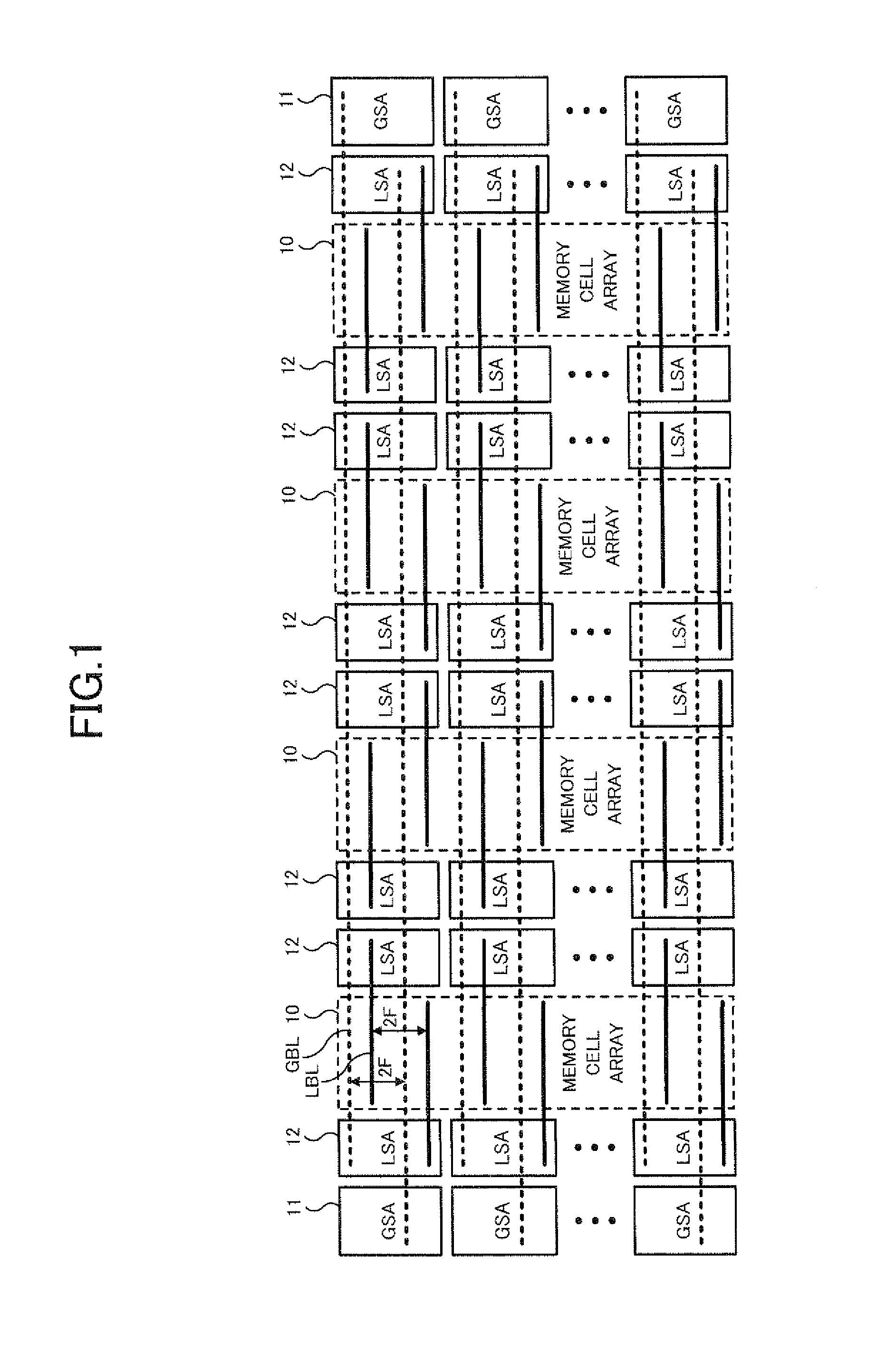

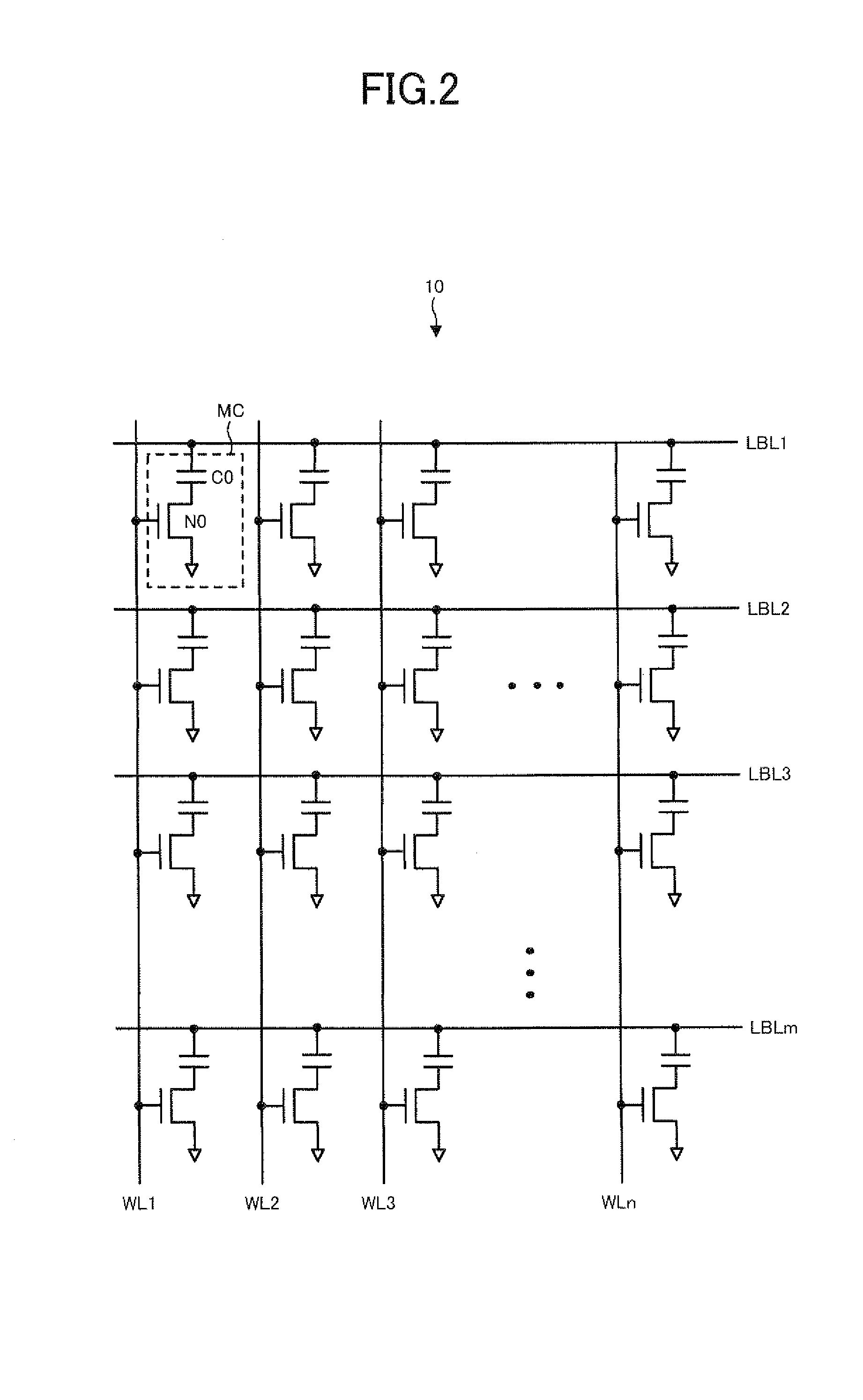

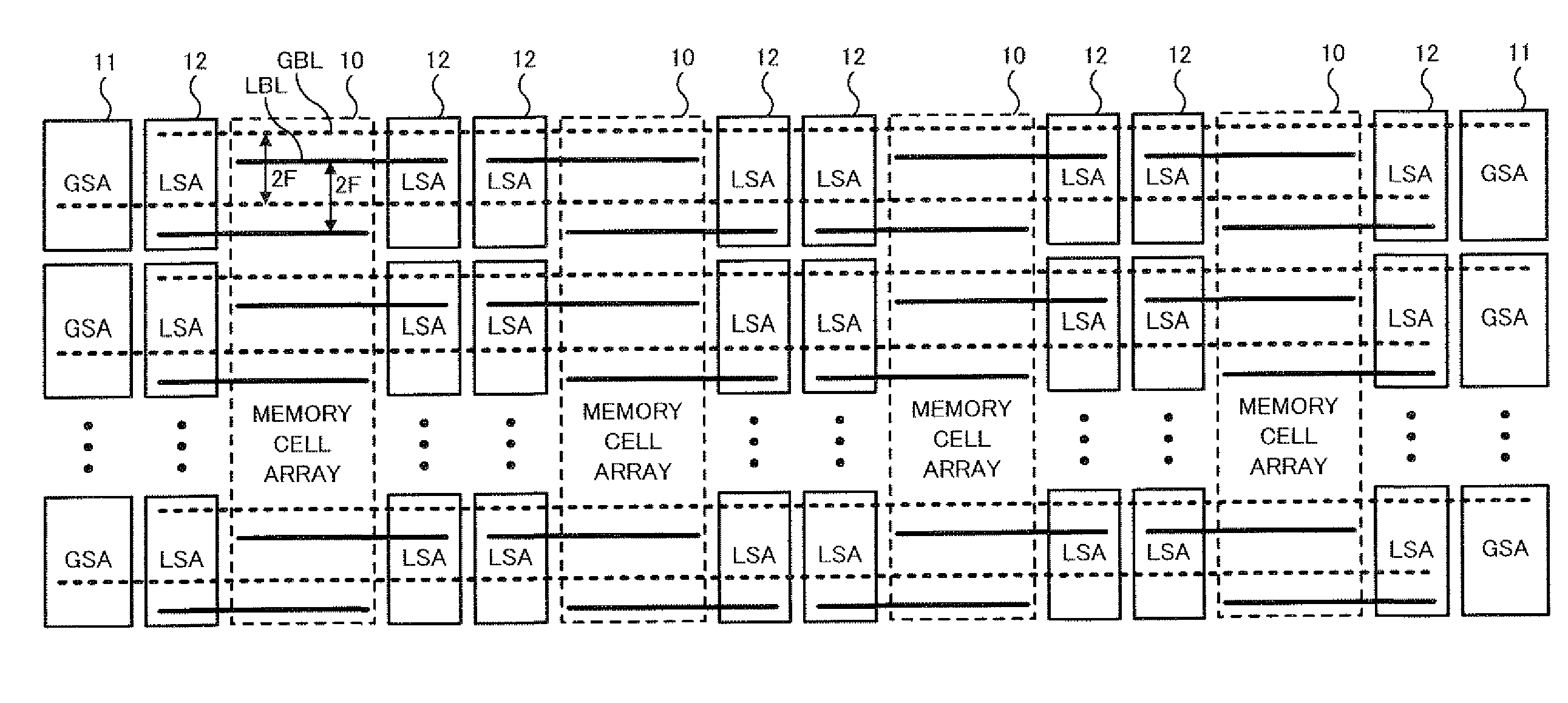

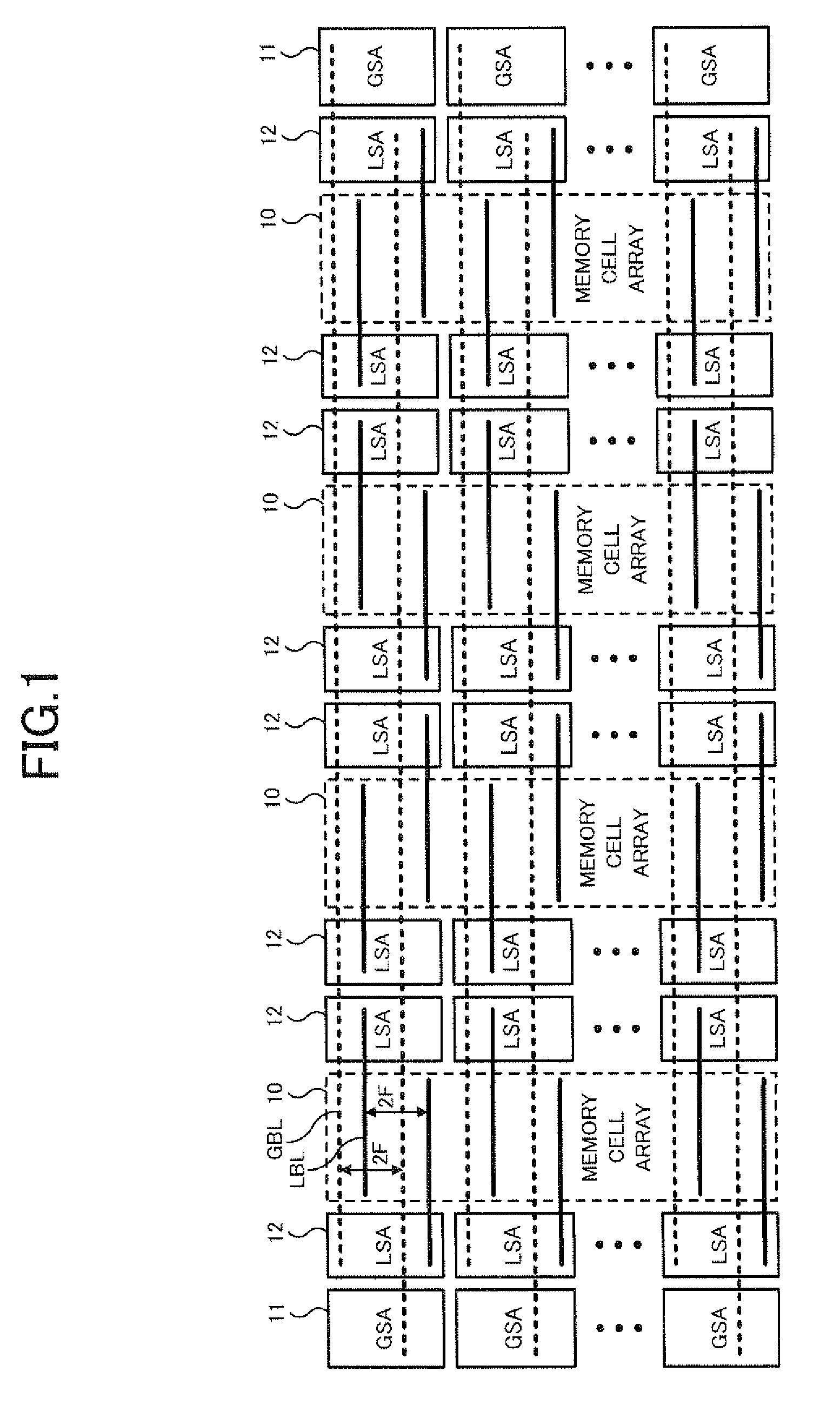

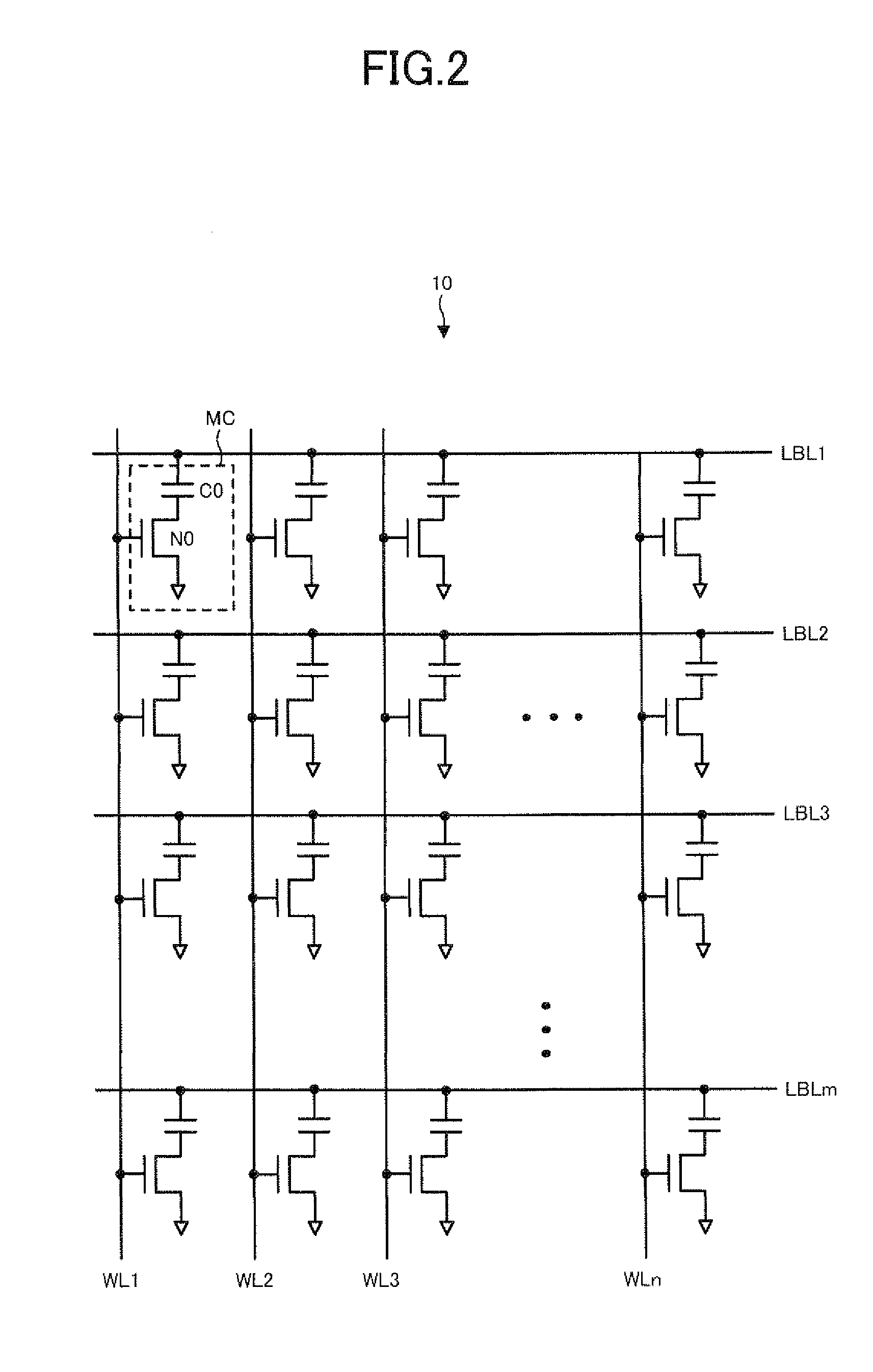

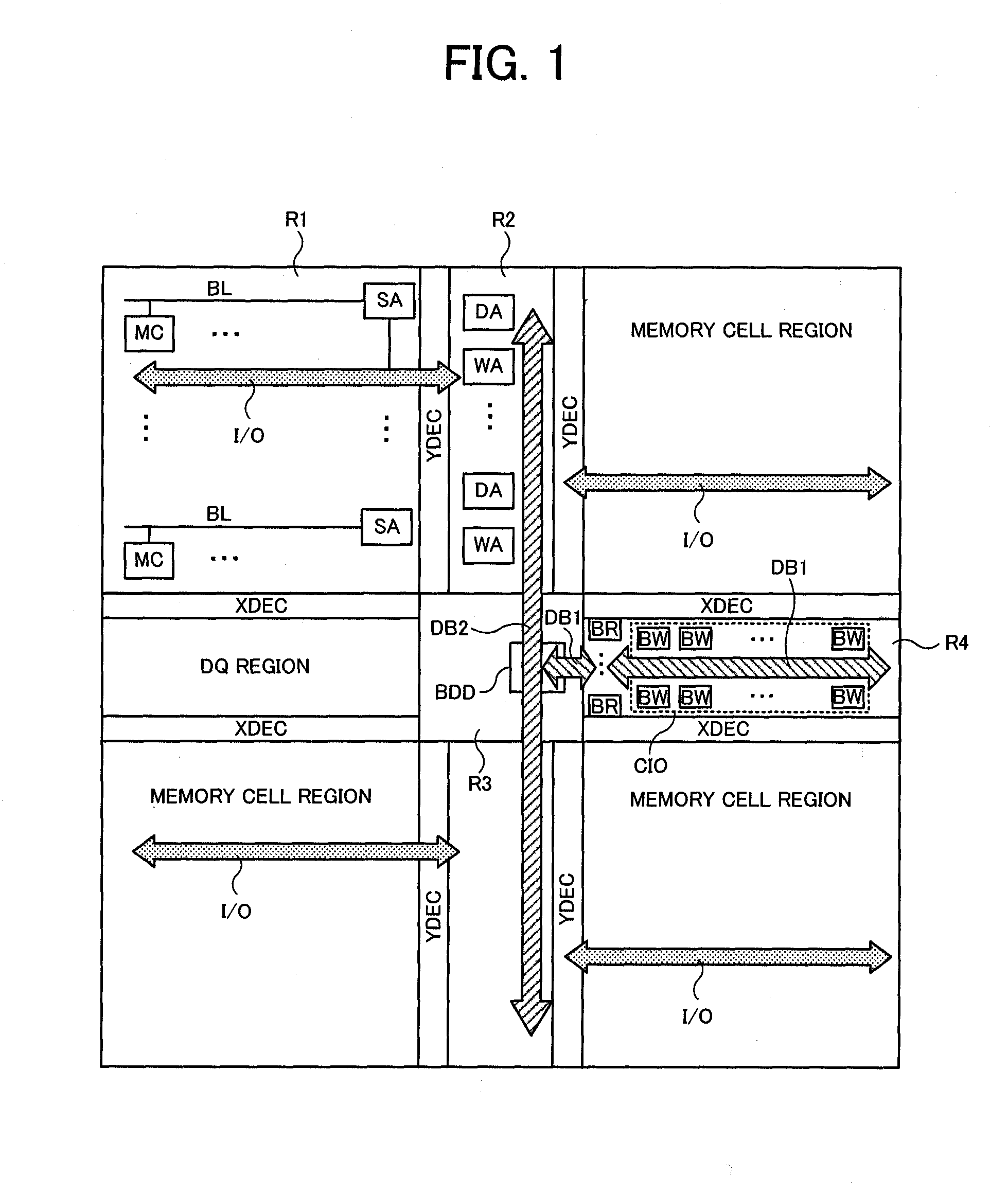

Semiconductor memory device

A semiconductor memory device comprises. word lines; global bit lines intersecting with the word lines; local bit lines partitioned into N (N is an integer greater than or equal to two) sections along the global bit lines and aligned with a same pitch as the global bit lines; N memory cell arrays each including memory cells each having cylindrical capacitor structure formed at intersections of the word lines and the local bit lines and being arranged corresponding to the sections of the local bit lines; local sense amplifiers for amplifying a signal read out from a selected memory cell to the local bit line and for outputting the signal to the global bit line; and global sense amplifiers for coupling the signal transmitted from the local sense amplifier corresponding to the selected memory cell through the global bit line to an external data line.

Owner:LONGITUDE LICENSING LTD

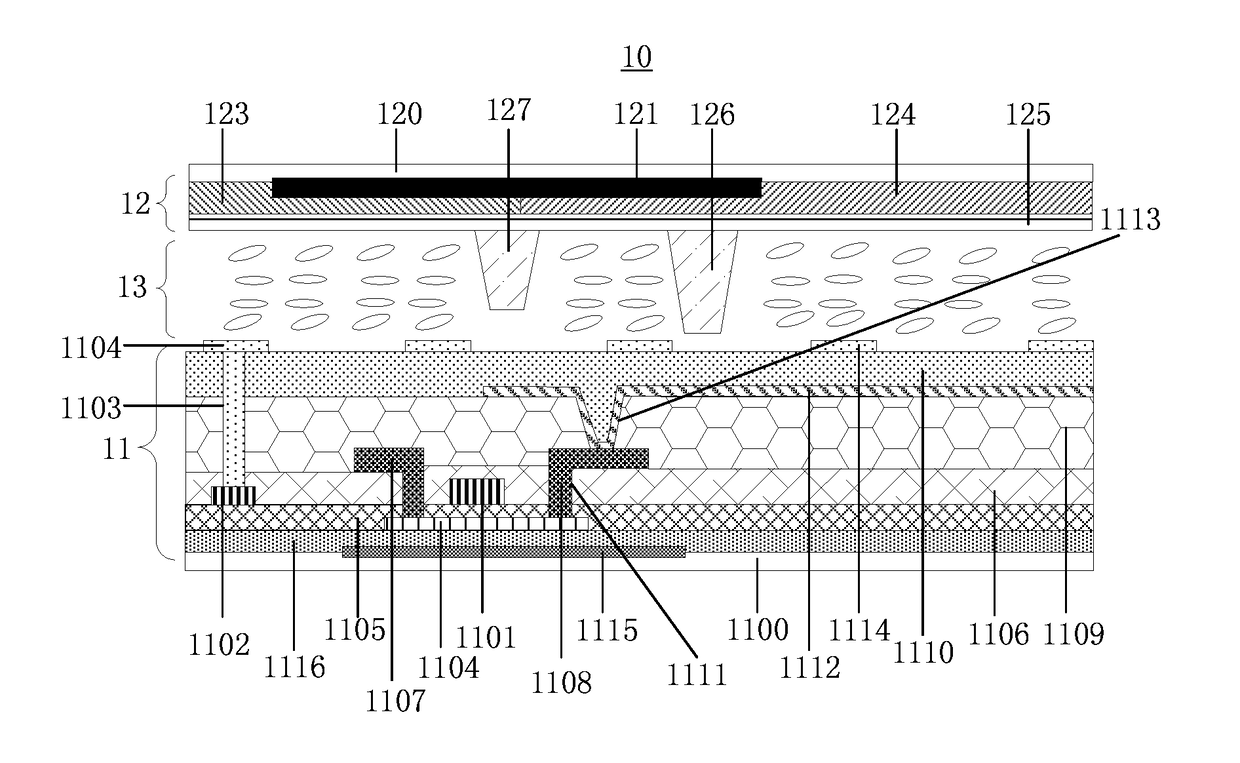

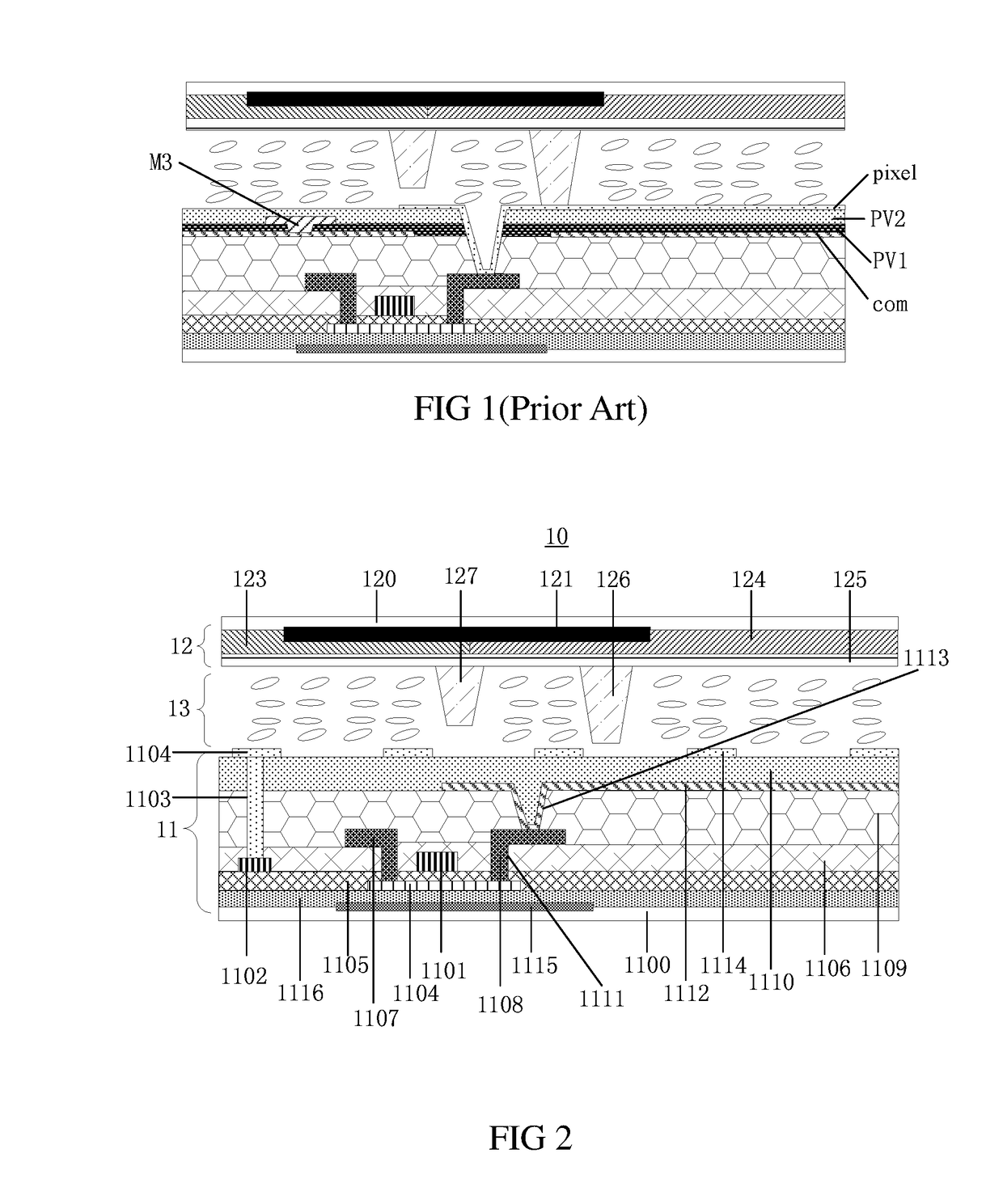

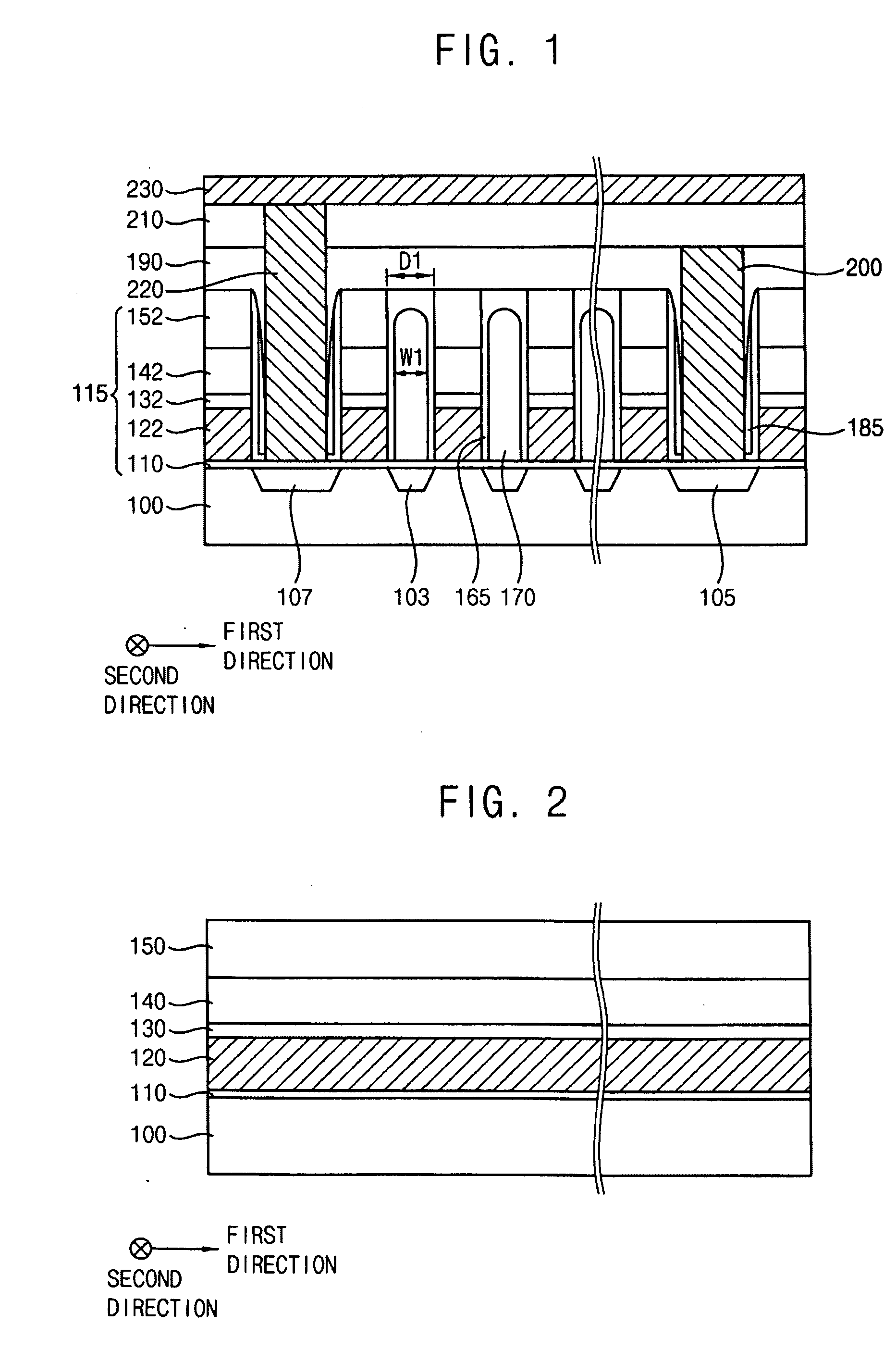

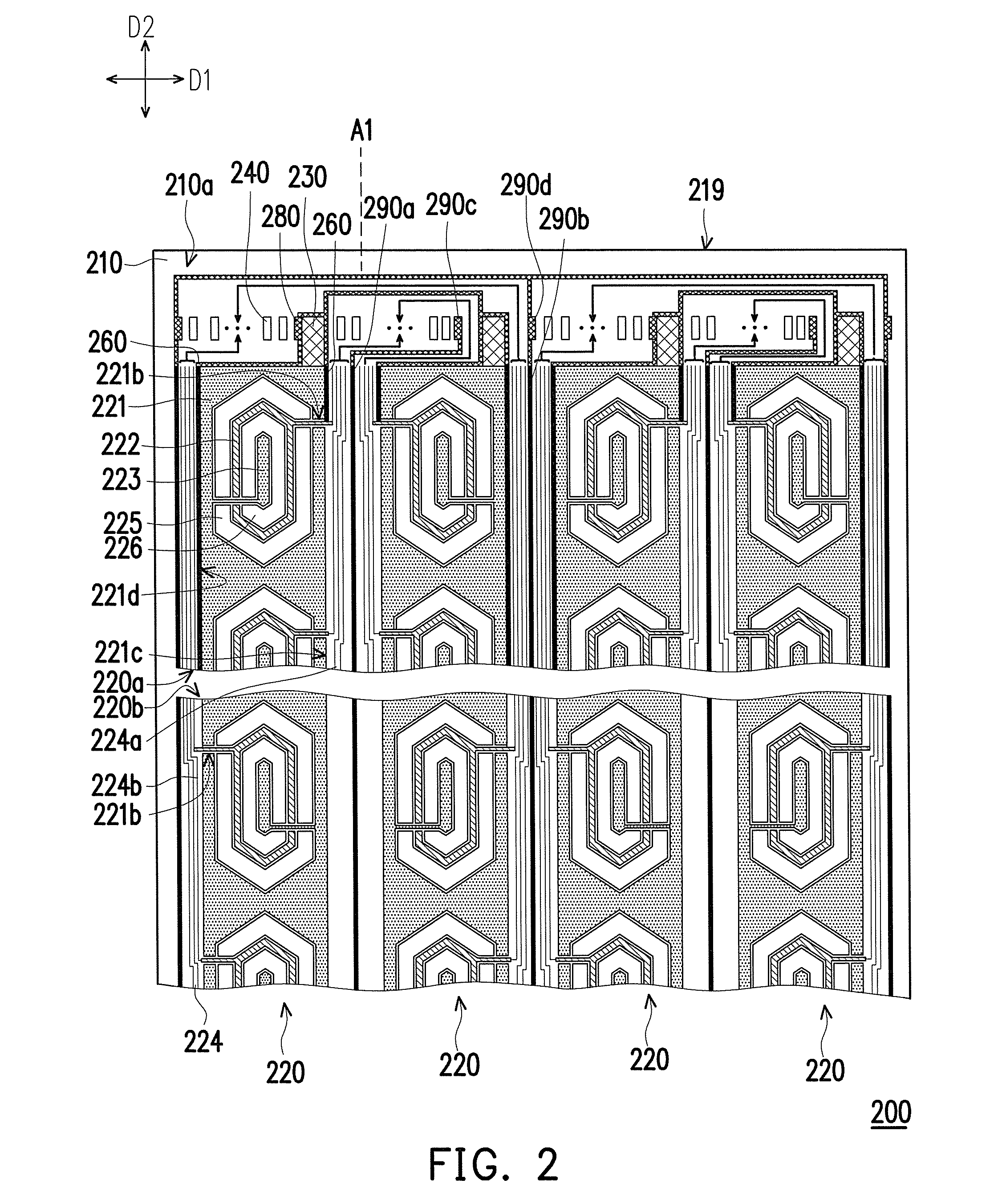

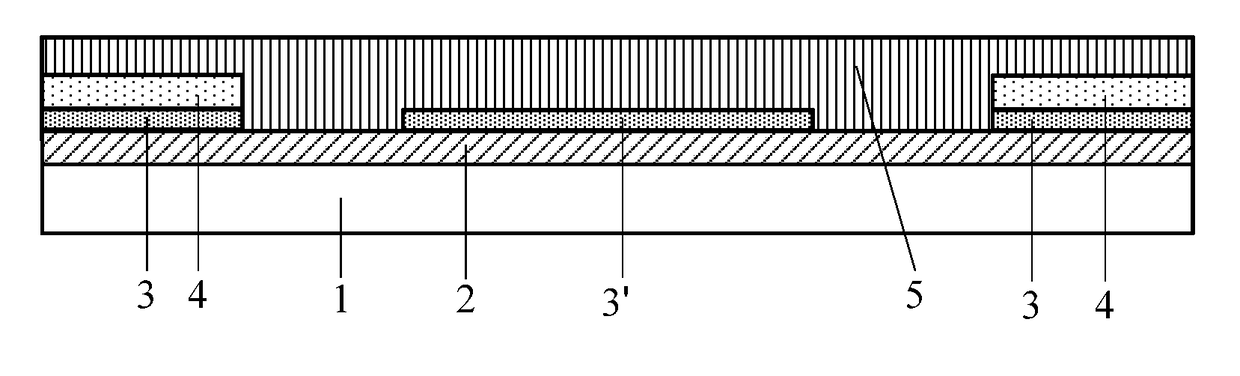

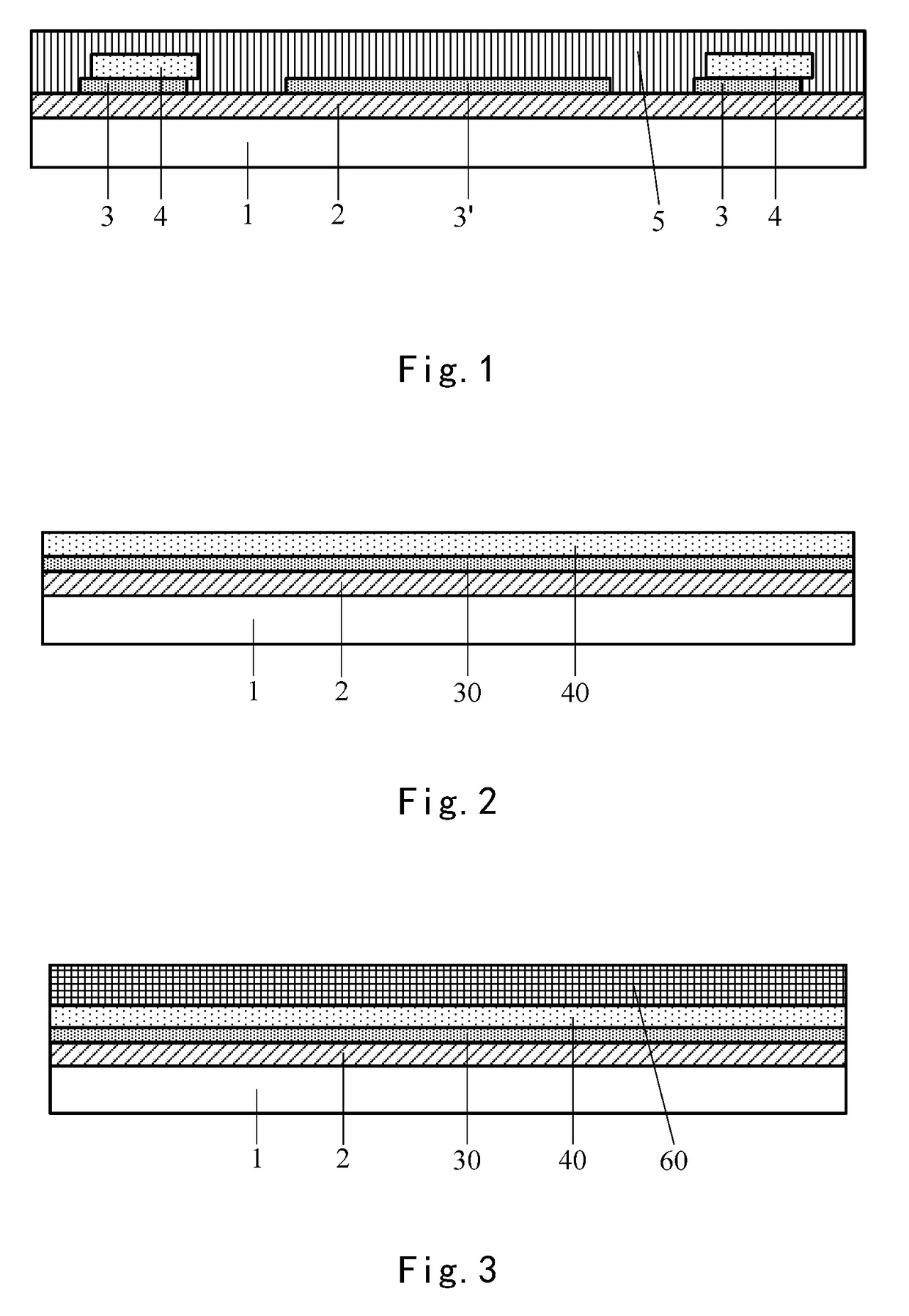

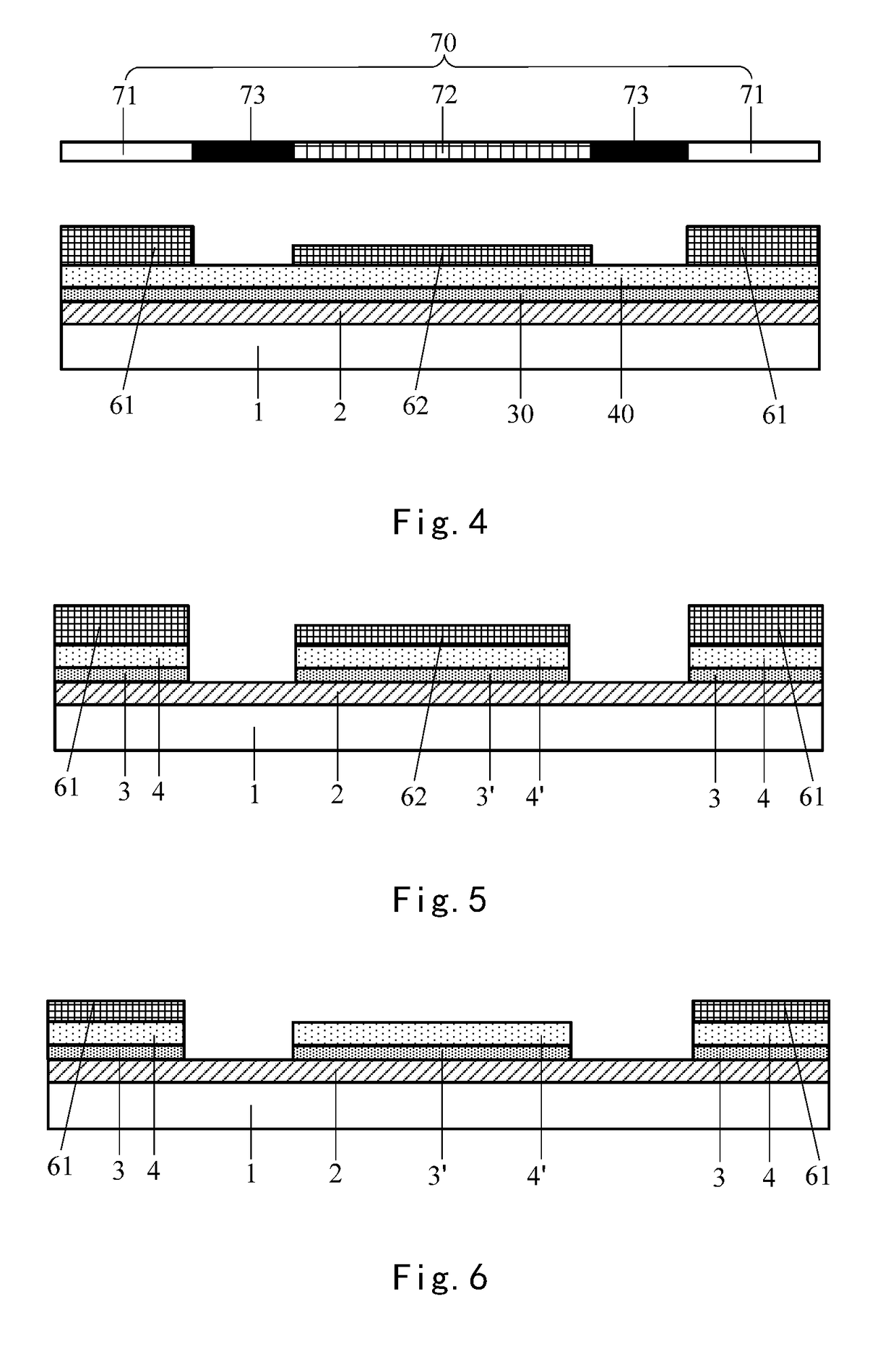

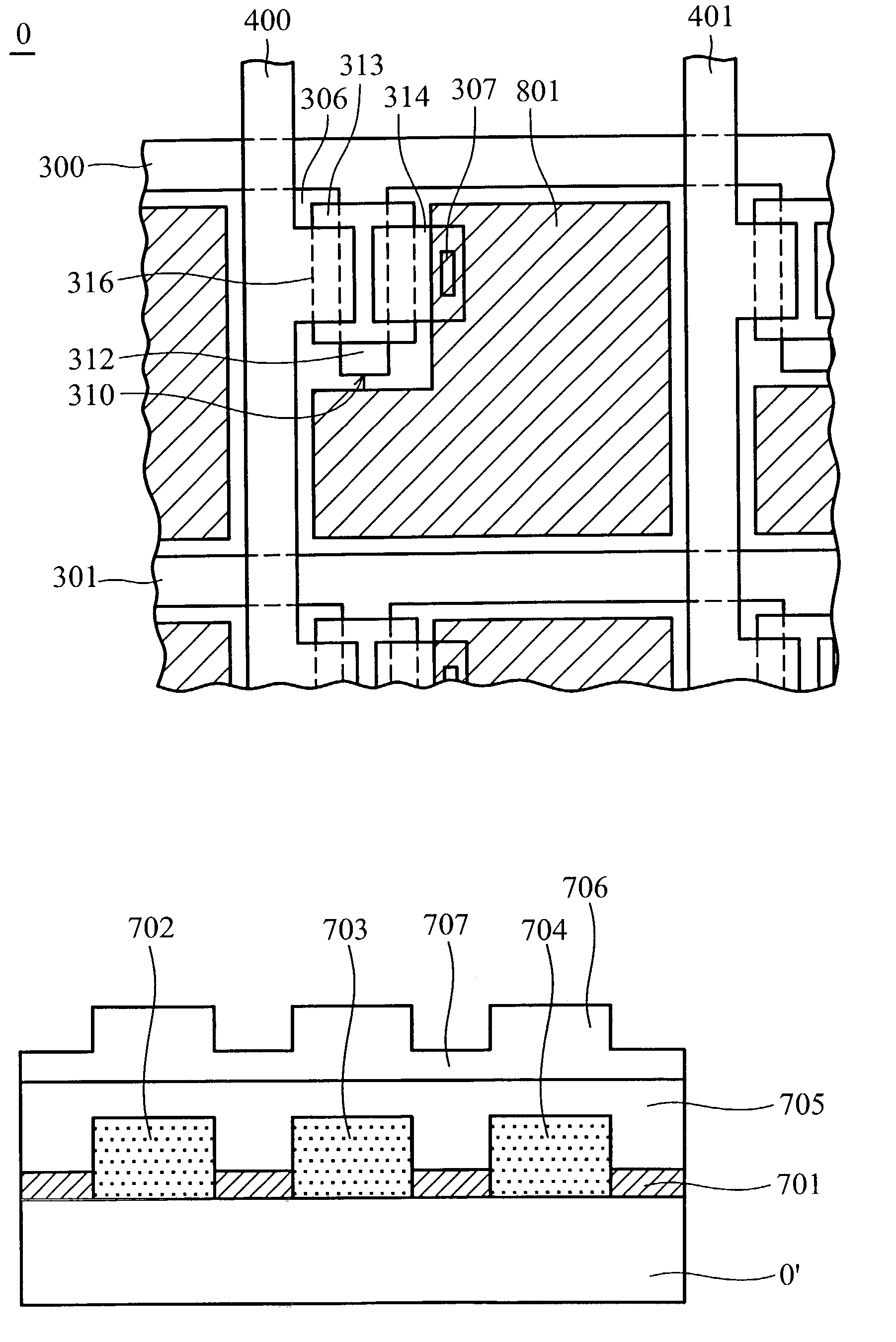

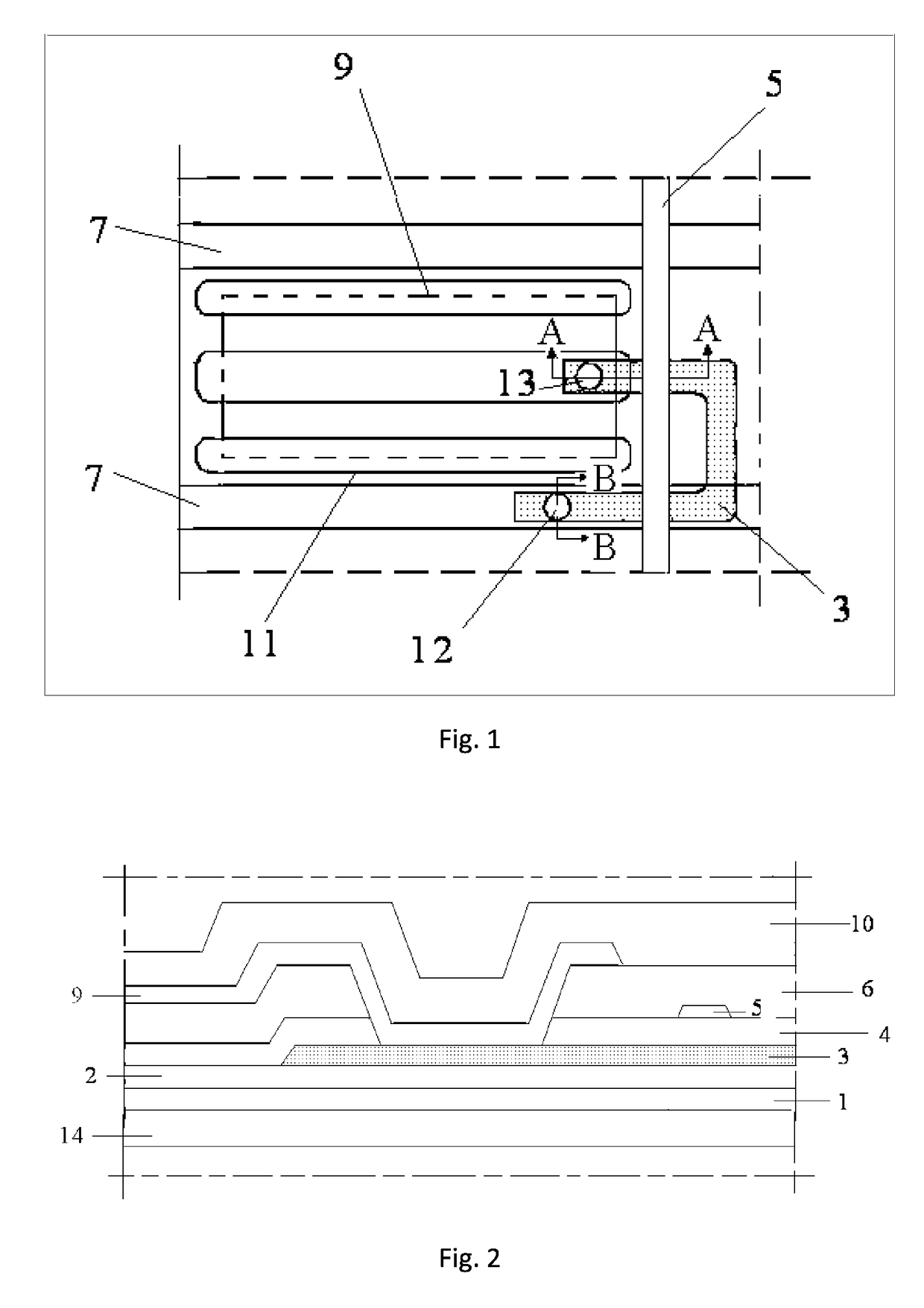

Array substrates and the manufacturing methods thereof, and liquid crystal panels

InactiveUS20180188581A1Storage capacitance is increasedCoupling capacitanceNon-linear opticsInput/output processes for data processingCapacitanceLiquid crystal

The present disclosure relates to an array substrate and the manufacturing method thereof, and a liquid crystal panel. The array substrate includes a transparent substrate; a gate line on the transparent substrate; a touch signal line on the same layer with the gate line, and the touch signal line is arranged on the transparent substrate; a dielectric layer covering the gate line and the touch signal line, and the dielectric layer is configured with at least one first through hole; and a touch electrode arranged on the dielectric layer, the touch electrode electrically connects to the touch signal line via the first through hole. In this way, the storage capacitance may be increased, and the pixels may be fully charged when the resolution rate is high. At the same time, the coupling capacitance between the touch electrode and the Rx signal line may be reduced.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

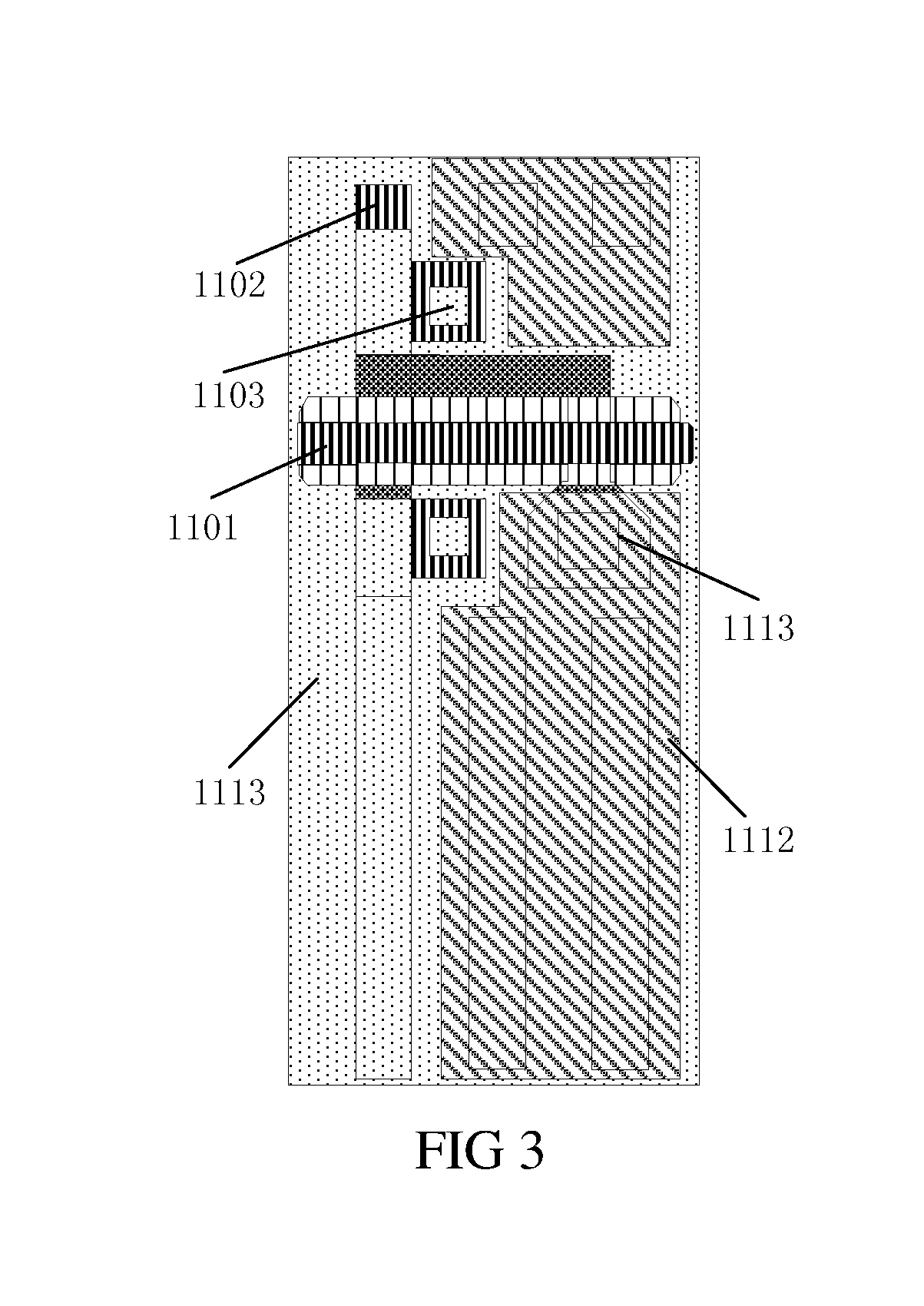

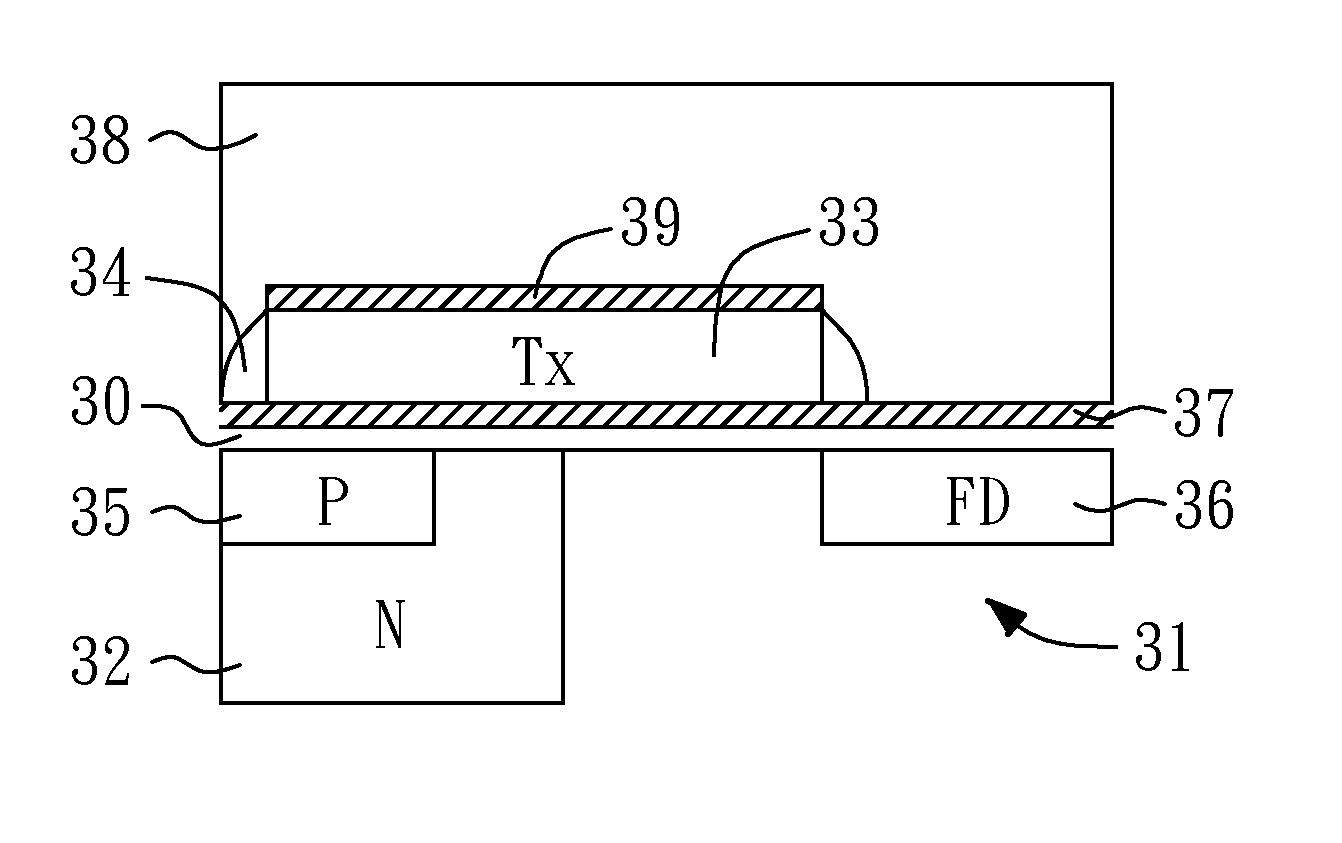

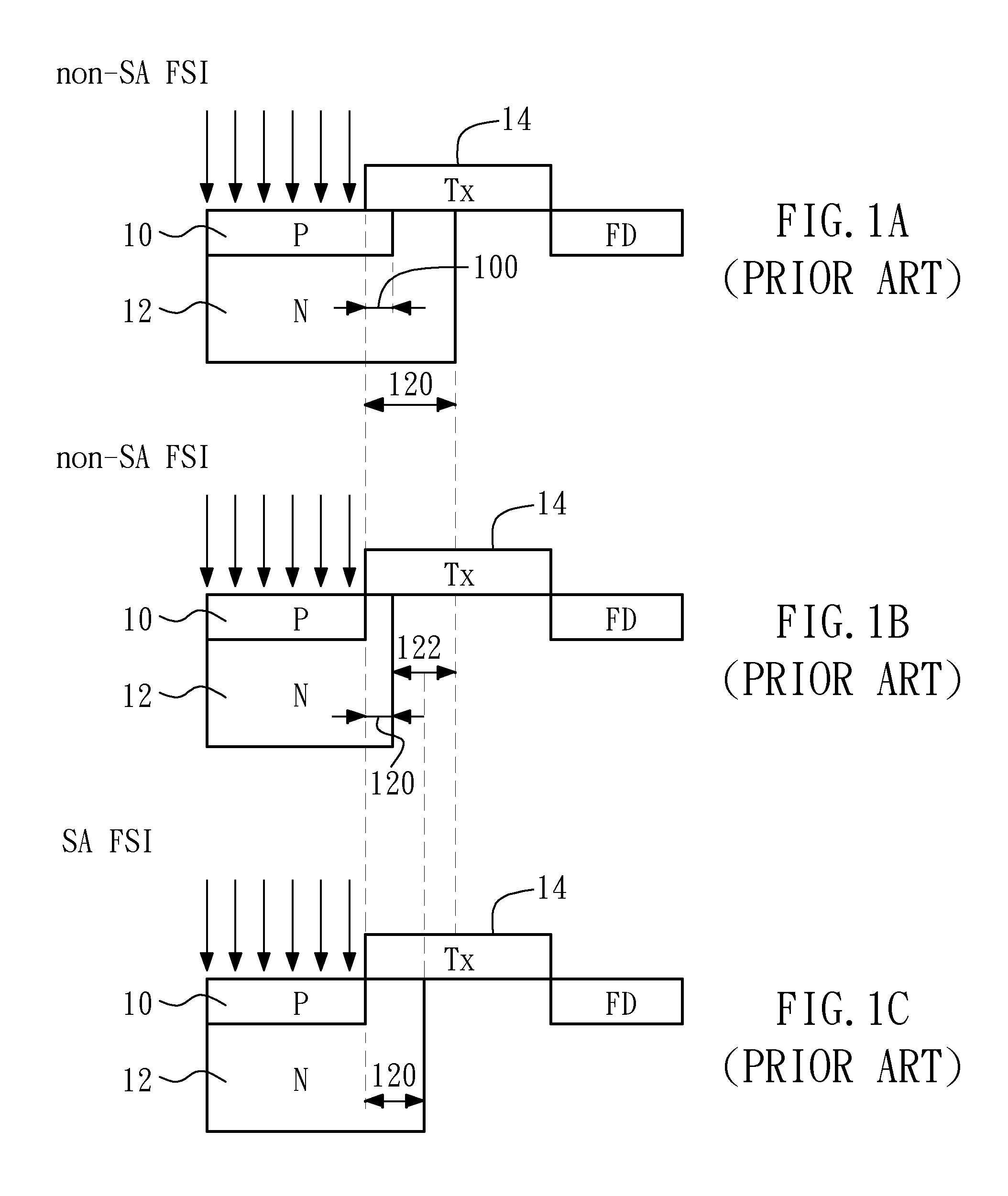

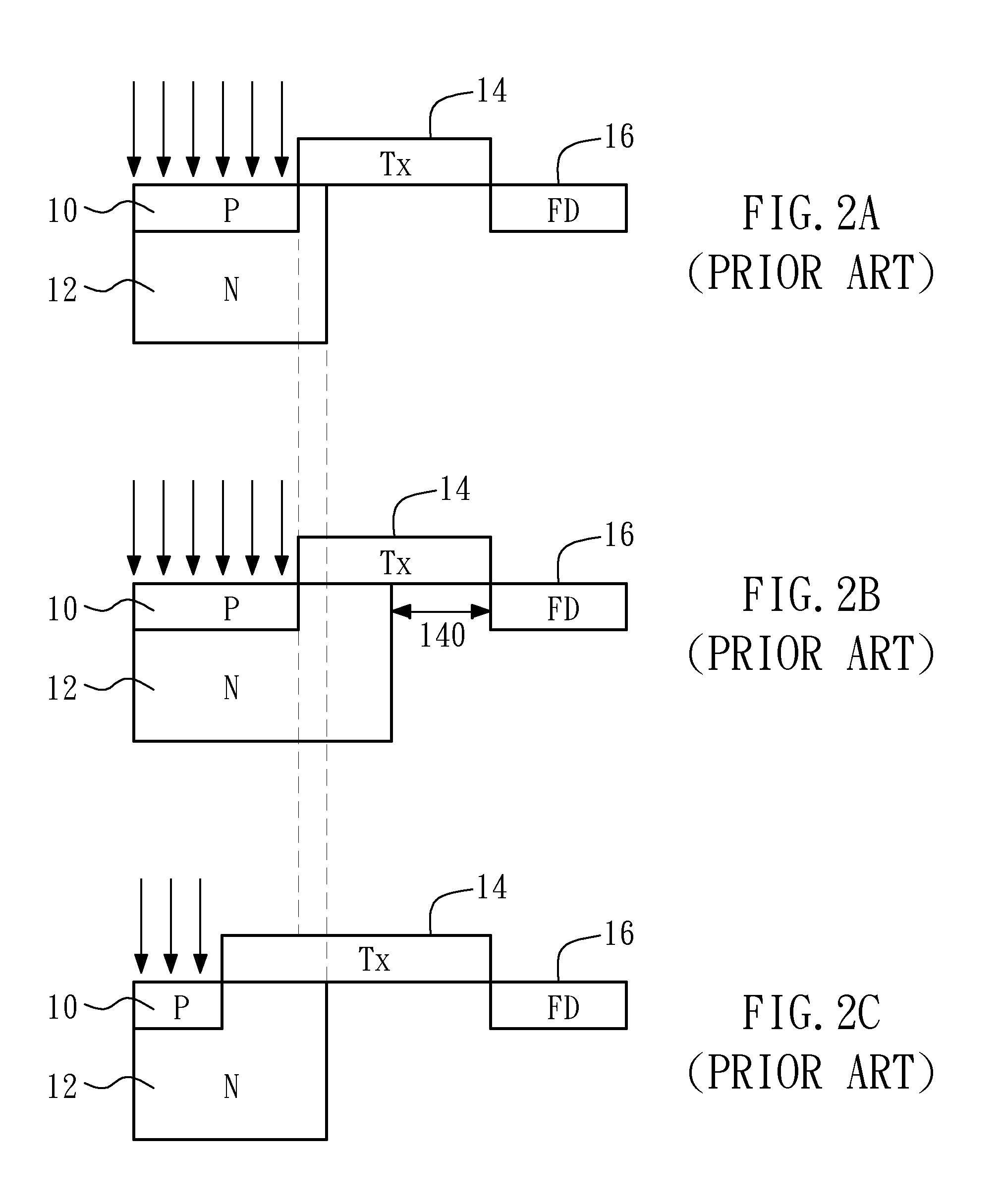

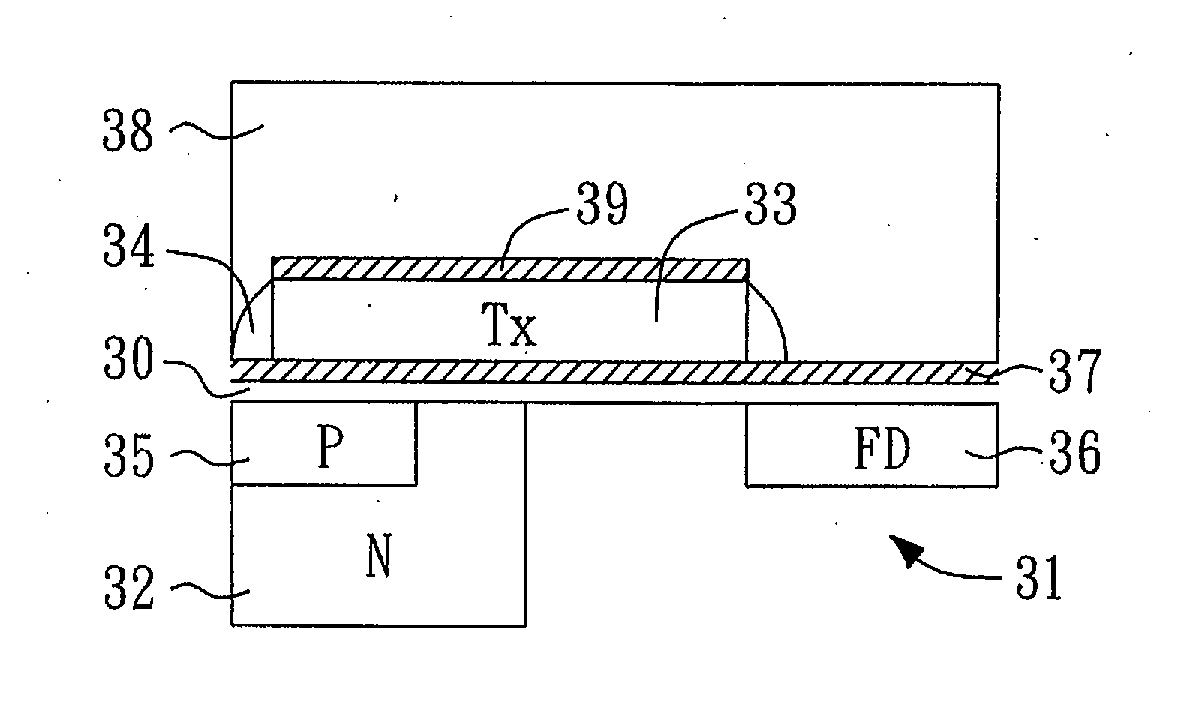

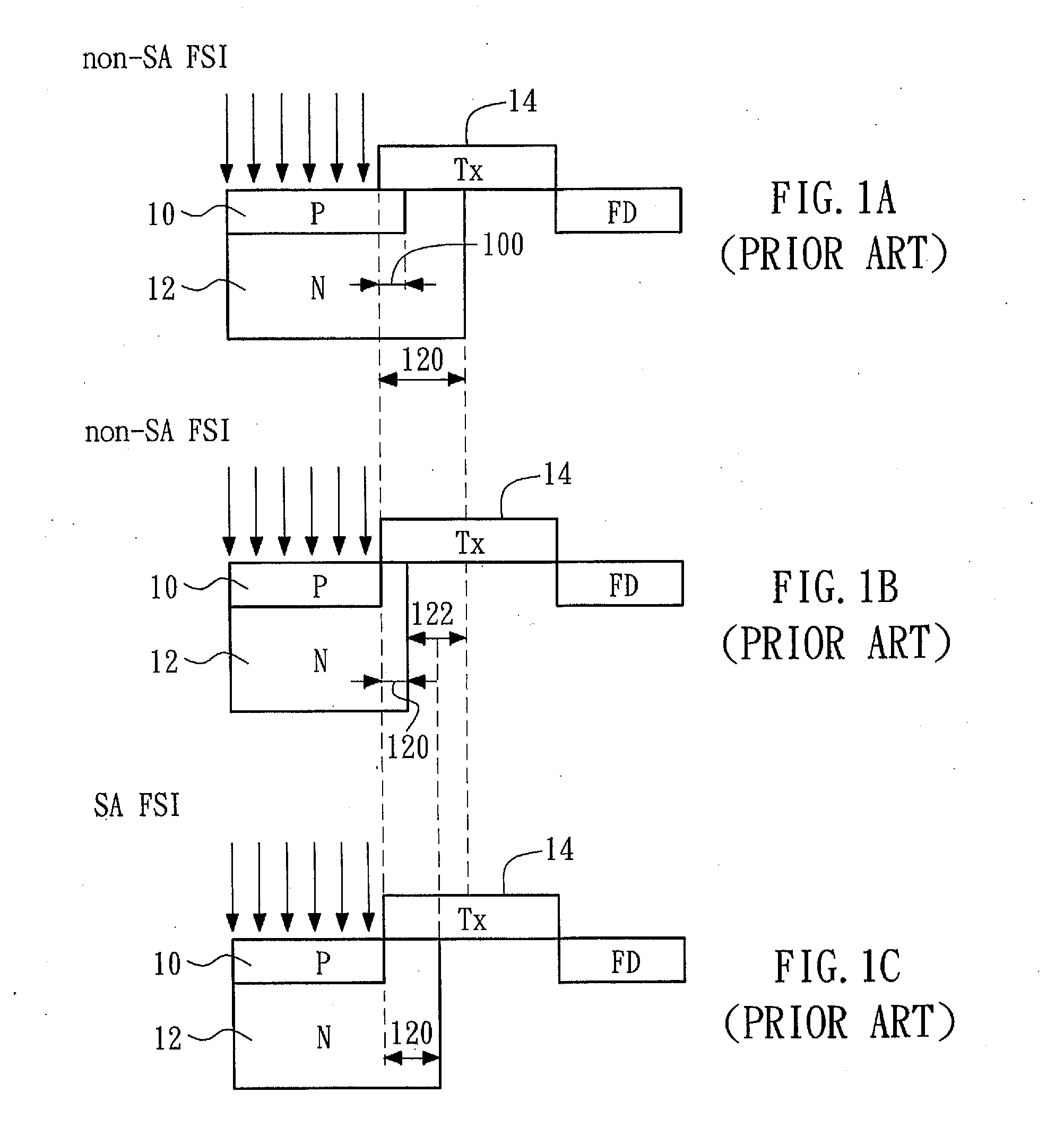

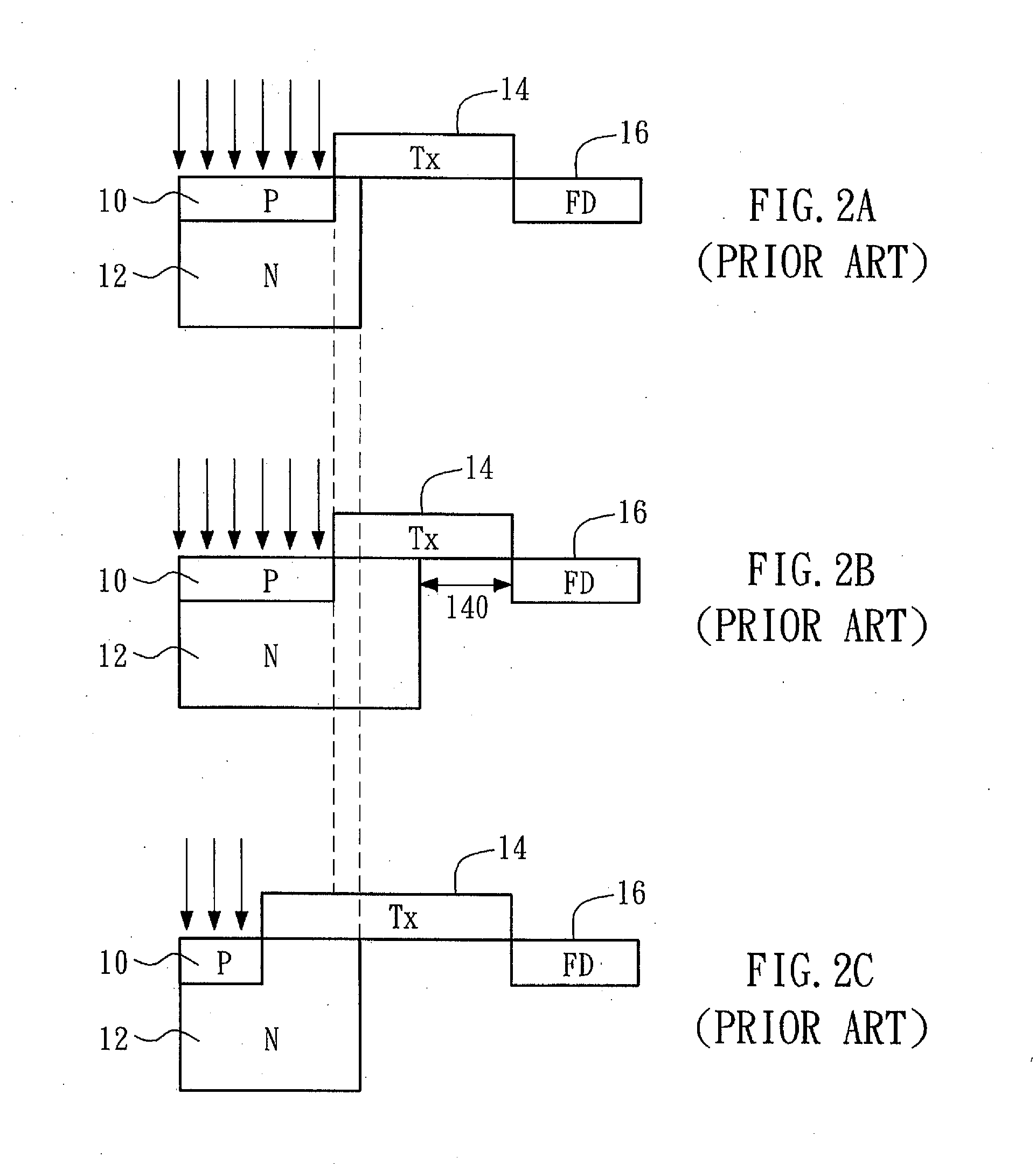

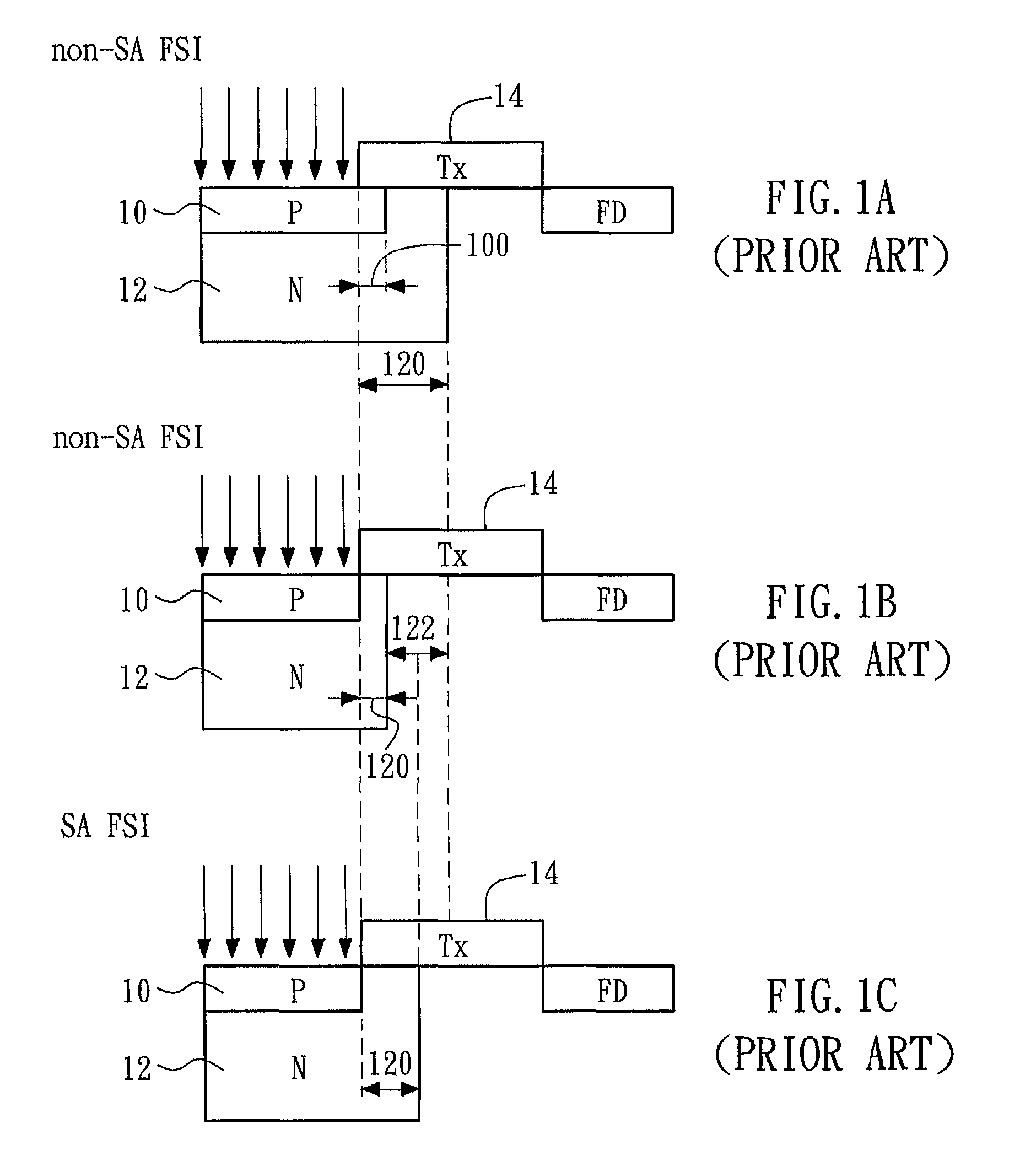

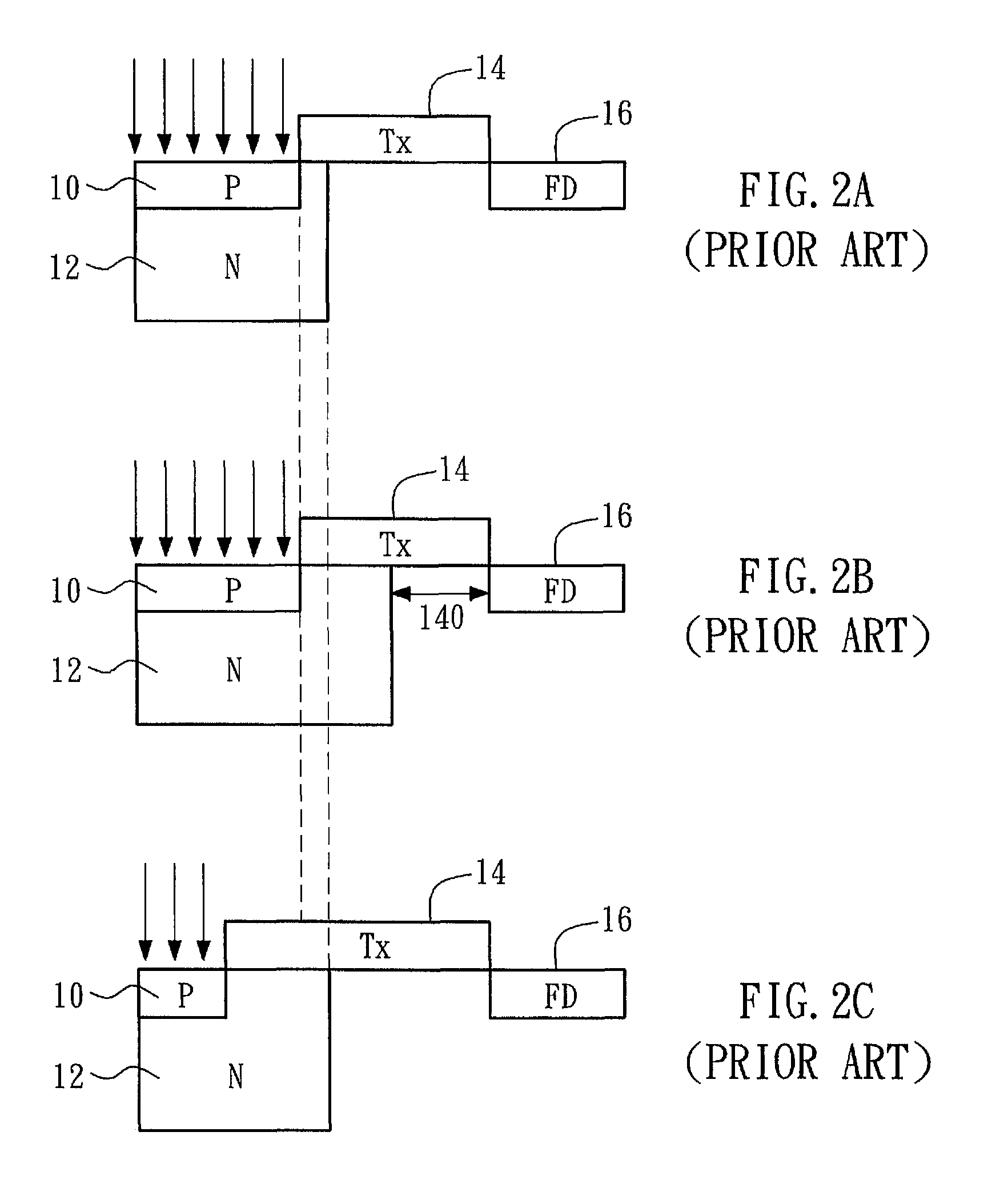

Back side illumination image sensor and a process thereof

ActiveUS20110169055A1Increase overlapAccelerate the accumulation processTransistorSolid-state devicesSemiconductorImage sensor

A process and structure of a back side illumination (BSI) image sensor are disclosed. An n-type doped region is formed in a substrate, and a transfer gate is formed on top of the semiconductor substrate. A p-type doped region is formed in the n-type doped region either using the transfer gate as a mask or is non-self aligned formed.

Owner:HIMAX IMAGING LIMITED

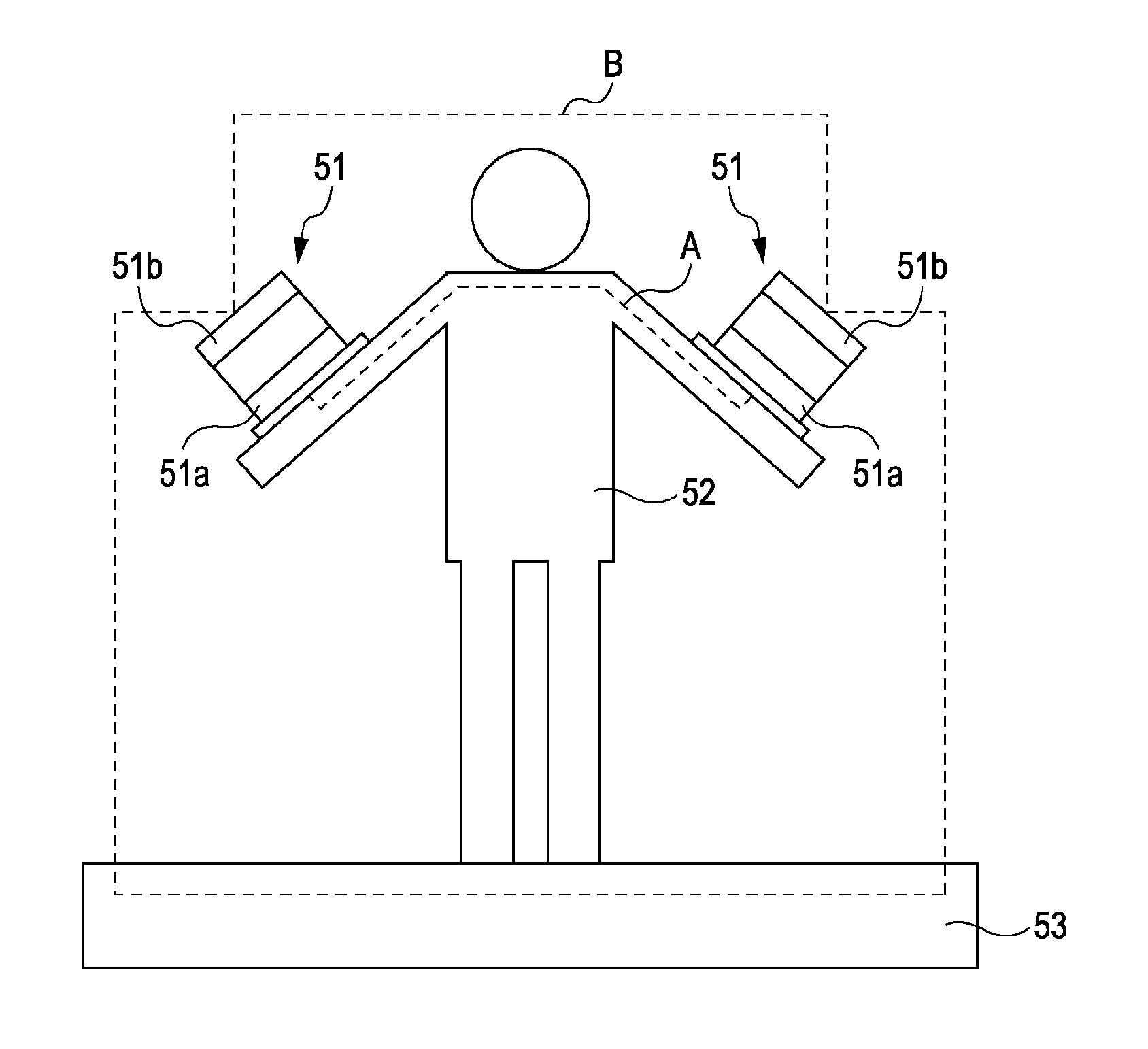

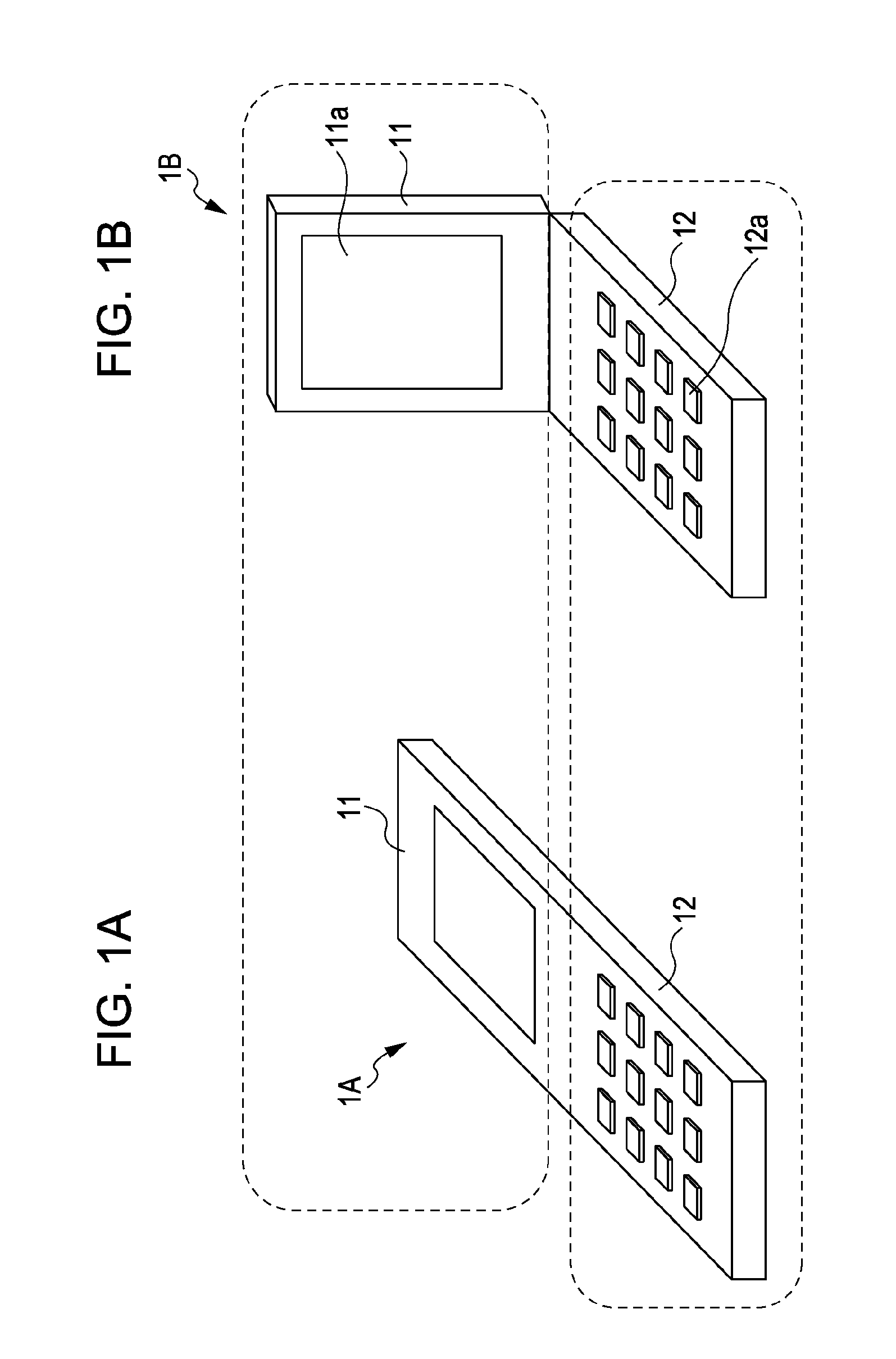

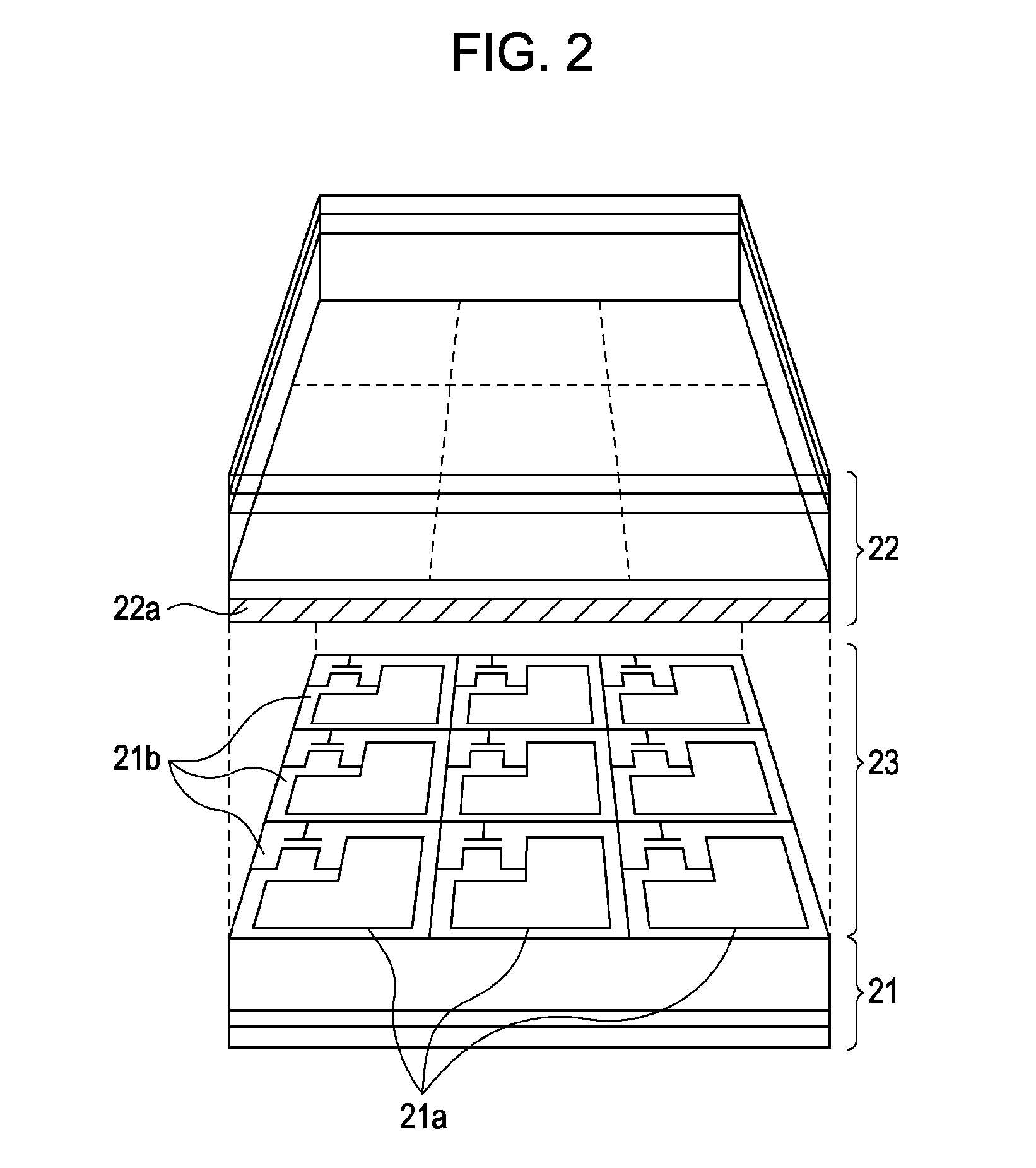

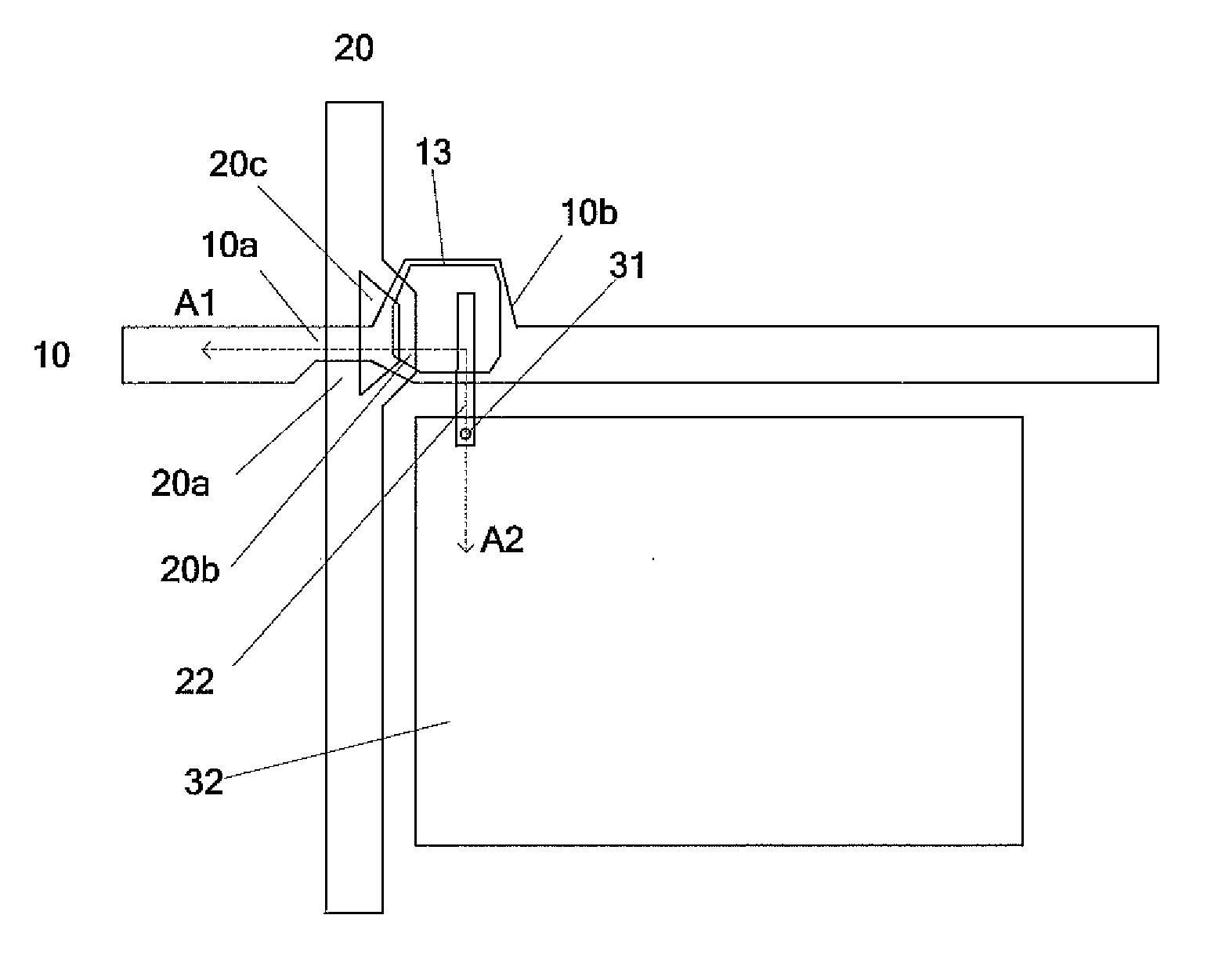

Information terminal device

InactiveUS20100184373A1Improve qualityReduce lossNear-field transmissionBiomedical engineeringElectrode pair

A mobile phone includes a display unit for visually confirming the information and an input unit for inputting the information. The display unit includes a display element, and the input unit includes an operation button. The mobile phone contains an electrode pair formed of a human side electrode and an external electrode for human body communication inside the casing. The mobile phone has the external electrode disposed around the display unit, and the human side electrode disposed around the input unit.

Owner:ALPS ALPINE CO LTD

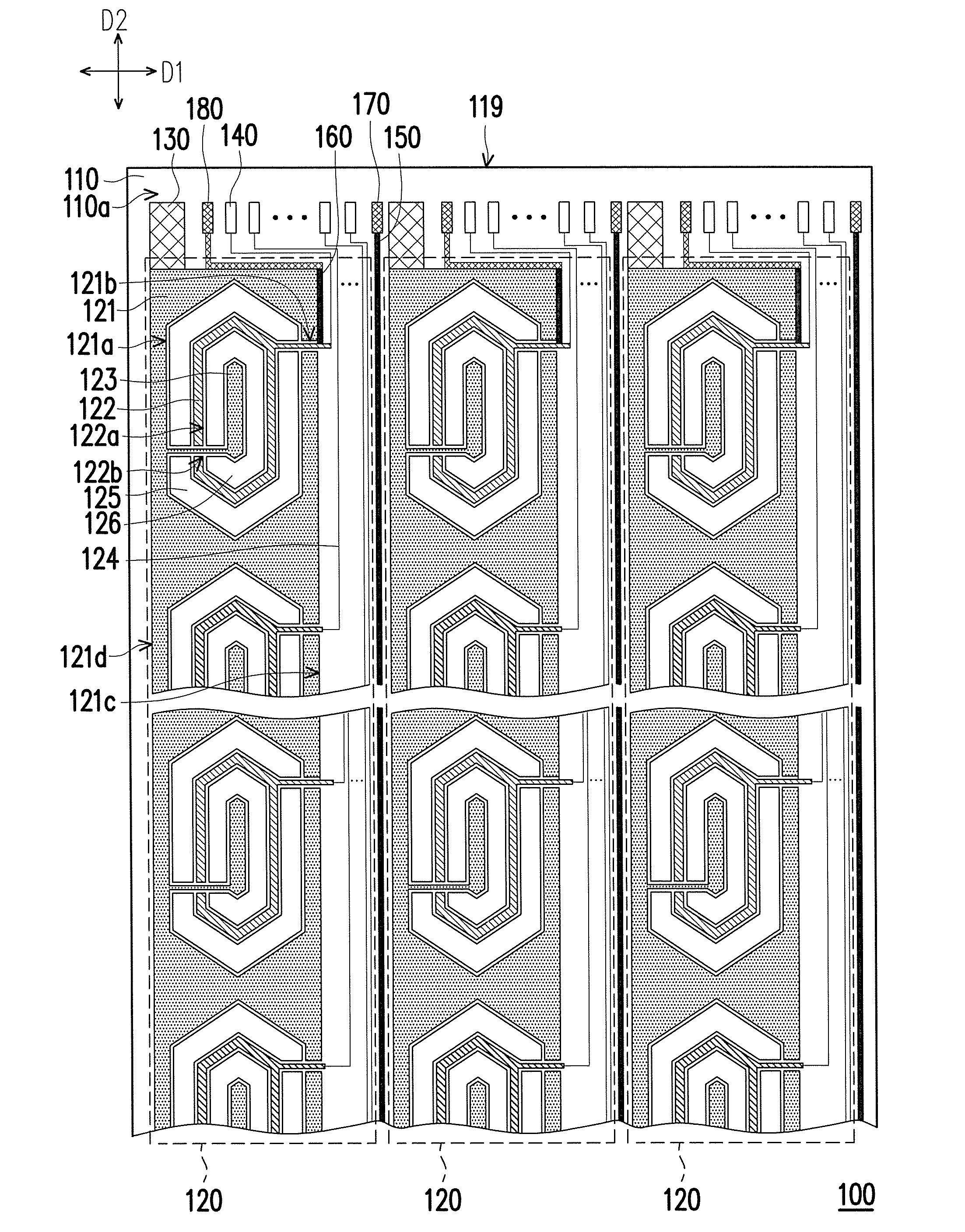

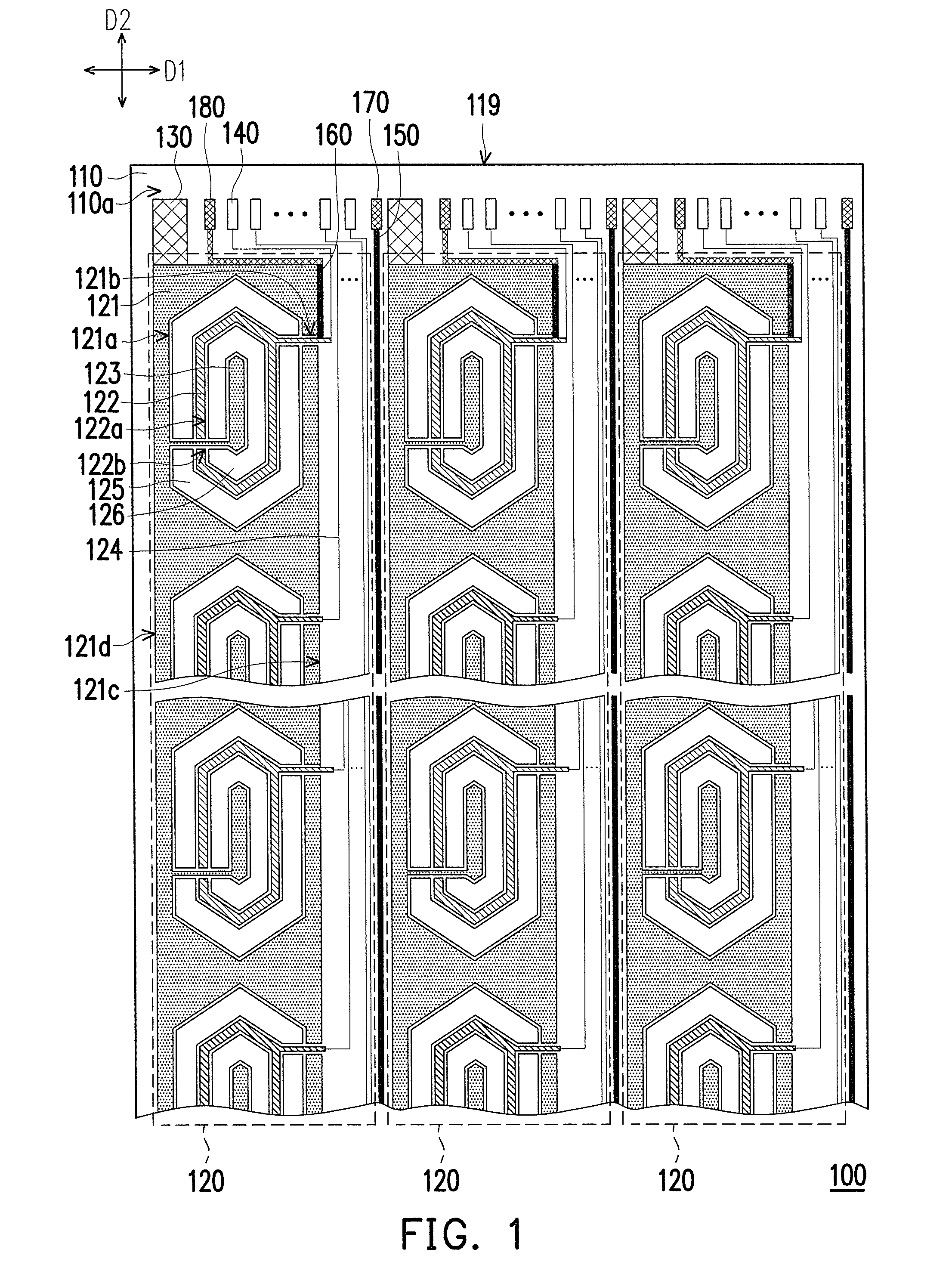

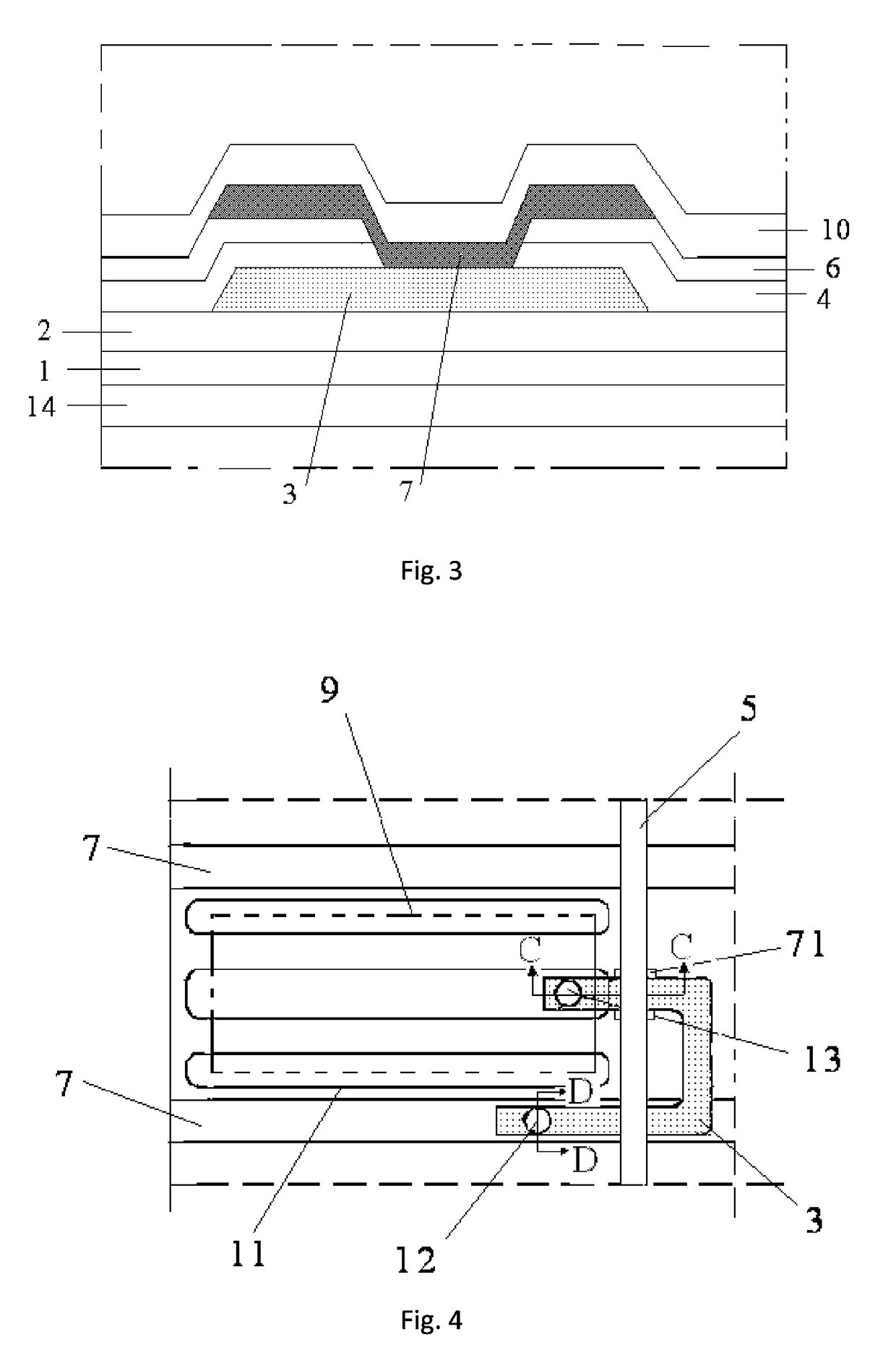

Array substrate and display device

ActiveUS20150364494A1Reduce coupling capacitanceImprove the display effectSolid-state devicesNon-linear opticsDisplay deviceGobio gobio obtusirostris

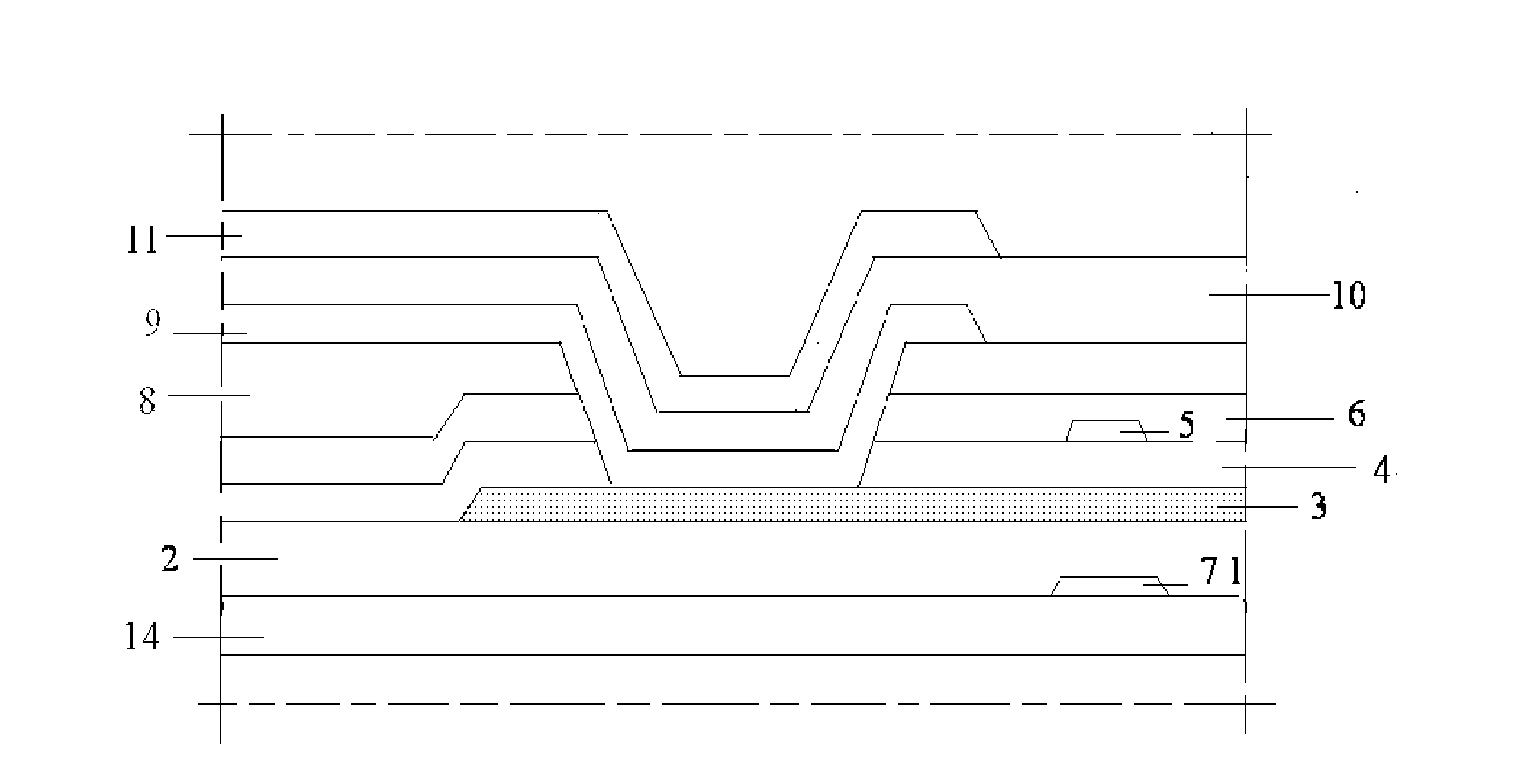

The present disclosure provides an array substrate and a display device. The array substrate includes gate lines, data lines, and thin film transistors (TFTs) connected to the gate lines and the data lines. At least one of the data lines is divided into a first branch and a second branch at a predetermined region where an intersection of the at least one of the data lines and at least one of the gate lines is located. The first branch overlaps the at least one of the gate lines, and has a width less than a width of a non-overlapping portion of the at least one of the data lines which does not overlap the at least one of the gate lines. The second branch overlaps a gate electrode of a corresponding one of the TFTs, and serves as, or is connected to, a source electrode of the corresponding TFT.

Owner:BOE TECH GRP CO LTD

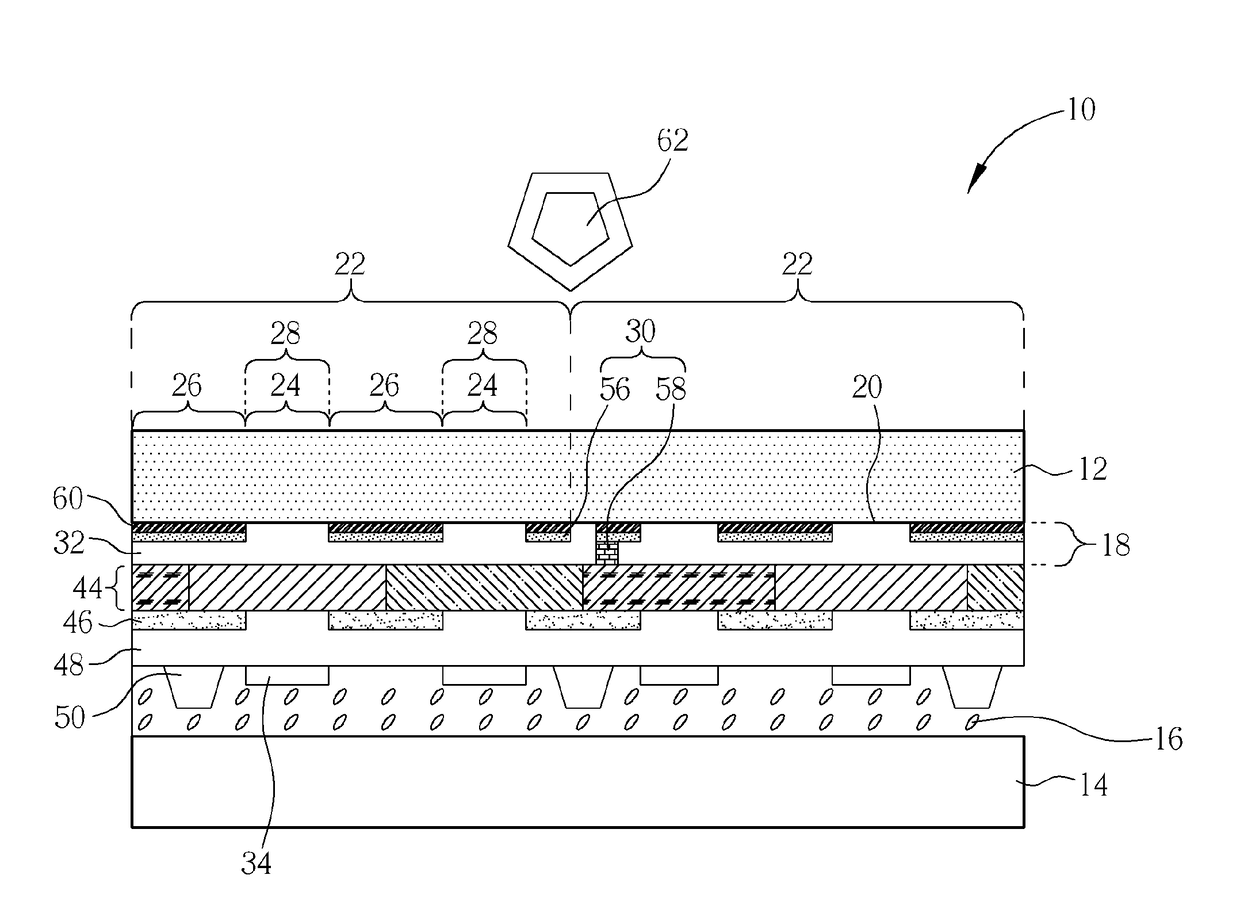

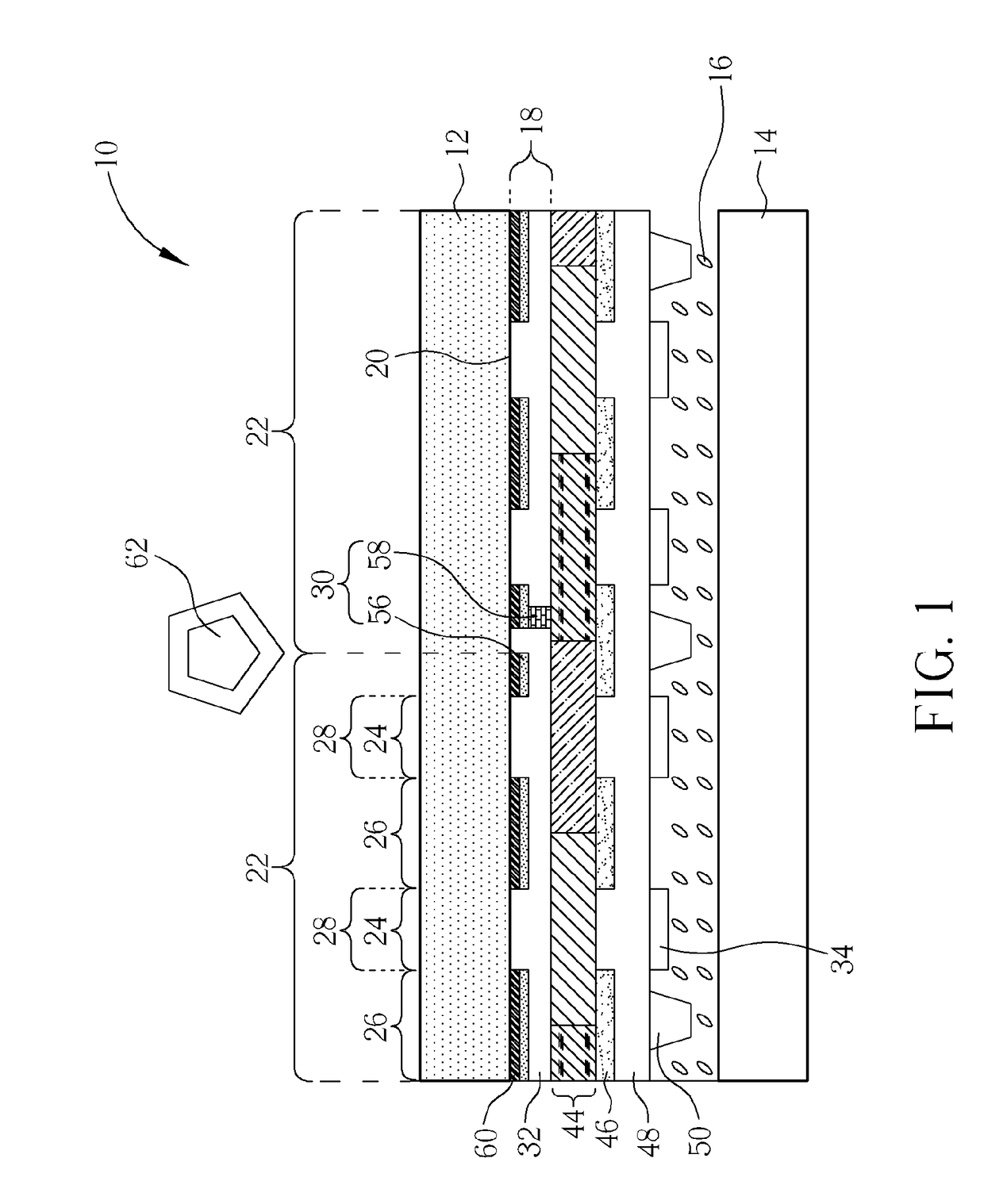

Touch device and touch display panel

ActiveUS20180321773A1Reduce coupling capacitanceHigh strengthStatic indicating devicesNon-linear opticsEngineeringBlack matrix

A touch display panel comprises a first substrate, a plurality of first sensing series and a plurality of second sensing series, wherein both the first sensing series and the second sensing series are above the first substrate, and the first sensing series and the second sensing series are crossly arranged to form a plurality of sensing series openings in between, a first insulating layer, covering the first sensing series and the second sensing series, a patterned black matrix layer, comprising a plurality of black matrix openings arranged in a matrix formation, a second insulating layer, covering the patterned black matrix layer; and a patterned common electrodes layer. The plurality of sensing series openings, the plurality of black matrix openings, and the patterned common electrode layer are overlapped.

Owner:AU OPTRONICS CORP

Array substrate and manufacturing method thereof, and display apparatus

InactiveUS20150279859A1Improve display qualityLarge coupling capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceCoupling

The present invention provides an array substrate and a manufacturing method thereof, and a display apparatus comprising the array substrate an array substrate, which can avoid poor displays due to large coupling capacitance between a data line and a pixel electrode in an array substrate in the prior art. The manufacturing method comprises the following steps: S1, forming a data line metal layer on a substrate, and forming a pattern of a data line by a patterning process; S2, forming a semiconductor layer on the substrate formed with the data line thereon, and forming a pattern of an active layer by a patterning process, wherein the data line is connected with the active layer.

Owner:BOE TECH GRP CO LTD +1

Contact air gap formation and structures thereof

ActiveUS10971408B2Eliminate riskLow effective capacitanceTransistorSolid-state devicesEngineering physicsMaterials science

A method of forming a device includes providing a transistor having a gate structure and a source / drain structure adjacent to the gate structure. A cavity is formed along a sidewall surface of a contact opening over the source / drain structure. After forming the cavity, a sacrificial layer is deposited over a bottom surface and along the sidewall surface of the contact opening including within the cavity. A first portion of the sacrificial layer along the bottom surface of the contact opening is removed to expose a portion of the source / drain structure. A metal plug is then formed over the portion of the exposed source / drain structure. A remaining portion of the sacrificial layer is removed to form an air gap disposed between the metal plug and the gate structure. Thereafter, a seal layer is deposited over the air gap to form an air gap spacer.

Owner:TAIWAN SEMICON MFG CO LTD

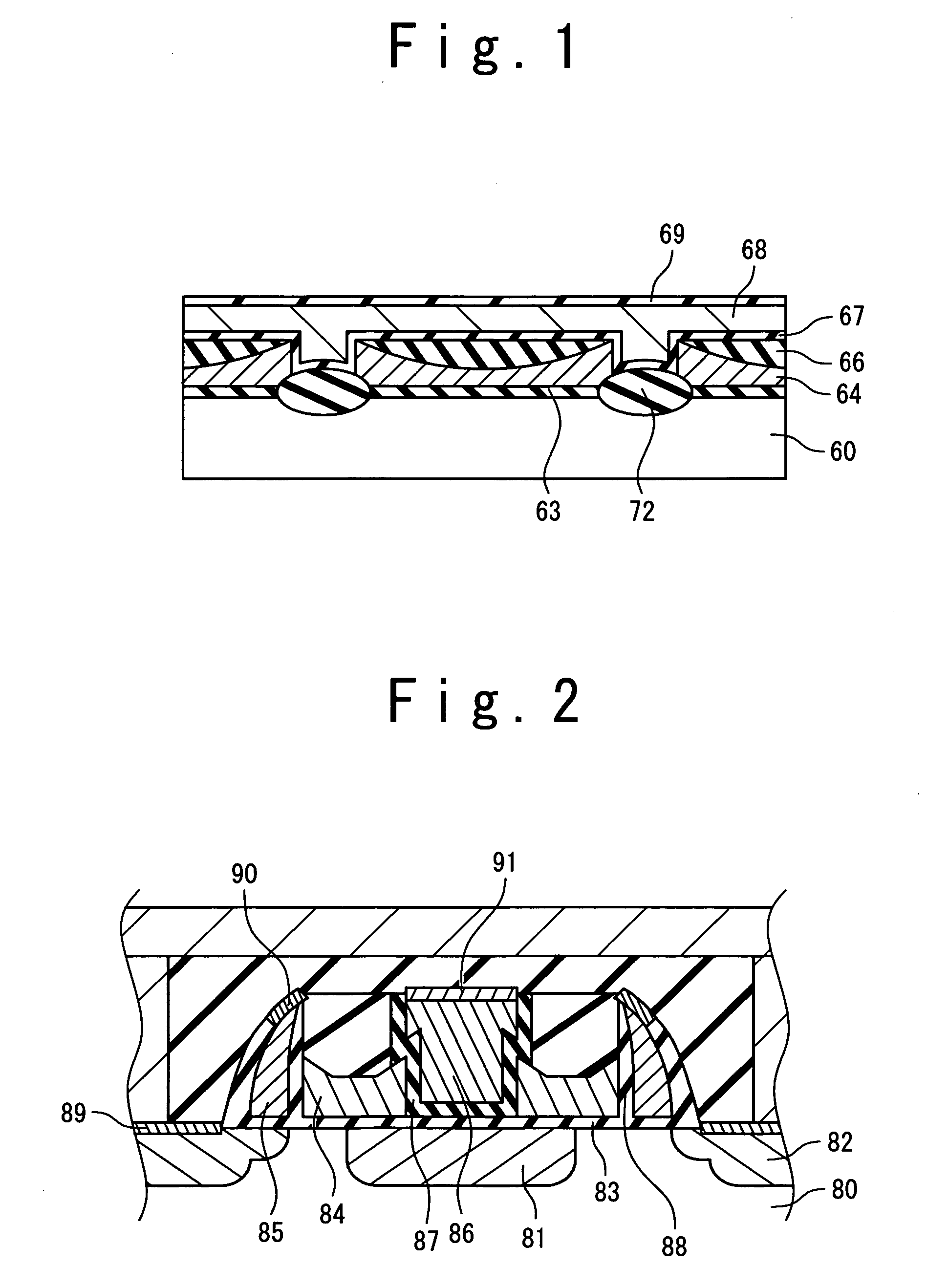

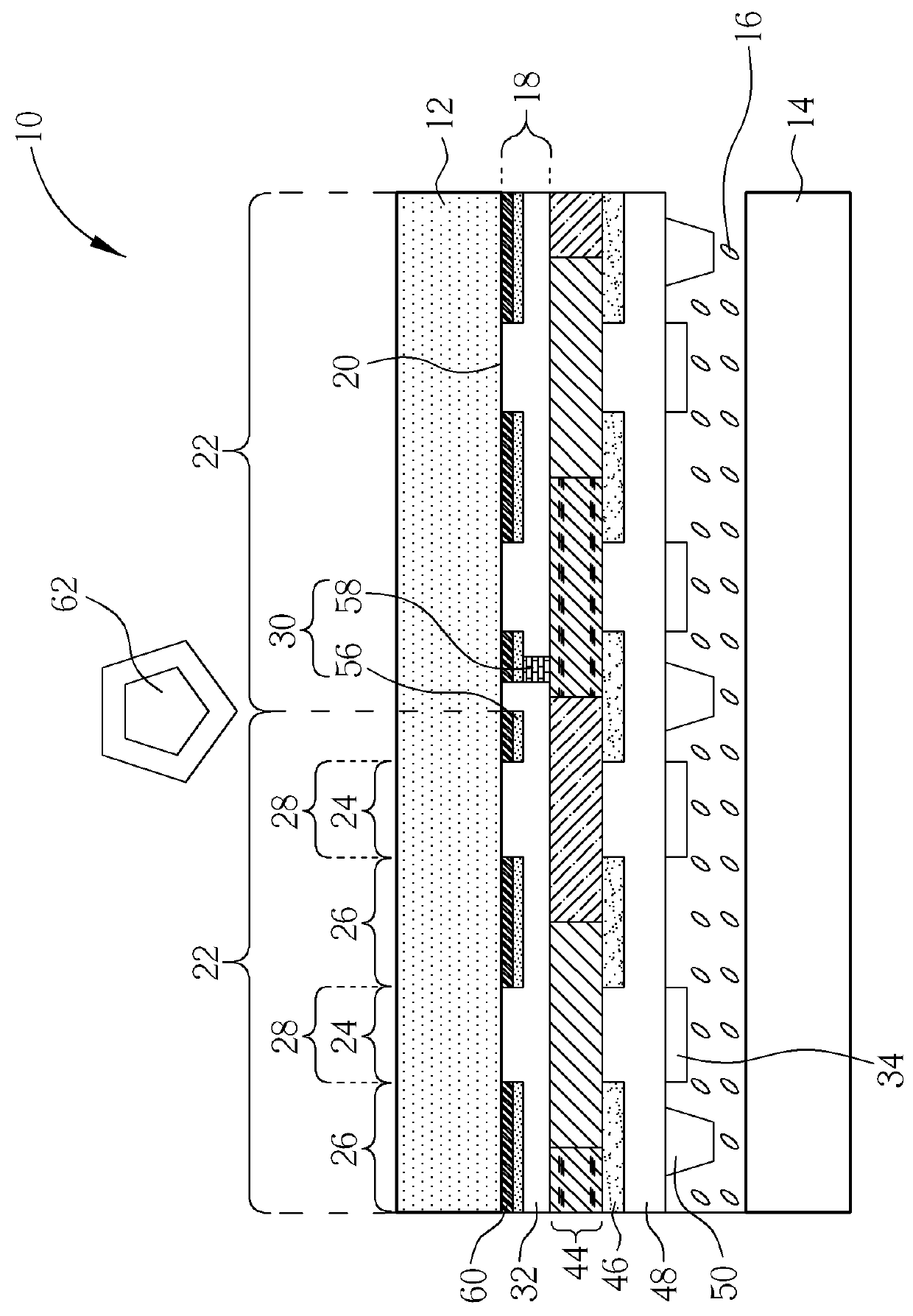

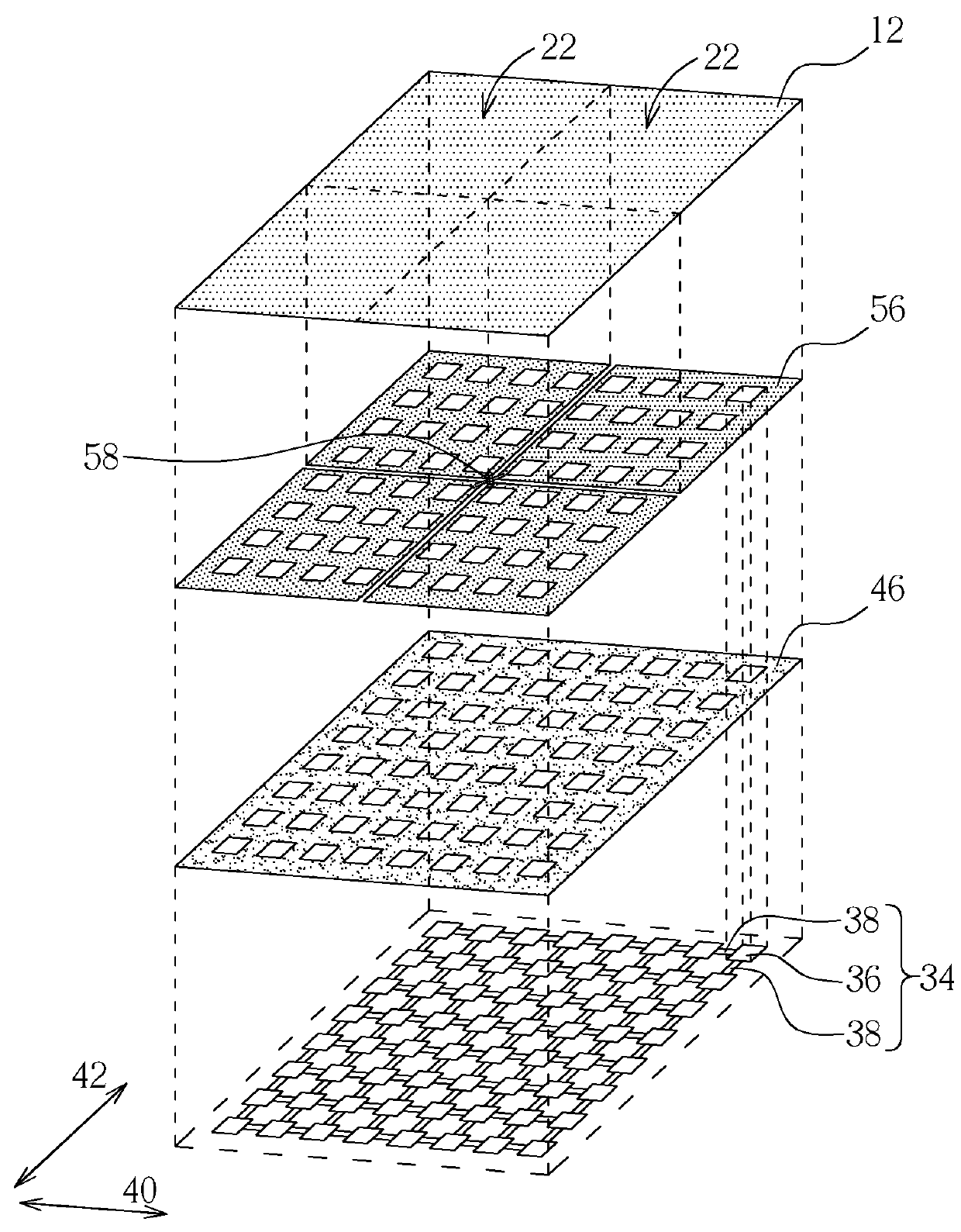

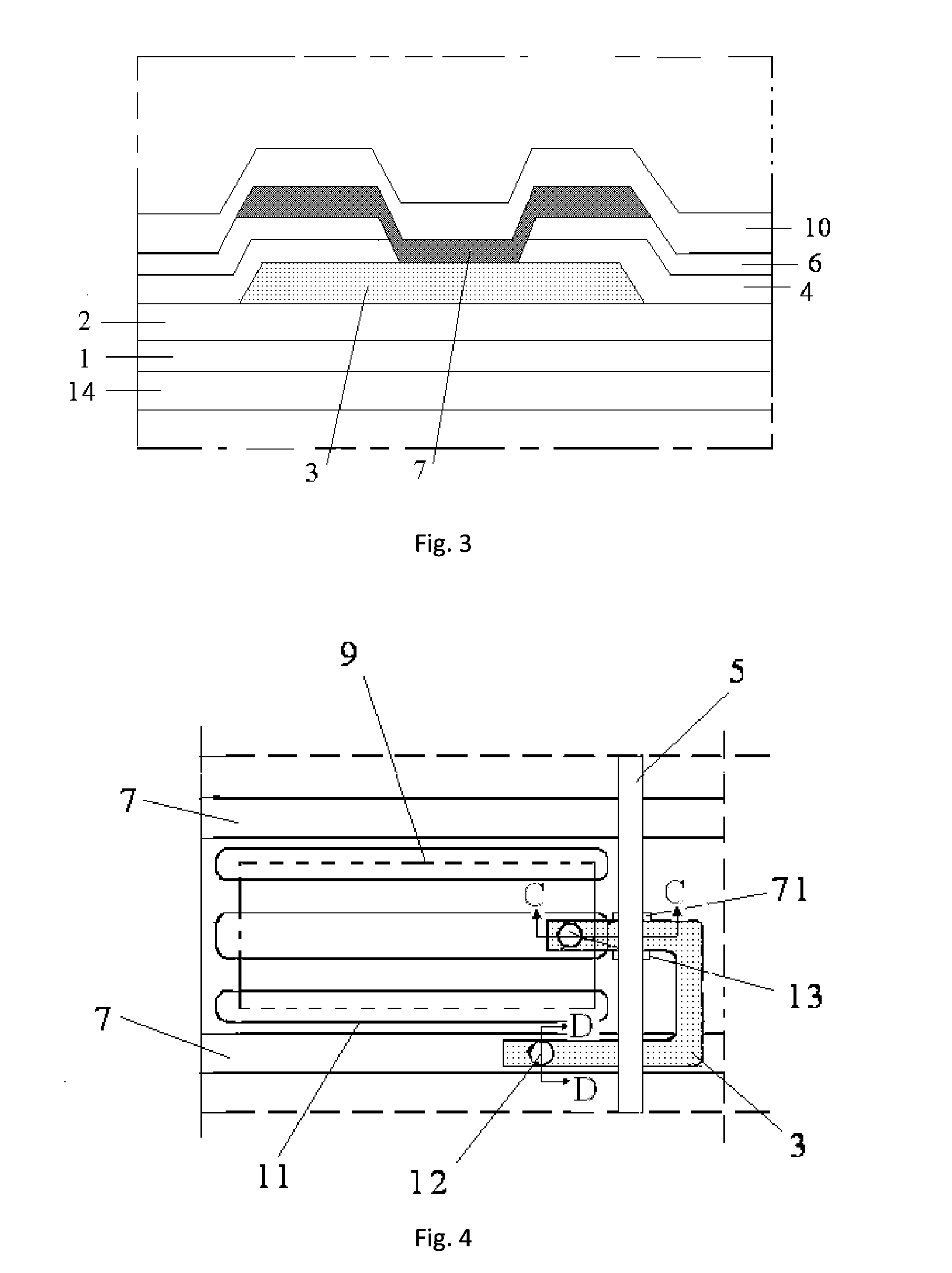

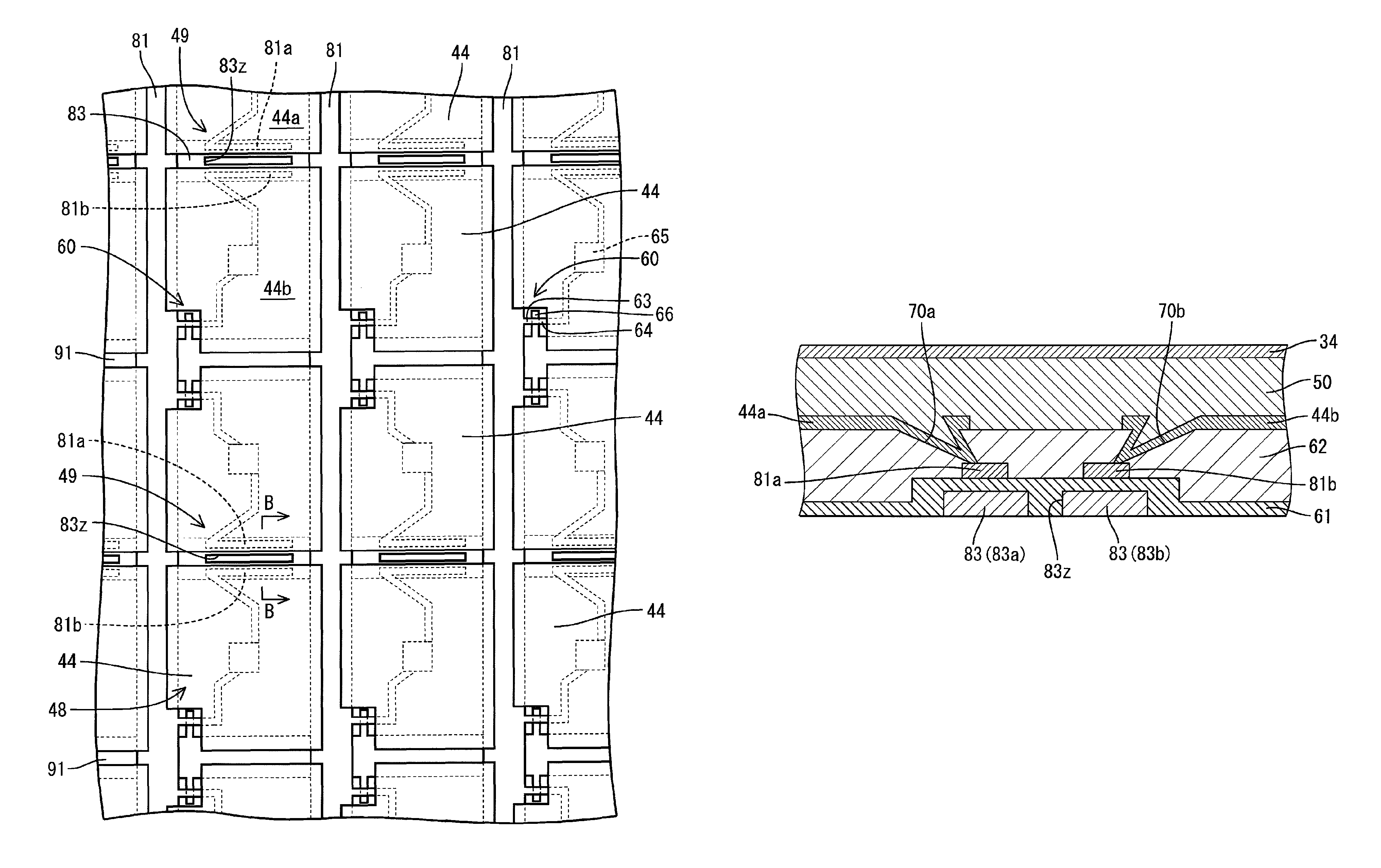

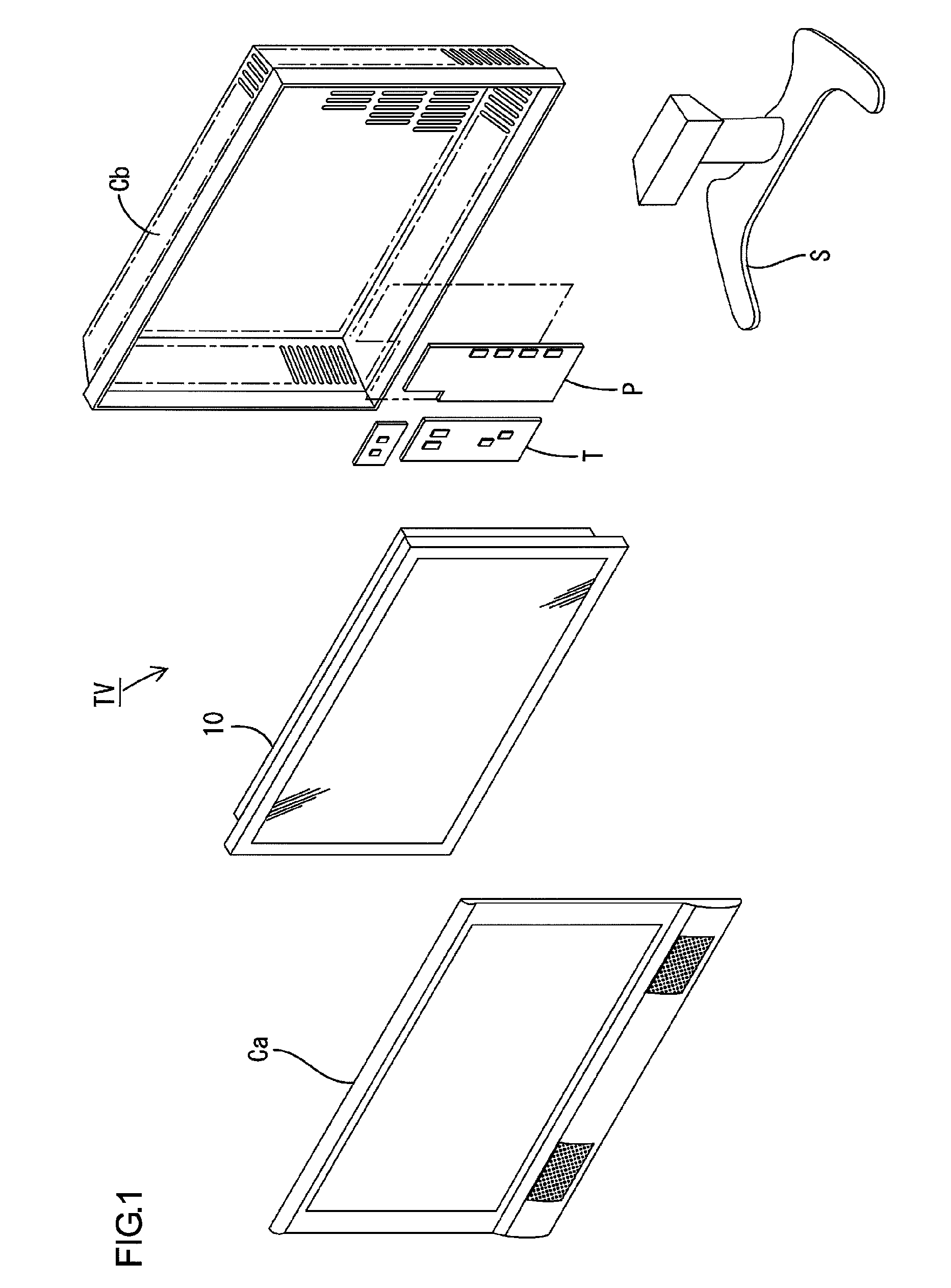

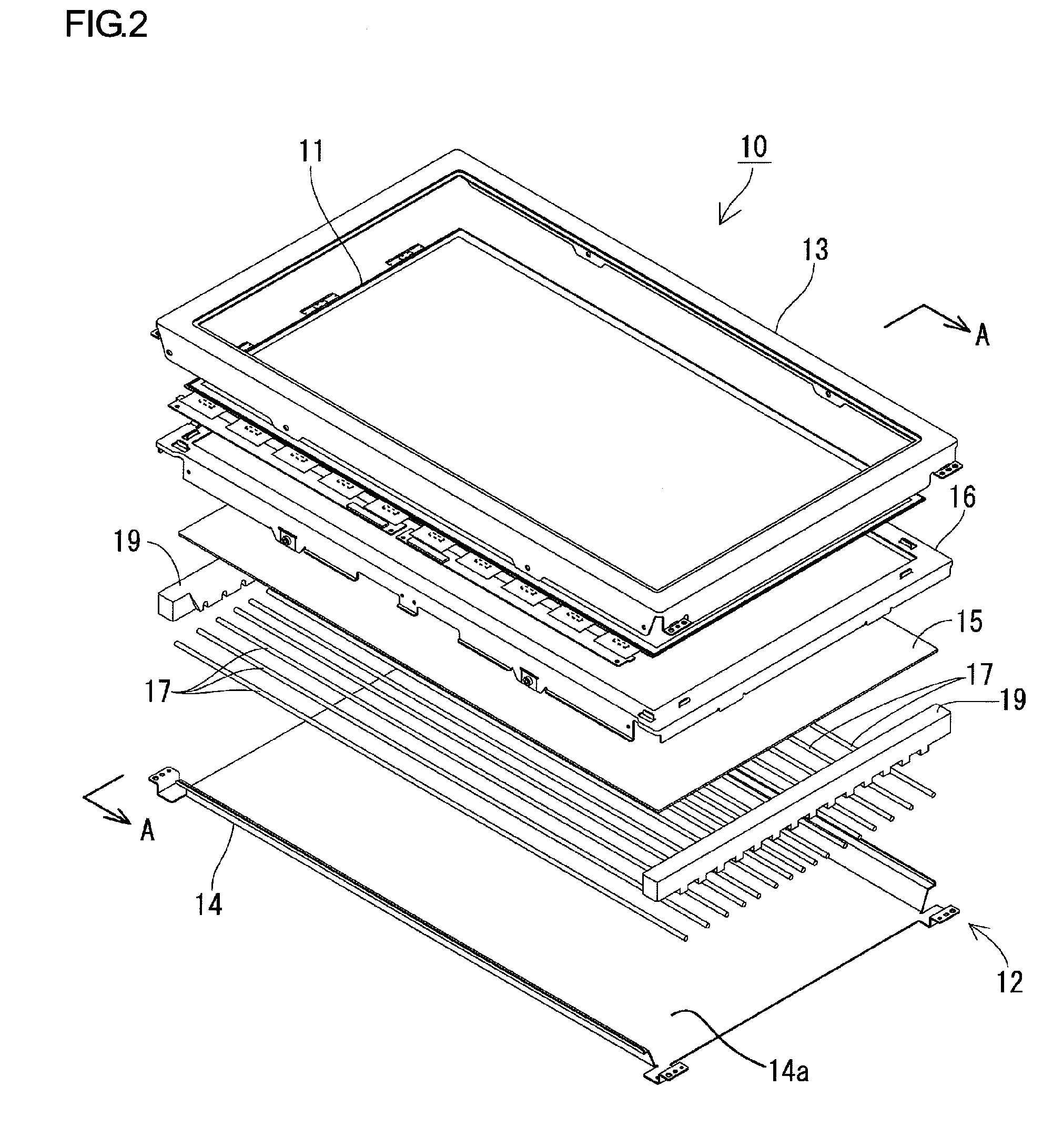

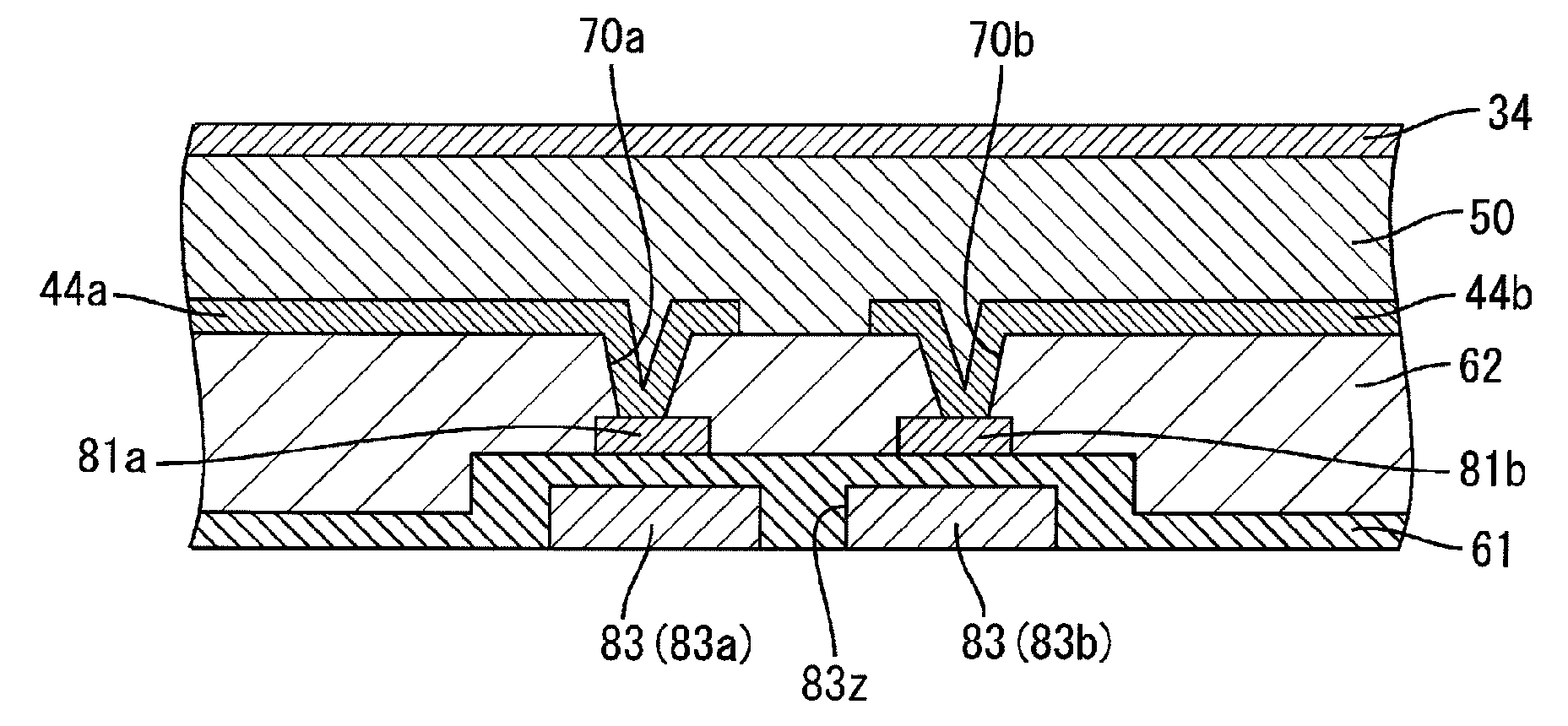

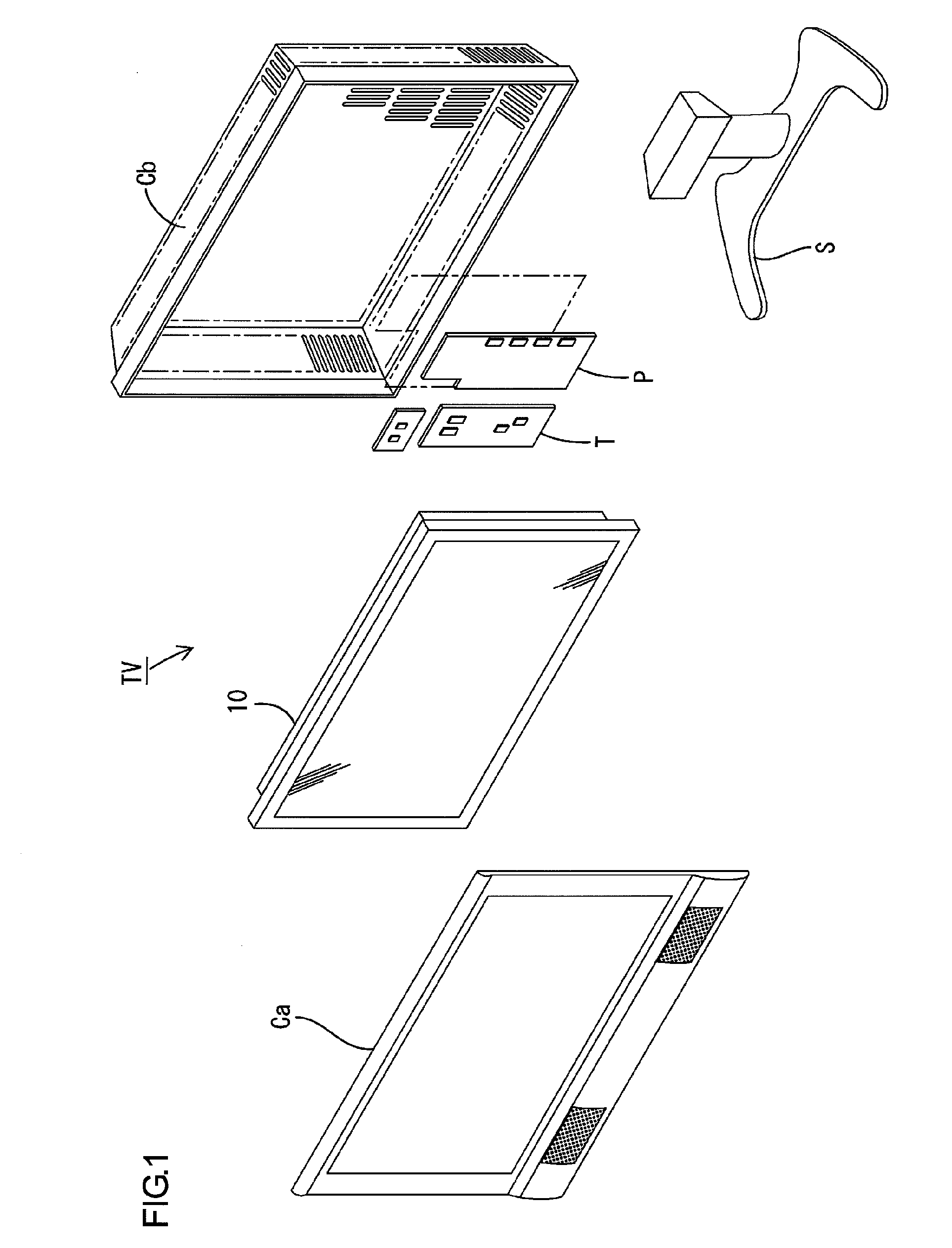

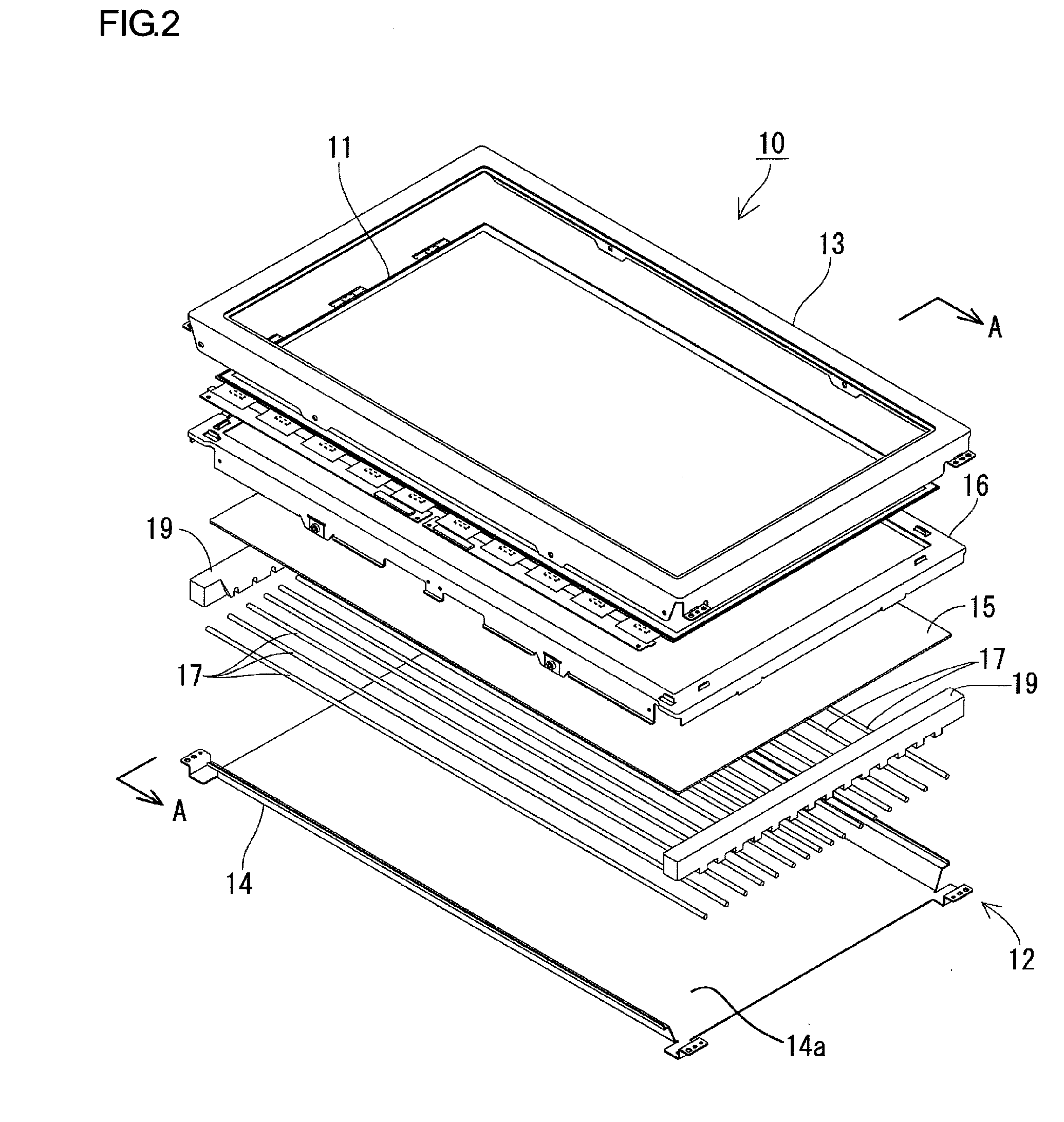

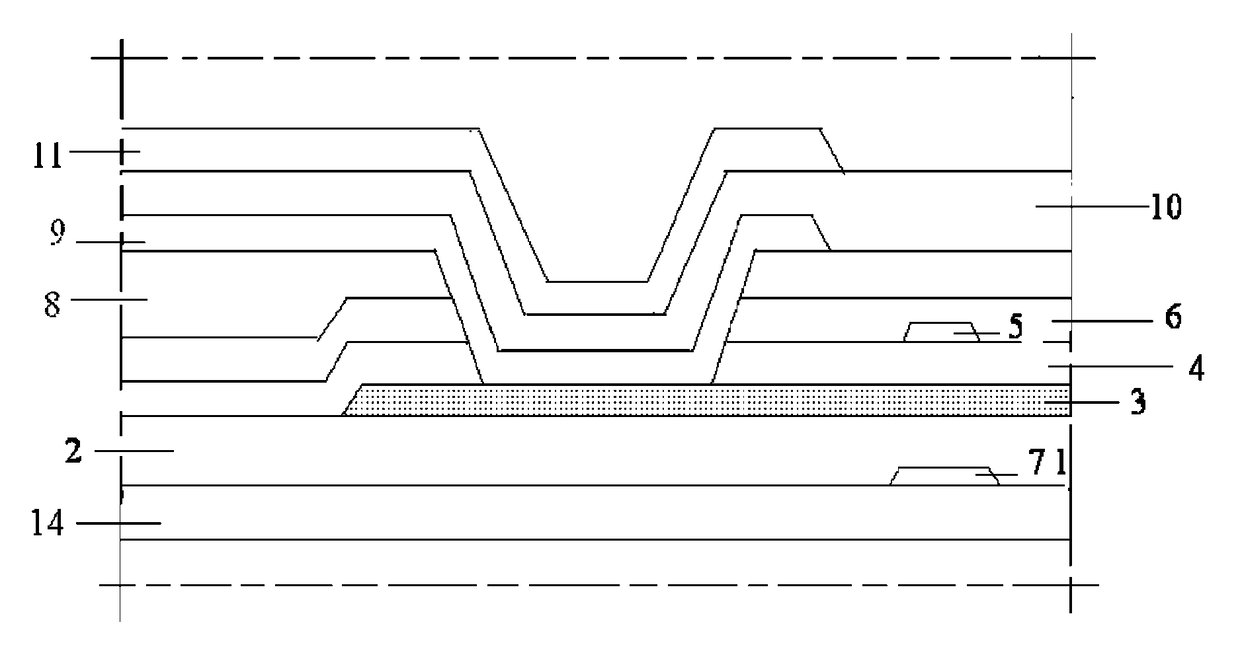

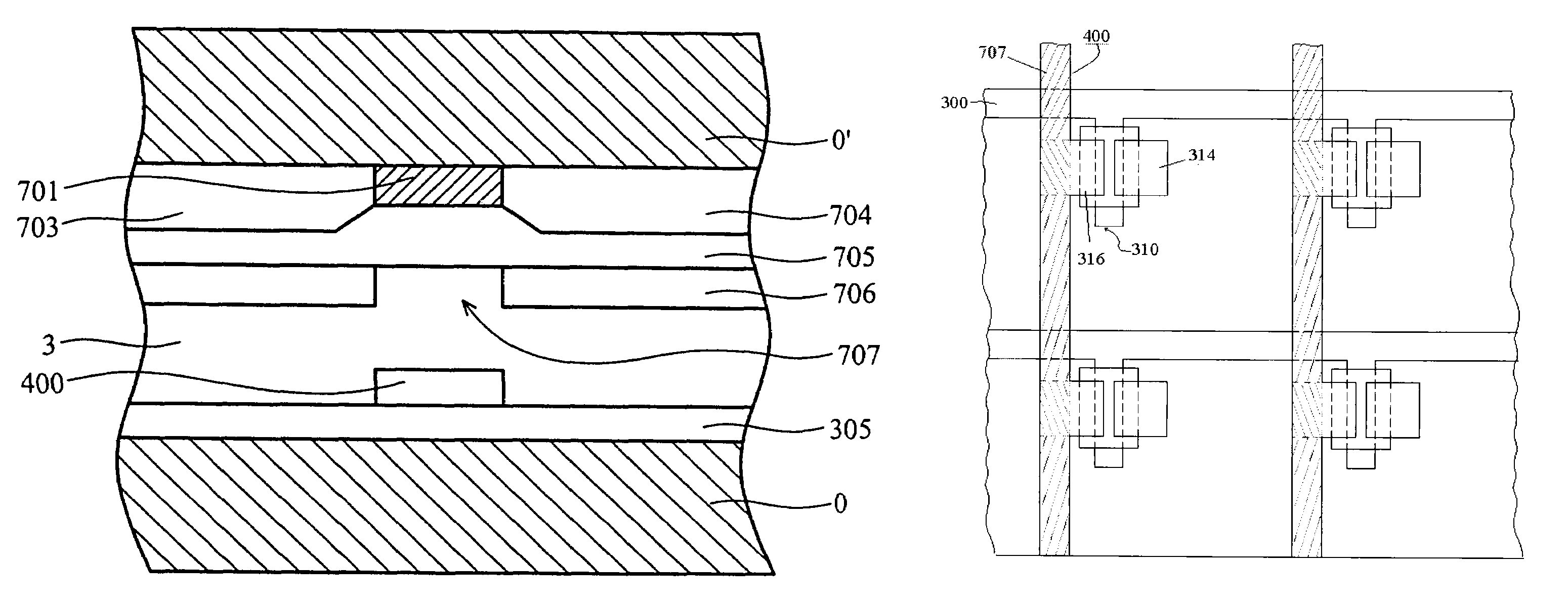

Liquid crystal device and television receiver

InactiveUS8223284B2Increase the aperture ratioReduce coupling capacitanceStatic indicating devicesNon-linear opticsTelevision receiversEngineering

A liquid crystal device 10 of the present invention includes conductive films 81a, 81b for storage capacitors, i.e., a first conductive film 81a and a second conductive film 81b, which are connected to two adjacent pixel electrodes 44a, 44b, respectively, via contact sections 70a, 70b formed through a second insulating film 62. The part of a storage capacitor 83 located below the conductive films 81a, 81b is divided into a first capacitor line 83a arranged below the first conductive film 81a and a second capacitor line 83b arranged below the second conductive film 81b.

Owner:SHARP KK

Semiconductor memory device

A semiconductor memory device comprises. word lines; global bit lines intersecting with the word lines; local bit lines partitioned into N (N is an integer greater than or equal to two) sections along the global bit lines and aligned with a same pitch as the global bit lines; N memory cell arrays each including memory cells each having cylindrical capacitor structure formed at intersections of the word lines and the local bit lines and being arranged corresponding to the sections of the local bit lines; local sense amplifiers for amplifying a signal read out from a selected memory cell to the local bit line and for outputting the signal to the global bit line; and global sense amplifiers for coupling the signal transmitted from the local sense amplifier corresponding to the selected memory cell through the global bit line to an external data line.

Owner:LONGITUDE LICENSING LTD

Semiconductor devices and methods of manufacturing the same

InactiveUS20140306280A1Poor gap fill characteristicLarge widthTransistorSemiconductor/solid-state device manufacturingInsulation layerDevice material

In the method, a plurality of gate structures may be formed on a substrate and be spaced apart from each other in a first direction. An insulation layer pattern may be formed by performing a chemical vapor deposition process using SiH4 gas as a source gas. The insulation layer pattern may partially define an air gap between the adjacent gate structures. A width of the air gap in the first direction may be about 65% to about 70% of a distance between the adjacent gate structures.

Owner:SAMSUNG ELECTRONICS CO LTD

Liquid crystal device and television receiver

InactiveUS20100253857A1Coupling capacitanceIncrease the aperture ratioTelevision system detailsStatic indicating devicesEngineeringLiquid crystal devices

A liquid crystal device 10 of the present invention includes conductive films 81a, 81b for storage capacitors, i.e., a first conductive film 81a and a second conductive film 81b, which are connected to two adjacent pixel electrodes 44a, 44b, respectively, via contact sections 70a, 70b formed through a second insulating film 62. The part of a storage capacitor 83 located below the conductive films 81a, 81b is divided into a first capacitor line 83a arranged below the first conductive film 81a and a second capacitor line 83b arranged below the second conductive film 81b.

Owner:SHARP KK

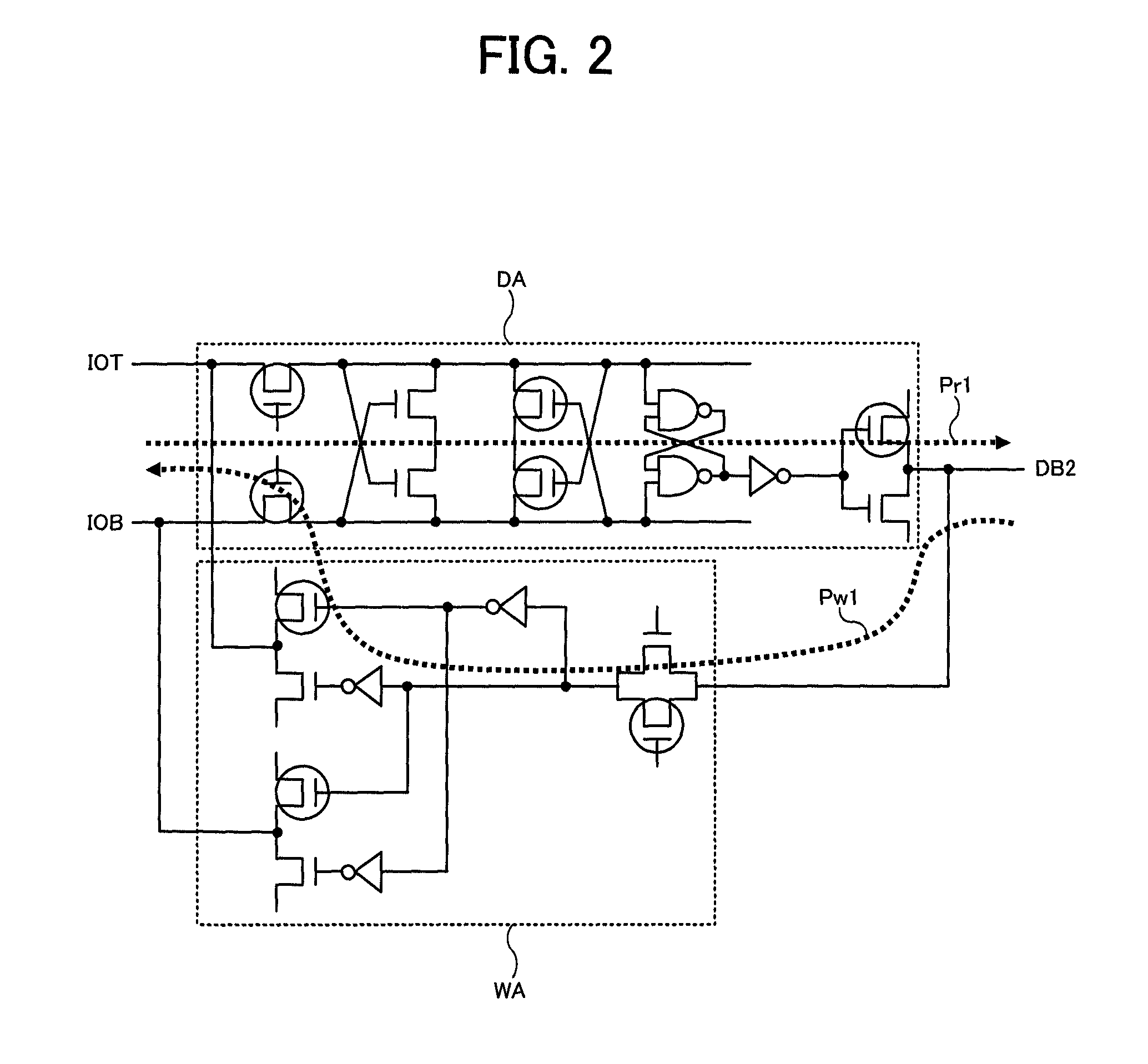

Semiconductor device having data bus

ActiveUS8644047B2Suppression of crosstalk effectsIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesSemiconductorSemiconductor device

A semiconductor device is disclosed which comprises a first wiring layer, a second wiring layer formed over the first wiring layer, data input / output terminals, and a data bus formed in the first and second wiring layers. The data bus includes N data lines transmitting data between a predetermined circuit and the input / output terminals. M first data lines among the N data lines have a length shorter than a predetermined length and residual N-M second data lines have a length longer than the predetermined length. Shield lines adjacent to the N data lines are formed in the first and second layers. The N data lines are arranged at positions at which the data lines do not overlap one another in a stacking direction of the first and second wiring layers.

Owner:LONGITUDE LICENSING LTD

Touch panel

ActiveUS8895882B2Coupling capacitanceImprove touch sensitivityMechanically variable capacitor detailsElectronic switchingEngineeringTouch panel

A touch panel includes a substrate and sensing units. Each sensing unit includes an electrode line, first electrode patterns, second electrode patterns and connecting lines. The electrode line extends along a second direction and has first openings arranged along the second direction and first breaches corresponding to the first openings. Each first breach connects the corresponding first opening and the exterior of the electrode line. The first electrode patterns are respectively disposed in the first openings. Each first electrode pattern has a second opening and a second breach connecting the second opening and the exterior of first electrode pattern. The second electrode patterns are respectively disposed in the second openings and respectively connected with the electrode line through the second breaches. The connecting lines are disposed on at least one side of the electrode line and connected with the corresponding first electrode pattern through the first breach.

Owner:HTC CORP

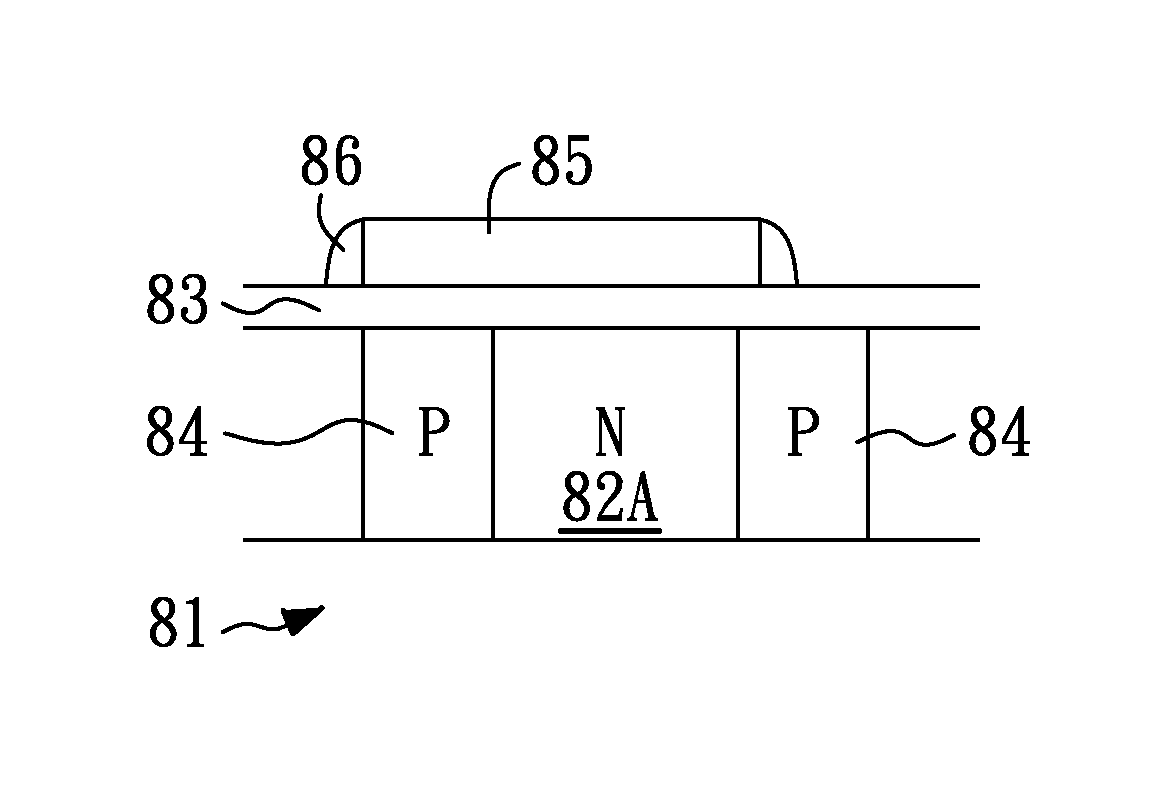

Process of forming a back side illumination image sensor

ActiveUS20140370642A1Increase overlapImprove hole accumulationTransistorSolid-state devicesEngineeringFloating diffusion

A process of forming a back side illumination (BSI) image sensor is disclosed. An n-type implant is formed in a semiconductor substrate, and a p-type implant region, surrounding n-type in each pixel, is formed in the n-type implant such that in cross sectional view an n-type implant region is sandwiched between the two p-type implant regions. A transfer gate is formed on the semiconductor substrate such that the transfer gate entirely covers the n-type implant region and at least partially covers each of the p-type implant regions. A floating diffusion is formed in one of the p-type implant regions.

Owner:HIMAX IMAGING LIMITED

Method for producing TFT array substrate, TFT array substrate, and display apparatus

ActiveUS20170301700A1Increase coupling capacitanceIncrease distanceSolid-state devicesSemiconductor devicesCapacitanceEngineering

The present disclosure provides a method for producing a TFT array substrate, a TFT array substrate, and a display apparatus, and relates to a technical field of display. It can solve a problem of no signal transmission caused by fracture of a source signal line, without increasing a coupling capacitance of the TFT array substrate. The method for producing a TFT array substrate includes: forming a transparent conductive layer and a source-drain metal layer in sequence onto a base substrate; and patterning the source-drain metal layer and the transparent conductive layer in one patterning process to form a source signal line and a pixel electrode line overlapping with each other.

Owner:BOE TECH GRP CO LTD +1

Process of forming a back side illumination image sensor

ActiveUS9153621B2Increase overlapAccelerate the accumulation processTransistorSolid-state devicesEngineeringFloating diffusion

Owner:HIMAX IMAGING LIMITED

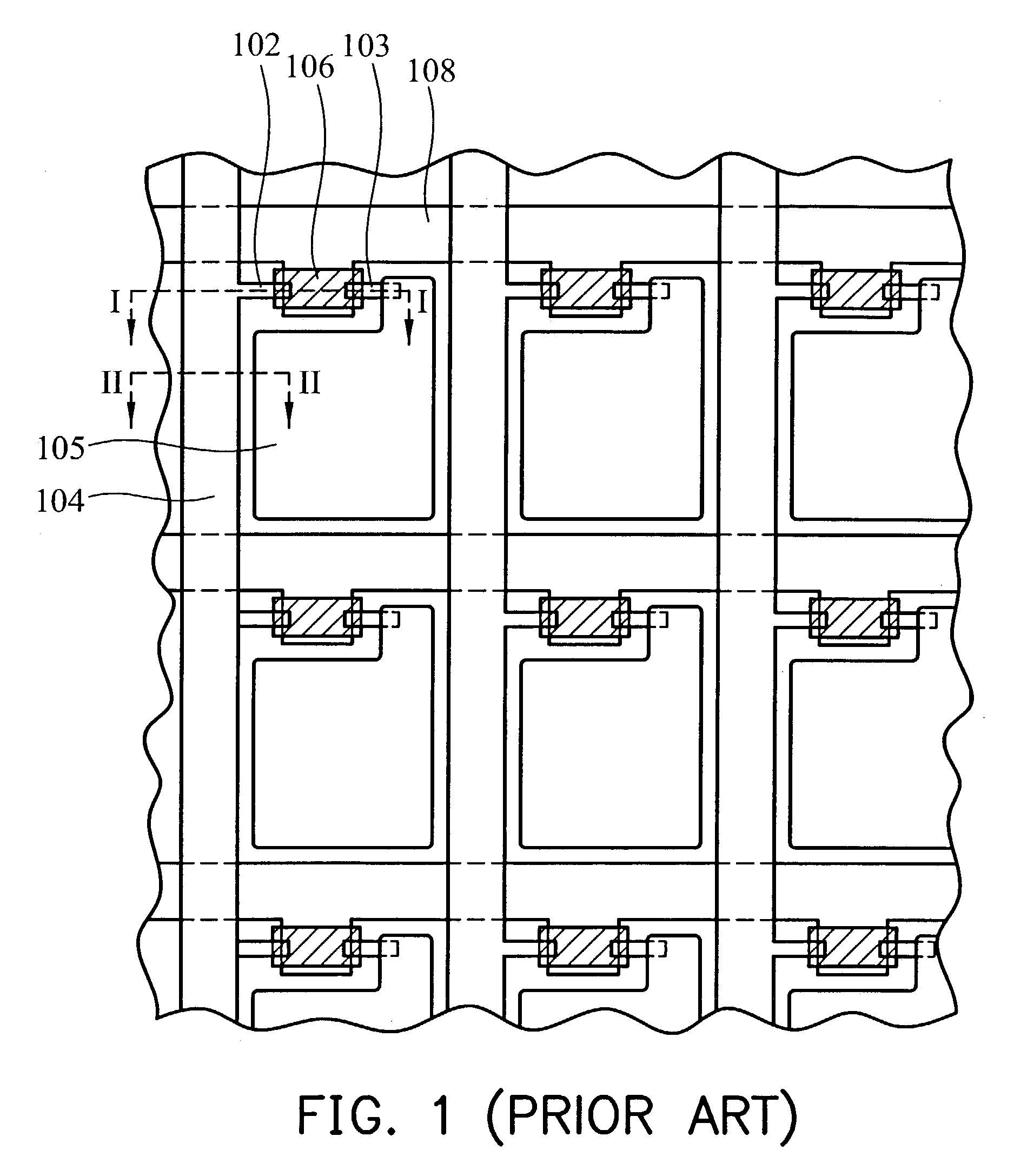

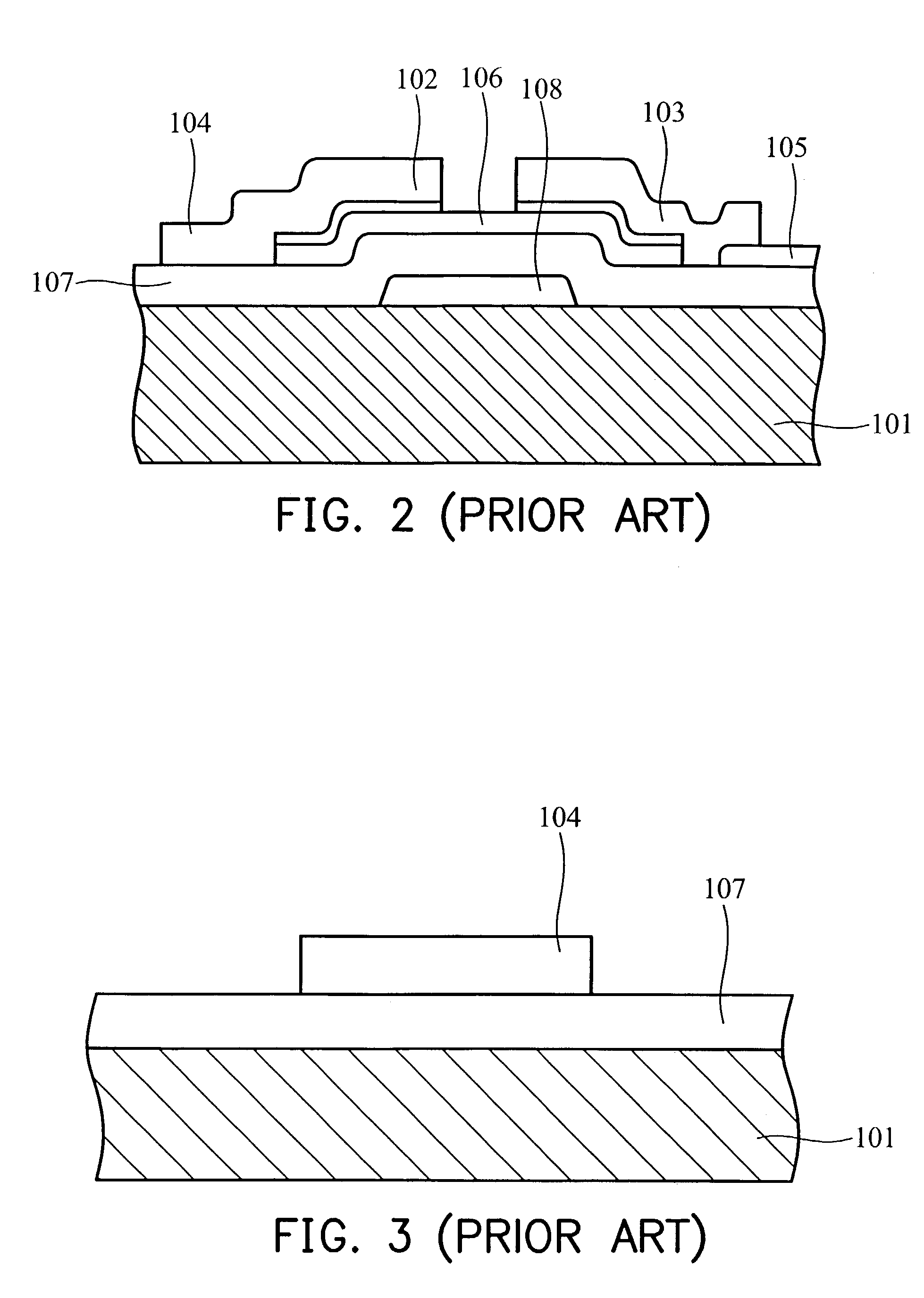

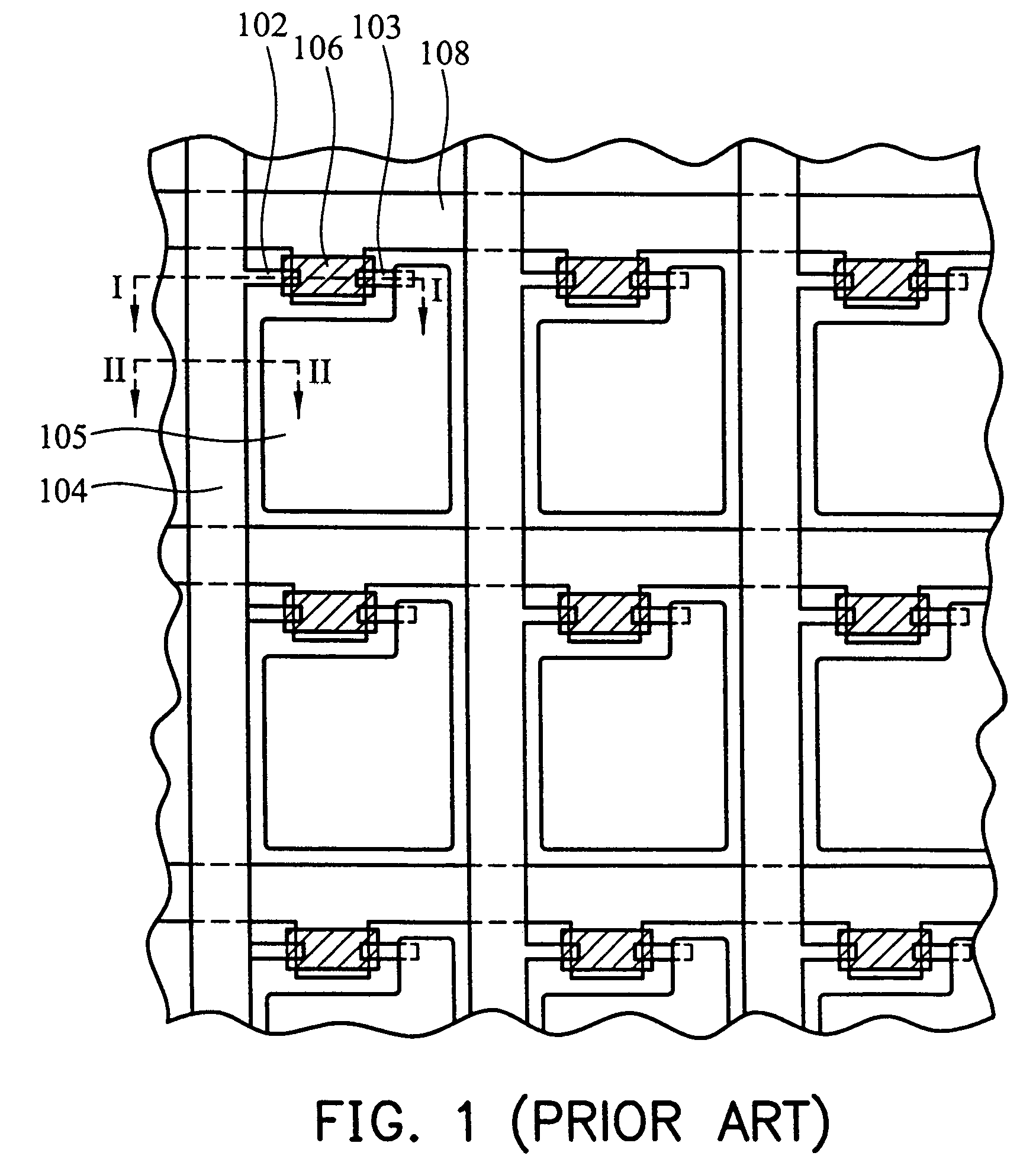

Liquid crystal display and fabricating method thereof

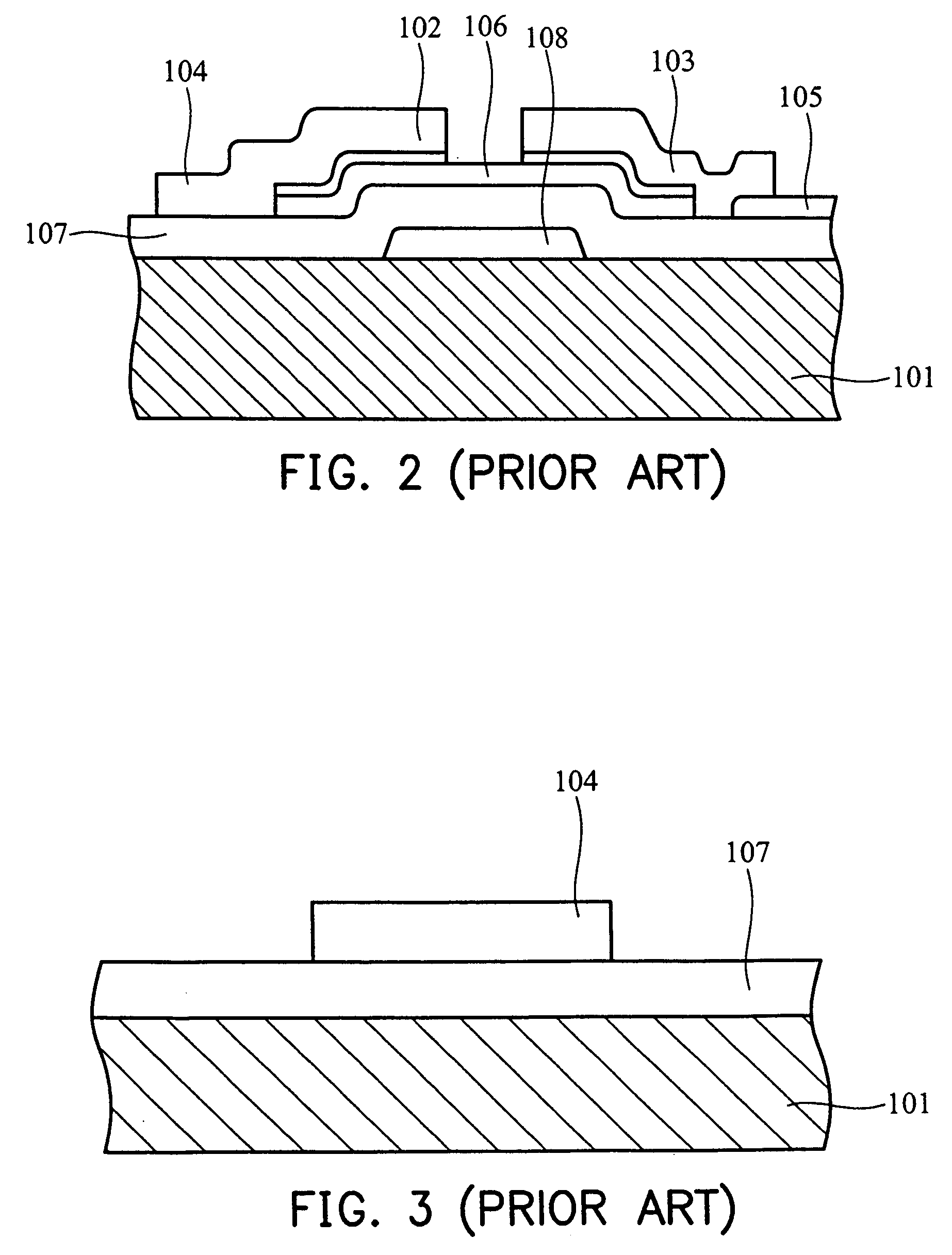

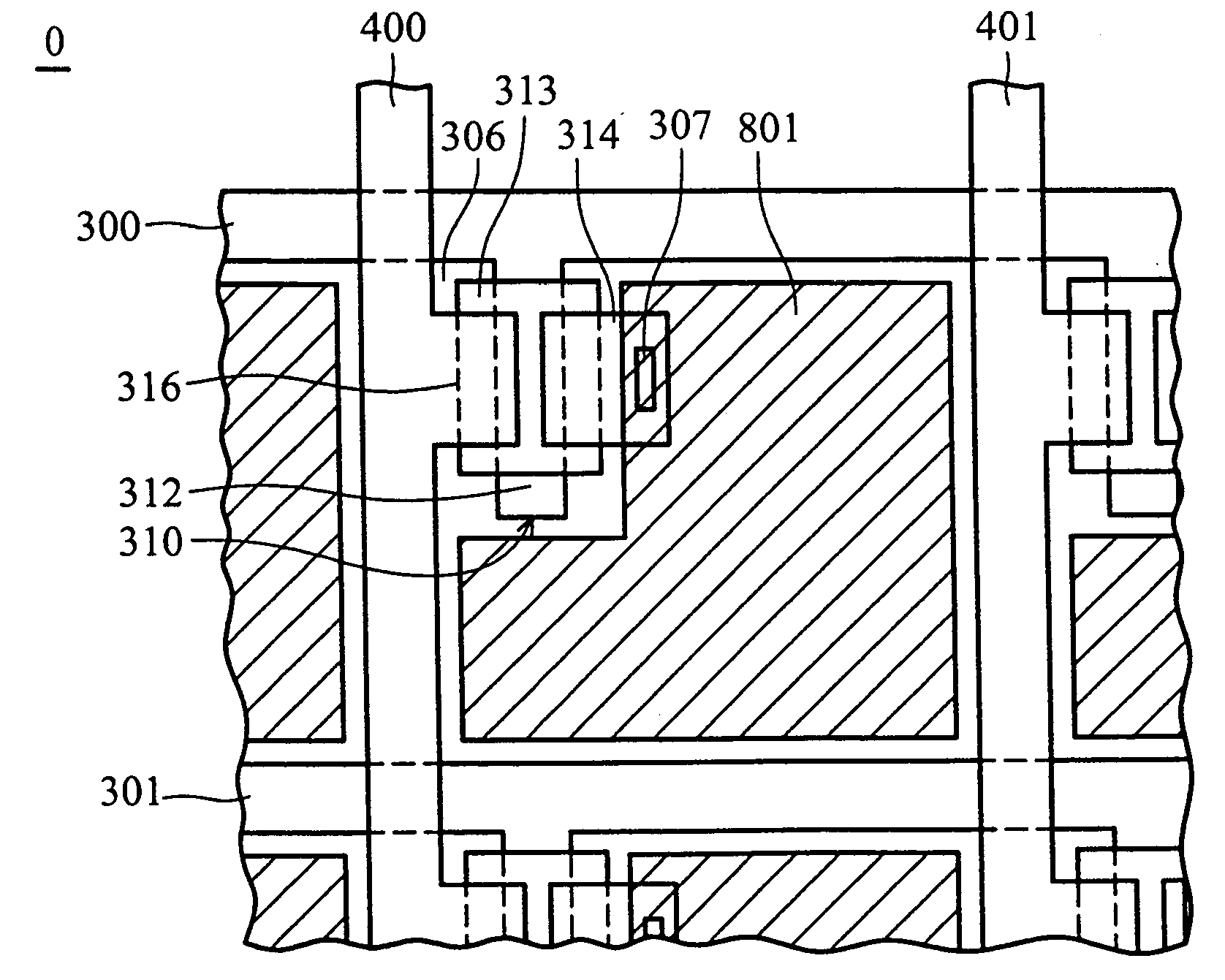

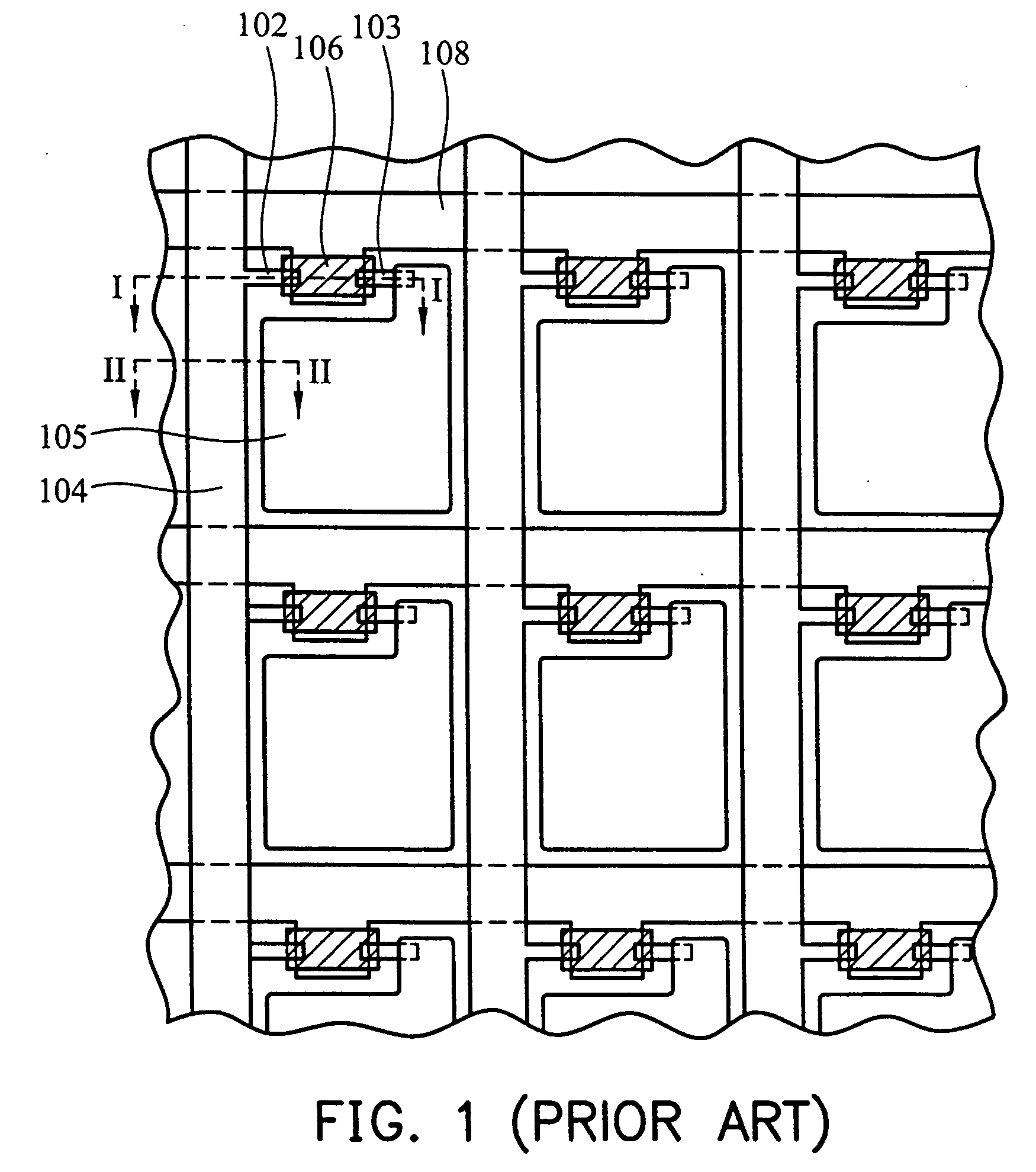

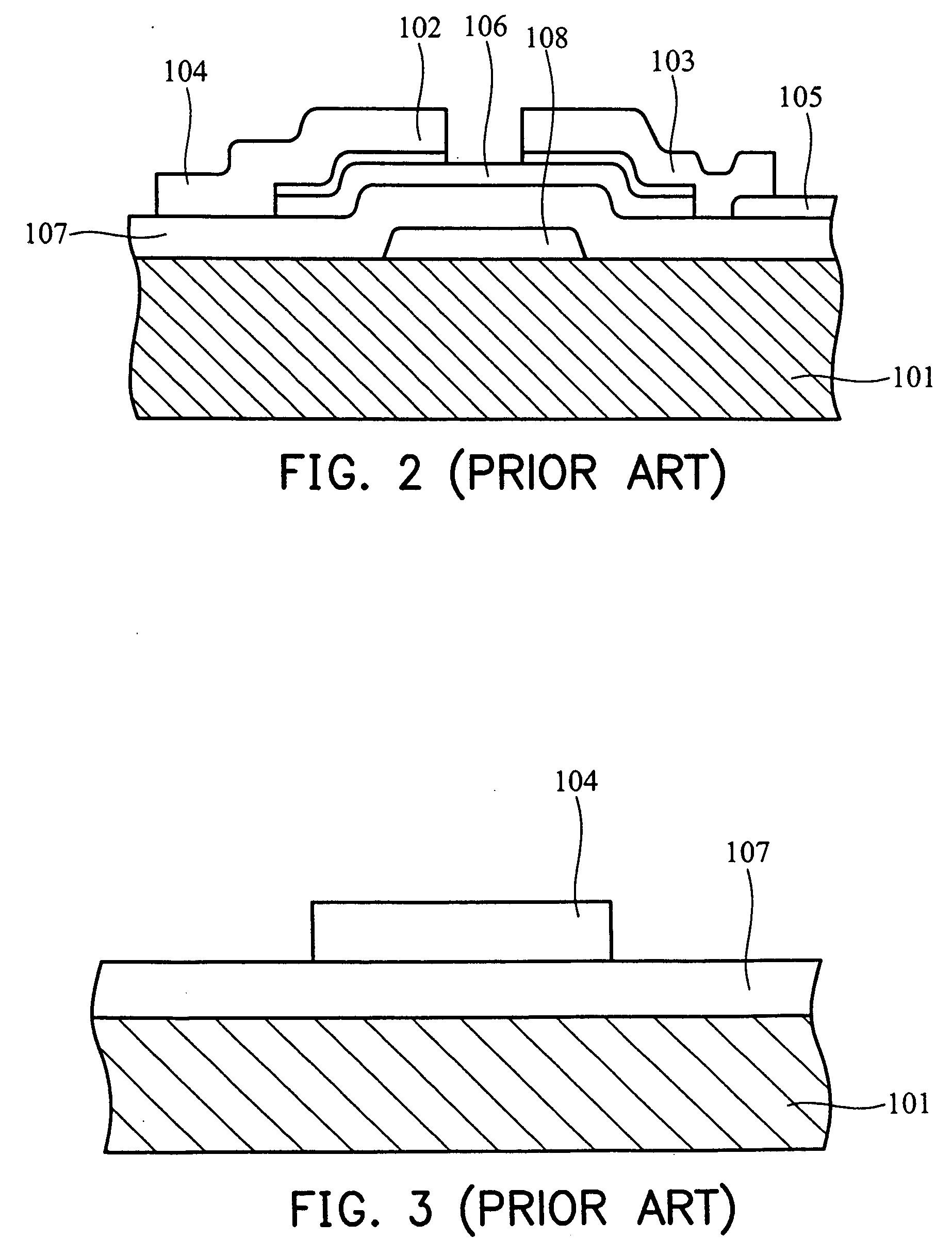

InactiveUS6965423B2Reduce crosstalkImprove display qualitySemiconductor/solid-state device manufacturingNon-linear opticsElectricityLiquid-crystal display

A liquid crystal display (LCD) and fabricating method thereof. The LCD includes a first substrate, provided with a plurality of parallel gate lines and a plurality of parallel signal lines, wherein the gate lines and signal lines are perpendicular, and a pixel area is defined by two adjacent gate lines and two adjacent signal lines. A source electrode, electrically connected to one of the adjacent signal lines, and a drain electrode are formed on the pixel area. A first pixel electrode is formed, electrically connected to the drain electrode, on the pixel area. A second substrate is provided a predetermined distance above the first substrate, having a plurality of color-filtering areas, directly above the respective pixel area. A second pixel electrode layer is formed on the second substrate, wherein the part thereof directly above the signal lines is relatively thin.

Owner:INNOLUX CORP

Method for fabricating semiconductor device with porous dielectric structure

PendingUS20220059686A1Coupling capacitanceReduce RC delaySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialDielectric structure

The present application discloses a method for fabricating a semiconductor device. The method includes providing a substrate; forming two conductive features apart from each other over the substrate; forming a porous middle layer positioned between the two conductive features and adjacent to the two conductive features; depositing an energy-removable material between the two conductive features and adjacent to the two conductive features; and performing an energy treatment to transform the energy-removable material into a porous middle layer. The porosity of the porous middle layer is between about 25% and about 100%.

Owner:NAN YA TECH

Array substrate and manufacturing method thereof, and display apparatus

InactiveUS9911766B2Large coupling capacitanceReduce coupling capacitanceSolid-state devicesSemiconductor devicesCapacitanceEngineering

The present invention provides an array substrate and a manufacturing method thereof, and a display apparatus comprising the array substrate an array substrate, which can avoid poor displays due to large coupling capacitance between a data line and a pixel electrode in an array substrate in the prior art. The manufacturing method comprises the following steps: S1, forming a data line metal layer on a substrate, and forming a pattern of a data line by a patterning process; S2, forming a semiconductor layer on the substrate formed with the data line thereon, and forming a pattern of an active layer by a patterning process, wherein the data line is connected with the active layer.

Owner:BOE TECH GRP CO LTD +1

Liquid crystal display and fabricating method thereof

InactiveUS7248326B2Reduce crosstalkImprove display qualitySemiconductor/solid-state device manufacturingNon-linear opticsElectricityLiquid-crystal display

A liquid crystal display (LCD) and fabricating method thereof. The LCD includes a first substrate, provided with a plurality of parallel gate lines and a plurality of parallel signal lines, wherein the gate lines and signal lines are perpendicular, and a pixel area is defined by two adjacent gate lines and two adjacent signal lines. A source electrode, electrically connected to one of the adjacent signal lines, and a drain electrode are formed on the pixel area. A first pixel electrode is formed, electrically connected to the drain electrode, on the pixel area. A second substrate is provided a predetermined distance above the first substrate, having a plurality of color-filtering areas, directly above the respective pixel area. A second pixel electrode layer is formed on the second substrate, wherein the part thereof directly above the signal lines is relatively thin.

Owner:INNOLUX CORP

Liquid crystal display and fabricating method thereof

InactiveUS20050280764A1Reduce crosstalkImprove display qualitySemiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displaySignal lines

A liquid crystal display (LCD) and fabricating method thereof. The LCD includes a first substrate, provided with a plurality of parallel gate lines and a plurality of parallel signal lines, wherein the gate lines and signal lines are perpendicular, and a pixel area is defined by two adjacent gate lines and two adjacent signal lines. A source electrode, electrically connected to one of the adjacent signal lines, and a drain electrode are formed on the pixel area. A first pixel electrode is formed, electrically connected to the drain electrode, on the pixel area. A second substrate is provided a predetermined distance above the first substrate, having a plurality of color-filtering areas, directly above the respective pixel area. A second pixel electrode layer is formed on the second substrate, wherein the part thereof directly above the signal lines is relatively thin.

Owner:INNOLUX CORP