Logic BRAM mapping method and system

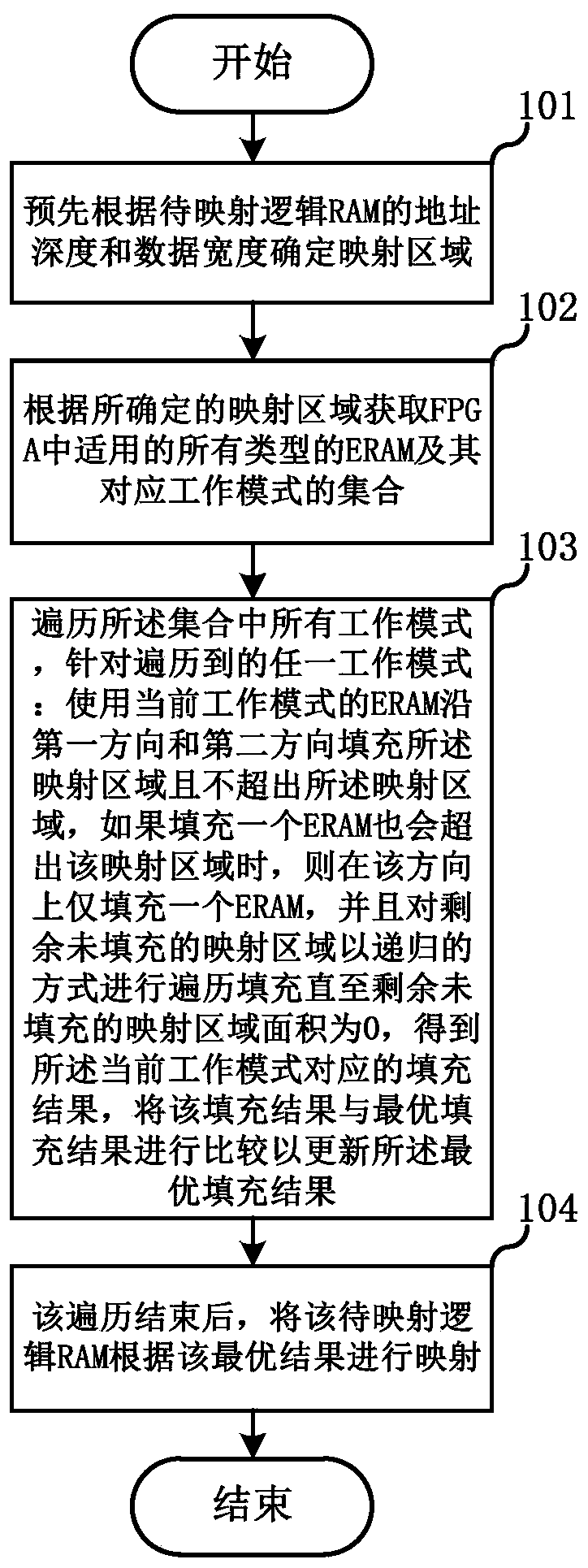

A mapping method and logic technology, applied in the field of logical BRAM mapping technology, can solve problems such as resource waste and filling failure, and achieve the effects of reducing waste, making up for resource waste, and optimizing the traversal filling process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

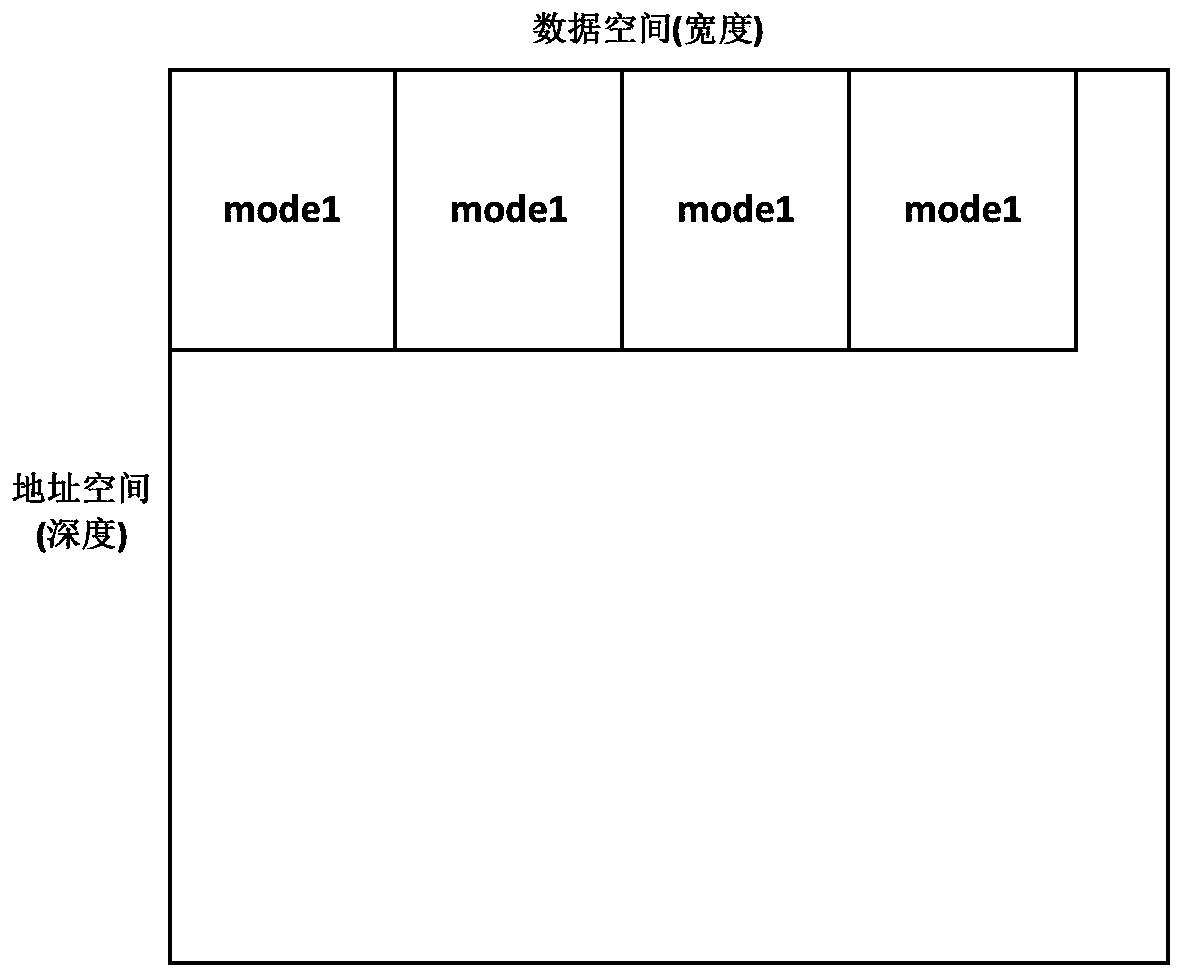

Examples

Embodiment Construction

[0050] In the following description, many technical details are proposed in order to enable readers to better understand the application. However, those skilled in the art can understand that the technical solutions claimed in this application can be realized even without these technical details and various changes and modifications based on the following implementation modes.

[0051] Explanation of some concepts:

[0052] FPGA: Field Programmable Gate Array, Field Programmable Logic Array. It appeared as a semi-custom circuit in the field of application-specific integrated circuits, which not only solved the shortcomings of full-custom circuits, but also overcome the shortcomings of the limited number of gates of the original programmable logic device.

[0053] ERAM: Embeded Random Access Memory, embedded random access memory. A hardware storage resource customized in FPGA has a fixed size and can be randomly accessed according to address and clock.

[0054] BRAM: Block R...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More