Method for simulating power failure of memory in FPGA

A storage and memory technology, applied in the field of integrated circuit verification, can solve the problems of timing convergence difficulties, insufficient simulation of real states, etc., to achieve the effect of saving resources and meeting timing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

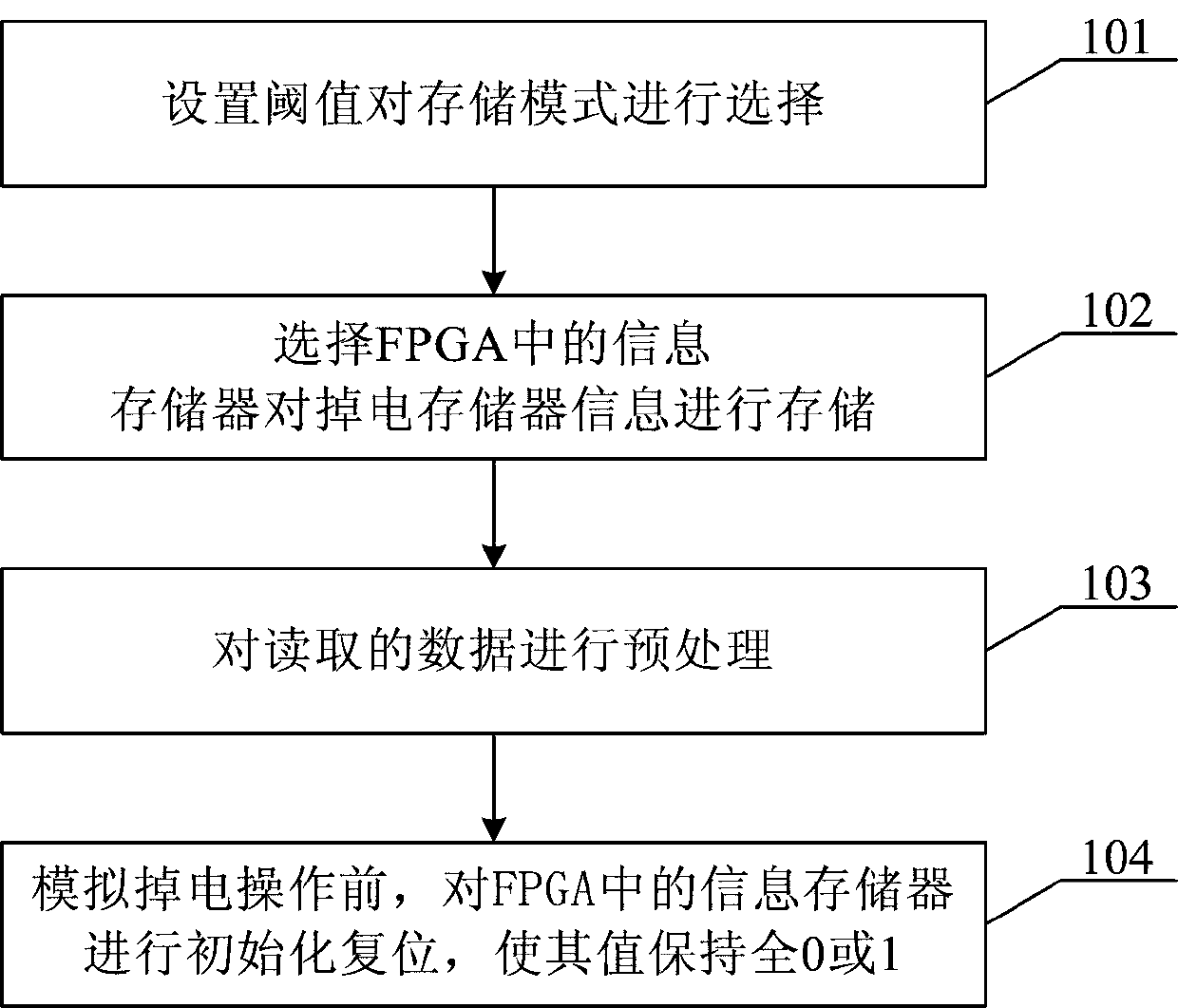

[0037] figure 1 For the method flowchart of simulating memory power-down in FPGA according to the present invention, below will refer to figure 1 , the method for simulating storage power-down in FPGA of the present invention is described in detail.

[0038] First, in step 101, a threshold is set to select a storage mode. In this step, when simulating the memory power-off, the user can first select a threshold to store the memory information through the FPGA memory; or the program automatically selects according to the size of the memory that needs power-off, for example If the number of memory addresses exceeds 1024, FPGA memory resources are used for storage. ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap