Acceleration design method of CNN network suitable for low-resource embedded chip

An embedded chip and design method technology, applied in the field of neural network deep learning, can solve problems such as insufficient DDR bandwidth resources, insufficient CPU utilization, and slow calculation speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

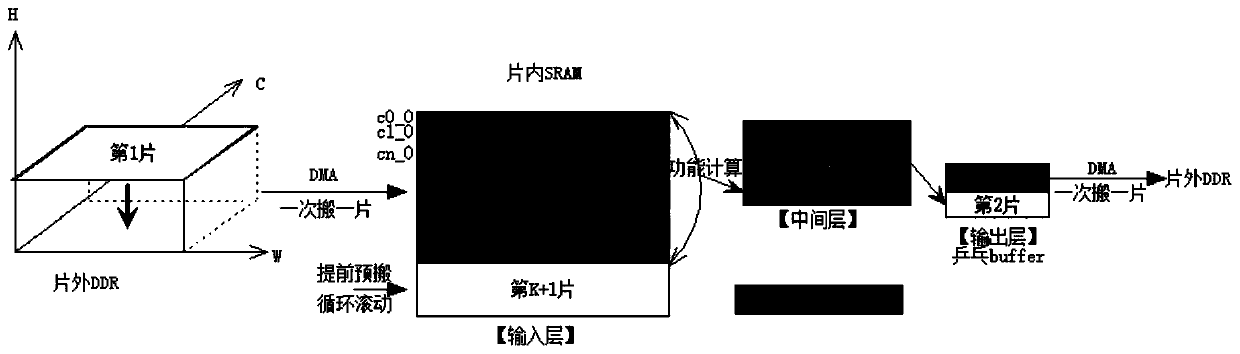

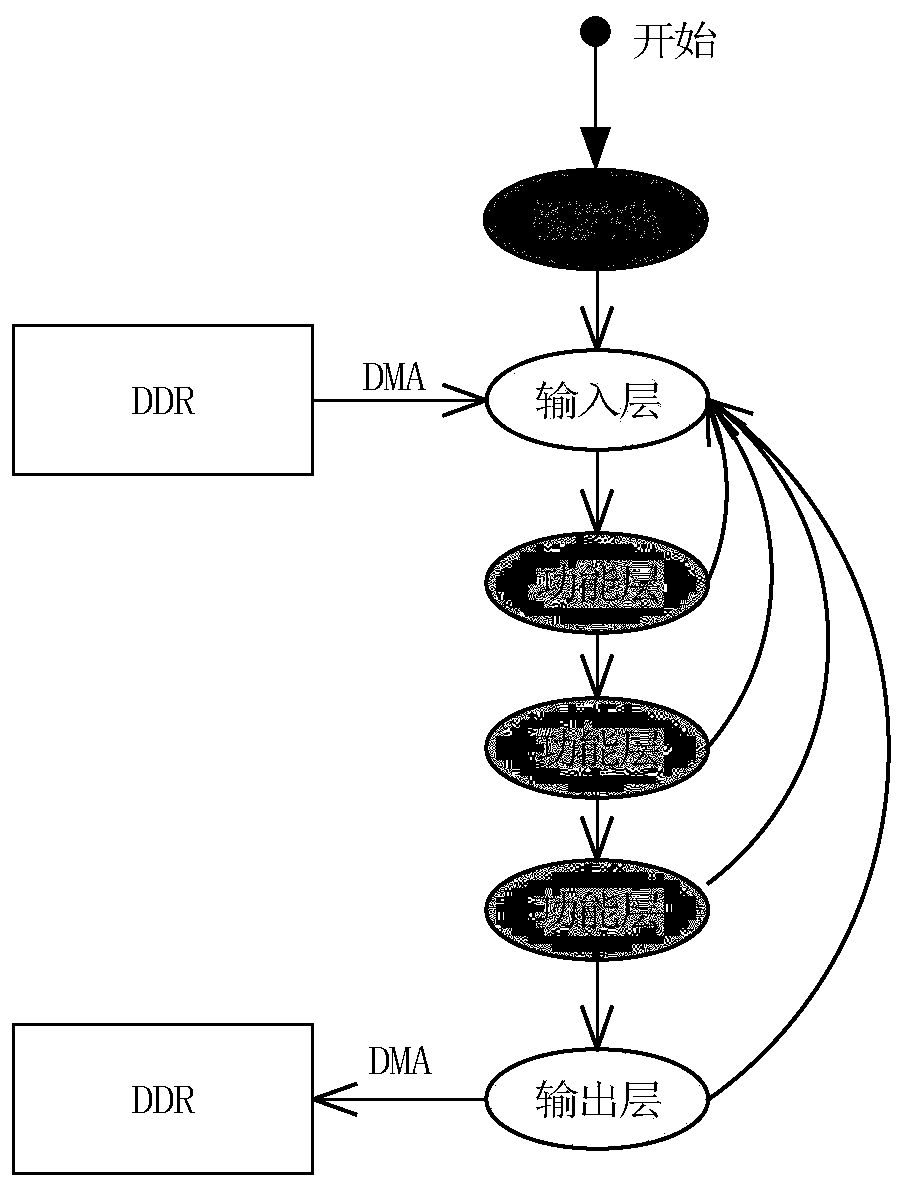

[0036] S1: Read the neural network structure file, analyze the data size and convolution kernel size of each layer, calculate and confirm the data buffer space required by each layer, and then allocate the corresponding address range in SRAM.

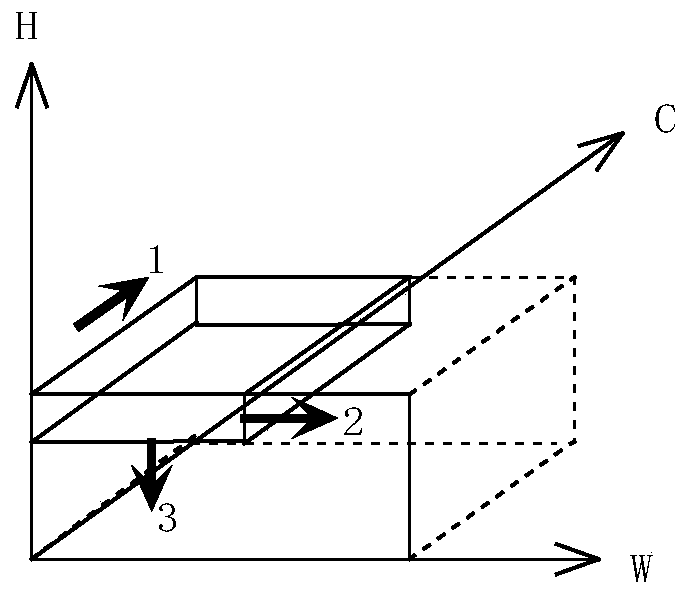

[0037] Taking the deep learning computing framework Caffe as an example, analyze the corresponding prototxt file. According to the network structure, the shape information of the data size of each layer (denoted as: C, H, W) and the size of the convolution kernel of each layer (denoted as: Kh, Kw) are obtained. Among them, the first layer needs to reserve the Kh+1th slice to allow the DMA to pre-move the data in advance, and the data from the second layer to the nth layer can be calculated and recycled only after K slices, so each layer The memory consumption of is marked as follows:

[0038] Input layer: move data from DDR to SRAM through DMA, the DMA operation unit for each move is (W*C), and the size of SRAM needs to be recorded as:...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More