Shift register unit and control method thereof, gate drive circuit and display device

A technology for shifting register units and gates, applied in information storage, static memory, static indicators, etc., can solve problems such as poor visual effects of display devices, affect user visual experience, and increase transistor leakage, and achieve high-quality visual effects , Improve the picture display quality, eliminate the effect of transistor leakage increase

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

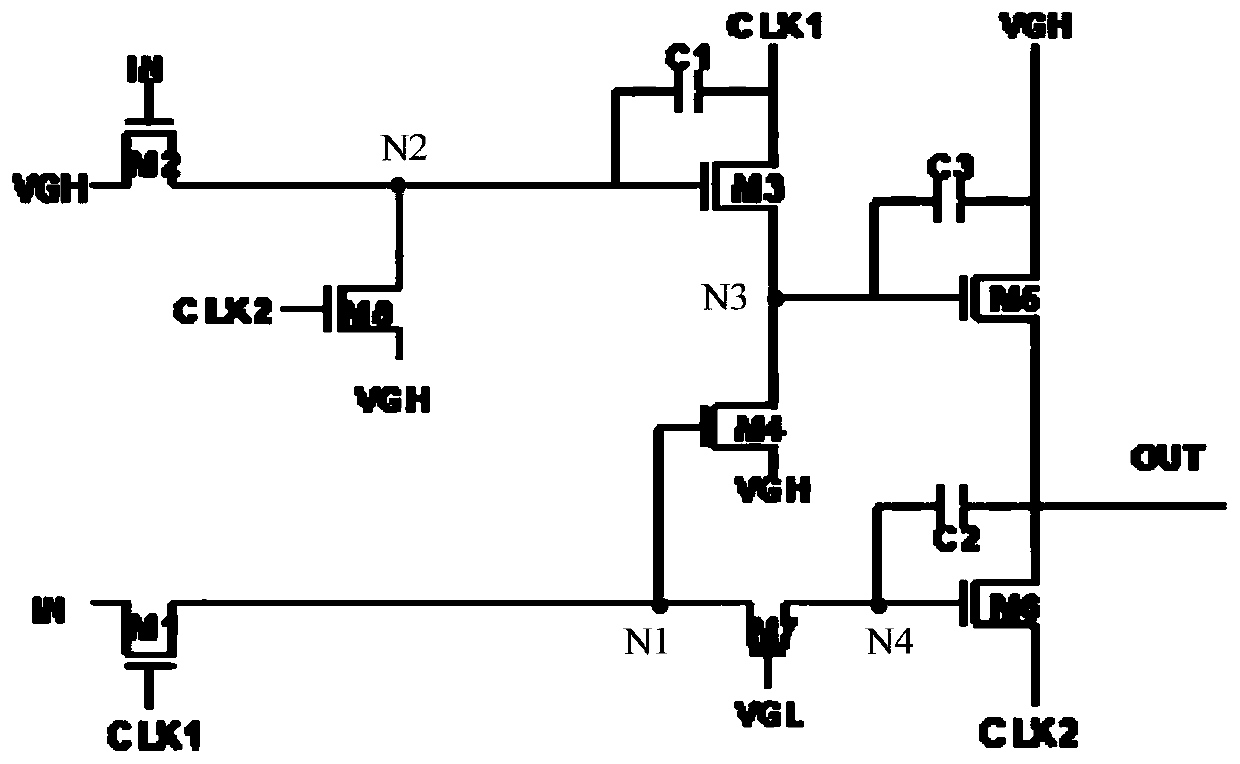

[0068] image 3 It is a schematic structural diagram of a shift register unit provided by an embodiment of the present application. Such as image 3 As shown, the shift register unit of the present application may include:

[0069] The first transistor M1 is controlled by the signal input from the first clock signal terminal CLK1 , and is used for transmitting the signal input from the input signal terminal IN to the first node N1 .

[0070] The second transistor M2 is controlled by the signal input from the input signal terminal IN, and is used for transmitting the signal input from the first voltage signal terminal VGH to the second node N2.

[0071] The third transistor M3 is controlled by the potential signal of the second node N2, and is used for transmitting the signal input from the first clock signal terminal CLK1 to the third node N3.

[0072] The first terminal of the first capacitor C1 is used to input the potential signal of the second node N2, and the second te...

Embodiment 2

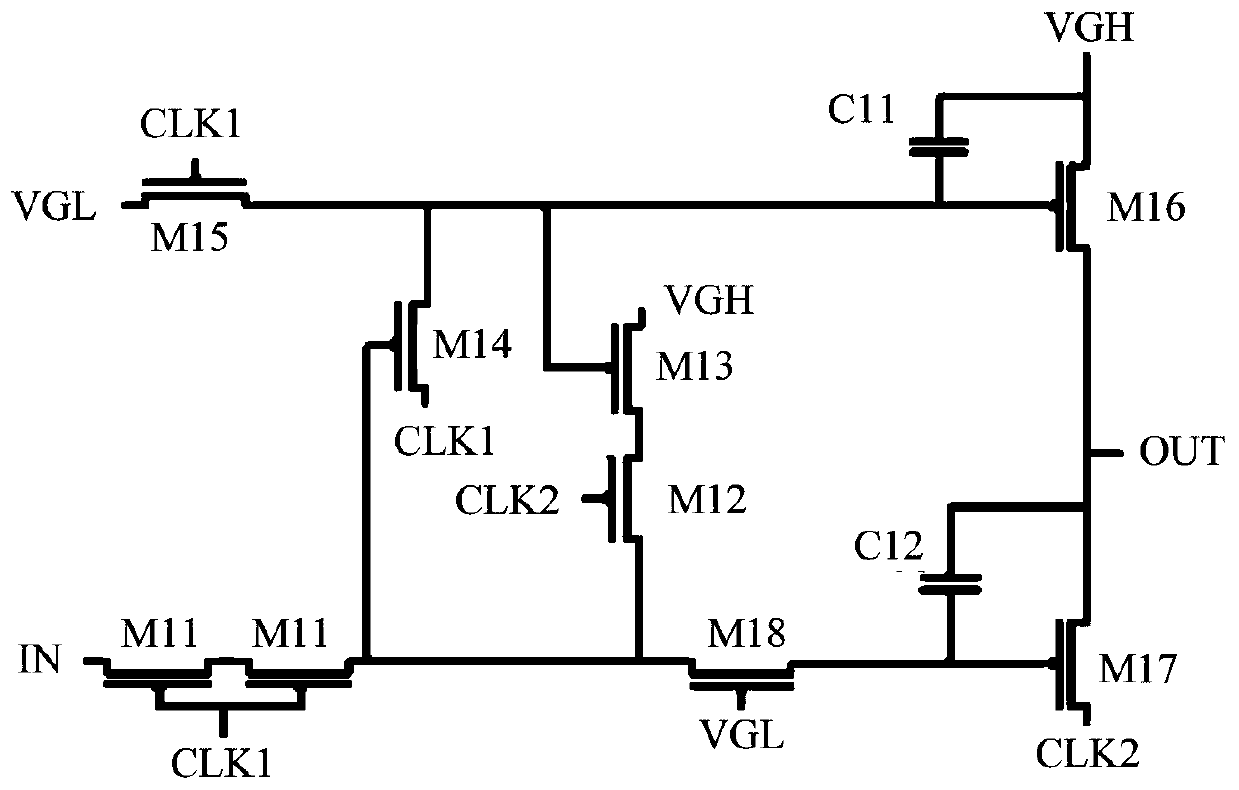

[0098] Image 6 It is a schematic structural diagram of a gate driving circuit provided by an embodiment of the present application. Such as Image 6 As shown, the shift register unit of the present application may include:

[0099] The first transistor M1 is controlled by the signal input from the clock signal terminal CLK, and is used for transmitting the signal input from the input signal terminal IN to the first node N1.

[0100] The second transistor M2 is controlled by the signal input from the clock signal terminal CLK, and is used for transmitting the signal input from the first voltage signal terminal VGH to the second node N2.

[0101] The fourth transistor M4 is controlled by the potential signal of the first node N1, and is used for transmitting the signal input from the first voltage signal terminal VGH to the second node N2.

[0102] The fifth transistor M5 is controlled by the potential signal of the second node N2, and is used for transmitting the signal inp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More