Gate drive circuit and display device

A gate drive circuit and display device technology, applied to static indicators, instruments, etc., can solve problems such as unevenness, horizontal dense lines of display devices, etc., and achieve the effect of avoiding picture quality problems and uneven brightness and darkness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

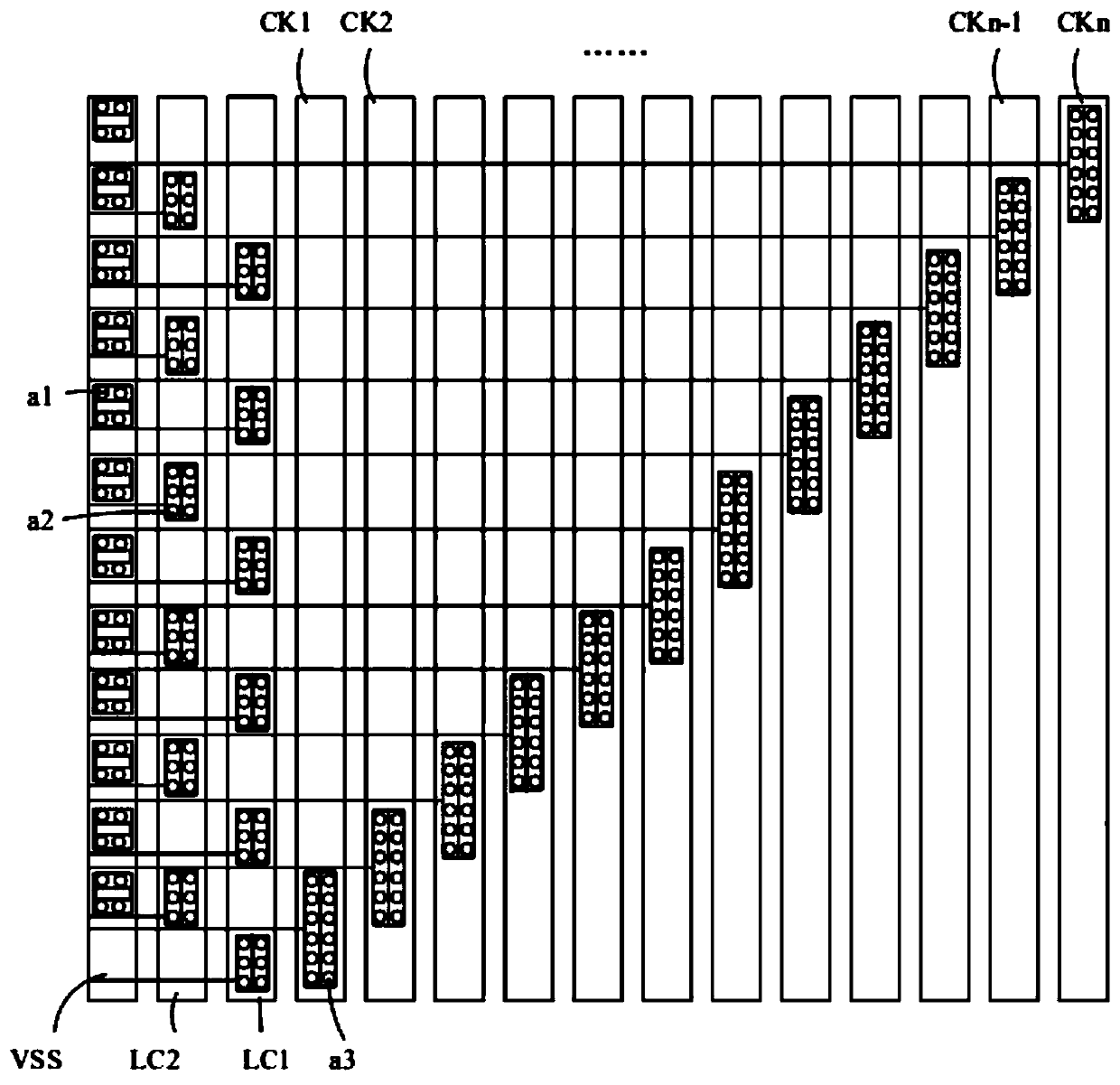

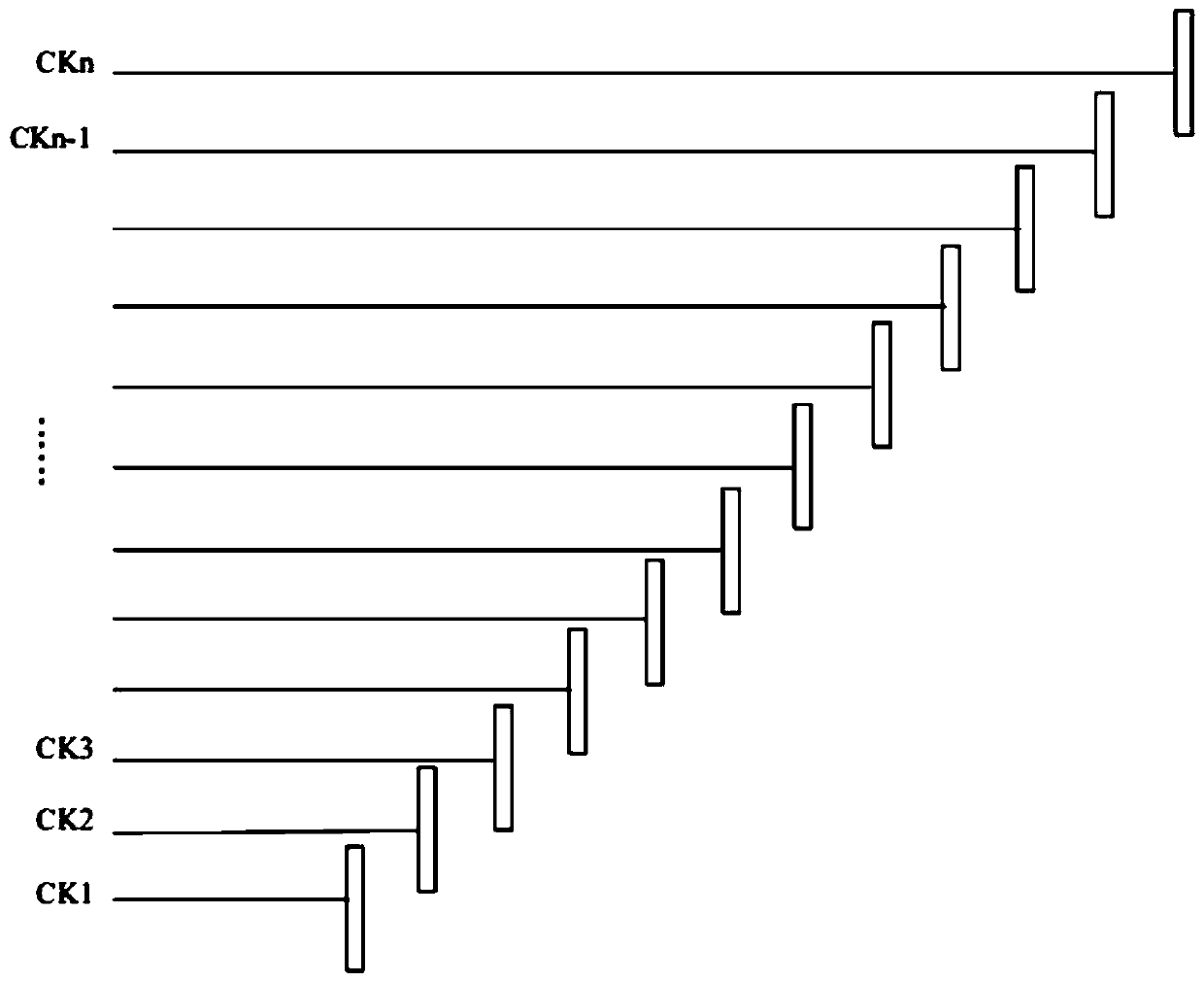

[0028] The technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application. Apparently, the described embodiments are only some of the embodiments of this application, not all of them. Based on the embodiments in this application, all other embodiments obtained by those skilled in the art without making creative efforts belong to the scope of protection of this application.

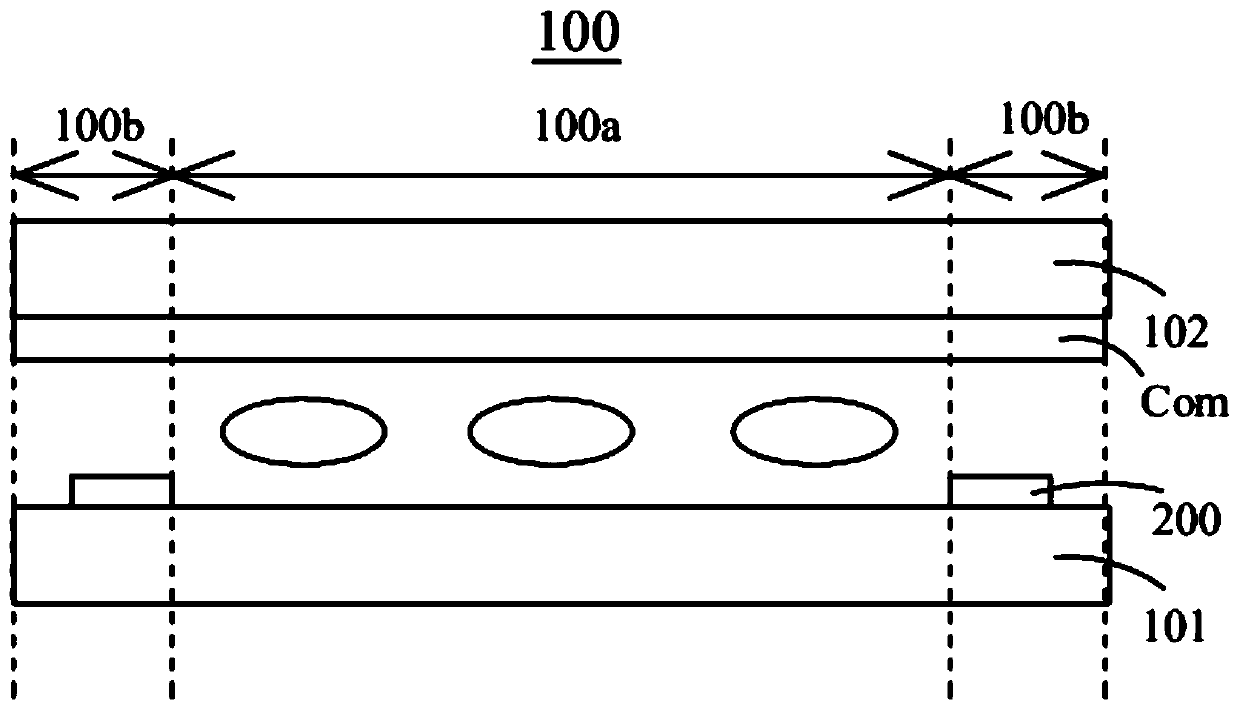

[0029] see figure 2 , which is a schematic diagram of a display device in an embodiment of the present application. The display device 100 includes an array substrate 101 , a color filter substrate 102 and a liquid crystal layer disposed between the array substrate 101 and the color filter substrate 102 .

[0030]The display device 100 has a display area 100a and a non-display area 100b located on the periphery of the display area 100a. The display area 100a is provided with ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More