Multi-instruction out-of-order transmitting method based on instruction withering and processor

A multi-instruction, processor technology, applied in concurrent instruction execution, electrical digital data processing, instruments, etc., can solve the problem of increased delay of the arbitration circuit, and achieve the effect of low delay and high IPC

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

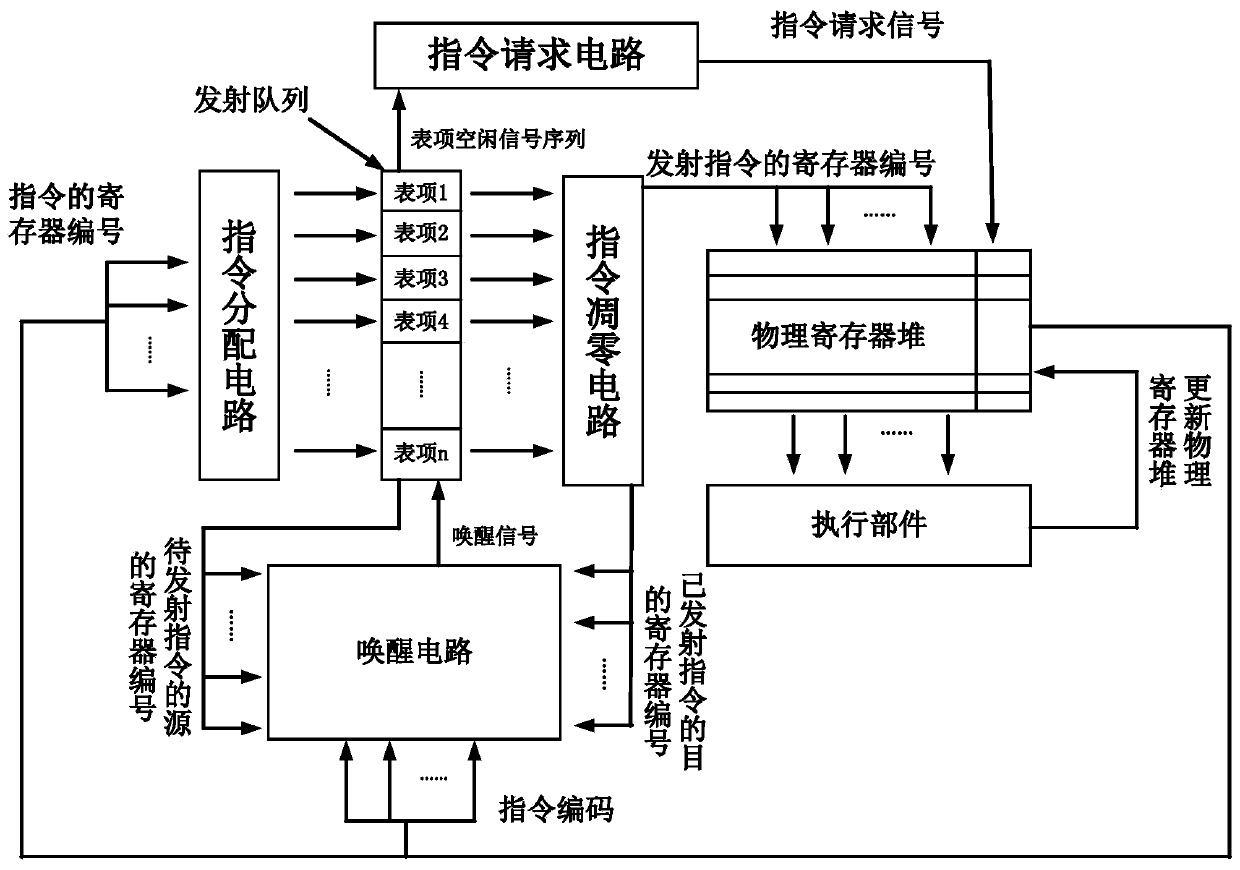

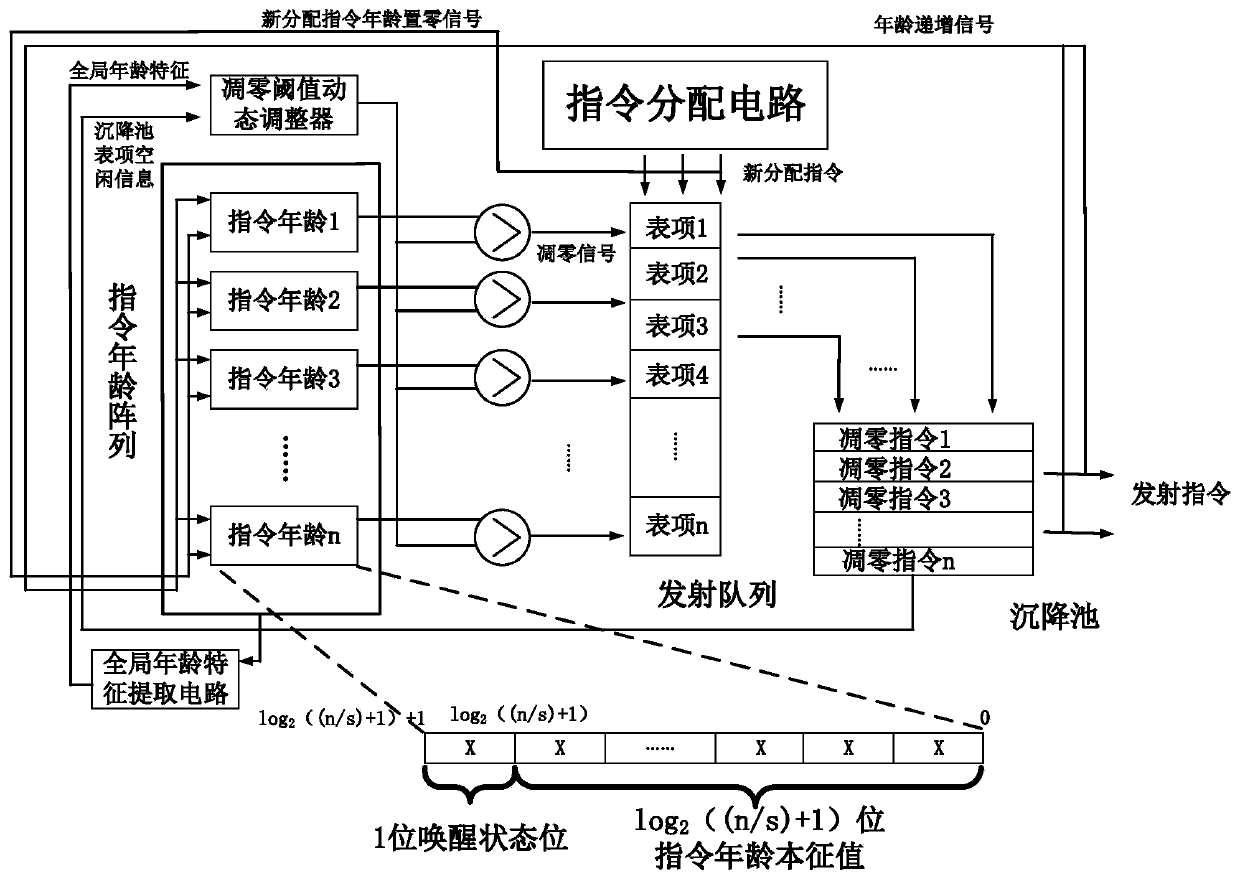

[0047] This embodiment provides a processor, see figure 1 , a schematic diagram of the overall composition of the multi-instruction out-of-order emission architecture of the processor, the multi-instruction out-of-order emission architecture includes: an instruction distribution circuit, an instruction withering circuit, an instruction request circuit based on a class adder, and a dynamic delay wake-up circuit.

[0048] Wherein, the instruction allocating circuit allocates the register-renamed instruction to each entry in the instruction issuing queue. The instruction issue queue includes multiple entries, and each entry contains an instruction to be issued. If there is an idle entry in the instruction issue queue, the instruction allocated through the allocation circuit will be accepted.

[0049] All the instructions to be issued that have just entered the entry are in the non-awakened state. If the number of the source register of an instruction is equal to the label of the ...

Embodiment 2

[0104] This embodiment provides a multi-instruction out-of-order emission method based on instruction withering, which is used in the processor described in Embodiment 1. The emission architecture of the processor is a non-data-capture emission architecture, that is, the CPU executes the instruction after the emission stage. The physical register file will be actually read, and each entry in the launch queue stores the number of the physical register; the method includes:

[0105] S1, when the physical register file receives an instruction request signal from the instruction request circuit, output a suitable instruction to the instruction allocation circuit.

[0106] S2, the instruction assignment circuit assigns the instruction output by the physical register file to each entry in the instruction emission queue:

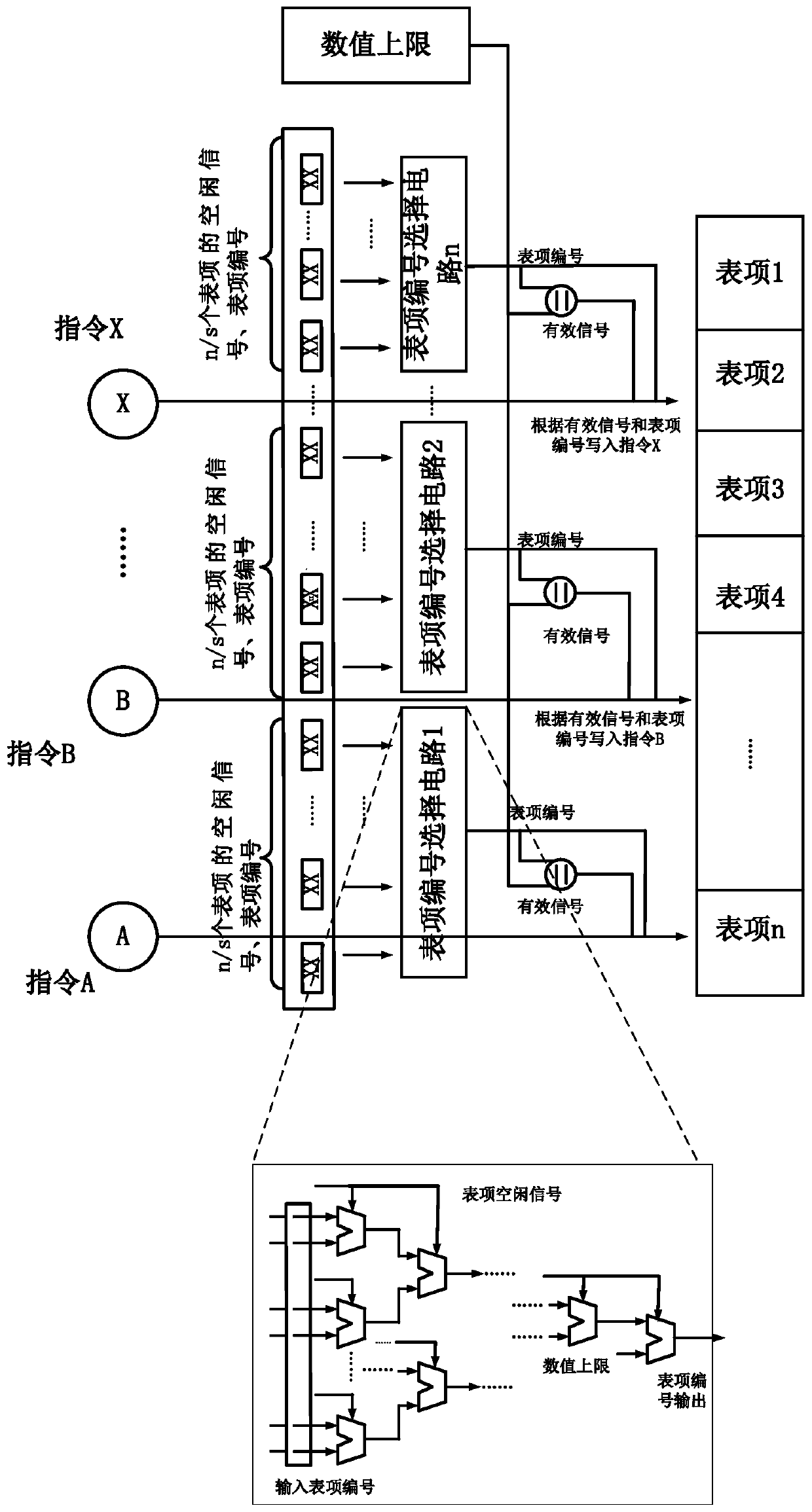

[0107] The command allocation circuit includes s table entry number selection circuits, and the input of each table entry number selection circuit is the idle sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More