Hybrid logical to physical caching scheme

A cache, physical address technology, applied in the field of memory devices, can solve problems such as increased processing time and a large amount of RAM storage space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The following detailed description refers to the accompanying drawings, which show, by way of illustration and not limitation, various embodiments in which the invention may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice these and other embodiments. Other embodiments may be utilized and structural, logical, mechanical, and electrical changes may be made to these embodiments. The various embodiments are not necessarily mutually exclusive, as some embodiments can be combined with one or more other embodiments to form new embodiments. Accordingly, the following detailed description should not be viewed in a limiting sense.

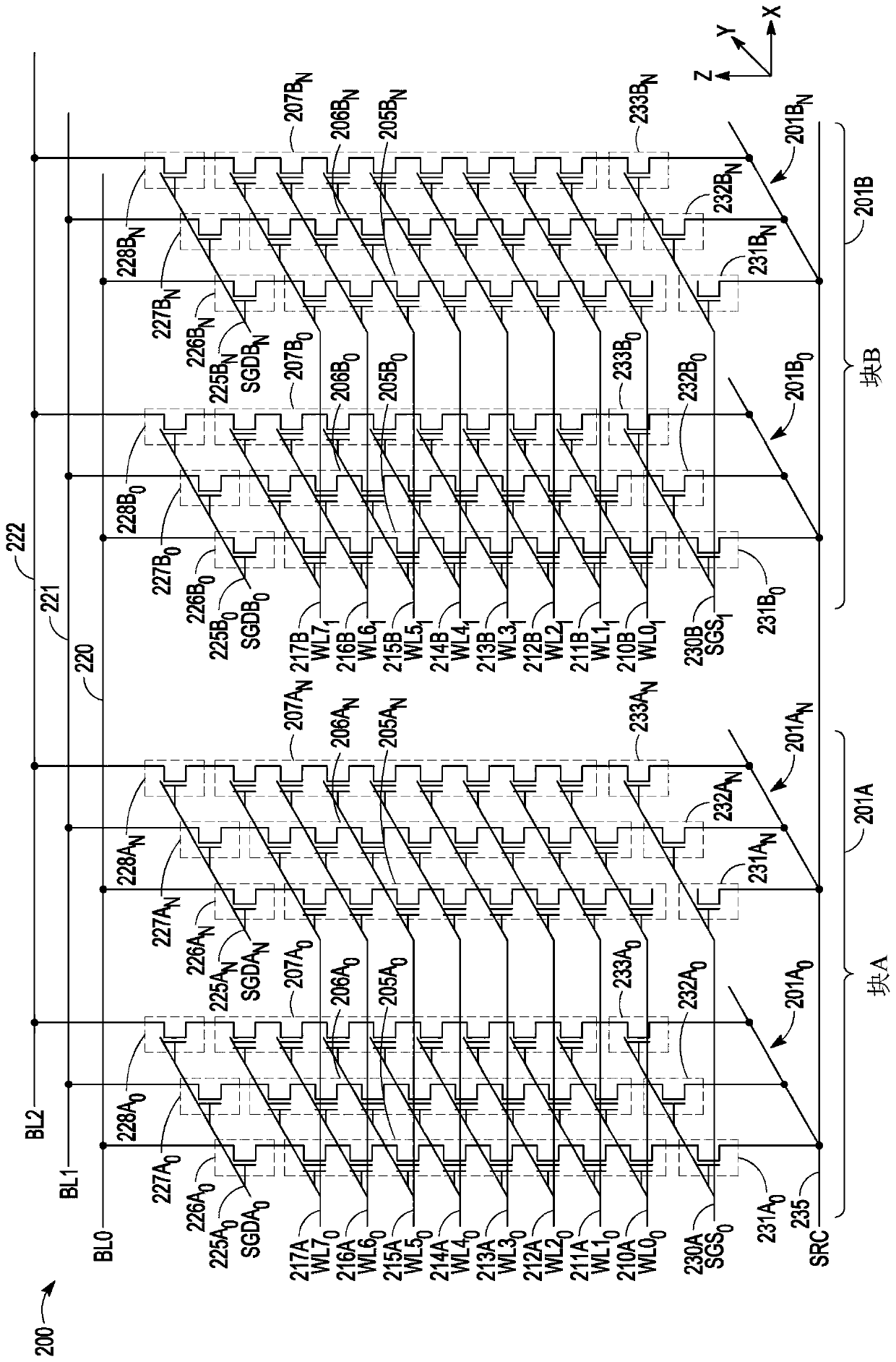

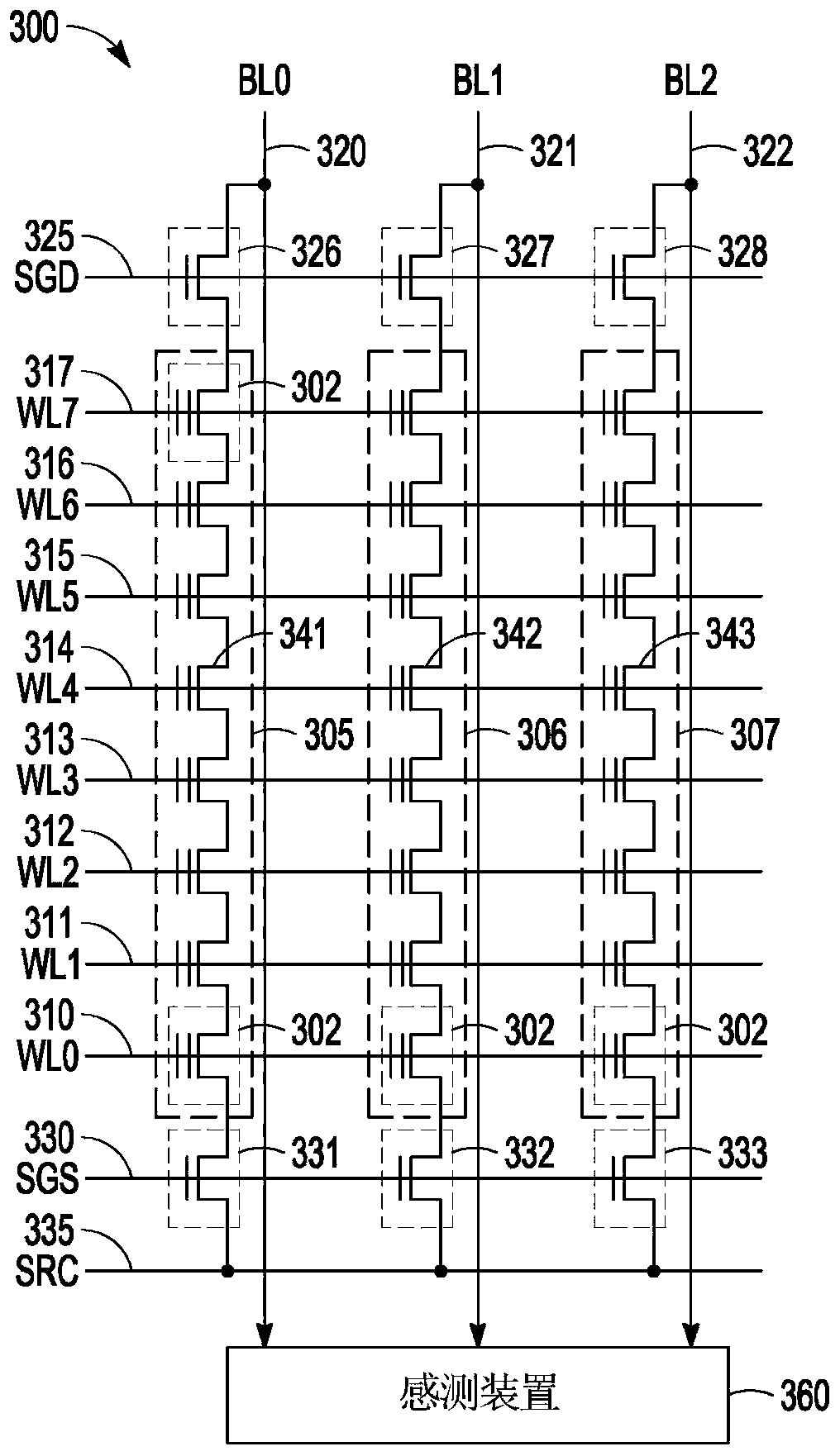

[0029] The memory system can be configured to maintain a set of L2P pointers. L2P pointers relate physical addresses at a memory array of a memory system to logical addresses used by one or more hosts. The L2P pointer can be stored in RAM of the memory system. Read and write request...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More