Interface circuit based on JESD204B protocol

A technology of interface circuits and protocols, applied in the field of high-speed serial interface circuits, can solve problems such as increasing design costs, and achieve the effects of simplified design, flexible application, and simple mechanism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

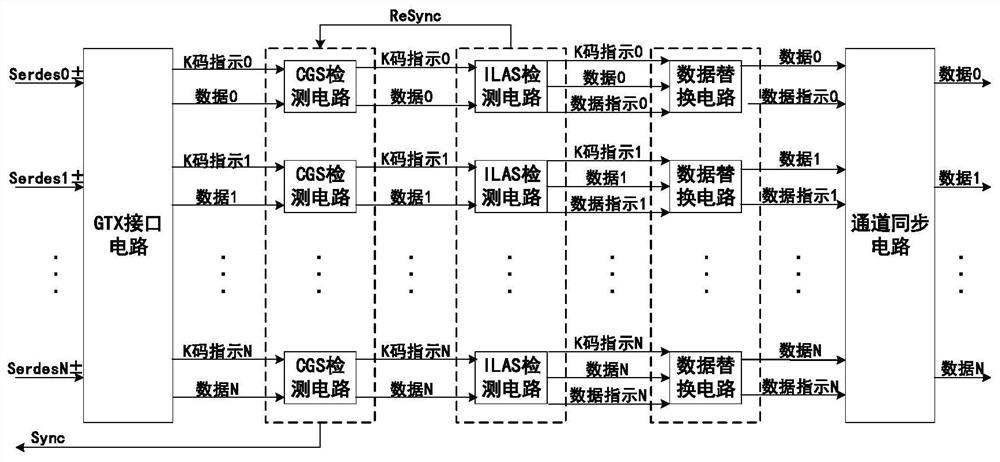

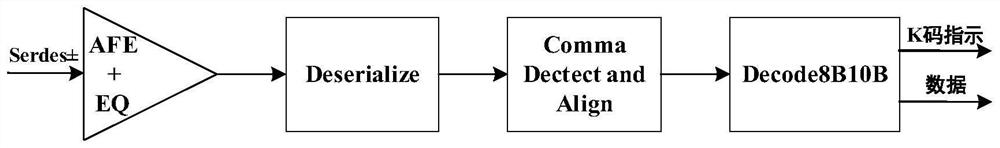

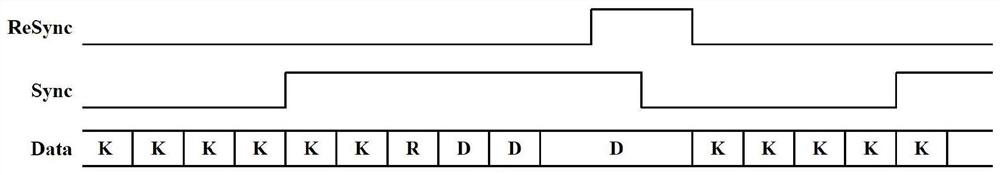

[0022] The interface circuit of the present invention is composed of a GTX interface circuit, a CGS detection circuit, an ILAS detection circuit, a data replacement circuit and a channel synchronization circuit; the GTX interface circuit uses the IP core to call N high-speed transceivers in the FPGA to realize the connection of N pairs of differential signal lines In, the serial data based on the JESD204B protocol is converted into parallel data, and the data and K code indication signal are output to the CGS detection circuit; the CGS detection circuit judges whether there is continuous 4 in each channel according to the input data and K code indication signal A K code (0xBC), after N channels are successfully detected, the Sync signal (link synchronization signal) output to the peripheral will be pulled high, and the data of each channel and K code indicator signal will be output to the ILAS detection circuit, waiting for the peripheral to send ILAS sequence. In addition, the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com