Data packet sorting method and system based on dual-port RAM

A sorting method and data packet technology, which is applied in the field of data transmission, can solve the problems of out-of-order data packets, out-of-order data packets, and different time-consuming data packets.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

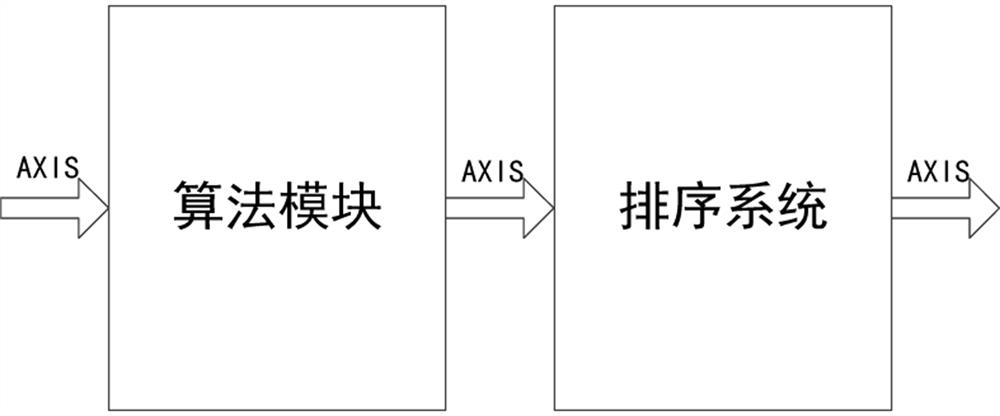

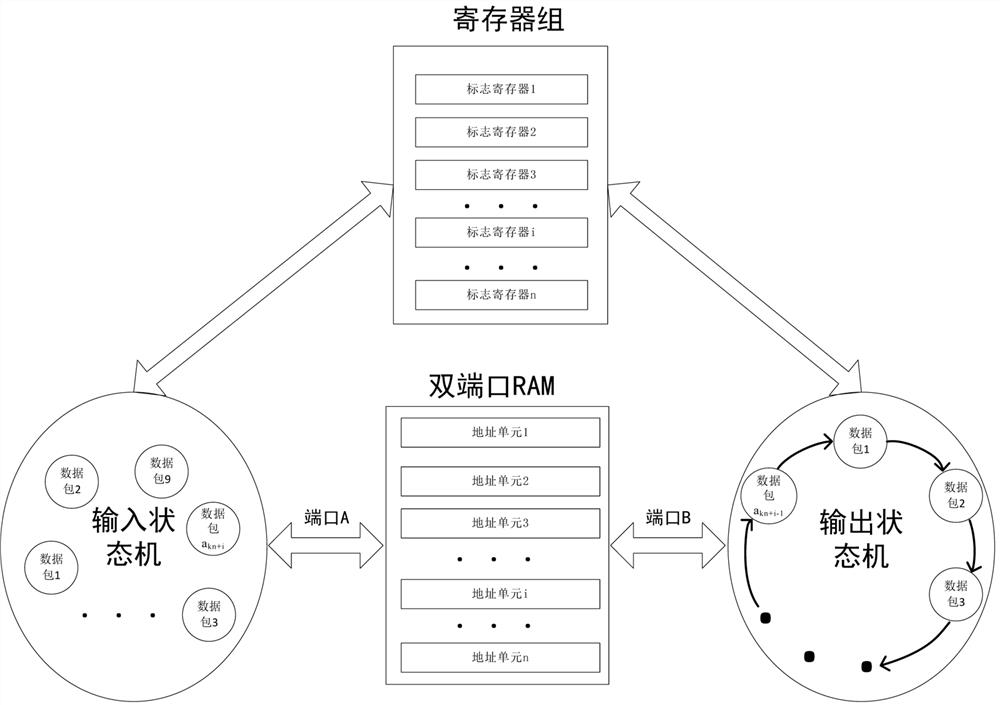

[0041] Please also see figure 1 and figure 2 , in a specific application, since the output results of multiple algorithm core operations of the algorithm module may be out of order, the present invention uses a sorting system to sort out the out-of-order data packets, and the sorting system includes an input state machine, a dual Port RAM, register bank, and output state machines. The dual-port RAM is respectively connected to the input state machine and the output state machine for data communication; the dual-port RAM includes n address units 1, 2, 3, ..., n, which are respectively used to receive the corresponding serial number The valid data packet; the register group includes n flag registers 1, 2, 3, ..., n, and the n flag registers are respectively one-to-one corresponding to n address units, and each flag register is used to identify the corresponding address Whether the unit has a valid data packet, if there is a valid data packet, the value of the flag register is...

Embodiment 2

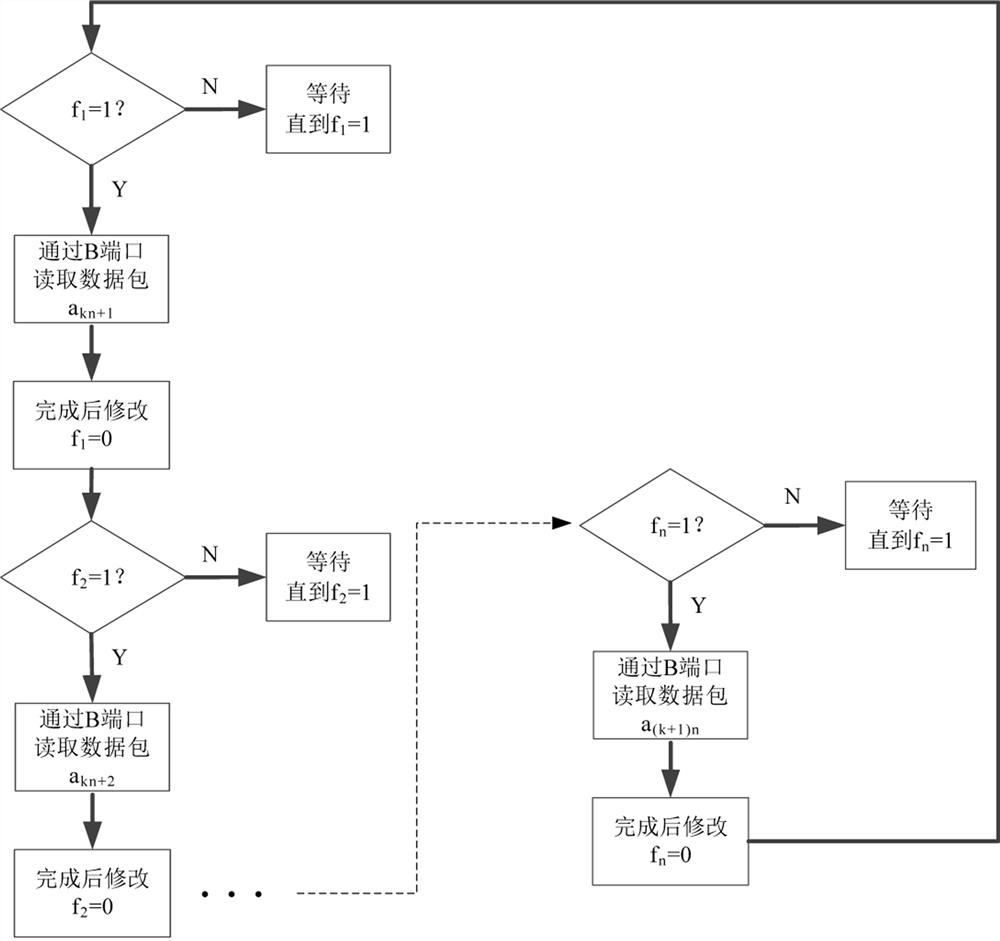

[0055] refer to Figure 4 The difference between this embodiment and Embodiment 1 is that another method for sorting data packets based on dual-port RAM is proposed, and the method includes the following steps:

[0056] Data packet reading phase:

[0057] Step 11, receive data packet a by input state machine kn+i , get the data packet a kn+i Sequence number i, wherein, k=1, 2, ..., m, 1≤i≤n; Let the input state machine have received the last packet of continuous sequence number as packet a p , the input state machine restricts the reception of data packets a within the specified sequence number range q , then p+1≤q≤p+n;

[0058] Step 12, after the input state machine determines the address unit i of the dual-port RAM based on the serial number i, check the value f of the flag register i corresponding to the address unit i i Whether it is equal to 0, if yes, then enter step 13, if no, then wait until the value f of the flag register i i equal to 0;

[0059] Step 13, the ...

Embodiment 3

[0071] The present embodiment provides a packet sorting system based on a dual-port RAM, including an input state machine, a dual-port RAM, a register bank, and an output state machine; the dual-port RAM is connected to the input state machine and the output state machine respectively Data communication connection is performed, and the register group is respectively connected with the input state machine and the output state machine for data communication, so as to realize the data packet sorting method based on dual-port RAM described in embodiment 1 or embodiment 2.

[0072] In the data packet sorting system based on dual-port RAM of this embodiment, the data packet received by the input state machine is a data packet processed by the algorithm module, wherein the algorithm module is connected to the input state machine for data communication , the algorithm module includes a plurality of algorithm cores, and the plurality of algorithm cores can respectively receive data pack...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More