Test structure and its test method

A technology for testing structures and testing methods, applied in semiconductor/solid-state device testing/measurement, electronic circuit testing, electrical measurement, etc., can solve the passivation layer crack, evaluate the internal stress of the passivation layer, detect the passivation layer crack, etc. problem, to achieve the effect of sensitive detection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

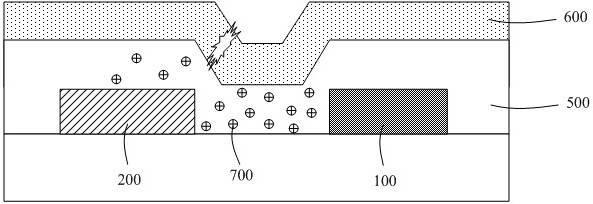

[0050] As mentioned in the background art, the film integrity of the passivation layer plays an extremely important role for the entire chip or device. Therefore, how to judge the integrity of the passivation layer and evaluate the internal stress of the passivation layer is particularly necessary.

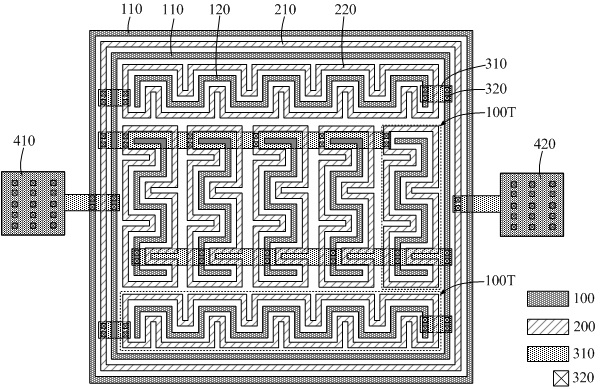

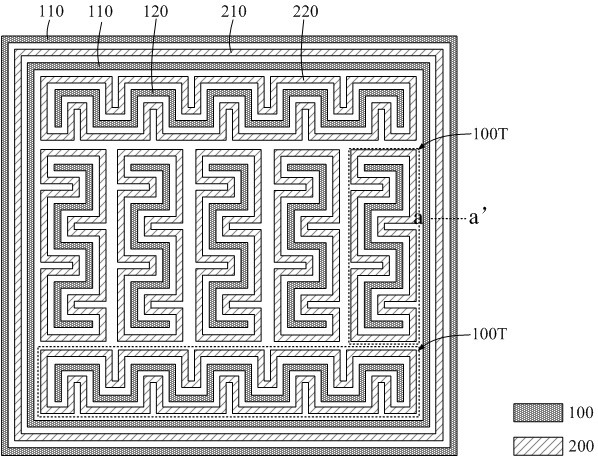

[0051] In view of the above technical problems, the present invention mainly obtains a test structure for detecting the integrity of the passivation layer by performing circuit layout on the metal layer immediately below the passivation layer.

[0052] In addition, the present invention also finds that the circuit layout of the metal layer immediately below the passivation layer will affect the stress distribution of the passivation layer. The circuit layout of the metal layer is improved so that the internal stress of the passivation layer can also be evaluated by using the test structure of the present invention.

[0053] The test structure and test method proposed by the prese...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More