A Fully Pipelined Multiply-Add Cell Array Circuit for Convolutional Neural Networks

A convolutional neural network and cell array technology, applied in the field of artificial intelligence algorithm hardware implementation, can solve the problems of difficult realization and application of MAC array circuit structure, low hardware resource utilization, complex control logic, etc., to improve the complexity of data space. The effect of increasing the utilization rate, increasing the time reuse rate, and improving the system performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention. In addition, the technical features involved in the various embodiments of the present invention described below can be combined with each other as long as they do not constitute a conflict with each other.

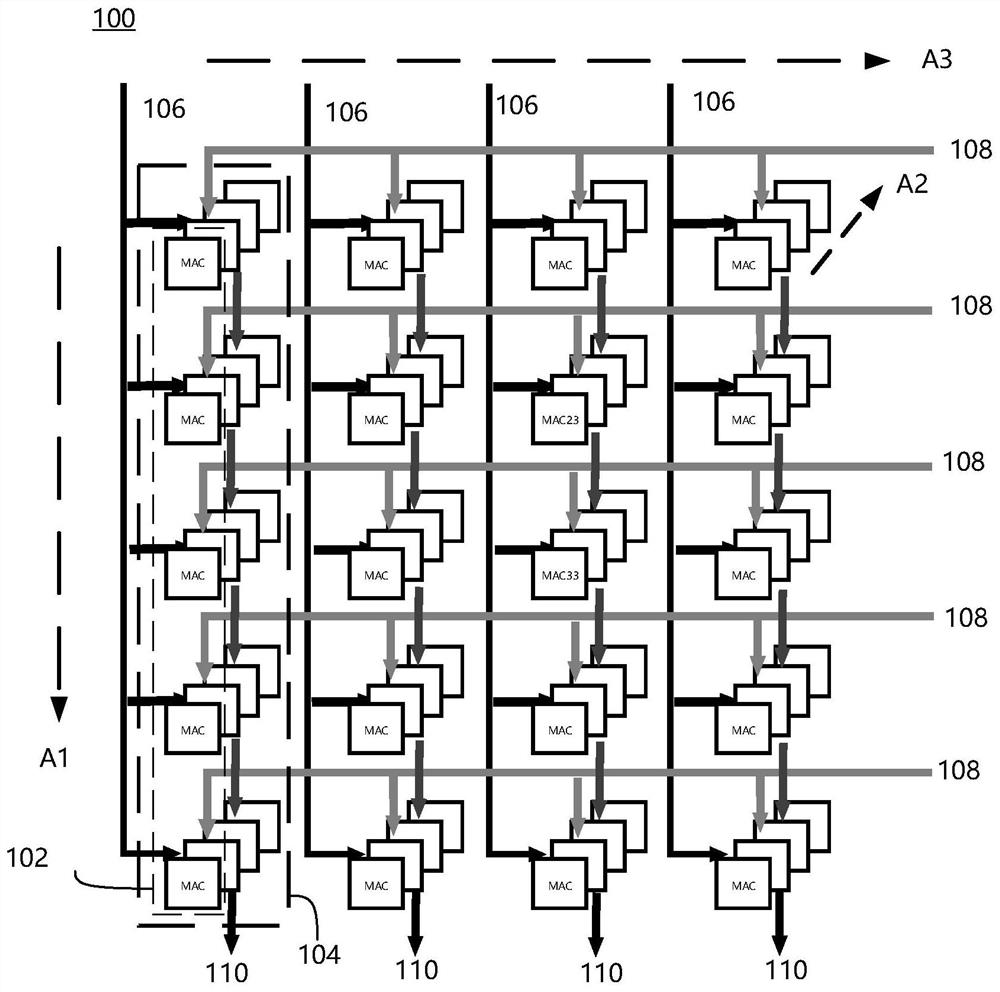

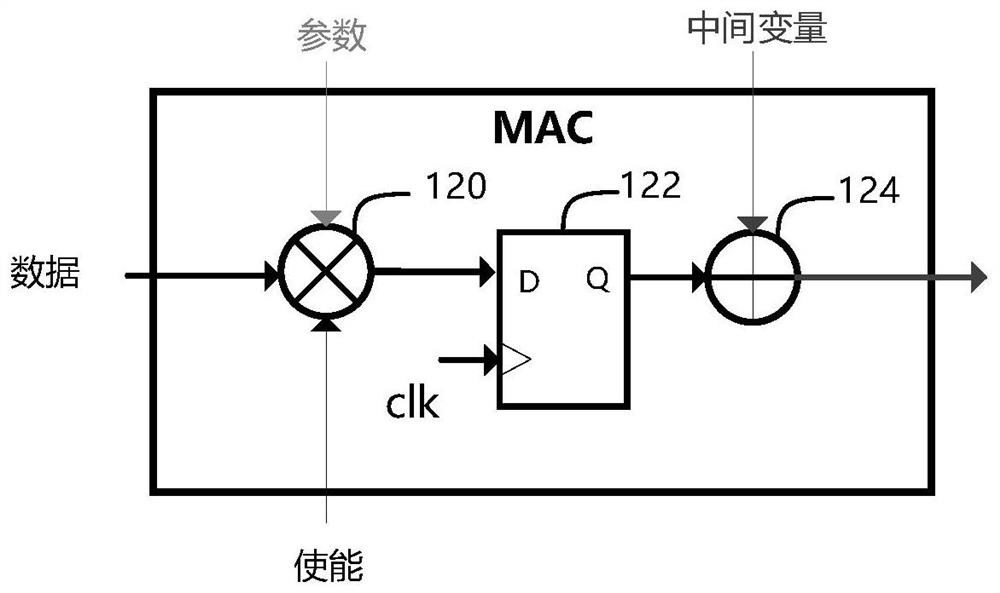

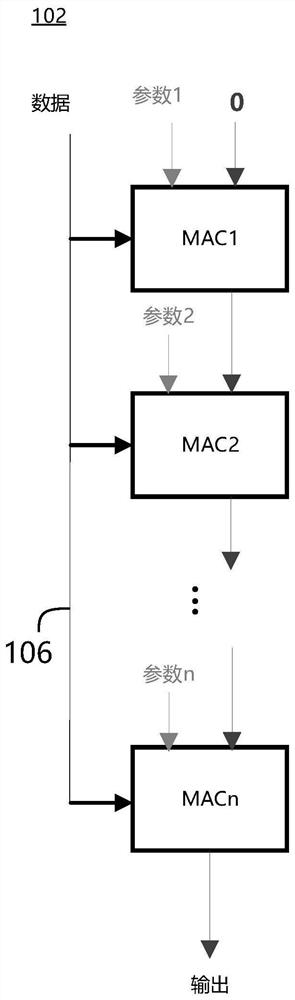

[0027] Please refer to figure 1 , the embodiment of the present application provides a MAC array, including a plurality of MAC units. The arrangement of the plurality of MAC units is: a single MAC unit is repeatedly arranged along the first direction A1 n, and the n MAC units are connected together in a cascade manner to form a MAC sub-module 102; the MAC sub-module The modules 102 are repea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More